- 技術解決方案

- PCI Express

概述

PCI Express® (PCIe®) 是一種通用串行互連,適用於通信、數據中心、企業、嵌入式、測量測試、軍事以及其它市場的廣泛應用。它可作為外設互連、芯片對芯片接口以及許多其它協議標準的橋接器。

AMD 可為 PCI Express 提供各種高性能、低功耗的集成塊,在眾多器件中作為經過強化的子係統。

此外,AMD 還提供 PCIe DMA 和 PCIe 橋接器軟硬 IP 塊,其可利用集成的 PCI Express 塊、帶有 PCI Express 連接器的板卡、連接套件、參考設計、驅動程序和工具,簡化實現基於 PCIe 的設計的過程。

選擇一個器件係列,以便查看該係列的 AMD PCIe 解決方案組合。

Versal 解決方案

利用 PCI Express® 規範實現方案的係統在數據中心、通信和嵌入式應用中非常普遍。Versal™ 架構中的多個連接選項直接支持用戶關注其核心能力的需求,采用基於標準的高級接口。Versal 架構中用於 PCI Express 的集成塊提供優異的高性能,與完全軟化的 IP 解決方案相比,不僅簡單易用,而且效率很高。Versal 架構集成五種 PCI Express 集成塊:

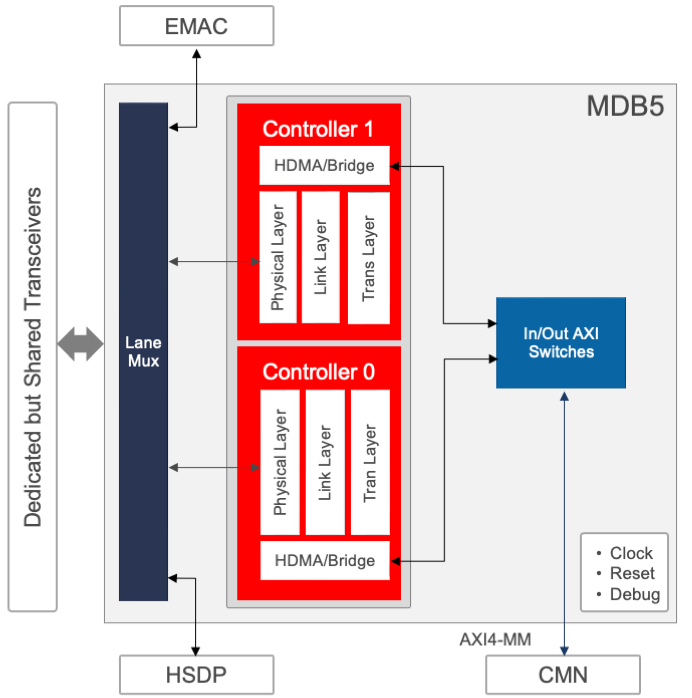

- MDB5:該集成塊適用於支持 DMA/ 橋接的 PCI Express Rev. 5.0

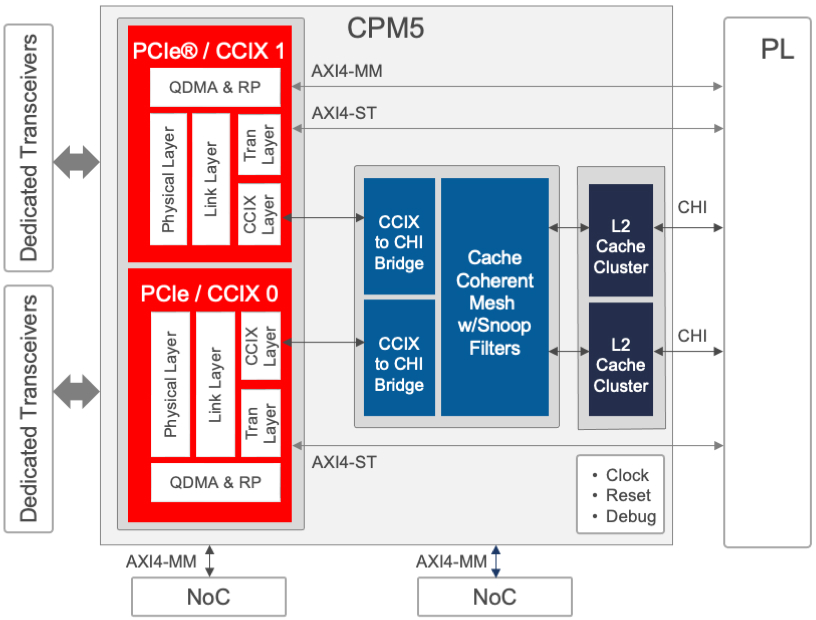

- CPM5:該集成塊適用於支持 DMA/ 橋接的 PCI Express Rev. 5.0

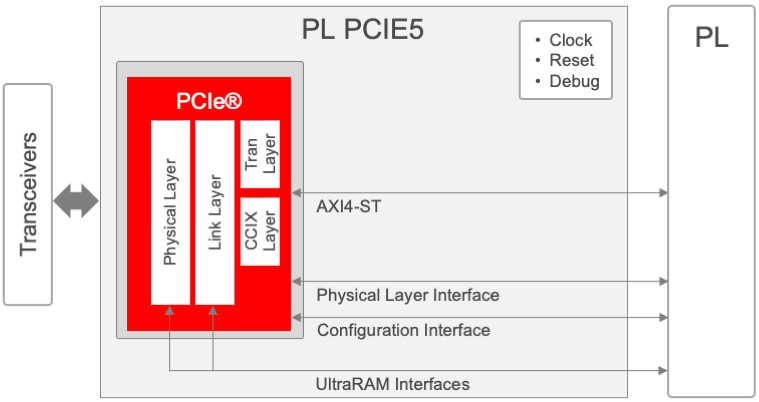

- PL PCIE5: 用於 PCI Express Rev. 5.0 的集成塊

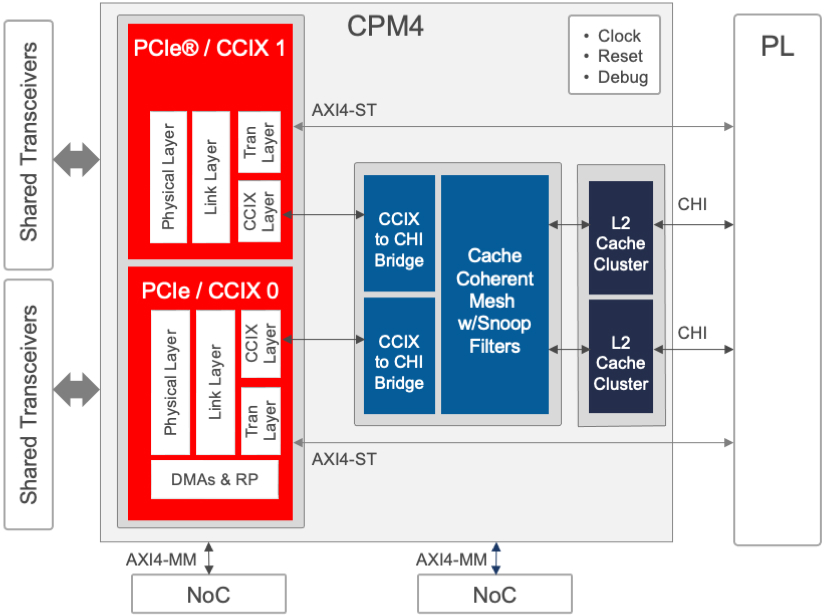

- CPM4:該集成塊適用於支持 DMA/ 橋接的 PCI Express Rev. 4.0

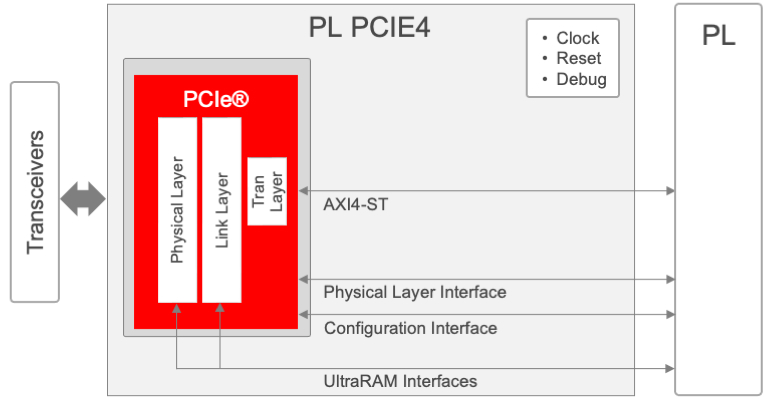

- PL PCIE4:用於 PCI Express Rev. 4.0 的集成塊

MDB5、CPM5、PL PCIE5、CPM4 及 PL PCIE4 與現在可用的 GTYP 及 GTY 收發器相結合,能夠以規範定義的數據速率進行接口運行。其範圍從單信道 (Gen1x1) 每通道 2.5GT/s 到其額定最大鏈路配置,有些集成塊可達 8 信道 (Gen5x8) 每信道 32GT/s,甚至 16 信道 (Gen4x16 16) 每信道 16GT/s。

下表總結了 Versal 架構中用於 PCI Express 的集成塊的主要特征。請參閱 Versal 架構與现金网博e百

說明書:概覽 (DS950),進一步了解基於可訂購器件、封裝及速度等級組合的可用資源和功能。

PCI Express 的 Versal 架構集成塊 |

|||||

|---|---|---|---|---|---|

MDB5 |

CPM5 |

PL PCIE5 |

35

CPM4

|

PL PCIE4 |

|

| 關聯 規格 |

PCIe Rev. 5.0 | PCIe Rev. 5.0 | PCIe Rev. 5.0 |

PCIe Rev. 4.0 |

PCIe Rev. 4.0 |

| PCIe 最大通道數 鏈路配置 |

Gen5x4 2 x Gen5x2 Gen5x2 |

2 x Gen5x8 Gen4x16 2 x Gen4x 8 |

Gen5x4 Gen4x8 Gen 3x16 |

Gen4x16 2 x Gen4x8 |

Gen4x8 Gen 3x16 |

| PCIe 端口 支持的類型 |

EP, RP | EP, RP, Switch |

EP, RP, Switch |

EP, RP, Switch |

EP, RP, Switch |

| Key PCIe 功能 |

SR-IOV 8PF / 64VF |

SR-IOV 16PF / 4KVF |

SR-IOV 8PF / 4KVF |

SR-IOV 4PF / 252VF |

SR-IOV 4PF / 252VF |

| 集成了 DMA/ 橋接 | 兩個橋接,需要選擇一個或兩個:可選 HDMA | 選擇一個或兩個:可選 QDMA/ 橋接 | - | 選擇其一: 可選 QDMA/ 橋接 可選 XDMA/ 橋接 |

- |

MDB5、CPM5、PL PCIE5、CPM4 和 PL PCIE4 可以用於減少的鏈路配置,以優化现金网博e百 設計成本,支持最新封裝,降低電路板複雜性並縮減功率預算。此外,更少的鏈路配置還可支持更低的可編程邏輯資源利用率,這取決於用於擴展這些集成塊應用級功能的任何軟 IP 解決方案的性質。CPM5、PL PCIE5、CPM4 和 PL PCIE4 可配置為端點 (EP)、根端口 (RP) 和交換機端口類型。參見 PCI Express Versal 自適應 SoC 集成塊现金网博e百 指南第 343 頁和 PCI Express Versal 自適應 SoC CPM 模式现金网博e百 指南第 346 頁。MDB5 不僅可配置為端點 (EP) 和根端口 (RP) 端口類型,而且還必須與其集成型 DMA/ 橋接解決方案一起使用。

AMD 可為 Versal 架構中用於 PCI Express 的集成塊提供預先驗證的高性能 DMA/ 橋接子係統,從而可幫助用戶將設計投資集中在其最有價值的領域。所提供的 DMA 和橋接子係統選項包括:

- MDB5 不僅包含兩個 PCI Express 控製器,而且還集成兩個 HDMA/ 橋接子係統實例。集成型 DMA 的使用是可選的,每個實例都是可獨立定製的。HDMA 子係統可提供集成處理器和 AXI 互連的緊密耦合。此外,該子係統還包含橋接功能性。數據可通過內存映射技術移動,其中包括可編程片上網絡 (NoC)。

- CPM5 不僅包含兩個 PCI Express 控製器,而且還集成兩個 QDMA/ 橋接子係統實例。集成型 DMA 的使用是可選的,每個實例都是可獨立定製的。QDMA 子係統提供基於隊列的可擴展 DMA,能夠在低時延情況下移動大量數據,並支持企業級现金网博e百 通常需要的多個物理及虛擬功能。數據可通過內存映射技術(包括可編程片上網絡 (NoC))或流媒體技術移動到 Versal 自適應 SoC 可編程邏輯中。該子係統還包括 AXI 互聯的橋接功能。

- CPM4 不僅包含兩個 PCI Express 控製器,而且還集成一個 QDMA/XDMA/ 橋接子係統實例。集成型 DMA 的使用是可選的,而且使用時,既可配置為 QDMA 子係統(如 CPM5 中的 QDMA 子係統),又可配置為 XDMA 子係統。數據可通過內存映射技術(包括可編程 NoC)或流媒體技術移動到 Versal 自適應 SoC 可編程邏輯中。該子係統還包括 AXI 互聯的橋接功能。

- PL PCIE5 和 PL PCIE4 是用於 PCI Express 的獨特控製器,由 DMA/ 橋接子係統(通過 Vivado™ 設計套件 IP 目錄免費提供)的軟 IP 實施方案提供支持。

對於大多數用戶,所提供的 DMA 和橋接子係統可提供省時的基礎架構,提供高性能的全方位數據移動。查看 Versal adaptive SoC DMA and Bridge Subsystem for PCI Express 现金网博e百

指南 PG344 和 Versal adaptive SoC CPM DMA and Bridge Mode for PCI Express 现金网博e百

指南 PG347。對於想要連接其自己的 DMA/ 橋接子係統的用戶,可保存其驅動程序及應用軟件的投資,而對於想要使用終端應用的詳細知識來定製或優化功能的用戶,選項可用於旁路 CPM5 和 CPM4 的 DMA/ 橋接。為了得到實現完全定製解決方案的終極自由度,AMD 還通過 Vivado Design Suite IP 目錄為 PCI Express 提供了一個軟 IP 核 PHY,這可幫助設計人員將其自己的 PCI Express 控製器連接至所提供的 GTYP 和 GTY 收發器。

支持的现金网博e百 與技術

PCI Express 的高速串行收發器

UltraScale+ 解決方案

AMD 16 nm UltraScale™ 器件集成當今數據中心、通信和嵌入式應用所需的大量重要 PCI Express® 功能。UltraScale+ 器件使用三種類型的集成塊:PCIE4、PCIE4C 和 PCIE4CE。

PCIE4 模塊符合 PCI Express 基本規範 v3.1,支持 Gen3x16,還可針對較低鏈路位寬及速度進行配置。PCIE4 模塊不支持 Gen4 運行。

PCIE4C 模塊符合 PCI Express 基本規範 v3.1(支持達 8.0 GT/s )(Gen3),與 PCI Express 基本規範 v4.0(支持達16.0 GT/s) (Gen4) 兼容。此外,PCIE4C 塊也符合 CCIX 基本規範 v1.0 Version 0.9,支持高達 16.0 GT/s 的速度。PCIE4C 模塊在 Gen3 上支持多達 16 個信道,在 Gen4 上支持多達 8 個信道,可針對較低的鏈路位寬和速度進行配置,節省資源和電源。

PCIE4CE 模塊符合 PCI Express 基本規範 v4.0,支持高達 16.0GT/s 的速率 (Gen4)。PCIE4CE 模塊在 Gen3 上支持多達 16 個信道,在 Gen4 上支持多達 8 個信道,可針對較低的鏈路位寬和速度進行配置,節省資源和電源。一部分器件隻包含一個版本的集成塊,而另一部分器件則提供一係列不同版本的集成塊。

UltraScale™ 架構中 PCIe® 的所有集成塊都可配置為端點或根端口。根端口可用於構建兼容根聯合體的基礎,允許通過 PCI Express 協議進行自定義芯片間的通信,並將 ASSP 端點器件(如以太網控製器或光纖通道 HBA 或 NVMe SSD)連接至 FPGA、MPSoC 或 RFSoC。

該 PCI Express 的集成塊 IP 在芯片中硬化,支持:

- 所有版本的集成塊提供高達 Gen3x16 的功能;在提供 PCIE4C 模塊的器件中與 Gen4x8 兼容;在提供 PCIE4CE 模塊的器件中與 Gen4x8 兼容。如需了解所支持的特定鏈路寬度和速度,請查看所需 IP 的现金网博e百 指南(PG213、 PG195 或 PG302)。如欲了解有關 PCIE4C 模塊與 Gen4x8 兼容的詳細信息,請查看第 213 頁。所提供的鏈路寬度可能取決於所提供的收發器計數和封裝管腳。

- 單根 IO 虛擬化 (SR-IOV) 所需的 4 個物理函數和 252 個虛擬函數,以便共享 IO 資源。

- 更多的標簽 (256),以支持可實現整體係統性能提升的更多請求。

- 集成的 MSI-X 表

此外,AMD 還提供高性能 DMA 和橋接器解決方案作為軟 IP:

- AMD QDMA IP 子係統是我們領先的 PCIe DMA 解決方案。QDMA 支持具有可擴展隊列的多個物理和虛擬功能的 SR-IOV。此外,QDMA 還提供了 AXI Bridge 的功能。如需了解更多詳情,請參見现金网博e百 指南 PG302。

- AMD XDMA IP 子係統是麵向 PCIe 的傳統 DMA 解決方案,被客戶廣泛使用。此外,XDMA 還提供了 AXI Bridge 的功能。查看现金网博e百 指南 PG195 ,了解更多詳情。

為了得到實現完全定製解決方案的終極自由度,AMD 還為 PCI Express 提供了一個軟 IP 核 PHY,這可幫助設計人員將其自己的 PCI Express 控製器連接至所提供的收發器。

支持的现金网博e百 與技術

PCI Express 的高速串行收發器

AMD 為 PCI Express 提供的評估套件

UltraScale 解決方案

AMD 20 nm UltraScale™ 器件集成當今數據中心、通信和嵌入式應用所需的大量重要 PCI Express® 功能。

該 PCI Express 的集成塊 IP 在芯片中硬化,支持:

- 原生 Gen3x8* 集成型 PCIe 模塊

- PCIe 請求的 64 個標簽

- 多向量 MSI(達 32 個向量)和 MSI-X

- 如需了解更多詳情,請查看{现金网博e百 指南 PG156。

此外,AMD 還提供高性能 DMA 和橋接器解決方案作為軟 IP:

- AMD XDMA IP 子係統是量產 PCIe DMA 解決方案,被客戶廣泛使用。查看现金网博e百 指南 PG195 ,了解更多詳情。

- AMD 提供一個映射至 PCI Express Bridge IP 的量產 AXI 內存。有關更多信息,請參見 现金网博e百 指南 PG194。

* 如需了解所支持的特定鏈路寬度和速度,請查看所需 IP 的適用现金网博e百 指南(PG156、 PG195 或PG194)

支持的现金网博e百 與技術

PCI Express 的高速串行收發器

7 係列解決方案

AMD 28 nm 7 係列器件集成當今數據中心、通信和嵌入式應用所需的大量重要 PCI Express® 功能。

該 PCI Express 的集成塊 IP 在芯片中硬化,支持:

- 原生 Gen3x8* 集成型 PCIe 模塊

- 64 位和 128 位數據位寬

- 如需了解更多詳情,請查看现金网博e百 指南PG054。

此外,AMD 還提供高性能 DMA 和橋接器解決方案作為軟 IP:

- AMD XDMA IP 子係統是量產 PCIe DMA 解決方案,被客戶廣泛使用。查看现金网博e百 指南 PG195 ,了解更多詳情。

- AMD 提供一個映射至 PCI Express Gen2 IP 的量產 AXI 內存。如需了解更多詳情,請查看 现金网博e百 指南 PG055。

* 如需了解所支持的特定鏈路寬度和速度,請查看所需 IP 的適用现金网博e百 指南(PG054、PG055 或 PG195)