DSP 解決方案

- 技術解決方案

- DSP

憑借其固有的靈活性,AMD 自適應 SoC 和 FPGA 是高性能或多通道數字信號處理 (DSP) 應用的理想選擇,這些應用可充分利用硬件的並行性。AMD 自適應 SoC 和 FPGA 將這種處理帶寬與各種綜合解決方案相結合,其中包括為硬件設計人員、軟件開發人員和係統架構師提供的簡單易用的設計工具。

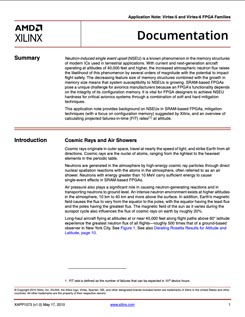

硬件並行性

一個標準 Von Neumann DSP 架構需要 256 個周期才能完成一個 256 個抽頭的 FIR 濾波器,而自適應 Soc 和 FPGA 隻需要一個時鍾周期便可達到相同的效果。

大規模並行計算可轉化為極高水平的 DSP 性能:

- 49.5 TeraMAC 的定點性能(8 位)

- 單精度浮點的 23.1 萬億次浮點運算

綜合 DSP 解決方案

AMD DSP 解決方案包含芯片、IP、參考設計、開發板、工具、文件和培訓,可實現廣泛市場的各種應用,包括(但不限於)無線通信、數據中心以及航空航天及軍用现金网博e百 。

綜合開發流程

針對不同的使用模型及不同等級的設計抽象提供各種工具流程:

硬件設計者可以在以下方麵進行設計:

- Vivado™ Design Suite 實現的 RTL 及係統級設計

- C/C++

- MATLAB® 和 Simulink® 環境使用 Vitis™ Model Composer

軟件真人百家乐游戏开户 ( 習慣於使用 C/C++ 進行開發) 可使用以下工具開發:

係統架構師可快速評估新算法,實現:

- 用於在 MATLAB 或 Simulink 環境中進行係統建模的 Vitis Model Composer

- 用於采用 C 或 C++ 執行算法探索的 Vitis HLS

有了 AMD 自適應 SoC 和 FPGA,設計人員可使用多種流程,根據設計方法和抽象級別部署其 DSP 應用。

AMD FPGA 和自適應 SoC 基於 ASIC 類架構,在Versal™ Premium 係列中將每秒數百千兆位 I/O 帶寬與超過 49 TeraMAC 的定點 DSP 性能相結合。在最新一代 AMD FPGA 中,AMD DSP slice 及其並行性是實現 DSP 性能的關鍵。

DSP Slice 架構

Versal 器件 slice 中的 DSP58 是 AMD 架構中的第 6 代 DSP slice。

這款專用的 DSP 處理模塊在全麵定製的芯片中實現,這種芯片可實現領先的功耗性能比,從而可高效實現乘法累加器 (MACC)、乘法加法器 (MADD) 或複雜乘法等普及型 DSP 功能。

此外,Slice 也可提供執行各種邏輯運算的功能,如 AND、OR 和 XOR 運算。

Versal 器件 DSP58 架構建立在 UltraScale™ FPGA DSP48E2 的成功基礎之上,具有更高的增強性能:

- 更寬的乘法器(27 x 24 位)

- 單精度浮點乘法器

- 18x18 複數乘法使用兩個背靠背的 DSP

- INT8 向量點積模式

這些增強功能有助於 DSP 關鍵應用在進入 FPGA 架構之前在 DSP48E2 slice 內執行更多的計算,最終可節省資源及電源。

DSP48E2 (UltraScale) 與 DSP58 (Versal) Slice 特性

| 功能 | UltraScale | Versal |

|---|---|---|

| DSP 模塊/Slice 類型 | DSP48E2 | DSP58 |

| 多重 Add/Sub/Acc 運算 |  |

|

| 乘法器和 MACC | 27x18 | 27x24 |

| 開方: [(A 或 B)+/- D]2 |  |

|

| WMUX 反饋超高效複雜乘法 CMACC | 3 x DSP48E2 | 2 x DSP58 |

| SIMD 支持 |  |

|

| 集成型模式檢測電路 |  |

|

| 集成型邏輯單元 |  |

|

| 寬複用功能 | 48 位 | 58 位 |

| Wide XOR | 96 位 | 116 位 |

| Single Precision Floating Point Multiplier |  |

|

| 可選 96 位輸出 |  |

|

| 級聯布線 |  |

|

| 流水線寄存器 |  |

|

| D 預加法器 |  |

|

| 序列複雜乘法、AB 動態訪問 |  |

|

| 改進的 AB 寄存器流水線平衡 |  |

|

工具與流程

AMD 可根據您的設計首選項為您提供支持 RTL、C/C++ 及模型設計入口的工具。這種設計流程靈活性加上大量 DSP IP 目錄,可實現對 AMD 工具及器件的更便捷應用。

訪問工具、庫和框架,了解更多詳情。

DSP 性能指標

下表是 7 係列、UltraScale 和 UltraScale+ 係列的部分重要 DSP 性能指標。 如需了解 SoC 器件性能,敬請查看軟件開發人員部分。

| Kintex UltraScale | Kintex UltraScale+ | Virtex UltraScale | Virtex UltraScale+ | Versal AI Core | Versal AI Edge | Versal AI Prime | Versal AI Premium | |

|---|---|---|---|---|---|---|---|---|

| 係統邏輯單元 (K) | 318–1,451 | 356–1,143 | 783–5,541 | 862–3,780 | 540 - 1,968 | 44 - 1,139 | 329 - 2,233 | 833 - 7,352 |

| DSP slice | 768–5,520 | 1,368–3,528 | 600–2,880 | 2,280–12,288 | 928 - 1,968 | 90 - 1,312 | 464 - 3,984 | 1,140 - 14,352 |

| 27x18 乘法器 | 768–5,520 | 1,368–3,528 | 600–2,880 | 2,280–12,288 | 928 - 1,968 | 90 - 1,312 | 464 - 3,984 | 1,140 - 14,352 |

| INT8 GOPs (1) | 1,774–14,315 | 4,263–11,000 | 1,554–7,469 | 7,108–38,318 | 6,403 - 13,579 | 62 - 9,052 | 3,201 - 27,489 | 7,866 - 99,029 |

| INT16 GOPs | 1,014–8,180 | 2,436–6,286 | 888–4,268 | 4,062–21,896 | 2,134 - 4,526 | 21 - 3,017 | 1,067 - 9,163 | 2,622 - 33,010 |

| 複雜的 INT18 GOP | 676 - 5,453 | 1,624 - 4,191 | 592 - 2,845 | 2708 - 14,597 | 913 - 1,937 | 8 - 1,291 | 456 - 3,920 | 1,122 - 14,122 |

| 單精度浮點 (GFLOP) (2) | 320–2,685 | 800–1,673 | 294–1,411 | 1,354–7,299 | 1,494 - 3,168 | 14 - 2112 | 747 - 6,414 | 1,835 - 23,107 |

注:

- 請參考 WP486 – “利用 AMD 器件的 INT8 優化開展深度學習”

- 單精度浮點性能在 Ultrascale+ 中使用支持 3 個 DSP slice 的浮點運算內核

我們推出了軟件開發環境及一係列功能強的常見綜合工具、庫以及軟件開發人員可用來便捷鎖定 AMD FPGA 及 SoC 目標的方法。 支持高層次抽象環境Vitis™ 統一軟件平台。我們可針對 C、C++ 和/或 OpenCL 開發提供類似於 GPU 的熟悉嵌入式應用開發及運行時體驗。

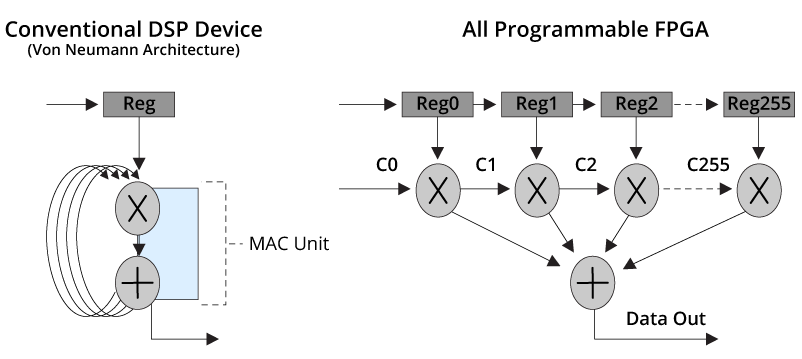

AMD MPSoC 和 Versal 器件

Zynq™ UltraScale+™ MPSoC 和 Versal 架構結合強大的處理係統 (PS),在單個器件中完美整合 ARM® Cortex® 處理器和用戶可編程邏輯 (PL)。

支持加速的應用剖析

Vitis 統一軟件平台不僅提供分析給定應用的功能,而且還允許創建硬件加速器,以便在可編程邏輯 (PL) 中更高效地運行,其中可利用 FPGA 的靈活性和並行性提供巨大的性能改進。此外,這還可實現必要時可在處理係統 (PS) 中並行運行的其它應用功能。

通過將 AMD FPGA 及自適應 SoC 定為目標,許多 DSP 及嵌入式應用都將實現效率的提升並為其應用降低功耗。

AMD SoC 器件的特性和 DSP 性能

下表是 AMD Zynq UltraScale+ MPSoC 係列和 Versal 器件的部分重要特性及 DSP 性能指標。 如欲了解非 SoC 器件性能,敬請訪問硬件設計人員部分。

| 處理係統 | Zynq 7000 SoC | Zynq UltraScale+ MPSoC |

|---|---|---|

| 應用 處理單元 (APU) |

|

|

| 實時 處理單元 (RPU) |

- |

|

| 多媒體處理 | - |

|

| 動態內存接口 | DDR3, DDR3L, DDR2, LPDDR2 | DDR4、LPDDR4、DDR3、DDR3L、LPDDR3、 |

| 高速外設 | USB 2.0、Gigabit Ethernet、SD/SDIO | PCIe® Gen2、USB3.0、SATA 3.1、 DisplayPort、Gigabit Ethernet、SD/SDIO |

| 安全 | RSA、AES、和 SHA, ARM TrustZone® | RSA、AES、和 SHA, ARM TrustZone |

| 最大 I/O 引腳數 | 128 | 214 |

| 可編程邏輯 | Zynq 7000 SoC | Zynq UltraScale+ MPSoC |

|---|---|---|

| 係統邏輯單元 (K) | 23–444 | 103–1,045 |

| 最大存儲器 (Mb) | 1.8–26.5 | 5.3–70.6 |

| 最大 I/O 引腳 | 100–362 | 252–668 |

| DSP Slice | 60–2,020 | 240–3,528 |

| 18x18 乘法器 | 60–2,020 | 240–3,528 |

| 定點性能 (GMACs) (1) | 42–1,313 | 213–3,143 |

| 定點性能 麵向對稱濾波器 (GMAC) (1) (2) | 84–2,626 | 426–6,286 |

| INT8 GOPs (1) (3) | 84–2,626 | 745–11,000 |

| INT16 GOPs (1) | 84–2,626 | 426–6,286 |

| 單精度浮點 (GFLOPs) (1) (4) | 23–716 | 142–1,673 |

| 單精度浮點 (GFLOPs) (1) (5) | 17–537 | 106–1,571 |

| 半精度浮點 (GFLOPs) (1) (6) | 34–1,074 | 212–3,142 |

注:

- 所有性能計算均基於 Zynq 7000 SoC 的 -2 速度級部件以及 Zynq UltraScale+ MPSoC 的 -3 速度級部件

- 為對稱濾波器使用預加法器,DSP 性能可提高 2 倍

- 請參考WP486 - “利用 AMD 器件的 INT8 優化開展深度學習” (不適用於 Zynq 器件)

- 使用支持 3 個 DSP slice 的浮點運算器內核實現單精度浮點性能

- 使用支持 4 個 DSP slice 的浮點運算器內核實現單精度浮點性能

- 使用支持 2 個 DSP slice 的浮點運算器內核實現半精度浮點性能

如欲了解有關 AMD SoC 及 MPSoC 的更多詳情,敬請訪問:

處理子係統中的 DSP

該處理係統 (PS) 可通過不同的 ARM 處理內核途徑提供各種 DSP 處理功能。

如欲進一步了解有關 ARM 的 DSP 功能,敬請訪問:

- Cortex-A 係列

- SIMD 和 高級 SIMD (NEON) 技術

- ARM 浮點架構

可在以下位置查看一些實用示例:

對於 Zynq UltraScale+ MPSoC,請查看:UG1211,了解使用 ARM NEON 指令集的 FFT 演示。

對於 Zynq 7000 SoC 而言,在將 Cortex-A9 和 ARM SIMD 確定為目標時,可在 Xilinx wiki 上獲得以下技術要點:

AMD 數據類型支持

AMD 為其器件提供極其靈活的數據類型支持。 AMD 工具原生支持不同精度的定點、浮點和整數,這些浮點運算是在 Floating Point Operator IP 核的支持下實現的。

與定點或整數實現方案相比,在 FPGA 上實現的浮點設計始終會導致消耗更多的資源及功率。 如果可能的話,轉化為定點解決方案,將帶來巨大的優勢:

- 更少的 FPGA 資源

- 功耗降低

- 成本降低

如需進一步了解有關將浮點轉換為定點數據類型的優勢,敬請閱讀 WP491。

基準測試

下表是一小部分算法以及使用 AMD 器件、特別是可編程邏輯 (PL) 中的架構加速設計可實現的性能提升。

| 算法 | CPU/GPU | Zynq UltraScale+ MPSoC | 優勢 |

|---|---|---|---|

| Stereo LocalBM @ 2K | ARM:每瓦 0.5 FPS nVidia:每瓦 3.5 FPS |

每瓦 146 FPS | 292x 42x |

| 光流法

(Lucas-Kanade) |

ARM:每瓦 0.1 FPS nVidia:每瓦 0.8 FPS |

每瓦 7.1 FPS | 9.3x |

| GoogleNet (Batch=1) |

ARM:0.1 Imgs/s/w nVidia:8.8 Imgs/s/w |

53 Imgs/s/w | 530x 6x |

注釋 1:ARM:四核 A53 以 1200MHz 的頻率運行在 Raspberry Pi 上

注釋 2:采用 Tegra X1 實現 Nvidia 基準

注釋 3:光流 (LK) — 窗口尺寸:11x1

| 算法 | CPU/DSP | Zynq 7000 | 優勢 |

|---|---|---|---|

| 正向投影 | ARM:每視圖 3 秒 | 每視圖 0.016 秒 | 188x |

| 運動檢測 | ARM: 0.7 FPS | 67 FPS | 90x |

| 噪聲降低 — Sobel | ARM: 1 FPS | 67 FPS | 60x |

| Canny 邊緣檢查 | ARM: 0.66 FPS | 40 FPS | 45x |

| 3D 圖像重建 | ARM: 75k | 8k | 9x |

| DPD | ARM: 506 ms | 31.3ms | 16x |

| FIR | TI DSP: 64020 ns | 1200 ns | 53x |

| FFT | TI DSP: 1036 ns | 128 ns | 8x |

注釋 1:將 ARM 作為目標時,Cortex-A9 內核隻用在 Zynq 器件上

注釋 2:使用 C66 DSP 內核完成 TI 基準

Vitis Model Composer for DSP 和高層次綜合等 AMD 高層次設計工具提供的抽象等級可幫助係統架構師及域專家快速評估最新算法並集中精力進行其設計的差異化部分開發。 完整的 AMD DSP 解決方案是這些設計工具、IP、參考設計、方法及電路板的完美整合,這些元素的結合能夠在盡可能最短的時間內獲得一項可行的生產設計。

Vitis Model Composer 是一款基於模型的設計工具,可利用 MATLAB 及 Simulink 開發環境以一小部分傳統 RTL 開發時間在可編程邏輯中定義、測試和實現生產質量級 DSP 算法。

該工具提供:

- 100 多個優化 DSP 模塊,許多都有 C 仿真模型,與 RTL 相比,仿真速度提高了 2 至 3 倍

- 高度集成 DSP 的 RTL、IP、Simulink、MATLAB 和 C/C++ 組件

- 位精確與周期精確的浮點、定點仿真

- 硬件協同仿真可加速仿真並可在可行硬件上驗證算法

- 從 Simulink 到打包 IP 或低層次 HDL 的自動代碼生成

- HDL 測試台的自動生成,包括測試矢量

了解有關 DSP Vivado 係統生成器的更多詳情:

高層次綜合 (HLS)

高層次綜合包括 Vitis 統一軟件平台,可移植 C、C++ 和 System C 算法規範能夠直接針對 AMD FPGA 和自適應 SoC,無需創建 RTL。就像從 C/C++ 到不同處理器架構提供編譯器一樣,HLS 編譯器可從 C/C++ 到 AMD FPGA & 自適應 SoC 提供相同的功能性。

了解更多有關高層次綜合的信息:

- Vitis 高層次綜合入門(視頻)

- Vitis 高層次綜合指南 (文檔)

工具

AMD 提供業界一流的工具,有助於在一款 AMD 自適應 SoC 和 FPGA 上以極低的功耗高效實現數字信號處理 (DSP) 應用。 無論您在使用 RTL、C/C++/SystemC 進行設計,還是在使用 Matlab/Simulink,以下 AMD 工具都可輕鬆簡化您的設計,縮短上市進程。

庫與框架

AMD 提供大量針對性能、資源利用及易用性進行優化的庫。

| 庫與框架 | 說明 |

應用 |

|---|---|---|

| GitHub 庫 | AMD 創建了各種 GitHub 庫,其可麵向包含 DSP 相關功能在內的大量應用提供各種實用示例。 | |

| Vitis 加速庫 | AMD 創建了一組廣泛的、性能優化的開源庫,這些庫提供了即開即用的加速功能,並且對現有應用實現最小化代碼更改或零更改。 | Vitis 庫 |

合作夥伴、開發板和套件

AMD 與其合作夥伴緊密協作,生產了各種工具及電路板,用於在大量不同市場領域簡化 DSP 應用對 AMD FPGA 及 SoC 的采用。

| 合作夥伴 | 說明 | 解決方案 |

|---|---|---|

| Avnet 以 DSP 為導向的開發套件及模塊 | 通過與 Xilinx、MathWorks 以及領先高速模擬供應商長期構建的協作,Avnet 可為嵌入式視覺、軟件定義無線電以及高性能電機控製提供以 DSP 為導向的開發套件和生成就緒型係統級模塊。 |

Avnet |

| Mathworks 計算軟件 | Mathworks MATLAB® 和 Simulink® 可顯著縮短自適應 SoC 和 FPGA 係統的開發時間,可幫助用戶:

|

Mathworks |

| 模擬器件附加電路板 | AD-FMCDAQ2-EBZ FMC 電路板是一款功能齊全的數據采集及信號綜合原型設計平台,支持簡單易行的工作,從而可加速終端係統信號處理開發。

|

Analog Devices |