# Versal ACAP CPM Mode for PCI Express

# **Product Guide**

Vivado Design Suite

PG346 (v1.0) July 24, 2020

# Table of Contents

| Chapter 1: Overview                                | 3  |

|----------------------------------------------------|----|

| Navigating Content by Design Process               |    |

| Introduction to the CPM4                           | 4  |

| Use Modes                                          | 9  |

| Charter 2. Draduct Charification                   |    |

| Chapter 2: Product Specification                   |    |

| Clocking<br>Resets                                 |    |

| Port Descriptions                                  |    |

| Register Space                                     |    |

| Register space                                     |    |

| Chapter 3: Design Flow Steps                       | 19 |

| Customizing and Generating the CIPS IP Core        |    |

|                                                    |    |

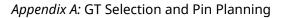

| Appendix A: GT Selection and Pin Planning          |    |

| CPM4 GT Selection                                  |    |

| CPM4 Additional Considerations                     |    |

| GT Locations                                       | 44 |

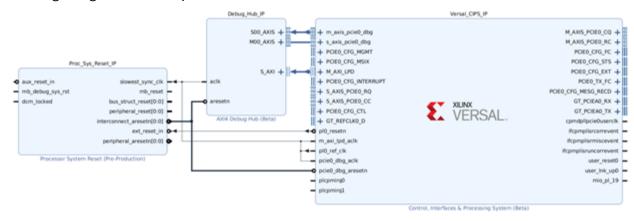

| Appendix B: PCIe Link Debug Enablement             | 48 |

| Enabling PCIe Link Debug                           |    |

| Connecting to PCIe Link Debug in Vivado            | 52 |

|                                                    |    |

| Appendix C: Debugging                              |    |

| Finding Help on Xilinx.com                         |    |

| Appendix D: Additional Resources and Legal Notices |    |

| Xilinx Resources                                   |    |

| Documentation Navigator and Design Hubs            |    |

| References                                         |    |

| Revision History                                   |    |

| Please Read: Important Legal Notices               |    |

|                                                    |    |

Chapter 1

# Overview

# Navigating Content by Design Process

Xilinx<sup>®</sup> documentation is organized around a set of standard design processes to help you find relevant content for your current development task. This document covers the following design processes:

- **System and Solution Planning:** Identifying the components, performance, I/O, and data transfer requirements at a system level. Includes application mapping for the solution to PS, PL, and AI Engine. Topics in this document that apply to this design process include:

- Introduction to the CPM4

- Use Modes

- **Embedded Software Development:** Creating the software platform from the hardware platform and developing the application code using the embedded CPU. Also covers XRT and Graph APIs. The topic in this document that applies to this design process include:

- Register Space

- Host Software Development: Developing the application code, accelerator development, including library, XRT, and Graph API use. The topic in this document that applies to this design process include:

- Register Space

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, subsystem functional simulation, and evaluating the Vivado<sup>®</sup> timing, resource use, and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Chapter 3: Design Flow Steps

- Appendix A: GT Selection and Pin Planning

- Appendix B: PCIe Link Debug Enablement

# **Introduction to the CPM4**

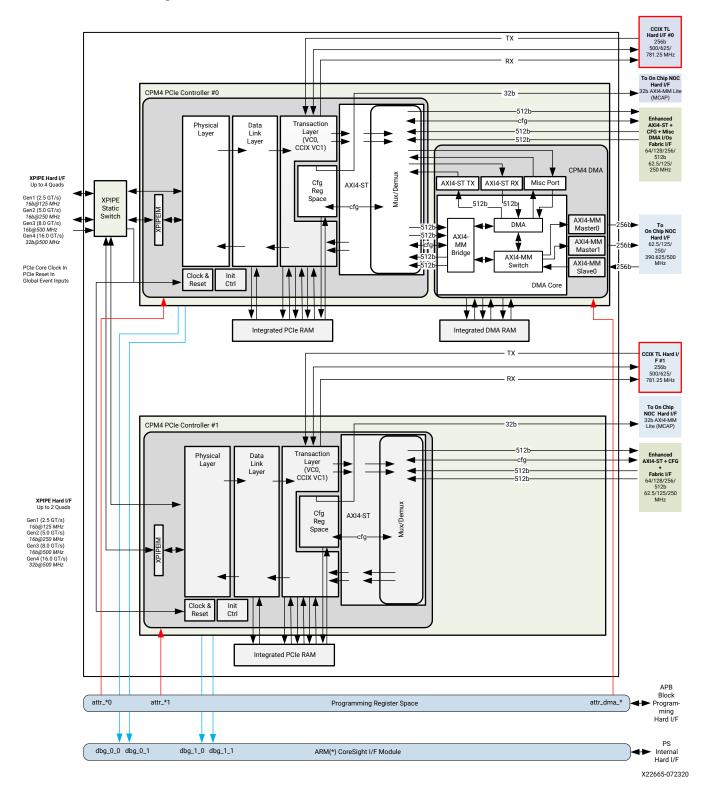

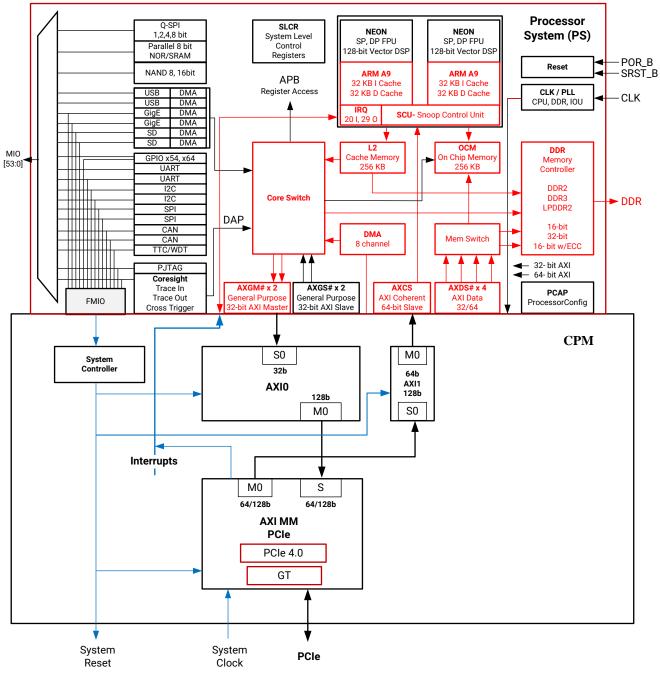

The integrated block for PCIe Rev. 4.0 with DMA and CCIX Rev. 1.0 (CPM4) consists of two PCIe controllers, DMA features, CCIX features, and network on chip (NoC) integration. The Versal<sup>™</sup> ACAP CPM Mode for PCI Express enables direct access to the two high-performance, independently customizable PCIe controllers. The CPM4 uses up to 16 Versal device GTY channels over the XPIPE. Application designs can also interface to the CPM4 with soft logic and clocking resources in the programmable logic. All feature references are applicable to both instances of CPM4 PCIe controllers, with the following exceptions:

- CPM4 PCIe controller #0 supports up to x16 operation, and CPM4 PCIe controller #1 supports up to x8 operation.

- CPM4 PCIe controller #1 with up to x8 support is available only when CPM4 PCIe controller #0 is configured with 8 lanes or fewer.

- The CPM4 DMA features are supported only with CPM4 PCIe controller #0. For more information about CPM4 DMA features, see the Versal ACAP CPM DMA and Bridge Mode for PCI Express Product Guide (PG347).

#### Figure 1: CPM4 Sub-Block for PCIe Function (CPM4 PCIE)

The CPM4 PCIe controllers are designed to the PCI Express Base Specification Revision 4.0 and support the Gen 4 data rate (16 GT/s per lane). They also support the Gen1 (2.5 GT/s per lane), Gen2 (5 GT/s per lane) and Gen3 (8 GT/s per lane) data rates, and can interoperate with components that are compliant with all versions of the PCI Express Base Specification.

The CPM4 PCIe controllers are available through the Vivado IP catalog in the Vivado Integrated Design Environment (IDE). The combination of the CPM4 PCIe controllers, the GTY, and clocking implement all layers of the PCI Express protocol, and the configuration space and controller.

## **Protocol Layers**

The layers of the protocol are the AXI4-Stream layer, the transaction layer, the data link layer and the physical layer, and they are described below.

### AXI4-Stream Layer

The AXI4-Stream layer implements Xilinx-specific requirements. In the transmit or outbound direction, the AXI4 layer interfaces the transaction layer with two AXI4-Stream interfaces. In the receive or inbound direction, the transaction layer output is forwarded to two AXI4-Stream interfaces. Application designs can attach to the AXI4-Stream interfaces, exchange information with the Versal<sup>™</sup> ACAP CPM Mode for PCI Express encoded as a Xilinx-specific streaming protocol implementation, and run on top of the industry standard AXI4-Stream interface. The CPM4 PCIe controllers support management of up to 256 (extended tag) or 1024 (scaled tag) outstanding customer initiated read requests, as part of the streaming protocol. The AXI4-Stream layer supports:

- Reception and transmission of address translation services (ATS) invalid requests, ATS invalid completions, ATS page requests and ATS PRG response message TLPs, which enable ATS to be implemented in the fabric logic.

- AXI4-Stream interface widths of 64 bits, 128 bits, 256 bits and 512 bits.

### **Transaction Layer**

The transaction layer is the upper layer of the PCI Express architecture, and its primary function is to accept, buffer, and forward transaction layer packets (TLPs). TLPs communicate information with the use of memory, I/O, configuration, and message transactions. To maximize the efficiency of communication between devices, the transaction layer enforces PCI-compliant transaction ordering rules and supports relaxed ordering (RO) of received transactions. The transaction layer also manages TLP buffer space through credit-based flow control. The transaction layer implements built-in tag management for transmitted non-posted transactions. It also implements cut-through forwarding of transactions in the transmit (or outbound) direction.

### CCIX Transaction Layer

The Cache Coherent Interconnect for Accelerators (CCIX) transaction layer requirements are implemented by the optional virtual channel 1 (VC1) in the design. Note that VC1 storage is in addition to the PCI Express-compliant virtual channel 0 (VC0) storage. The CCIX transaction layer interfaces with the CCIX protocol layer is implemented externally to the PCIe ports over the CCIX transaction layer (ARM CXS) hard interface. For more information, see the *Versal ACAP CPM CCIX Architecture Manual* (AM016).

### Data Link Layer

The data link layer acts as an intermediate stage between the transaction layer and the physical layer. Its primary responsibility is to provide a reliable mechanism for the exchange of information between two components on a link. This includes data exchange (TLPs), error detection and recovery, initialization services and the generation and consumption of data link layer packets (DLLPs). DLLPs are used to transfer information between data link layers of two directly connected components on the link. DLLPs convey information, such as power management, flow control, and TLP acknowledgments. The data link layer supports 32 kilobyte replay buffers and the feature DLLP.

### Physical Layer

The physical layer interfaces the data link layer with signaling technology for link data interchange, and is subdivided into the logical sub-block and the electrical sub-block.

- The logical sub-block frames and de-frames TLPs and DLLPs. It also implements the link training and status state machine (LTSSM), which handles link initialization, training, and maintenance. Scrambling and descrambling of data (for Gen1/Gen2/Gen3/Gen4 operation) is also performed in this sub-block.

- The electrical sub-block defines the input and output buffer characteristics that interface the device to the PCIe link. The physical layer also supports lane reversal (for multi-lane designs) and lane polarity inversion, as required by the PCI Express Base Specification 4.0 (http://www.pcisig.com/specifications).

Data exchange with the other components on the link occurs over the serial lines of one or more gigabit transceivers (GTs), which expose parallel interfaces at lower clock frequencies to the PCIe controller. For Gen1, Gen2, Gen3 and Gen4 operation, the physical layer is up-configuration capable in the downstream port mode only.

# Standards

The CPM4 block adheres to the following standards:

PCI Express Base Specification 4.0 Version 1.0, and Errata updates (available at http://pcisig.com/specifications).

• Cache Coherent Interconnect for Accelerators (CCIX) Transport Specification 1.0 (available at http://www.ccixconsortium.com).

### Features

- Support for the following PCI Express architecture components:

- 。 PCI Express Endpoint, Legacy Endpoint

- 。 Root Port

- Switch Upstream and Downstream Ports

- x1, x2, x4, x8 or x16 link widths

- Gen1, Gen2, Gen3 or Gen4 link speeds

- CCIX support in PCI Express and EDR PHY Modes

- PCI Express support for Gen4x4, and Gen4x8

- Advanced Error Reporting (AER) and End-to-End CRC (ECRC)

- Two PCI Express virtual channels

- One PCI Express compliant virtual channel, eight traffic classes

- One CCIX compliant virtual channel

- Support for multiple functions and Single-Root IO Virtualization (SR-IOV)

- Up to four physical functions

- Up to 252 virtual functions

- Built-in lane reversal and receiver lane-lane de-skew

- 3 x 64-bit or 6 x 32-bit Base Address Registers (BARs) that are fully configurable

- Expansion ROM BAR supported

- All Interrupt types are supported:

- 。 INTx

- 32 multi-vector MSI capability

- MSI-X capability with up to 2048 vectors with optional built-in vector tables

- Features that enable high-performance applications include:

- AXI4-Stream TLP Straddle on Requester Completion Interface

- 。 Address Translation Services (ATS) and Page Request Interface (PRI) Messaging

- Atomic Operation Transactions Support

- Transaction Tag Scaling as Completer

- Flow Control Scaling

# **Use Modes**

All design use modes support Endpoint, Legacy Endpoint, and Root Port configurations.

## **PCI Express Endpoint Use Modes**

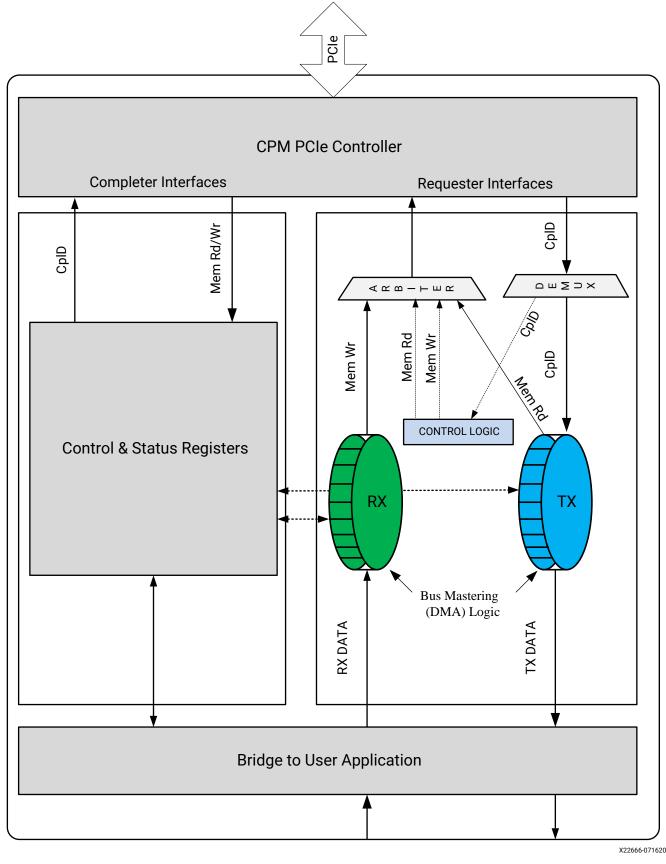

### **Illustrative Example of Basic Bus Mastering Endpoint**

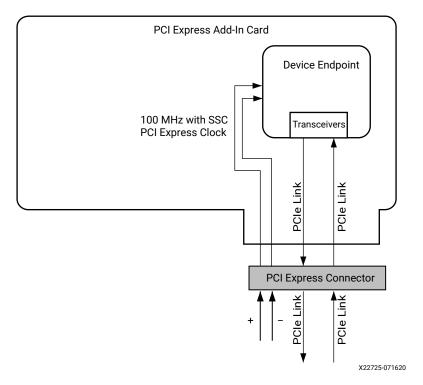

By far the most common use of the Versal<sup>™</sup> ACAP CPM Mode for PCI Express is to construct a bus mastering Endpoint using a CPM PCIe controller. This use model is applicable to most applications that interface the Endpoint port on the ACAP (on an add-in card) to a root complex or that switch ASSP downstream port through a PCI Express connector. The following figure shows a block diagram of the bus mastering Endpoint use case.

#### Figure 2: Basic PCI Express Bus Mastering Endpoint Use Case

PG346 (v1.0) July 24, 2020 CPM Mode for PCI Express

Send Feedback

www.xilinx.com 10

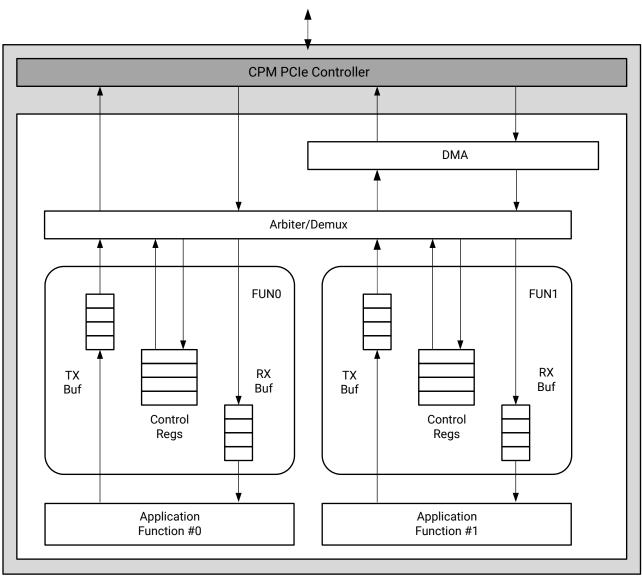

#### **PCI Express Two Function Endpoint**

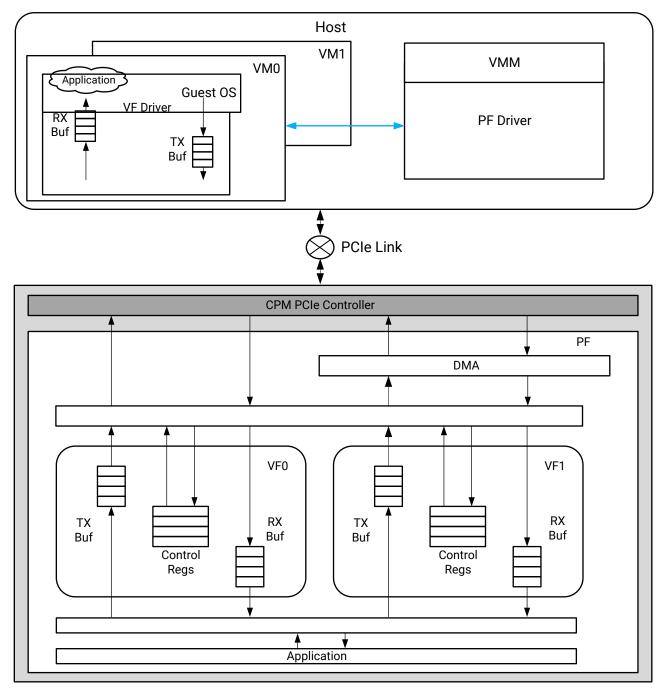

The following figure shows the architecture of a two-function Endpoint design. The CPM PCIe Controller is configured to enable two built-in function configuration spaces. This use case enables the application device driver to access and control two distinct applications independently. The user logic implements the DMA, control registers and applications.

X22667-071620

#### PCI Express Endpoint with SR-IOV

The following figure shows the CPM PCIe Controller configured as a SR-IOV capable Endpoint, interfacing with the user design. This use case addresses requirements for up to four physical and 252 virtual functions, and minimizes the soft logic requirement to implement an SR-IOV Endpoint.

X22668-071620

#### PCI Express Endpoint with AXI4 Memory Mapped Interface

This use case describes a PCI Express Endpoint functional unit that implements AXI4 Memory Mapped (AXI-MM) interfaces. This functional block implements a soft logic bridge between the native AXI4-Stream interface on the CPM PCIe controller and AXI4 Memory Mapped interconnect.

#### PCI Express Endpoint Using Staged Configuration Flow

This use case addresses the ability to configure the ACAP and bring up the CPM block in less than 100 ms after power to the ACAP is stable. This will be accomplished through a staged configuration flow.

#### PCI Express Endpoint Using Customizable Tandem Design

This use case addresses the ability to initially load fully configurable PCI Express protocol solution from a small external ROM, so as to meet the 100 ms configuration requirement. A PCIe link is formed with a Root Complex or Switch component, which is subsequently used to download the design that configures the rest of the ACAP. In this case the PCIe link is used by the user application. A light weight staged configuration flow is used.

## **PCI Express Root Port Use Mode**

#### **Basic PCI Express Root Complex Use Case**

The following figure shows a PCI Express Root Complex in the simplest form consisting of a PCI Express Root Port to an AXI4 memory mapped bridge interfaced with the interconnect. The interconnect consists of an Arm<sup>®</sup>-based processor system (PS) containing most of the critical blocks such as CPU, memory controller and other important peripherals. One of the goals of this use case is to minimize ACAP soft logic requirements.

Figure 5: Basic PCI Express Root Complex Use Case

X22670-051319

Send Feedback

# Chapter 2

# **Product Specification**

# Clocking

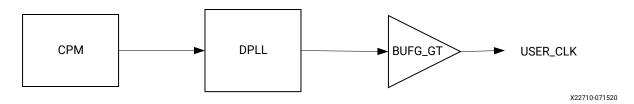

The Versal<sup>™</sup> ACAP CPM Mode for PCI Express<sup>®</sup> requires a 100, 125, or 250 MHz reference clock input. The following figure shows the clocking architecture. The user\_clk clock is available for use in the fabric logic.

### Figure 6: USER\_CLK Clocking Architecture

All user interface signals are timed with respect to the same clock  $(user_clk)$  which can have a frequency of 62.5, 125, or 250 MHz depending on the configured link speed and width.

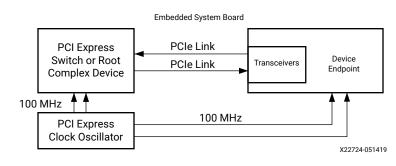

Each link partner device shares the same reference clock source. The following figures show a system using a 100 MHz reference clock. Even if the device is part of an embedded system, if the system uses commercial PCI Express root complexes or switches along with typical motherboard clocking schemes, synchronous clocking should still be used.

*Note*: The following figures are high-level representations of the board layout. Ensure that coupling, termination, and details are correct when laying out a board.

### Figure 7: Embedded System Using 100 MHz Reference Clock

Send Feedback

### Figure 8: Open System Add-In Card Using 100 MHz Reference Clock

## Resets

The fundamental resets for the CPM PCIe controllers and associated GTs are perst0n and perst1n. The resets are driven by the I/O inside the PS. In addition, there is a power-on-reset for CPM driven by the platform management controller (PMC). When both PS and the power-on reset from PMC are released, CPM PCIe controllers and the associated GTs will come out of reset.

After the reset is released, the core attempts to link train and resumes normal operation.

In addition, there is a user\_reset given from the CPM PCIe controller to the user design present in the fabric logic. Whenever the CMP PCIe block goes through a reset, or there is a link down, the CPM PCIe controller issues a user\_reset to the user design in the programmable logic (PL) region. After the PCIe link is up, user\_reset is released for the user design to come out of reset.

# **Port Descriptions**

The interfaces and ports of the Versal<sup>™</sup> ACAP CPM Mode for PCIe are similar to those described in the Versal ACAP Integrated Block for PCI Express LogiCORE IP Product Guide (PG343), except that signal names used for this solution begin with the letters *ifcpm*. Detailed information will be provided in a future release.

# **Register Space**

The configuration space is a register space defined by the PCI Express Base Specification 4.0 (http://www.pcisig.com/specifications). The Versal<sup>™</sup> ACAP CPM Mode for PCIe supports Xilinx proprietary read/write configuration interfaces into this register space, and supports up to four Physical Functions (PFs) and 252 Virtual Functions (VFs).

The PCI configuration space consists of the following primary parts.

### Legacy PCI v4.0 Type 0/1 Configuration Space Header

- Type 0 Configuration Space Header supported for Endpoint configuration

- Type 1 Configuration Space Header supported for Root, Switch Port configuration

#### **Legacy Extended Capability Items**

- PCIe Capability

- Power Management Capability

- Message Signaled Interrupt (MSI) Capability

- MSI-X Capability

- Legacy Extend Capabilities

#### **PCIe Extended Capabilities**

- Advanced Error Reporting Capability

- Function Level Reset

- ASPM L1 Support

- ASPM LOs Support (supported in Gen1 and Gen2 configurations only)

- Device Serial Number Capability

- Virtual Channel Capability

- ARI Capability (optional)

- SR-IOV Extended Capability Structure

- Configuration Space Extend Capabilities

- Address Translation Services (ATS)

- Page Request Interface (PRI)

- Feature DLLP

- CCIX Transport DVSEC through configuration space extension

- CCIX Protocol DVSEC through configuration space extension

- Transaction Tag Scaling as Requester and Completer

- Flow Control Scaling

- MCAP Interface for Staged Configuration and Dynamic Function eXchange per PCI Express port

# Chapter 3

# **Design Flow Steps**

This section describes customizing and generating the Versal<sup>™</sup> ACAP CPM Mode for PCIe, constraining the Versal<sup>™</sup> ACAP CPM Mode for PCIe, and the simulation, synthesis, and implementation steps that are specific to this IP Versal<sup>™</sup> ACAP CPM Mode for PCIe. More detailed information about the standard Vivado<sup>®</sup> design flows and the IP integrator can be found in the following Vivado Design Suite user guides:

- Vivado Design Suite User Guide: Designing IP Subsystems using IP Integrator (UG994)

- Vivado Design Suite User Guide: Designing with IP (UG896)

- Vivado Design Suite User Guide: Getting Started (UG910)

- Vivado Design Suite User Guide: Logic Simulation (UG900)

# **Customizing and Generating the CIPS IP Core**

This section includes information about using the Vivado<sup>®</sup> Design Suite to customize and generate the Control, Interfaces, and Processing System IP core. This section configures the CIPS IP core to access the CPM PCIe controllers directly. For extended information about the CIPS IP core, see the *Control Interface and Processing System IP Product Guide* (PG352).

## **Configuring the CIPS IP Core**

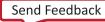

1. In the Vivado IDE, select **IP Integrator** → **Create Block Design** from the Flow Navigator, as shown in the following figure.

A popup dialog displays to create the block design.

- 2. Click **OK**. An empty block design diagram canvas opens in the IP integrator.

- 3. Right-click on the block design canvas and from the context menu select Add IP.

- 4. Search for cips.

| Search:                                 | Q- cips | $\otimes$ | (1 match) |  |  |  |  |  |

|-----------------------------------------|---------|-----------|-----------|--|--|--|--|--|

| Control, Interfaces & Processing System |         |           |           |  |  |  |  |  |

|                                         |         |           |           |  |  |  |  |  |

|                                         |         |           |           |  |  |  |  |  |

- 5. Double-click the **Control, Interface, and Processing System** IP core to customize it.

- In the Configuration Options pane, expand CPM, and click CPM Configuration.

The CPM Basic Configuration page displays.

| Control, Interfaces & Processing System                                                               | Control, Interfaces & Processing System (2.0)                                                                                            |   |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|--|--|--|

| Documentation P Location     Component Name versal_cips_0                                             |                                                                                                                                          |   |  |  |  |  |  |  |  |

| Configuration Options                                                                                 | CPM Basic Configuration                                                                                                                  | î |  |  |  |  |  |  |  |

| > Boot Mode<br>> Debug<br>> Ps-PMC<br>< CPM(CCIX PCIe Module)<br>CPM Configuration                    | PCIe0 Controller<br>PCIe0 Modes PCIE  Lane Width X16  PCIe1 Controller                                                                   | _ |  |  |  |  |  |  |  |

| PCIe0 Configuration<br>PCIe1 Configuration<br>CCIX(Cache Coherent Interconnect)<br>> Device Integrity | PCIel Modes None  Lane Width NONE  CPM Interfaces  CPM to NoC 0 CPM to NoC 1 NoC to CPM  GT OUTCLK setting  Select GT OUT clock TXOUTCLK |   |  |  |  |  |  |  |  |

- 7. Set the PCIe0 Modes to **PCIE**, and select the lane width. This setting enables the PCIe Port 0, and in a later step, you will be configuring the PCIe Port 0.

- 8. If you require the PCIe Port 1, set the PCIe1 Modes to PCIE, and select the lane width.

Available lane width combinations are:

| PCIe Port 0       | PCIe Port 1       |  |  |  |  |

|-------------------|-------------------|--|--|--|--|

| X1, X2, X4, or X8 | X1, X2, X4, or X8 |  |  |  |  |

| X16               | Not available     |  |  |  |  |

*Note*: There is no PCIe Port 1-only option available.

*Note*: PCle Port 1 is available only if the lane width of PCle Port 0 is less than or equal to X8.

*Note*: PCle Port 1 supports up to X8 when PCle Port 0 is configured up to X8.

- 9. Leave the Select GT OUT clock option set to **TXOUTCLK**.

- 10. In the Configuration Options pane, expand **PS-PMC**, and click **IO Configuration**.

The IO Configuration tab has a list of options to configure the external PCIe Reset options.

| ocumentation  🗎 IP Location          |                                                                       |              |        |                  |             |                  |            |     |  |  |  |

|--------------------------------------|-----------------------------------------------------------------------|--------------|--------|------------------|-------------|------------------|------------|-----|--|--|--|

| omponent Name versal_cips_0          |                                                                       |              |        |                  |             |                  |            |     |  |  |  |

| Configuration Options                | MIO Voltage Standar                                                   | rd           |        |                  |             |                  |            |     |  |  |  |

| Home                                 | Bank0 [MI0 0:25] Bank1 [MI0 26:51] Bank2 [MI0 0:25] Bank3 [Dedicated] |              |        |                  |             |                  |            |     |  |  |  |

| > Boot Mode                          |                                                                       |              |        |                  |             |                  |            |     |  |  |  |

| > Debug<br>< PS-PMC                  | LVCMOS1.8 🗸                                                           | VCMOS1.8 🗸   | LVCMO  | 51.8 🗸           | LVCMOS1.8 🗸 |                  |            |     |  |  |  |

| IO Configuration                     | Q ¥ ≑ ⊞                                                               |              |        |                  |             |                  |            |     |  |  |  |

| Clock Configuration                  | Search: Q-                                                            |              |        |                  | PMC Bank 0  |                  | PMC Bank 1 |     |  |  |  |

| PL-PS Interfaces                     |                                                                       |              |        | MIO 0            |             | MIO 26           |            | мю  |  |  |  |

| NoC                                  | Peripheral                                                            | I/O          | -      | MIO 1            |             | MI0 27           |            | MIO |  |  |  |

| Interrupts                           | ENET1 MDIO                                                            | PMC MIO 50 5 |        | MIO 2            |             | MIO 28           |            | MIO |  |  |  |

| > CPM(CCIX PCIe Module)              | TSU Clock Port                                                        | PS MIO 24    | ~      | MIO 3            |             | MIO 29           |            | MIO |  |  |  |

| <ul> <li>Device Integrity</li> </ul> |                                                                       |              |        | MIO 4            |             | MIO 30           |            | MIO |  |  |  |

|                                      | USB                                                                   | PMC MI0 13 2 | $\sim$ | MIO 5            |             | MIO 31           |            | MIO |  |  |  |

|                                      | ✓ ✓ PCle Reset                                                        |              |        | MIO 6            |             | MI0 32           |            | MIO |  |  |  |

|                                      | A0 End Point                                                          | PS MIO 18    |        | MIO 7            |             | MI0 33           |            | MIO |  |  |  |

|                                      |                                                                       | -            | ~      | MIO 8            |             | MI0 34           |            | MIO |  |  |  |

|                                      | A1 End Point                                                          | PS MIO 18    |        | MIO 9            |             | MI0 35           |            | MIO |  |  |  |

|                                      | A0 Root Port                                                          | PMC MIO 24   | - 11   | MIO 10           |             | MIO 36           |            | MIO |  |  |  |

|                                      | Al Root Port                                                          | PMC MIO 38   |        | MIO 11           |             | MIO 37           |            | MIO |  |  |  |

|                                      | V 🗌 UARTO                                                             | PS MIO 0 1   | ~      | MI0 12<br>MI0 13 |             | MIO 38<br>MIO 39 |            | MIO |  |  |  |

|                                      |                                                                       |              |        | MIO 13           |             | MIO 39           |            | MIO |  |  |  |

|                                      | RTS CTS                                                               | PS MIO 2 3   | $\sim$ | MIO 14           |             | MIO 40           |            | MIO |  |  |  |

|                                      | Baud Rate                                                             | 115200       | $\sim$ | MI0 16           |             | MI0 42           |            | MIO |  |  |  |

|                                      | V UART1                                                               | PMC MIO 4 5  | ~      | MIO 17           |             | MIO 43           |            | MIO |  |  |  |

|                                      |                                                                       |              |        | MIO 18           |             | MIO 44           |            | MIO |  |  |  |

|                                      | RTS CTS                                                               | PMC MIO 6 7  | ~      | MIO 19           |             | MIO 45           |            | MIO |  |  |  |

|                                      | Baud Rate                                                             | 115200       | $\sim$ | MIO 20           |             | MIO 46           |            | MIO |  |  |  |

|                                      | V SPIO                                                                | PMC MI0 12 1 | ~      | MIO 21           |             | MIO 47           |            | MIO |  |  |  |

|                                      | <b>—</b> 550                                                          | PMC MIO 15   | ~ ~    | MI0 22           |             | MI0 48           |            | MIO |  |  |  |

|                                      | 550                                                                   | FMC MIU 15   | V V    |                  |             |                  |            |     |  |  |  |

11. Select the PCle Reset option located in the Peripheral column.

Notice that the MIO pin selected in the PCIe reset is automatically connected to the PCIe reset I/O. In the figure below, MIO 38 is connected to the PCIe reset I/O.

- a. For PCIe Port 0 End Point configuration: Next to A0 End Point, select one of the available MIOs: PS MIO 18, PMC MIO 24, or PMC MIO 38. This selection should match the MIO that is connected to the PCIe reset I/O in the board schematic. In the figure below, PMC MIO 38 is selected to correspond to PCIe reset MIO 38.

- b. If PCIe Port 1 is enabled: Next to A1 End Point, select one of the available MIOs (PS MIO 19, PMC MIO 25, or PMC MIO 39) based on which MIO is connected to the PCIe reset I/O in the board schematic.

- 12. If the board will boot from serial NOR flash, select the a **QSPI** or **OSPI** option to enable programming of the flash on the board. Select the appropriate MIOs based on availability to match the board schematic.

To set up the boot device, see the *Versal ACAP Technical Reference Manual* (AM011). If a serial NOR flash boot device will be used, the correct options must be selected to enable the correct MIOs.

| Configuration Options   | MIO Voltage Standard | I               |                          |               |        |                  |        |                                       |

|-------------------------|----------------------|-----------------|--------------------------|---------------|--------|------------------|--------|---------------------------------------|

| Home                    | Bank0 [MIO 0:25] Ba  | nk1 [MIO 26:51] | Ban                      | k2 [MIO 0:25] | Bank3  | [Dedicated]      |        |                                       |

| > Boot Mode             | LVCMOS1.8 V LV       | смоз1.8 🗸       | IVC                      | M0S1.8 🗸      | LVCMO  | )S1.8 ¥          |        |                                       |

| > Debug                 | EVCHOSI.6 V          | CH031.6 +       | LVC                      | M031.0 V      | EVENIE | 51.0 +           |        |                                       |

| V PS-PMC                |                      |                 |                          |               |        |                  |        |                                       |

| IO Configuration        | Q. ≚ ≑ ≔             |                 |                          |               |        |                  |        |                                       |

| Clock Configuration     | Search: Q-           |                 |                          |               |        | PMC Bank 0       |        | PMC Bank 1                            |

| PL-PS Interfaces        | _                    |                 |                          |               | MIO 0  | OSPI: ospi_clk   | MIO 26 |                                       |

| NoC                     | Peripheral           | I/O             |                          | ^             | MIO 1  | OSPI: ospi io[0] | MIO 27 |                                       |

| Interrupts              | PMC-Domain           |                 |                          |               | MI0 2  | OSPI: ospi_io[1] | MIO 28 |                                       |

| > CPM(CCIX PCIe Module) | V 🗌 QSPI             | Single          | $\sim$                   |               | MIO 3  | OSPI: ospi_io[2] | MIO 29 |                                       |

| > Device Integrity      | QSPI Data Mode       | ×l              |                          |               | MIO 4  | OSPI: ospi_io[3] | MIO 30 |                                       |

|                         |                      |                 | ~                        |               | MI0 5  | OSPI: ospi_io[4] | MIO 31 |                                       |

|                         | 🗌 Loopback Clock     | PMC MI0 6       | $\sim$                   |               | MIO 6  | OSPI: ospi_ds    | MI0 32 |                                       |

|                         | OSPI                 | PMC MIO 0 11    |                          |               | MIO 7  | OSPI: ospi_io[5] | MI0 33 |                                       |

|                         | C 03H                |                 |                          |               | MIO 8  | OSPI: ospi_io[6] | MIO 34 |                                       |

|                         | ~ 🗆 SD0              | PMC MIO 0 11    | 0 2.0 ~<br>MC MIO 0 11 ~ |               | MIO 9  | OSPI: ospi_io[7] | MIO 35 |                                       |

|                         | Slot Type            | SD 2.0          |                          |               | MIO 10 | OSPI: ospi0_cs_b | MIO 36 |                                       |

|                         |                      |                 |                          |               | MIO 11 | OSPI: ospi1_cs_b | MIO 37 |                                       |

|                         | ~ 🗆 SD1              | PMC MIO 0 11    |                          |               | MI0 12 |                  | MIO 38 |                                       |

|                         | Slot Type            | SD 2.0          |                          |               | MI0 13 |                  | MIO 39 |                                       |

|                         |                      |                 |                          |               | MIO 14 |                  | MIO 40 |                                       |

|                         | I2C PMC              | PMC MI0 2 3     | ~                        |               | MI0 15 |                  | MIO 41 |                                       |

|                         | External Tamper Ev   | NONE            | ~                        |               | MIO 16 |                  | MI0 42 |                                       |

|                         | SMAP                 | 32 Bit          | ~                        |               | MIO 17 |                  | MIO 43 |                                       |

|                         |                      | 32 BIL          | ~                        |               | MIO 18 |                  | MIO 44 |                                       |

|                         | PMC_GPIO             |                 |                          |               | MIO 19 |                  | MIO 45 |                                       |

|                         | GPIO EMIO            | 0               |                          |               | MI0 20 |                  | MIO 46 |                                       |

|                         | ✓ PS-Domain          |                 |                          |               | MIO 21 |                  | MIO 47 |                                       |

|                         |                      |                 |                          |               | MI0 22 |                  | MIO 48 |                                       |

|                         | CAN-FD0              | PMC MIO 8 9     | ~                        |               | MI0 23 |                  | MIO 49 | · · · · · · · · · · · · · · · · · · · |

- 13. To enable additional I/O interfaces, such as UART, 12C, and USB IOs, select them here in a similar manner. See the *Versal ACAP Technical Reference Manual* (AM011) for more details on these interfaces.

- 14. In the Configuration Options pane, expand **CPM**, and click **PCIE 0 Configuration** to customize the PCIe Port 0 for the Versal ACAP CPM Mode for PCI Express core. It offers two modes: Basic, and Advanced. To select a mode, use the CPM Modes drop-down list on the first page of the Customize IP dialog box. The following sections explain the parameters available in each mode.

| Configuration Options                     | Basic Capabilities PF IDs PF BARs Legacy/MSI Cap MSI-X Cap Adv. Options Adv. Options-Capabilities Interfac |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Home<br>> PS-PMC                          | CPM Modes Advanced V                                                                                       |

| > OPERATIONAL INTEGRITY                   |                                                                                                            |

| V CPM                                     | PCIE0 Functional Mode PCIE V                                                                               |

| CPM Configuration<br>PCIe 0 Configuration | Port Type PCI Express Endpoint device 🗸                                                                    |

| PCIe1 Configuration<br>CCIX Configuration | Maximum Link Speed                                                                                         |

| HSDP                                      | ○ 2.5 GT/s ○ 5.0 GT/s ④ 8.0 GT/s ○ 16.0 GT/s                                                               |

|                                           | AXI-ST Interface Width         AXI-ST Interface Frequency (MHz)         250 MHz         V                  |

|                                           | Enable Client Tag                                                                                          |

|                                           | AXI-ST Alignment Mode                                                                                      |

|                                           | AXISTEN CQ/CC Alignment Mode DWORD Aligned 🗸                                                               |

|                                           | AXI-ST CQ/CC Frame Straddle                                                                                |

|                                           | AXISTEN RQ/RC Alignment Mode DWORD Aligned 🗸                                                               |

|                                           | ☑ AX0-ST RQ/RC Frame Straddle                                                                              |

|                                           | AXI-ST 512-bit RC 4TLP Straddle                                                                            |

|                                           | Reference Clock Frequency (MHz) 100 MHz 🗸                                                                  |

|                                           |                                                                                                            |

|                                           | <                                                                                                          |

|                                           | OK Cancel                                                                                                  |

15. If applicable, in the Configuration Options pane, expand **CPM**, and click **PCIE 1 Configuration** to customize PCIe Port 1.

### **Basic Mode Parameters**

The Basic mode parameters are explained in this section.

### Basic Tab

The following figure shows the initial customization page, used to set the Basic mode parameters.

#### Figure 9: Basic Tab

| ntrol, Interfaces &                    | Processing System (2.0)                                                        |           |  |  |  |  |  |  |  |

|----------------------------------------|--------------------------------------------------------------------------------|-----------|--|--|--|--|--|--|--|

| ocumentation 🛛 📄 IP Loc                | ation                                                                          |           |  |  |  |  |  |  |  |

| omponent Name versal_                  | cips_0                                                                         |           |  |  |  |  |  |  |  |

| Configuration Optio                    | Basic Capabilities PF IDs PF BARs Legacy/MSI Cap                               |           |  |  |  |  |  |  |  |

| Home<br>Boot Mode<br>Debug             | CPM Modes Basic V                                                              |           |  |  |  |  |  |  |  |

| PS-PMC                                 | PCIE0 Functional Mode PCIE                                                     |           |  |  |  |  |  |  |  |

| CPM(CCIX PCIe Modu<br>CPM Configuratio | Port Type PCI Express Endpoint device                                          |           |  |  |  |  |  |  |  |

| PCIe0 Configurat<br>PCIe1 Configurat   | Maximum Link Speed                                                             |           |  |  |  |  |  |  |  |

| CCIX(Cache Cohe<br>Device Integrity    | ○ 2.5 GT/s ○ 5.0 GT/s ④ 8.0 GT/s ○ 16.0 GT/s                                   |           |  |  |  |  |  |  |  |

|                                        | AXI-ST Interface                                                               |           |  |  |  |  |  |  |  |

|                                        | AXI-ST Interface Width (Bits) 512 V AXI-ST Interface Frequency (MHz) 250 MHz V |           |  |  |  |  |  |  |  |

|                                        | Enable Client Tag                                                              |           |  |  |  |  |  |  |  |

|                                        | AXI-ST Alignment Mode                                                          |           |  |  |  |  |  |  |  |

|                                        | AXISTEN CQ/CC Alignment Mode DWORD Aligned 🗸                                   |           |  |  |  |  |  |  |  |

|                                        | AXI-ST CQ/CC Frame Straddle                                                    |           |  |  |  |  |  |  |  |

|                                        | AXISTEN RQ/RC Alignment Mode DWORD Aligned 🗸                                   |           |  |  |  |  |  |  |  |

|                                        | AXI-ST RQ/RC Frame Straddle                                                    |           |  |  |  |  |  |  |  |

|                                        | ✓ AXI-ST 512-bit RC 4TLP Straddle                                              |           |  |  |  |  |  |  |  |

|                                        | Reference Clock Frequency (MHz) 100 MHz 🗸                                      |           |  |  |  |  |  |  |  |

|                                        |                                                                                |           |  |  |  |  |  |  |  |

| >                                      | <                                                                              |           |  |  |  |  |  |  |  |

|                                        |                                                                                |           |  |  |  |  |  |  |  |

|                                        |                                                                                | OK Cancel |  |  |  |  |  |  |  |

- **Component Name:** Base name of the output files generated for the core. The name must begin with a letter and can be composed of these characters: a to z, 0 to 9, and "\_."

- CPM Mode: Allows you to select the Basic or Advanced mode of the configuration of core.

- Port Type: Indicates the PCI Express logical device type.

- **Maximum Link Speed:** The core allows you to select the Maximum Link Speed supported by the device. Higher link speed cores are capable of training to a lower link speed if connected to a lower link speed capable device.

- **AXI-ST Interface Width:** The core allows you to select the Interface Width. The default interface width set in the Customize IP dialog box is the lowest possible interface width.

- AXI-ST Interface Frequency: Enables you to specify the AXI-ST Interface frequency.

- Enable Client Tag: Enables you to use the client tag.

- AXI-ST Alignment Mode: When a payload is present, there are two options for aligning the first byte of the payload with respect to the datapath. The options are provided to select the CQ/CC and RQ/RC interfaces.

- Enable AXI-ST Frame Straddle: The core provides an option to straddle packets on the requester completion interface when the interface width is 256 bits.

- AXI-ST CQ/CC Frame Straddle and AXI-ST RQ/RC Frame Straddle: When 512-bit AXI-ST interface width is selected AXI-ST frame Straddle is supported for CQ, CC, RQ and RC AXI-ST interfaces. Option to select CQ and CC AXI-ST frame straddle together and for RQ and RC interfaces

- **Reference Clock Frequency:** Selects the frequency of the reference clock provided on <code>sys\_clk</code>.

#### **Related Information**

Clocking

### **Capabilities Tab**

The Capabilites settings are explained in this section as shown in the following figure.

| Configuration Options                                    | Basic Capabilities PF IDs PF BARs SRIOV Config SRIOV PF BARs |                                                                                                                                        |

|----------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Home                                                     |                                                              |                                                                                                                                        |

| > Boot Mode                                              | Physical Functions                                           |                                                                                                                                        |

| > Debug                                                  | Total Physical Functions 4                                   |                                                                                                                                        |

| > PS-PMC                                                 |                                                              |                                                                                                                                        |

| CPM(CCIX PCIe Module)                                    | Device Capabilities Register PFx                             | Link Status Register                                                                                                                   |

| CPM Configuration                                        | PFx Max Payload Size 1024 bytes 🗸                            | Selects whether the device reference clock is provided by the connector<br>(Synchronous) or generated via an onboard PLL(Asynchronous) |

| PCIe0 Configuration                                      |                                                              | (Synchronous) or generated via an onboard PLL(Asynchronous)                                                                            |

| PCIe1 Configuration<br>CCIX(Cache Coherent Interconnect) | Extended Tag Field                                           | Enable Slot Clock Configuration                                                                                                        |

| > Device Integrity                                       |                                                              |                                                                                                                                        |

| > Device integrity                                       | SRIOV Capability                                             |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

|                                                          |                                                              |                                                                                                                                        |

- **Physical Functions:** Enables you to select the number of physical functions. The number of physical functions supported is 4.

- **PFx Max Payload Size:** This field indicates the maximum payload size that the device or function can support for TLPs. This is the value advertised to the system in the Device Capabilities Register.

- **Extended Tag Field:** This field indicates the maximum supported size of the Tag field as a Requester. The options are:

- When selected, 8-bit Tag field support (256 tags)

- When deselected, 5-bit Tag field support (32 tags)

- Enable Slot Clock Configuration: Enables the Slot Clock Configuration bit in the Link Status register. When you select this option, the link is synchronously clocked.

- **SRIOV Capabilities:** Enables Single Root Port I/O Virtualization (SR-IOV) capabilities. The integrated block implements extended Single Root Port I/O Virtualization PCIe. When this is enabled, SR-IOV is implemented on all the selected physical functions.

#### **Related Information**

Clocking

### PF IDs Tab

The following figure shows the Identity Settings parameters.

| PF - ID Initia |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Vendor ID                                                                                                                                                                            |                                                                                                                                                                              |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PF#            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Vendor ID                                                                                                                                                                            |                                                                                                                                                                              |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |