# Versal ACAP DMA and Bridge Subsystem for PCI Express

## **Product Guide**

Vivado Design Suite

PG344 (v1.0) May 20, 2022

Xilinx is creating an environment where employees, customers, and partners feel welcome and included. To that end, we're removing non-inclusive language from our products and related collateral. We've launched an internal initiative to remove language that could exclude people or reinforce historical biases, including terms embedded in our software and IPs. You may still find examples of non-inclusive language in our older products as we work to make these changes and align with evolving industry standards. Follow this <a href="link">link</a> for more information.

## **Table of Contents**

| Section I: Introduction to the DMA and Bridge Subsystems | 6  |

|----------------------------------------------------------|----|

| Modular IP Architecture                                  | 6  |

| QDMA Subsystem                                           | 7  |

| AXI Bridge Subsystem                                     | 7  |

| XDMA Subsystem                                           | 8  |

| Features of the DMA and Bridge Subsystem                 | 8  |

| QDMA Subsystem                                           | 9  |

| AXI Bridge Subsystem                                     | 9  |

| XDMA Subsystem                                           | 10 |

| Maximum Supported Link Rates and Widths                  | 10 |

| IP Facts                                                 | 11 |

| Chapter 1: Overview                                      | 12 |

| Navigating Content by Design Process                     |    |

| Unsupported Features                                     |    |

| Standards for the DMA and Bridge Subsystems              |    |

| Minimum Device Requirements                              |    |

| Licensing and Ordering                                   |    |

| Chapter 2: Designing with the Subsystem                  | 15 |

| Clocking                                                 |    |

| Resets                                                   |    |

| Section II: QDMA Subsystem for PL PCIE4 and PL PCIE5     | 18 |

| Overview                                                 |    |

| Modular IP Architecture                                  |    |

| Features                                                 |    |

| QDMA Architecture                                        |    |

| QDMA Subsystem Limitations                               |    |

| Applications                                             |    |

| Chapter 3: Product Specification                         | 39 |

| Performance and Resource Utilization                         | 39  |

|--------------------------------------------------------------|-----|

| QDMA Operations                                              | 41  |

| Port Descriptions                                            |     |

| Register Space                                               | 142 |

| Chapter 4: Design Flow Steps                                 | 155 |

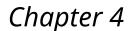

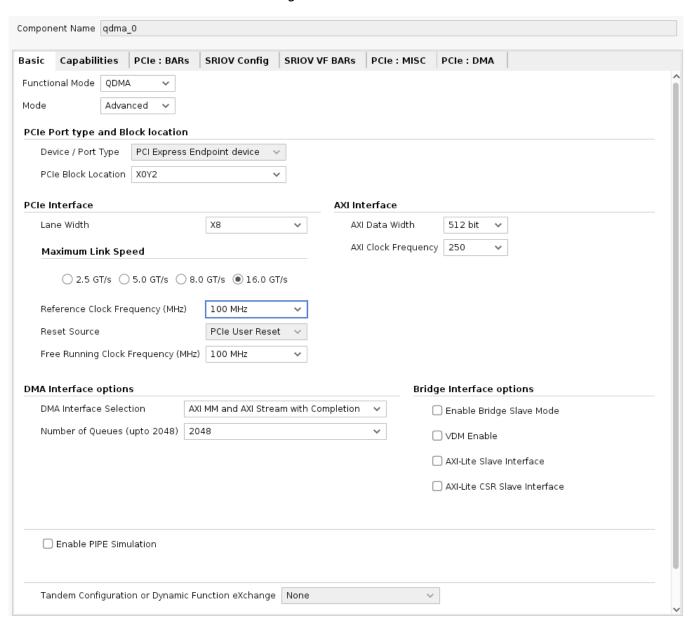

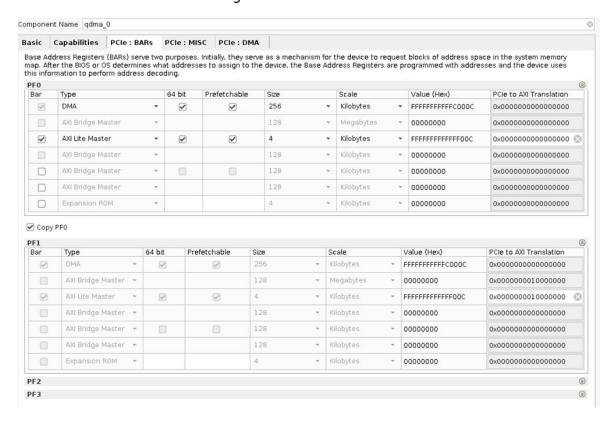

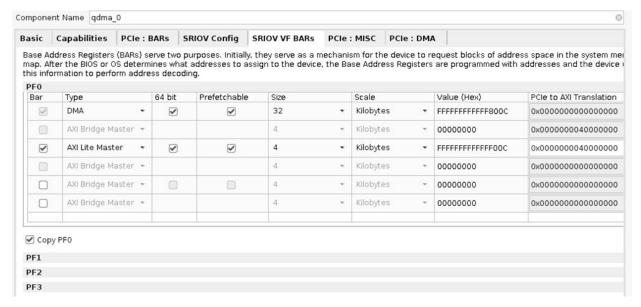

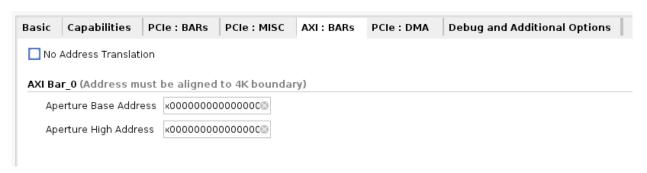

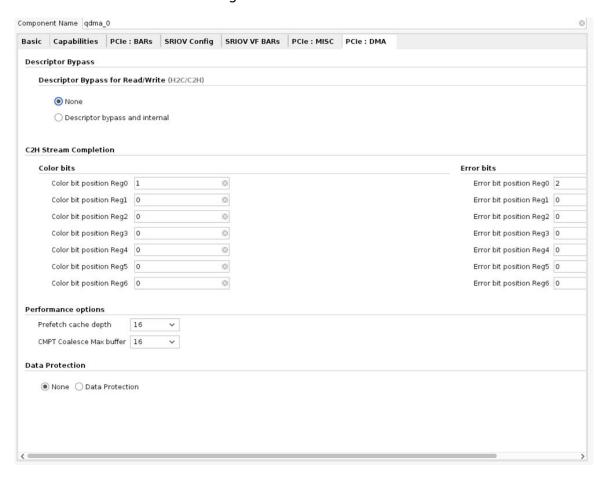

| Customizing and Generating the Subsystem                     | 155 |

| Constraining the Subsystem                                   | 168 |

| Simulation                                                   | 170 |

| Synthesis and Implementation                                 | 171 |

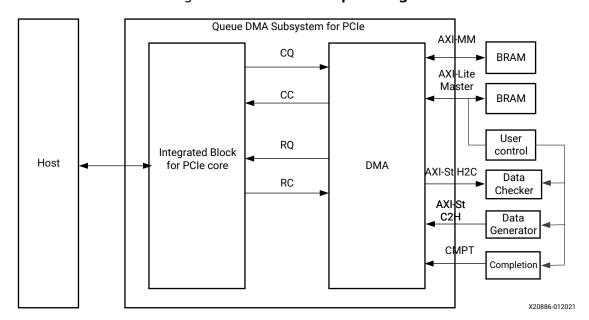

| Chapter 5: Example Design                                    | 172 |

| Available Example Designs                                    | 172 |

| Example Design Registers                                     | 177 |

| Customizing and Generating the Example Design                | 186 |

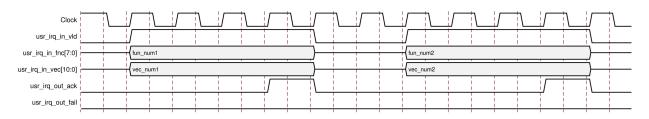

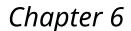

| Chapter 6: Test Bench                                        | 187 |

| Architecture                                                 | 188 |

| Scaled Simulation Timeouts                                   | 189 |

| Test Selection                                               | 189 |

| Waveform Dumping                                             | 190 |

| Output Logging                                               | 190 |

| Test Description                                             | 191 |

| Model Task List                                              | 191 |

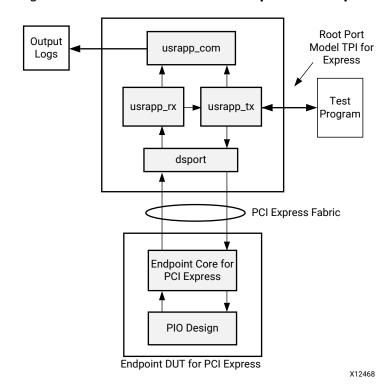

| Chapter 7: Application Software Development                  | 193 |

| Device Drivers                                               | 193 |

| Linux QDMA Software Architecture (PF/VF)                     | 194 |

| Using the Drivers                                            | 195 |

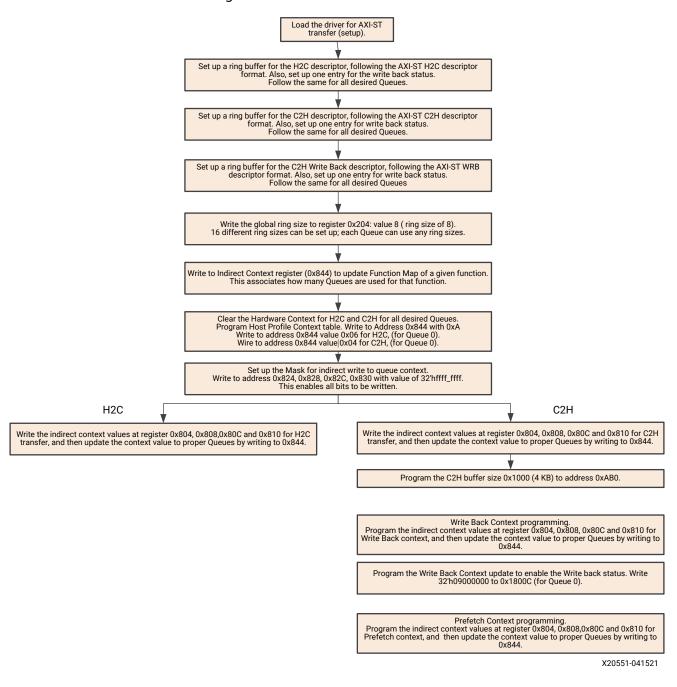

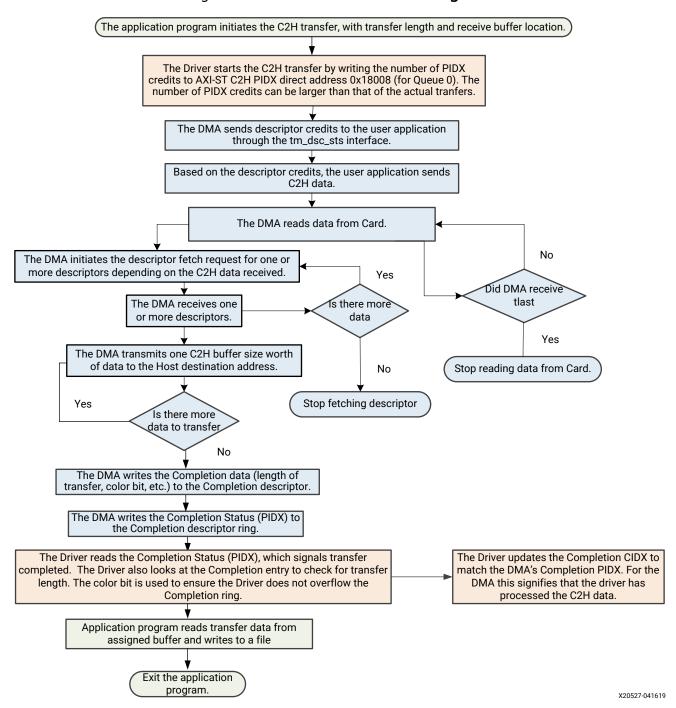

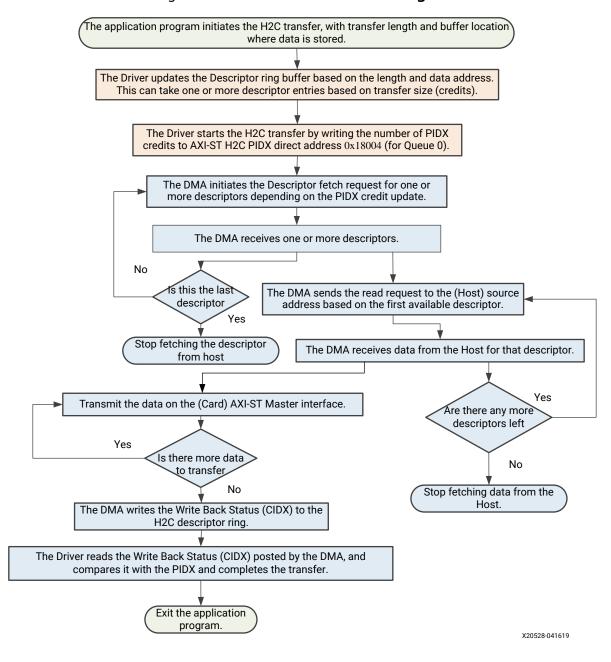

| Reference Software Driver Flow                               | 196 |

| Chapter 8: Debugging                                         | 202 |

| Finding Help on Xilinx.com                                   | 202 |

| Section III: AXI Bridge Subsystem for PL PCIE4 and PL PCIE5. | 204 |

| Overview                                                     |     |

| Modular IP Architecture                                      |     |

| Feature Summary                                              | 206 |

| AXI Bridge Subsystem Limitations                             | 206 |

| Chapter 9: Product Specification              | 207 |

|-----------------------------------------------|-----|

| Performance and Resource Utilization          | 208 |

| AXI Bridge Operations                         | 208 |

| AXI Bridge Port Descriptions                  | 225 |

| Register Space                                | 228 |

| Chapter 10: Design Flow Steps                 | 230 |

| Customizing and Generating the Subsystem      | 230 |

| Chapter 11: Example Design                    | 240 |

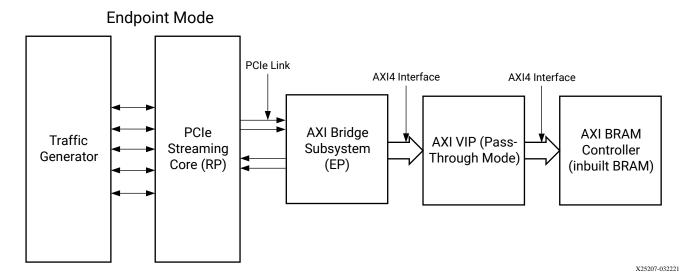

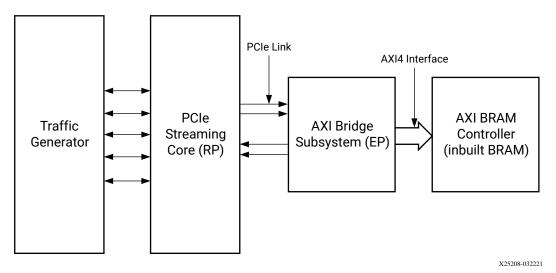

| Endpoint Configuration                        | 240 |

| Customizing and Generating the Example Design | 241 |

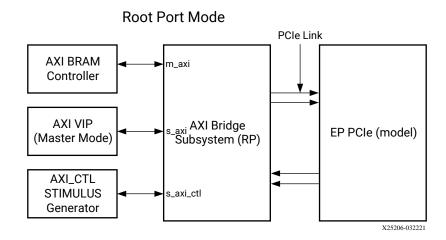

| Simulation Design Overview                    | 242 |

| Implementation Design Overview                | 243 |

| Example Design Elements                       | 243 |

| Chapter 12: Debugging                         | 244 |

| Finding Help on Xilinx.com                    | 244 |

| Debug Tools                                   | 245 |

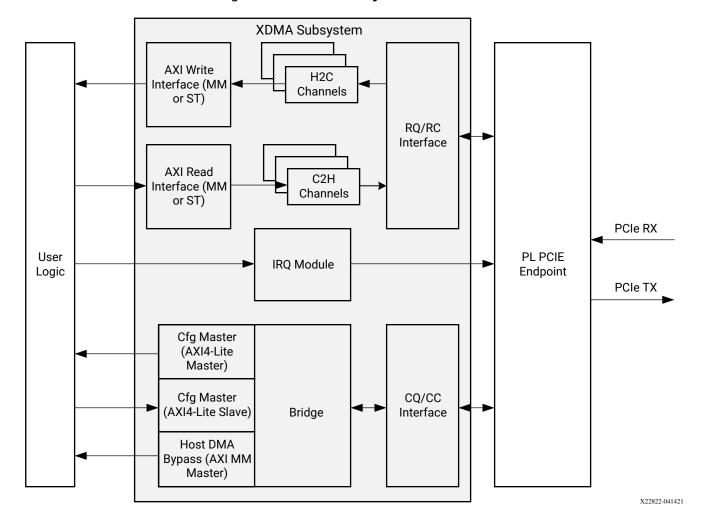

| Section IV: XDMA Subsystem for PL PCIE4       | 247 |

| Overview                                      | 247 |

| Modular IP Architecture                       | 248 |

| Feature Summary                               | 249 |

| Applications                                  | 249 |

| XDMA Subsystem Limitations                    | 250 |

| Chapter 13: Product Specification             | 251 |

| Performance and Resource Utilization          | 251 |

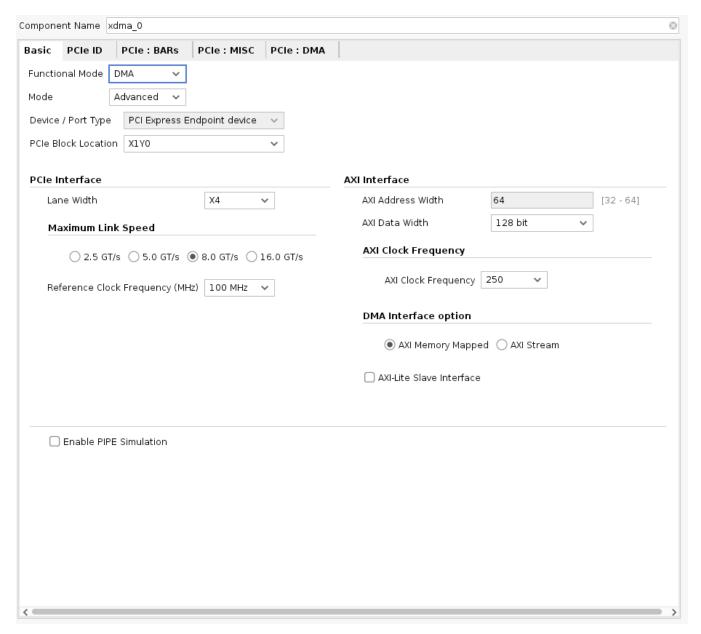

| Configurable Components of the Subsystem      | 251 |

| XDMA Operations                               | 257 |

| Port Descriptions                             | 267 |

| Register Space                                | 280 |

| Chapter 14: Design Flow Steps                 | 314 |

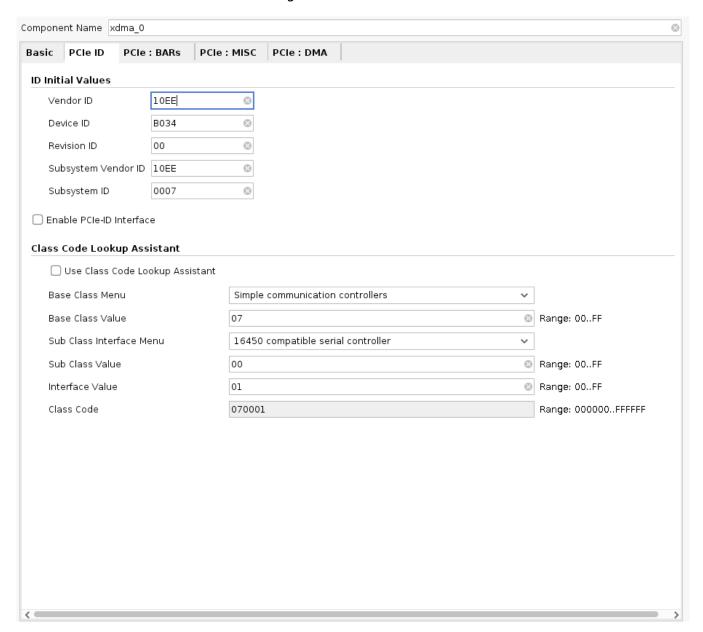

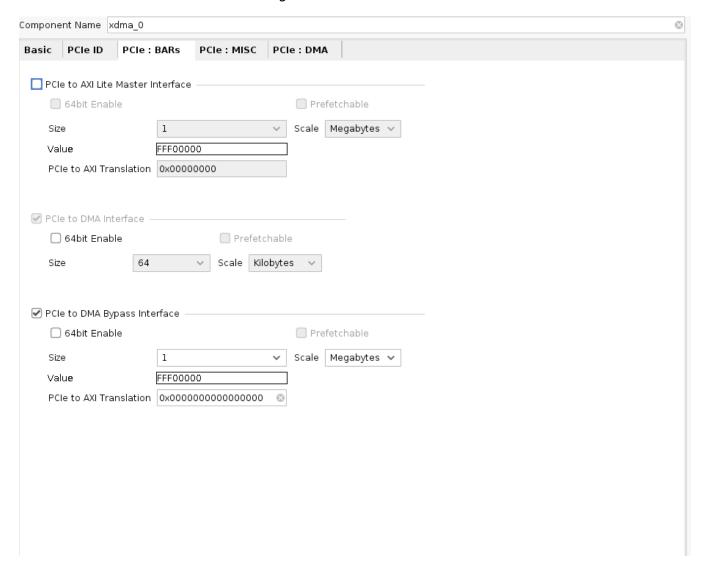

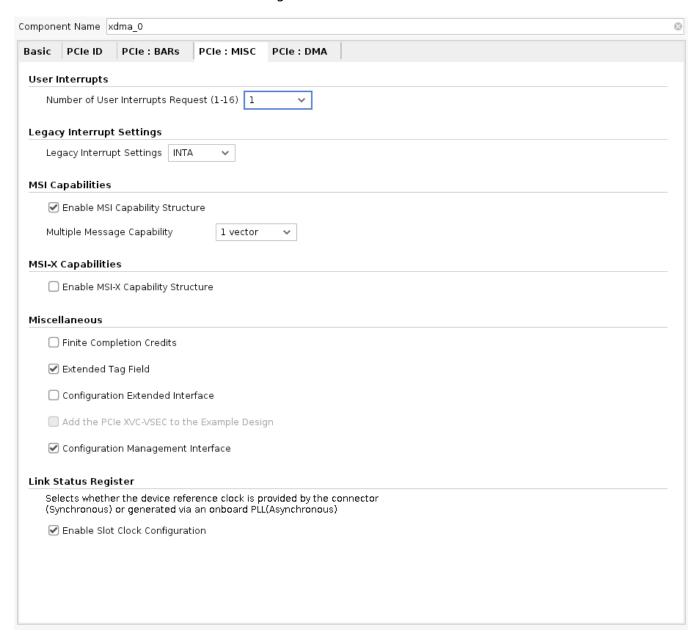

| Customizing and Generating the Subsystem      | 314 |

|                                               |     |

| Available Example Designs                          | 323 |

|----------------------------------------------------|-----|

| Customizing and Generating the Example Design      | 330 |

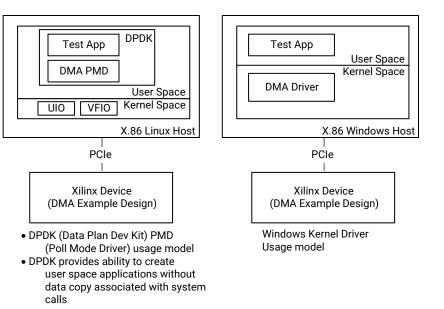

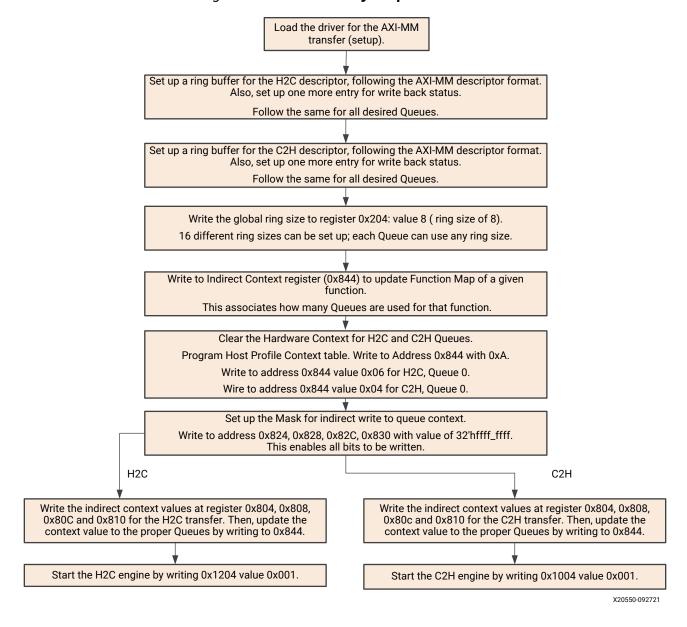

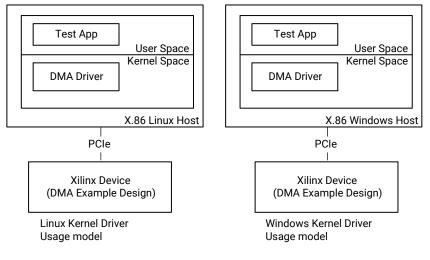

| Chapter 16: Application Software Development       | 331 |

| Device Drivers                                     |     |

| Linux Device Driver                                |     |

| Using the Driver                                   |     |

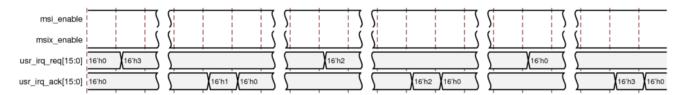

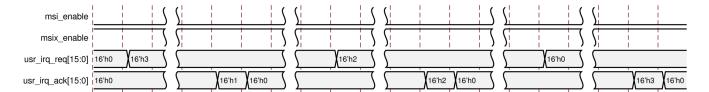

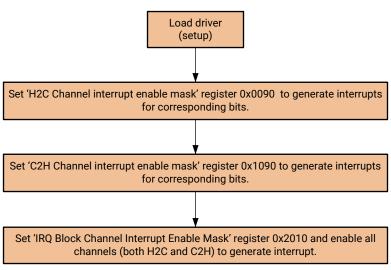

| Interrupt Processing                               |     |

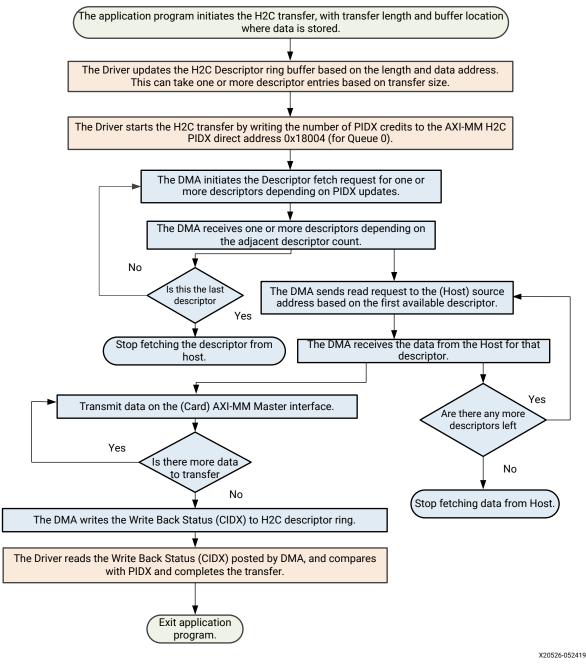

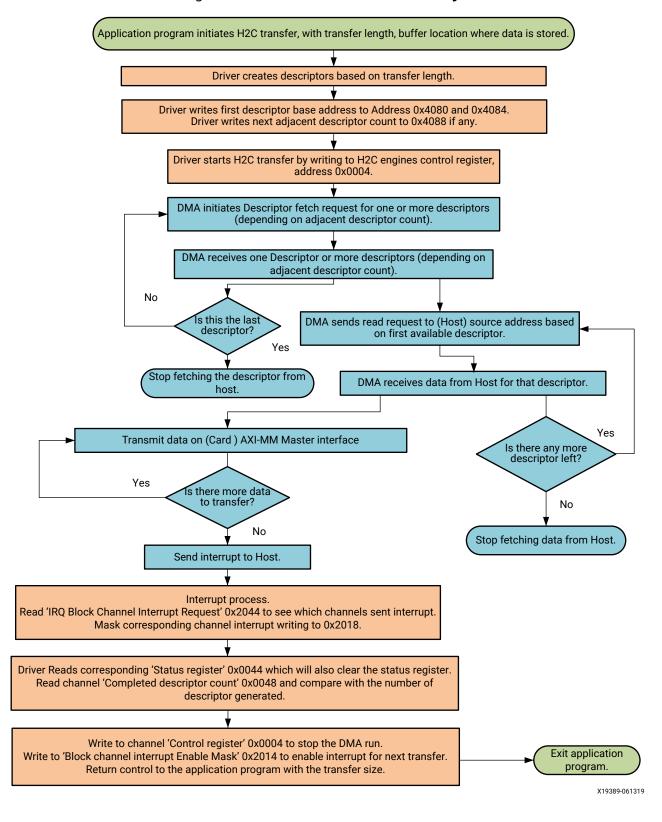

| Example H2C Flow                                   |     |

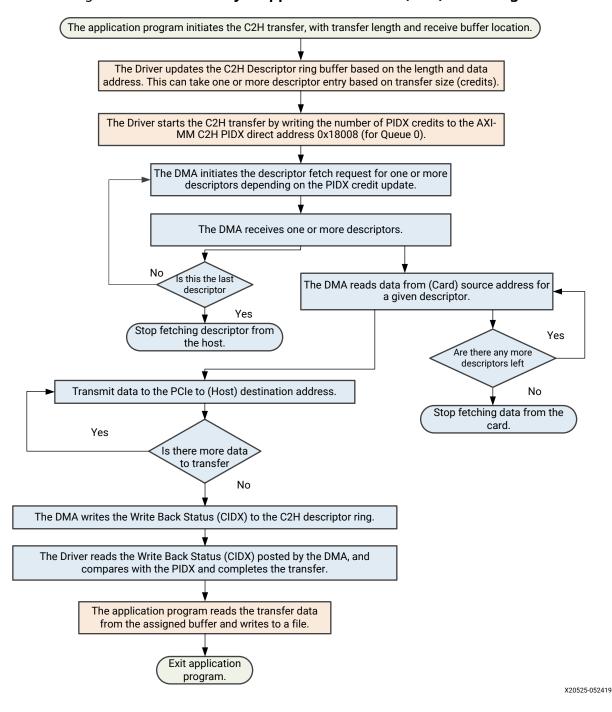

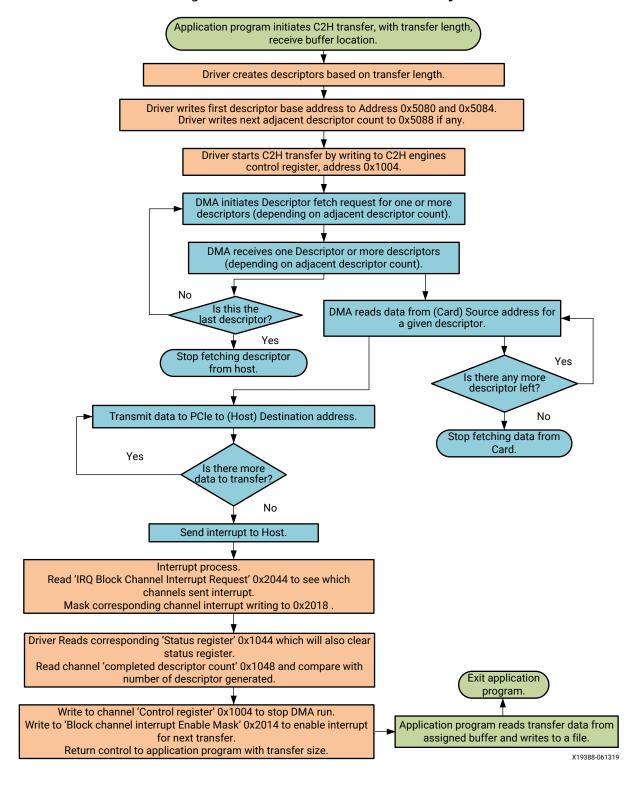

| Example C2H Flow                                   | 334 |

| Chapter 17: Debugging                              | 335 |

| Finding Help on Xilinx.com                         |     |

| Hardware Debug                                     |     |

| Appendix A: Upgrading                              | 338 |

| Appendix B: Limitations                            |     |

|                                                    |     |

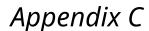

| Appendix C: GT Selection and Pin Planning          |     |

| PL PCIe GT Selection                               |     |

| CPM4 Additional Considerations                     |     |

| GT Locations                                       | 344 |

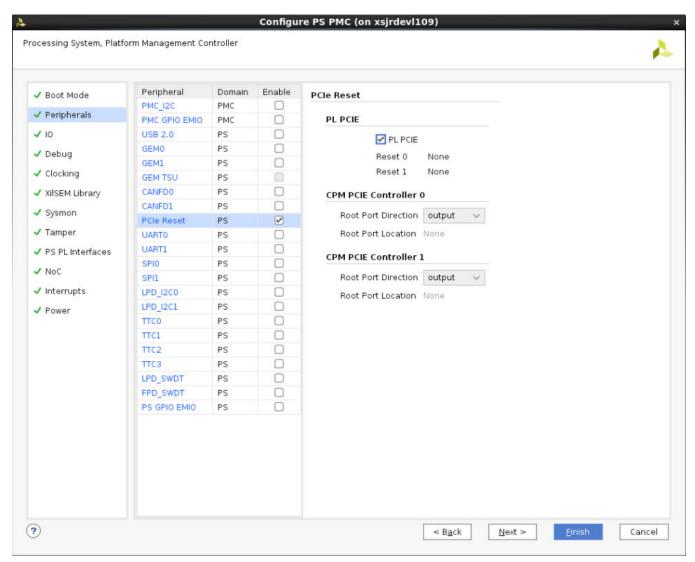

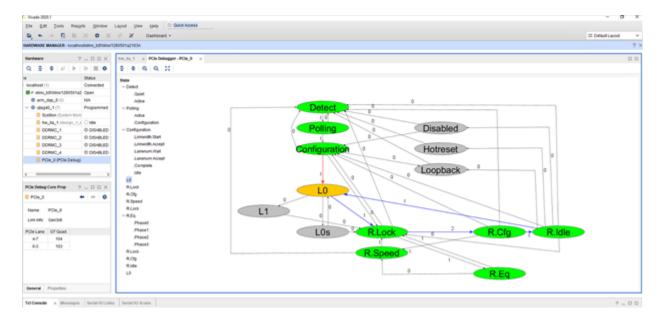

| Appendix D: PCIe Link Debug Enablement             | 348 |

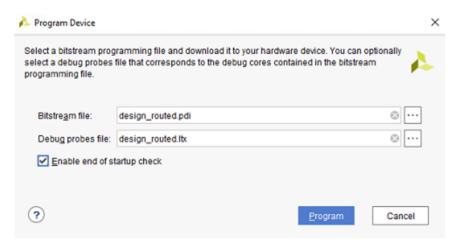

| Enabling PCIe Link Debug                           | 348 |

| Connecting to PCIe Link Debug in Vivado            | 352 |

| Appendix E: Additional Resources and Legal Notices | 354 |

| Xilinx Resources                                   |     |

| Documentation Navigator and Design Hubs            | 354 |

| References                                         | 355 |

| Revision History                                   | 355 |

| Please Read: Important Legal Notices               | 356 |

## Introduction to the DMA and Bridge Subsystems

The Versal® ACAP DMA and Bridge Subsystems for PCIe provide a rich set of options for high performance data transfer between a Versal® ACAP and other devices using the widely deployed and industry standard PCI Express system architecture.

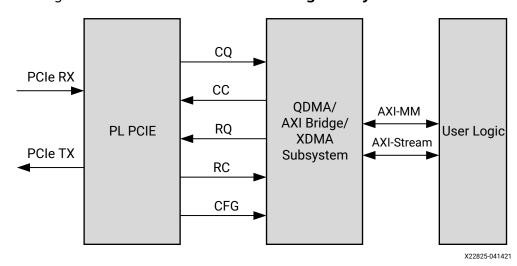

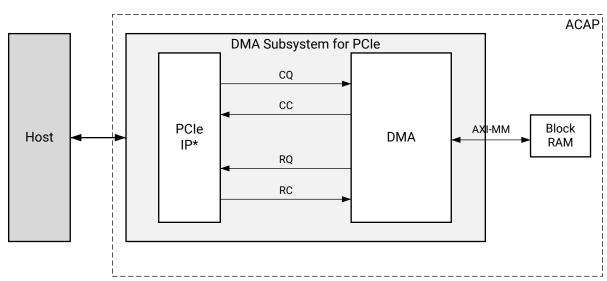

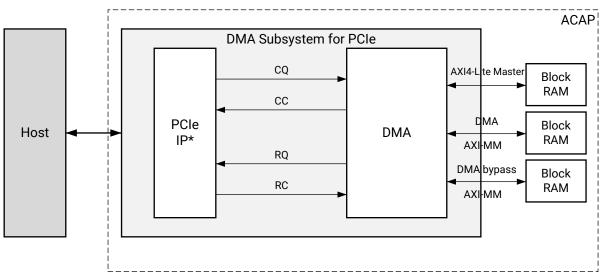

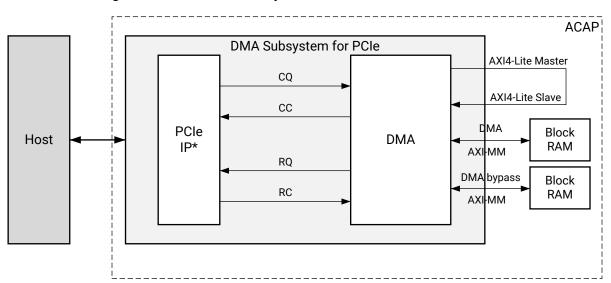

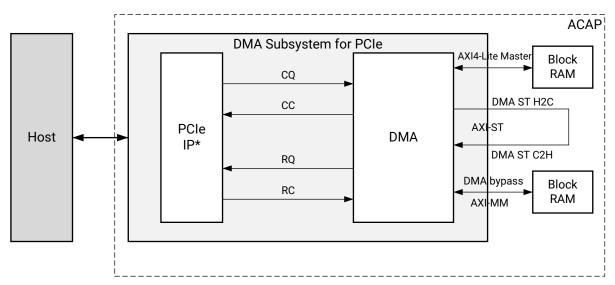

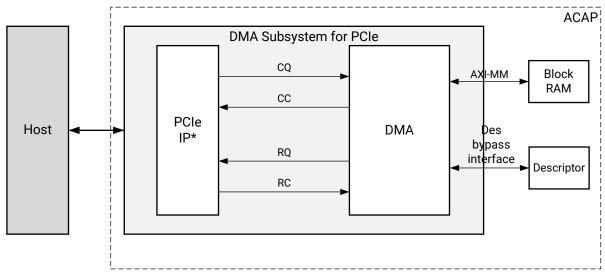

Figure 1: Versal® ACAP DMA and Bridge Subsystem for PCIe

These subsystems are built upon the robust and flexible programmable logic integrated block for PCI Express (PL PCIE) as shown in the figure above, and expands the integrated block capabilities through soft IP implemented in the Versal ACAP programmable logic. Three subsystems are available: QDMA Subsystem, AXI Bridge Subsystem, and XDMA Subsystem.

## Modular IP Architecture

The subsystems in the Versal® ACAP DMA and Bridge Subsystem for PCIe are packaged in what is called a **modular IP architecture**. Modular IP architecture refers to the programmable logic integrated block for PCIe (PL PCIE) IP and the DMA and Bridge subsystem appearing as two separate IP that are connected in the Vivado IP integrator.

To generate the IP:

- 1. In the Vivado IP catalog, locate the subsystem, and add it to your design.

- 2. Configure the subsystem as required.

- 3. In the Vivado IP integrator, click **Run Block Automation**. This stitches the PL PCIE and subsystem together.

After these steps, a fully integrated subsystem is available and you can add designs as needed.

## **QDMA Subsystem**

#### Locating the Subsystem

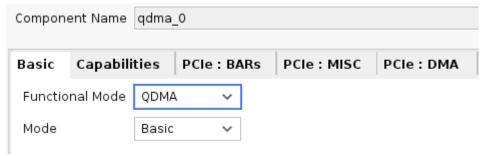

- 1. In the Vivado IP catalog, select Queue DMA Subsystem for PCI Express.

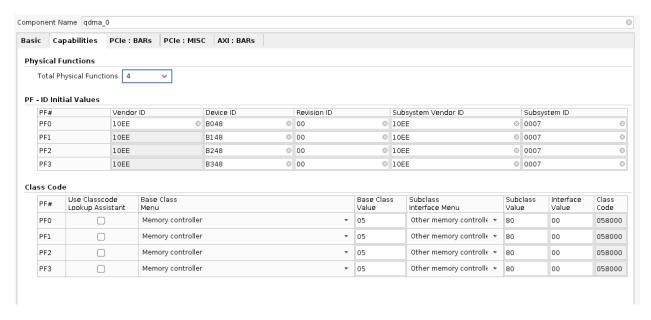

- 2. In the Basic tab, and set Functional Mode to QDMA.

#### Description

The QDMA subsystem is a queue based, configurable scatter-gather DMA implementation which provides thousands of queues, support for multiple physical/virtual functions with single-root I/O virtualization (SR-IOV), and advanced interrupt support. In this mode the IP provides AXI4-MM and AXI4-Stream user interfaces which may be configured on a per-queue basis. Based on PCIe system architecture conventions, the QDMA is highly suitable for endpoint (EP) use cases and may also be used to construct proprietary system architectures.

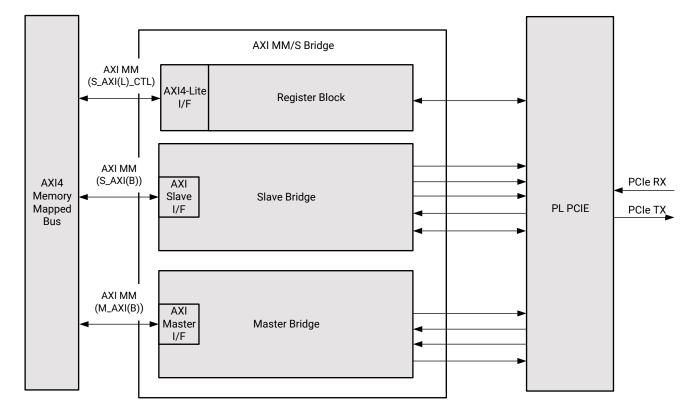

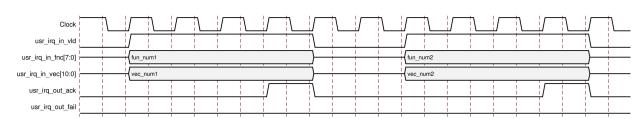

## **AXI Bridge Subsystem**

#### **Locating the Subsystem**

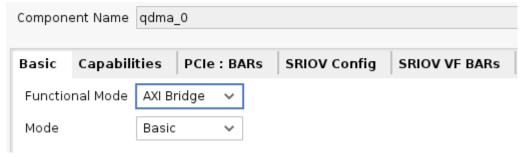

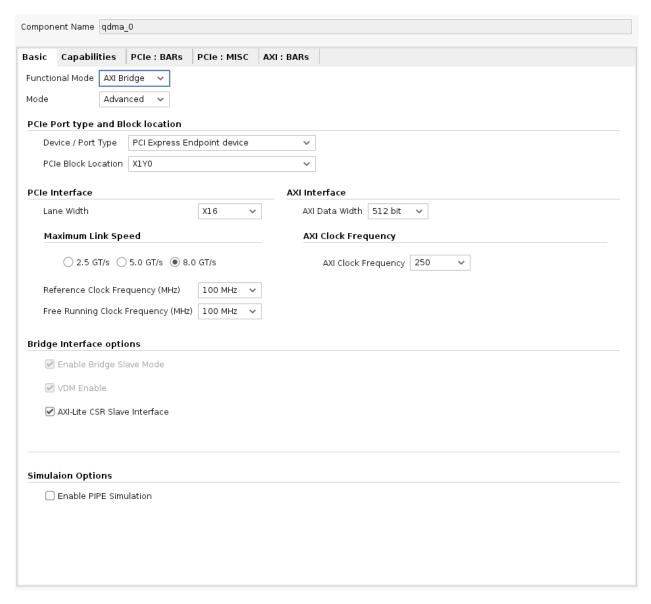

1. In the Vivado IP catalog, select Queue DMA Subsystem for PCI Express.

2. In the Basic tab, and set Functional Mode to AXI Bridge.

#### Description

A bridge based, configurable translation level between the PCIe system and AXI4-MM internal to the Xilinx device. In this mode the IP translates and forwards PCIe read and write accesses into AXI4-MM interface commands, and conversely translates and forwards AXI4-MM interface commands into PCIe read and write accesses. Based on PCIe system architecture conventions, the AXI Bridge is highly suitable for root port (RP) use cases as well as endpoint (EP) use cases and may also be used to construct proprietary system architectures.

## **XDMA Subsystem**

#### Locating the Subsystem

In the Vivado IP catalog, select XDMA Subsystem for PCIe.

#### Description

A channel based, configurable scatter-gather DMA implementation which provides four card-to-host (C2H) channels and four host-to-card (H2C) channels with interrupt support. In this mode the IP provides either AXI4-MM or AXI4-Stream user interfaces. Based on PCIe system architecture conventions, the XDMA is highly suitable for endpoint (EP) use cases and may also be used to construct proprietary system architectures.

## Features of the DMA and Bridge Subsystem

The subsystem supports these features:

• 64, 128, 256, and 512-bit data path.

- x1, x2, x4, x8, or x16 link widths.

- x1-x16 supported for Gen1-Gen3 line rates.

- x1-x8 supported for Gen4 line rates.

- x1-x4 supported for Gen5 line rates.

### **QDMA Subsystem**

- Support for both AXI4-MM and AXI4-Stream interfaces on a per queue basis

- 2K queue sets

- 2K H2C Descriptor rings

- 2K C2H Descriptor rings

- 2K C2H Writeback rings

- Supports Polling Mode (Status Descriptor Writeback)

- C2H stream interrupt moderation, CMPT entry coalesce

- Descriptor and DMA customization through user logic

- Custom descriptor formats

- Traffic management

- SR-IOV support with access control, FLR, and mailboxes

- Advanced and flexible interrupt support

#### **Related Information**

Features

QDMA Subsystem Limitations

## **AXI Bridge Subsystem**

- AXI4-MM access to PCle address space

- PCle access to AXI4-MM address space

- Tracks and manages Transaction Layer Packets (TLPs) completion processing

- Detects and indicates error conditions with interrupts

- Supports up to six PCle 32-bit or three 64-bit PCle BARs as endpoint (EP)

• Supports up to two PCle 32-bit or a single PCle 64-bit BAR as root port (RP)

#### **Related Information**

Feature Summary

AXI Bridge Subsystem Limitations

## **XDMA Subsystem**

- Four host-to-card (H2C/Read) data channels

- Four card-to-host (C2H/Write) data channels

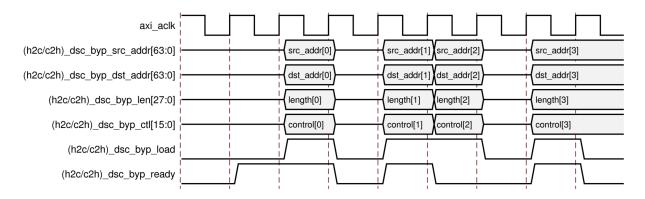

- Per channel descriptor bypass for custom descriptor creation

- Configurable user interface (AXI4-MM or AXI4-Stream)

- Advanced and flexible interrupt support

#### **Related Information**

Feature Summary

XDMA Subsystem Limitations

## Maximum Supported Link Rates and Widths

Maximum Supported Link Rates and Widths with PL PCIE4:

- 2.5 GT/s, 5.0 GT/s, 8.0 GT/s at x1, x2, x4, x8, or x16

- 16 GT/s at x1, x2, x4, or x8

Maximum Supported Link Rates and Widths with PL PCIE5:

- 2.5 GT/s, 5.0 GT/s, 8.0 GT/s at x1, x2, x4, x8, or x16

- 16 GT/s at x8

- 32 GT/s at x4

## **IP Facts**

|                                                                                      | LogiCORE™ IP Facts Table                                                                                                  |  |  |  |  |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Subsystem Specifics                                                                  |                                                                                                                           |  |  |  |  |

| Supported Device Family <sup>1</sup> Versal® ACAP and Versal Premium ACAP            |                                                                                                                           |  |  |  |  |

| Supported User Interfaces                                                            | AXI4 Memory Map, AXI4-Lite, AXI4-Stream                                                                                   |  |  |  |  |

| Resources                                                                            | QDMA and AXI Bridge Subsystems: Performance and Resource Utilization XDMA Subsystem: Performance and Resource Utilization |  |  |  |  |

|                                                                                      | Provided with Subsystem                                                                                                   |  |  |  |  |

| Design Files                                                                         | Encrypted System Verilog                                                                                                  |  |  |  |  |

| Example Design                                                                       | Verilog                                                                                                                   |  |  |  |  |

| Test Bench                                                                           | Verilog                                                                                                                   |  |  |  |  |

| Constraints File                                                                     | Xilinx Constraints File (XDC)                                                                                             |  |  |  |  |

| Simulation Model                                                                     | Verilog                                                                                                                   |  |  |  |  |

| Supported S/W Driver <sup>2</sup>                                                    | QDMA Subsystem and AXI Bridge Subsystem: Linux, DPDK, and Windows Drivers                                                 |  |  |  |  |

|                                                                                      | XDMA Subsystem: Linux, and Windows Drivers                                                                                |  |  |  |  |

|                                                                                      | Tested Design Flows <sup>3</sup>                                                                                          |  |  |  |  |

| Design Entry                                                                         | Vivado® Design Suite                                                                                                      |  |  |  |  |

| Simulation For supported simulators, see the Xilinx Design Tools: Release Notes Guid |                                                                                                                           |  |  |  |  |

| Synthesis                                                                            | Vivado Synthesis                                                                                                          |  |  |  |  |

|                                                                                      | Support                                                                                                                   |  |  |  |  |

| Release Notes and Known Issues                                                       | Master Answer Record: AR 75397                                                                                            |  |  |  |  |

| All Vivado IP Change Logs                                                            | Master Vivado IP Change Logs: 72775                                                                                       |  |  |  |  |

|                                                                                      | Xilinx Support web page                                                                                                   |  |  |  |  |

#### Notes:

- 1. For a complete list of supported devices, see the Vivado® IP catalog.

- 2. See the "Application Software Development" chapter in the QDMA Subsystem, and XDMA Subsystem sections below.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

## Overview

## **Navigating Content by Design Process**

Xilinx® documentation is organized around a set of standard design processes to help you find relevant content for your current development task. All Versal® ACAP design process Design Hubs and the Design Flow Assistant materials can be found on the Xilinx.com website. This document covers the following design processes:

- System and Solution Planning: Identifying the components, performance, I/O, and data transfer requirements at a system level. Includes application mapping for the solution to PS, PL, and Al Engine. Topics in this document that apply to this design process include:

- QDMA Subsystem

- AXI Bridge Subsystem

- XDMA Subsystem

- IP Facts

- Embedded Software Development: Creating the software platform from the hardware platform and developing the application code using the embedded CPU. Also covers XRT and Graph APIs. Topics in this document that apply to this design process include:

- QDMA Subsystem Register Space

- AXI Bridge Subsystem Register Space

- XDMA Subsystem Register Space

- Host Software Development: Developing the application code, accelerator development, including library, XRT, and Graph API use. Topics in this document that apply to this design process include:

- QDMA Subsystem Register Space

- AXI Bridge Subsystem Register Space

- XDMA Subsystem Register Space

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, functional simulation, and evaluating the Vivado® timing, resource use, and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- QDMA Subsystem Customizing and Generating the Subsystem

- AXI Bridge Subsystem Customizing and Generating the Subsystem

- XDMA Subsystem Customizing and Generating the Subsystem

## **Unsupported Features**

Fast PCI Express Endpoint Enumeration using Tandem Configuration is not supported. This use case addresses the ability to initially load a fully configurable PCI Express protocol solution from a small external ROM, so as to meet the 100 ms enumeration requirement. Support for Tandem Configuration for the PL PCIE block in Versal ACAP is not currently planned.

**Note:** Any user design requiring fast PCle enumeration or configuration through PCle should use the PCle controllers in the CPM. Not all Versal ACAP contain this particular resource. For details, see *Versal ACAP CPM Mode for PCl Express Product Guide* (PG346).

## Standards for the DMA and Bridge Subsystems

#### **Using PL PCIE4**

This subsystem adheres to the following standards:

- PCI Express<sup>®</sup> Base Specification 4.0

- AMBA AXI4-Stream Protocol Specification (ARM IHI 0051A)

For more information about PCI/PCIe specifications, see *PCI-SIG Specifications* (https://www.pcisig.com/specifications).

#### Using PL PCIE5

This subsystem adheres to the following standards:

- PCI Express Base Specification 5.0, and Errata/ECN updates

- AMBA AXI4-Stream Protocol Specification (ARM IHI 0051A)

For more information about PCI/PCIe specifications, see *PCI-SIG Specifications* (https://www.pcisig.com/specifications).

## **Minimum Device Requirements**

Table 1: PL PCIE4 with QDMA, Bridge, or XDMA Soft IP Subsystem Maximum Configurations (Versal Prime, Versal AI Core, Versal AI Edge)

| Speed Grade              | -1        | -1        | -2        | -2        | -2        | -3        |

|--------------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| Voltage Grade            | L (0.70V) | M (0.80V) | L (0.70V) | M (0.80V) | H (0.88V) | H (0.88V) |

| Gen1 (2.5 GT/s per lane) | x16       | x16       | x16       | x16       | x16       | x16       |

| Gen2 (5 GT/s per lane)   | x16       | x16       | x16       | x16       | x16       | x16       |

| Gen3 (8 GT/s per lane)   | x16       | x16       | x16       | x16       | x16       | x16       |

| Gen4 (16 GT/s per lane)  | x8        | x8        | x8        | x8        | x8        | x8        |

*Table 2:* PL PCIE5 with QDMA or Bridge Soft IP Subsystem Maximum Configurations (Versal Premium, Versal HBM, Versal AI Core)

| Speed Grade                          | -1        | -1        | -2        | -2        | -2        | -3        |

|--------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| Voltage Grade                        | L (0.70V) | M (0.80V) | L (0.70V) | M (0.80V) | H (0.88V) | H (0.88V) |

| Gen1 (2.5 GT/s per lane)             | x16       | x16       | x16       | x16       | x16       | x16       |

| Gen2 (5 GT/s per lane)               | x16       | x16       | x16       | x16       | x16       | x16       |

| Gen3 (8 GT/s per lane)               | x16       | x16       | x16       | x16       | x16       | x16       |

| Gen4 (16 GT/s per lane)              | x8        | x8        | x8        | х8        | x8        | x8        |

| Gen5 (32 GT/s per lane) <sup>1</sup> | N/A       | x4        | x4        | x4        | x4        | x4        |

#### Notes:

## **Licensing and Ordering**

This Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP module is provided at no additional cost with the Xilinx Vivado<sup>®</sup> Design Suite under the terms of the Xilinx End User License.

Information about other Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

<sup>1.</sup> Gen5 support is available only in Versal Premium, Versal HBM, and Versal AI Core series.

## Designing with the Subsystem

## Clocking

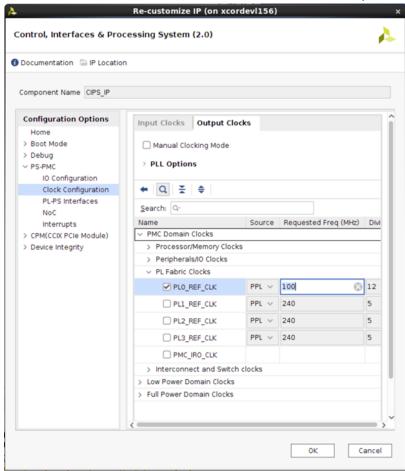

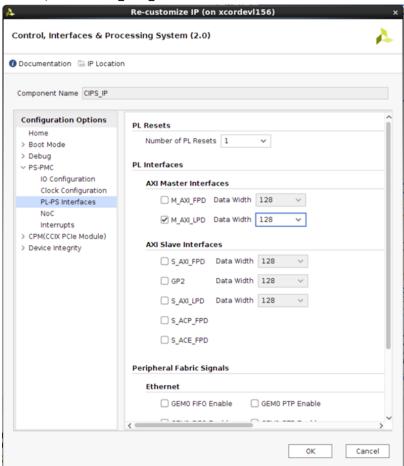

The programmable logic integrated block for PCIe (PL PCIE) requires a 100, 125, or 250 MHz reference clock input. The following figure shows the clocking architecture. The  $user_clk$  clock is available for use in the fabric logic. The  $user_clk$  clock can be used as the system clock.

CLKP

IBUFDS

GTE

CLKN

Versal

GTY QUAD

TXOUTCLK

BUFG\_GT

USER\_CLK

To DMA

X25061-012621

Figure 2: USER\_CLK Clocking Architecture

All user interface signals are timed with respect to the same clock (user\_clk) which can have a frequency of 62.5, 125, or 250 MHz depending on the configured link speed and width.

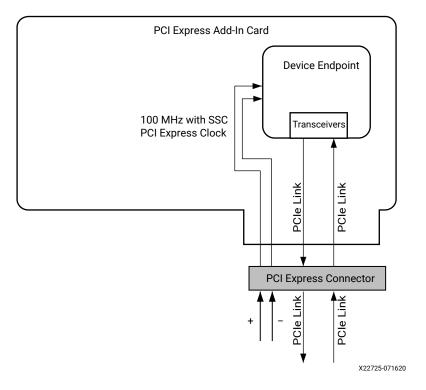

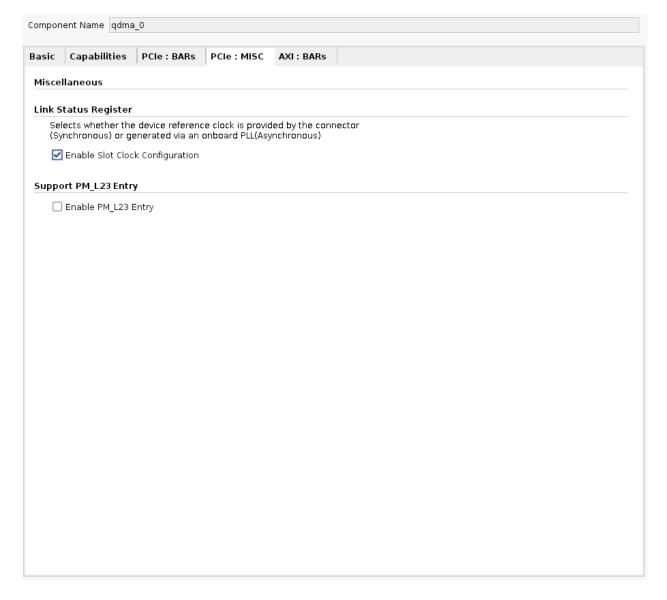

Each link partner device shares the same reference clock source. The following figures show a system using a 100 MHz reference clock. Even if the device is part of an embedded system, if the system uses commercial PCI Express<sup>®</sup> root complexes or switches along with typical motherboard clocking schemes, synchronous clocking should be used.

**Note:** The following figures are high-level representations of the board layout. Ensure that coupling, termination, and details are correct when laying out a board.

X22724-051419

PCI Express

Switch or Root

Complex Device

PCIE Link

PCIE Link

Transceivers

Device

Endpoint

100 MHz

PCI Express

Clock Oscillator

Figure 3: Embedded System Using 100 MHz Reference Clock

Figure 4: Open System Add-In Card Using 100 MHz Reference Clock

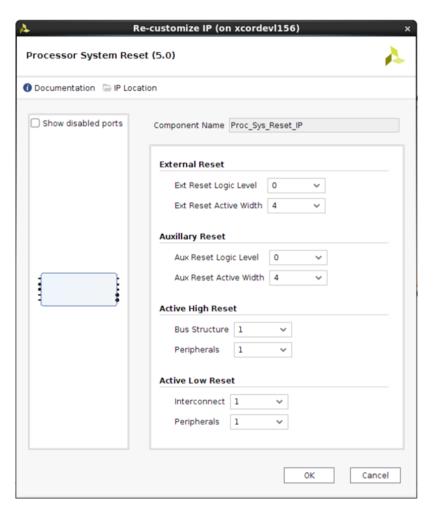

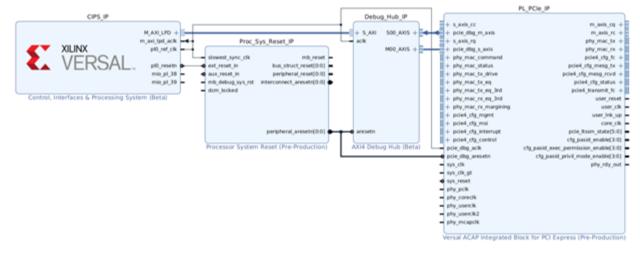

#### Resets

If your board is designed to use the same PCIe edge connectors to operate with CPM and PL PCIE, then we recommend using PS reset using the Control, Interface and Processing System (CIPS) IP core. For more information, see the *Versal ACAP CPM Mode for PCI Express Product Guide* (PG346).

If your board is designed to use PL PCIE in the PCIe edge connectors, then any PL reset pin can be used.

After the reset is released, the core attempts to link train and resumes normal operation.

The DMA subsystem receives the reset signal user\_reset from the PL PCIE. The DMA subsystem uses user\_reset as main reset for all its logic. When the PL PCIE goes through a reset or there is a link down, it issues a user\_reset to the DMA subsystem. After the PCIe link is up, the user\_reset is released for the DMA subsystem.

## QDMA Subsystem for PL PCIE4 and PL PCIE5

## Overview

The Queue-based Direct Memory Access (QDMA) subsystem is a PCI Express® (PCle®) based DMA engine that is optimized for both high bandwidth and high packet count data transfers. The QDMA is composed of the Versal® Integrated Block for PCI Express, and an extensive DMA and bridge infrastructure that enables the ultimate in performance and flexibility.

The QDMA offers a wide range of setup and use options, many selectable on a per-queue basis, such as memory-mapped DMA or stream DMA, interrupt mode and polling. The subsystem provides many options for customizing the descriptor and DMA through user logic to provide complex traffic management capabilities.

The primary mechanism to transfer data using the QDMA is for the QDMA engine to operate on instructions (descriptors) provided by the host operating system. Using the descriptors, the QDMA can move data in both the Host to Card (H2C) direction, or the Card to Host (C2H) direction. You can select on a per-queue basis whether DMA traffic goes to an AXI4 memory map (MM) interface or to an AXI4-Stream interface. In addition, the QDMA has the option to implement both an AXI4 MM Master port and an AXI4 MM Slave port, allowing PCIe traffic to bypass the DMA engine completely.

The main difference between QDMA and other DMA offerings is the concept of queues. The idea of queues is derived from the "queue set" concepts of Remote Direct Memory Access (RDMA) from high performance computing (HPC) interconnects. These queues can be individually configured by interface type, and they function in many different modes. Based on how the DMA descriptors are loaded for a single queue, each queue provides a very low overhead option for setup and continuous update functionality. By assigning queues as resources to multiple PCIe Physical Functions (PFs) and Virtual Functions (VFs), a single QDMA core and PCI Express interface can be used across a wide variety of multifunction and virtualized application spaces.

The QDMA can be used and exercised with a Xilinx® provided QDMA reference driver, and then built out to meet a variety of application spaces.

#### **Related Information**

**Port Descriptions**

#### Modular IP Architecture

The QDMA Subsystem is packaged in what is called a **modular IP architecture**. Modular IP architecture refers to the programmable logic integrated block for PCIe (PL PCIE) IP and the QDMA subsystem appearing as two separate IP that are connected in the Vivado IP integrator.

To generate the IP:

- In the Vivado IP catalog, locate the QDMA Subsystem for PCI Express, and add it to your design.

- 2. Configure the subsystem as required

- 3. In the Vivado IP integrator, click **Run Block Automation**. This stitches the PL PCIE and QDMA together.

After these steps, a fully integrated PL PCIE and QDMA is available, and you can add designs as needed.

#### **Related Information**

**Customizing and Generating the Subsystem**

### **Features**

- The PCIe Integrated Block is supported in Versal® ACAP.

- Supports 64, 128, 256, and 512-bit data path.

- Supports x1, x2, x4, x8, or x16 link widths.

- Supports Gen1, Gen2, and Gen3 link speeds. Gen4 for PCIE4C block.

- Support for both the AXI4 Memory Mapped and AXI4-Stream interfaces per queue.

- 2048 queue sets

- 2048 H2C descriptor rings.

- 2048 C2H descriptor rings.

- <sub>o</sub> 2048 C2H Completion (CMPT) rings.

- Supports Polling Mode (Status Descriptor Write Back) and Interrupt Mode.

- Interrupts

- 2048 MSI-X vectors.

- Up to 8 MSI-X per function.

Note: It is possible to assign more vectors per function. For more information, see AR 72352.

- . Interrupt aggregation.

- C2H Stream interrupt moderation.

- C2H Stream Completion queue entry coalescence.

- Descriptor and DMA customization through user logic

- Allows custom descriptor format.

- Traffic Management.

- Supports SR-IOV with up to 4 Physical Functions (PF) and 252 Virtual Functions (VF)

- Thin hypervisor model.

- QID virtualization.

- Allows only privileged/Physical functions to program contexts and registers.

- Function level reset (FLR) support.

- 。 Mailbox.

- Rich programmability on a per queue basis, such as AXI4 Memory Mapped versus AXI4-Stream interfaces.

## **QDMA Architecture**

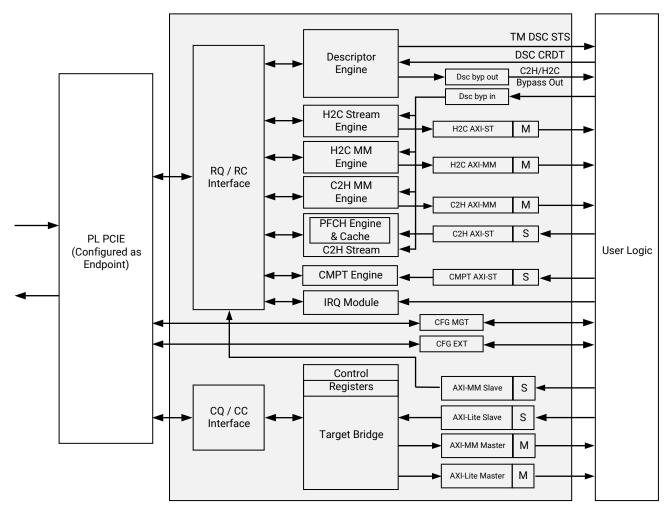

The following figure shows the block diagram of the QDMA.

Figure 5: **QDMA Architecture**

X22823-041421

### **DMA Engines**

#### **Descriptor Engine**

The Host to Card (H2C) and Card to Host (C2H) descriptors are fetched by the Descriptor Engine in one of two modes: Internal mode, and Descriptor bypass mode. The descriptor engine maintains per queue contexts where it tracks software (SW) producer index pointer (PIDX), consumer index pointer (CIDX), base address of the queue (BADDR), and queue configurations for each queue. The descriptor engine uses a round robin algorithm for fetching the descriptors. The descriptor engine has separate buffers for H2C and C2H queues, and ensures it never fetches more descriptors than available space. The descriptor engine will have only one DMA read outstanding per queue at a time and can read as many descriptors as can fit in a MRRS. The descriptor engine is responsible for reordering the out of order completions and ensures that descriptors for queues are always in order.

The descriptor bypass can be enabled on a per-queue basis and the fetched descriptors, after buffering, are sent to the respective bypass output interface instead of directly to the H2C or C2H engine. In internal mode, based on the context settings the descriptors are sent to delete per H2C memory mapped (MM), C2H MM, H2C Stream, or C2H Stream engines.

The descriptor engine is also responsible for generating the status descriptor for the completion of the DMA operations. With the exception of C2H Stream mode, all modes use this mechanism to convey completion of each DMA operation so that software can reclaim descriptors and free up any associated buffers. This is indicated by the CIDX field of the status descriptor.

**RECOMMENDED:** If a queue is associated with interrupt aggregation, Xilinx recommends that the status descriptor be turned off, and instead the DMA status be received from the interrupt aggregation ring.

To put a limit on the number of fetched descriptors (for example, to limit the amount of buffering required to store the descriptor), it is possible to turn-on and throttle credit on a per-queue basis. In this mode, the descriptor engine fetches the descriptors up to available credit, and the total number of descriptors fetched per queue is limited to the credit provided. The user logic can return the credit through the <code>dsc\_crdt</code> interface. The credit is in the granularity of the size of the descriptor.

To help a user-developed traffic manager prioritize the workload, the available descriptor to be fetched (incremental PIDX value) of the PIDX update is sent to the user logic on the  $tm_dsc_st_s$  interface. Using this interface it is possible to implement a design that can prioritize and optimize the descriptor storage.

#### **H2C MM Engine**

The H2C MM Engine moves data from the host memory to card memory through the H2C AXI-MM interface. The engine generates reads on PCIe, splitting descriptors into multiple read requests based on the MRRS and the requirement that PCIe reads do not cross 4 KB boundaries. Once completion data for a read request is received, an AXI write is generated on the H2C AXI-MM interface. For source and destination addresses that are not aligned, the hardware will shift the data and split writes on AXI-MM to prevent 4 KB boundary crossing. Each completed descriptor is checked to determine whether a writeback and/or interrupt is required.

For Internal mode, the descriptor engine delivers memory mapped descriptors straight to the H2C MM engine. The user logic can also inject the descriptor into the H2C descriptor bypass interface to move data from host to card memory. This gives the ability to do interesting things such as mixing control and DMA commands in the same queue. Control information can be sent to a control processor indicating the completion of DMA operation.

#### C2H MM Engine

The C2H MM Engine moves data from card memory to host memory through the C2H AXI-MM interface. The engine generates AXI reads on the C2H AXI-MM bus, splitting descriptors into multiple requests based on 4 KB boundaries. Once completion data for the read request is received on the AXI4 interface, a PCIe write is generated using the data from the AXI read as the contents of the write. For source and destination addresses that are not aligned, the hardware will shift the data and split writes on PCIe to obey Maximum Payload Size (MPS) and prevent 4 KB boundary crossings. Each completed descriptor is checked to determine whether a writeback and/or interrupt is required.

For Internal mode, the descriptor engine delivers memory mapped descriptors straight to the C2H MM engine. As with H2C MM Engine, the user logic can also inject the descriptor into the C2H descriptor bypass interface to move data from card to host memory.

For multi-function configuration support, the PCle function number information will be provided in the aruser bits of the AXI-MM interface bus to help virtualization of card memory by the user logic. A parity bus, separate from the data and user bus, is also provided for end-to-end parity support.

#### **H2C Stream Engine**

The H2C stream engine moves data from the host to the H2C Stream interface. For internal mode, descriptors are delivered straight to the H2C stream engine; for a queue in bypass mode, the descriptors can be reformatted and fed to the bypass input interface. The engine is responsible for breaking up DMA reads to MRRS size, guaranteeing the space for completions, and also makes sure completions are reordered to ensure H2C stream data is delivered to user logic in-order.

The engine has sufficient buffering for up to 256 descriptor reads and up to 32 KB of data. DMA fetches the data and aligns to the first byte to transfer on the AXI4 interface side. This allows every descriptor to have random offset and random length. The total length of all descriptors put together must be less than 64 KB.

For internal mode queues, each descriptor defines a single AXI4-Stream packet to be transferred to the H2C AXI-ST interface. A packet with multiple descriptors straddling is not allowed due to the lack of per queue storage. However, packets with multiple descriptors straddling can be implemented using the descriptor bypass mode. In this mode, the H2C DMA engine can be initiated when the user logic has enough descriptors to form a packet. The DMA engine is initiated by delivering the multiple descriptors straddled packet along with other H2C ST packet descriptors through the bypass interface, making sure they are not interleaved. Also, through the bypass interface, the user logic can control the generation of the status descriptor.

#### C2H Stream Engine

The C2H streaming engine is responsible for receiving data from the user logic and writing to the Host memory address provided by the C2H descriptor for a given Queue.

The C2H engine has two major blocks to accomplish C2H streaming DMA, Descriptor Prefetch Cache (PFCH), and the C2H-ST DMA Write Engine. The PFCH has per queue context to enhance the performance of its function and the software that is expected to program it.

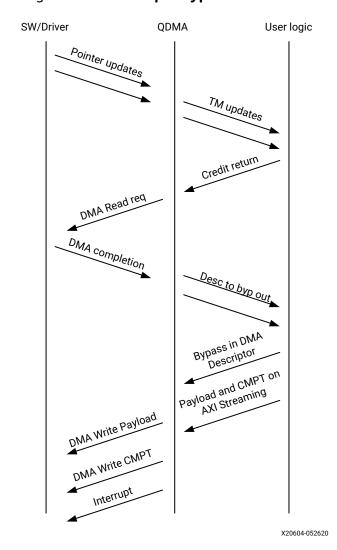

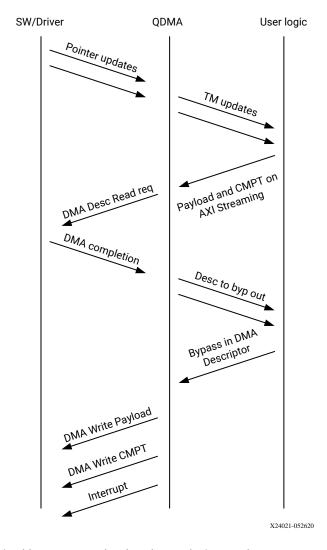

PFCH cache has three main modes, on a per queue basis, called Simple Bypass Mode, Internal Cache Mode, and Cached Bypass Mode.

- In Simple Bypass Mode, the engine does not track anything for the queue, and the user logic can define its own method to receive descriptors. The user logic is then responsible for delivering the packet and associated descriptor through the simple bypass interface. The ordering of the descriptors fetched by a queue in the bypass interface and the C2H stream interface must be maintained across all queues in bypass mode.

- In Internal Cache Mode and Cached Bypass Mode, the PFCH module offers storage for up to 512 descriptors and these descriptors can be used by up to 64 different queues. In this mode, the engine controls the descriptors to be fetched by managing the C2H descriptor queue credit on demand based on received packets in the pipeline. Pre-fetch mode can be enabled on a per queue basis, and when enabled, causes the descriptors to be opportunistically pre-fetched so that descriptors are available before the packet data is available. The status can be found in prefetch context. This significantly reduces the latency by allowing packet data to be transferred to the PCle integrated block almost immediately, instead of having to wait for the relevant descriptor to be fetched. The size of the data buffer is fixed for a queue (PFCH context) and the engine can scatter the packet across as many as seven descriptors. In cached bypass mode descriptor is bypassed to user logic for further processing, such as address translation, and sent back on the bypass in interface. This mode does not assume any ordering descriptor and C2H stream packet interface, and the pre-fetch engine can match the packet and descriptors. When pre-fetch mode is enabled, do not give credits to IP. The pre-fetch engine takes care of credit management.

#### **Completion Engine**

The Completion (CMPT) Engine is used to write to the completion queues. Although the Completion Engine can be used with an AXI-MM interface and Stream DMA engines, the C2H Stream DMA engine is designed to work closely with the Completion Engine. The Completion Engine can also be used to pass immediate data to the Completion Ring. The Completion Engine can be used to write Completions of up to 64B in the Completion ring. When used with a DMA engine, the completion is used by the driver to determine how many bytes of data were transferred with every packet. This allows the driver to reclaim the descriptors.

The Completion Engine maintains the Completion Context. This context is programmed by the Driver and is maintained on a per-queue basis. The Completion Context stores information like the base address of the Completion Ring, PIDX, CIDX and a number of aspects of the Completion Engine, which can be controlled by setting the fields of the Completion Context.

The engine also can be configured on a per-queue basis to generate an interrupt or a completion status update, or both, based on the needs of the software. If the interrupts for multiple queues are aggregated into the interrupt aggregation ring, the status descriptor information is available in the interrupt aggregation ring as well.

The CMPT Engine has a cache of up to 64 entries to coalesce the multiple smaller CMPT writes into 64B writes to improve the PCle efficiency. At any time, completions can be simultaneously coalesced for up to 64 queues. Beyond this, any additional queue that needs to write a CMPT entry will cause the eviction of the least recently used queue from the cache. The depth of the cache used for this purpose is configurable with possible values of 8, 16, 32, and 64.

#### **Bridge Interfaces**

#### AXI Memory Mapped Bridge Master Interface

The AXI MM Bridge Master interface is used for high bandwidth access to AXI Memory Mapped space from the host. The interface supports up to 32 outstanding AXI reads and writes. One or more PCle BAR of any physical function (PF) or virtual function (VF) can be mapped to the AXI-MM bridge master interface. This selection must be made prior to design compilation. The function ID, BAR ID, VF group, and VF group offset will be made available as part of aruser and awuser of the AXI-MM interface allowing the user logic to identify the source of each memory access. The  $m_axib_awuser/m_axib_aruser[54:0]$  user bits mapping is listed in AXI Bridge Master Ports.

Virtual function group (VFG) refers to the VF group number. It is equivalent to the PF number associated with the corresponding VF. VFG\_OFFSET refers to the VF number with respect to a particular PF. Note that this is not the FIRST\_VF\_OFFSET of each PF.

For example, if both PFO and PF1 have 8 VFs, FIRST\_VF\_OFFSET for PFO and PF1 is 4 and 11. Below is the mapping for VFG and VFG\_OFFSET.

|   | Table 3: AXI-MM | Interface ' | Virtual | Function Gro | up |

|---|-----------------|-------------|---------|--------------|----|

| 1 |                 |             |         |              |    |

| Function<br>Number | PF Number | VFG | VFG_OFFSET                                                                                                                               |

|--------------------|-----------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| 0                  | 0         | 0   | 0                                                                                                                                        |

| 1                  | 1         | 0   | 0                                                                                                                                        |

| 4                  | 0         | 0   | 0 (Because FIRST_VF_OFFSET for PF0 is 4, the first VF of PF0 starts at FN_NUM=4 and VFG_OFFSET=0 indicates this is the first VF for PF0) |

| 5                  | 0         | 0   | 1 (VFG_OFFSET=1 indicates this is the second VF for PF0)                                                                                 |

|                    |           |     |                                                                                                                                          |

| 12                 | 1         | 1   | 0 (VFG=1 indicates this VF is associated with PF1)                                                                                       |

| 13                 | 1         | 1   | 1                                                                                                                                        |

Each host initiated access can be uniquely mapped to the 64 bit AXI address space through the PCIe to AXI BAR translation.

Since all functions share the same AXI Master address space, a mechanism is needed to map requests from different functions to a distinct address space on the AXI master side. An example provided below shows how PCIe to AXI translation vector is used. Note that all VFs belonging to the same PF share the same PCIe to AXI translation vector. Therefore, the AXI address space of each VF is concatenated together. Use VFG\_OFFSET to calculate the actual starting address of AXI for a particular VF.

To summarize, m\_axib\_awaddr is determined as:

- For PF, m\_axib\_awaddr = pcie2axi\_vec + axib\_offset.

- For VF, m\_axib\_awaddr = pcie2axi\_vec + (VFG\_OFFSET + 1)\*vf\_bar\_size + axib\_offset.

Where pcielaxi\_vec is PCIe to AXI BAR translation (that can be set when the IP core is configured from the Vivado IP Catalog).

And axib\_offset is the address offset in the requested target space.

#### **Related Information**

**AXI Bridge Master Ports**

#### AXI4-Lite Bridge Master Interface

One or more PCIe BAR of any physical function (PF) or virtual function (VF) can be mapped to the AXI4-Lite master interface. This selection must be done at the point of configuring the IP. The function ID, BAR ID (BAR hit), VF group, and VF group offset will be made available as part of aruser and awuser of the AXI4-Lite interface to help the user logic identify the source of memory access.

The m\_axil\_awuser/m\_axil\_aruser[54:0] user bits mapping is listed in AXI4-Lite Master Ports.

Virtual function group (VFG) refers to the VF group number. It is equivalent to the PF number associated with the corresponding VF. VFG\_OFFSET refer to the VF number with respect to a particular PF. Note that this is not the FIRST\_VF\_OFFSET of each PF.

For example, if both PFO and PF1 has 8 VFs, and FIRST\_VF\_OFFSET for PFO and PF1 is 4 and 11 and below is the mapping for VFG and VFG\_OFFSET.

Table 4: AXI4-Lite Interface VFG

| Function<br>Number | PF Number | VFG | VFG_OFFSET                                                                                                                              |

|--------------------|-----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0                  | 0         | 0   | 0                                                                                                                                       |

| 1                  | 1         | 0   | 0                                                                                                                                       |

| 4                  | 0         | 0   | 0 (Because FIRST_VF_OFFSET for PF0 is 4, the first VF of PF0 starts at FN_NUM=4 and VFG_OSSET=0 indicates this is the first VF for PF0) |

| 5                  | 0         | 0   | 1 (VFG_OSSET=1 indicates this is the second VF for PF0)                                                                                 |

|                    |           |     |                                                                                                                                         |

| 12                 | 1         | 1   | 0 (VFG=1 indicates this VF is associated with PF1)                                                                                      |

| 13                 | 1         | 1   | 1                                                                                                                                       |

Each host initiated access can be uniquely mapped to the 64 bit AXI address space through the PCIe to AXI BAR translation.

Because all functions shares the same AXI4 master address space, a mechanism is needed to map requests from different functions to a distinct address space on the AXI master side. This below shows how PCIe to AXI translation vector is used. Note that all VFs belonging to the same PF shares the same PCIe to AXI translation vector. Therefore, the AXI address space of each VF is concatenated together. Use VFG\_OFFSET to calculate the actual starting address of AXI for a particular VF.

To summarize, m axil awaddr is determined as:

- For PF, m\_axil\_awaddr = pcie2axi\_vec + axil\_offset.

- For VF, m\_axil\_awaddr = pcie2axi\_vec + (VFG\_OFFSET + 1)\*vf\_bar\_size + axil\_offset

Where pcielaxi\_vec is PCle to AXI BAR translation (that can be set during IP configuration.).

And axib\_offset is the address offset in the requested target space.

Each host initiated access can be uniquely mapped to the 64 bit AXI address space. One outstanding read and one outstanding write are supported on this interface.

Expansion ROM BAR can also be mapped to AXI4-Lite interface at the IP configuration time.

#### **Related Information**

**AXI4-Lite Master Ports**

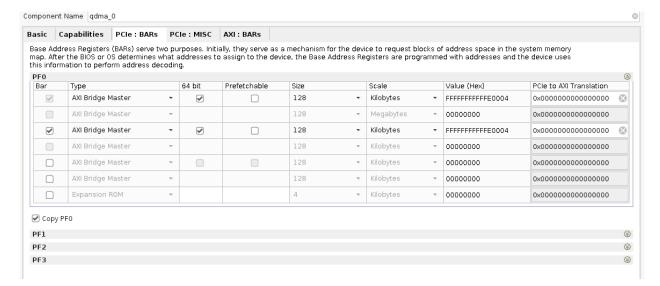

#### PCIe to AXI BARS

For each physical function, the PCle configuration space consists of a set of six 32-bit memory BARs and one 32-bit Expansion ROM BAR. When SR-IOV is enabled, an additional six 32-bit BARs are enabled for each Virtual Function. These BARs provide address translation to the AXI4 memory mapped space capability, interface routing, and AXI4 request attribute configuration. Any pairs of BARs can be configured as a single 64-bit BAR. Each BAR can be configured to route its requests to the QDMA register space, the Bridge AXI4-Lite master interface, or the AXI MM bridge master interface.

#### **Request Memory Type**

The memory type can be set for each PCle BAR through attributes attr\_dma\_pciebar2axibar\_\*\_cache\_pf\*.

- AxCache[0] is set to 1 for modifiable, and 0 for non-modifiable.

- AxCache[1] is set to 1 for cacheable, and 0 for non-cacheable.

#### AXI Memory Mapped Bridge Slave Interface

The AXI-MM Bridge Slave interface is used for high bandwidth memory transfers between the user logic and the Host. AXI to PCIe translation is supported through the AXI to PCIe BARs. The interface will split requests as necessary to obey PCIe MPS and 4 KB boundary crossing requirements. Up to 32 outstanding read and write requests are supported.

#### AXI4-Lite Bridge Slave CSR Interface

The AXI4-Lite slave interface is used to access the AXI Bridge and QDMA internal registers. Address bit [15] indicates if the access is for QDMA registers or AXI Bridge registers.

- When s\_axil\_csr\_awaddr[15] = 1'b1, the write access is for QDMA CSR registers.

- When s\_axil\_csr\_awaddr[15] = 1'b0, the write access is for Bridge registers (When accessing Bridge Registers, access from address 0x000 to 0xDFF will be redirected to PCle core configuration space access and from address 0xE00 will be directed towards Bridge registers).

- When s\_axil\_csr\_araddr[15] = 1'b1, the read access is for QDMA CSR registers.

- When s\_axil\_csr\_araddr[15] = 1'b0, the read access is for Bridge registers. When accessing Bridge Registers, access from address 0x000 to 0xDFF will be redirected to PCle core configuration space access and from address 0xE00 will be directed towards Bridge registers.

The QDMA registers are virtualized for VFs and PFs. For example, VFs and PFs can access different parts of the address space, and each has access to its own queues. To accommodate the function specific accesses, the user logic can provide function ID on  $s_{axil_awuser[7:0]}$  for write access and  $s_{axil_aruser[7:0]}$  read access, which gives the QDMA proper internal register access. One outstanding read request and one outstanding write request are supported on the AXI4-Lite slave interface.

The AXI4-Lite slave interface is also used to generate Vendor defined messages (VDM) using the Bridge registers.

#### **Related Information**

**VDM**

#### AXI to PCIe BARS

In the Bridge Slave interface, there is one BARs which can be configured as 32 bits or 64 bits. This BAR provide address translation from AXI address space to PCIe address space. The address translation is configured through BDF table programming. Refer to Slave Bride section for BDF programming.

#### **Related Information**

Slave Bridge

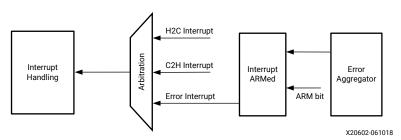

### **Interrupt Module**

The IRQ module aggregates interrupts from various sources. The interrupt sources are queue-based interrupts, user interrupts and error interrupts.

Queue-based interrupts and user interrupts are allowed on PFs and VFs, but error interrupts are allowed only on PFs. If the SR-IOV is not enabled, each PF has the choice of MSI-X or Legacy Interrupts. With SR-IOV enabled, only MSI-X interrupts are supported across all functions.

MSI-X interrupt is enabled by default. Host system (Root Complex) will enable one or all of the interrupt types supported in hardware. If MSI-X is enabled, it takes precedence.

Up to eight interrupts per function are available. To allow many queues on a given function and each to have interrupts, the QDMA offers a novel way of aggregating interrupts from multiple queues to a single interrupt vector. In this way, all 2048 queues could in principle be mapped to a single interrupt vector. QDMA offers 256 interrupt aggregation rings that can be flexibly allocated among the 256 available functions.

#### **PCIe Block Interface**

#### PCIe CQ/CC

The PCIe Completer Request (CQ)/Completer Completion (CC) modules receive and process TLP requests from the remote PCIe agent. This interface to the Versal Integrated Block for PCIe IP operates in address aligned mode. The module uses the BAR information from the Integrated Block for PCIe IP to determine where the request should be forwarded. The possible destinations for these requests are:

- DMA configuration module

- AXI4 MM Bridge Master interface

- the AXI4-Lite Bridge Master interface

Non-posted requests are expected to receive completions from the destination, which are forwarded to the remote PCIe agent. For further details, see the Versal ACAP Integrated Block for PCI Express LogiCORE IP Product Guide (PG343).

#### PCIe RQ/RC

The PCIe Requester Request (RQ)/Requester Completion (RC) interface generates PCIeTLPs on the RQ bus and processes PCIe Completion TLPs from the RC bus. This interface to the Versal Integrated Block for PCIe® core operates in DWord aligned mode. With a 512-bit interface, straddling will be enabled. While straddling is supported, all combinations of RQ straddled transactions may not be implemented. For further details, see the Versal ACAP Integrated Block for PCI Express LogiCORE IP Product Guide (PG343).

#### **PCIe Configuration**

Several factors can throttle outgoing non-posted transactions. Outgoing non-posted transactions are throttled based on flow control information from the PCIe<sup>®</sup> integrated block to prevent head of line blocking of posted requests. The DMA will meter non-posted transactions based on the PCIe Receive FIFO space.

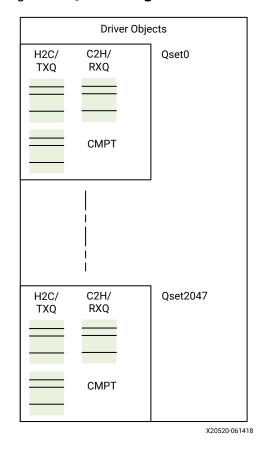

### **General Design of Queues**

The multi-queue DMA engine of the QDMA uses RDMA model queue pairs to allow RNIC implementation in the user logic. Each queue set consists of Host to Card (H2C), Card to Host (C2H), and a C2H Stream Completion (CMPT). The elements of each queue are descriptors.

H2C and C2H are always written by the driver/software; hardware always reads from these queues. H2C carries the descriptors for the DMA read operations from Host. C2H carries the descriptors for the DMA write operations to the Host.

In internal mode, H2C descriptors carry address and length information and are called gather descriptors. They support 32 bits of metadata that can be passed from software to hardware along with every descriptor. The descriptor can be memory mapped (where it carries host address, card address, and length of DMA transfer) or streaming (only host address, and length of DMA transfer) based on context settings. Through descriptor bypass, an arbitrary descriptor format can be defined, where software can pass immediate data and/or additional metadata along with packet.

C2H queue memory mapped descriptors include the card address, the host address and the length. In streaming internal cached mode, descriptors carry only the host address. The buffer size of the descriptor, which is programmed by the driver, is expected to be of fixed size for the whole queue. Actual data transferred associated with each descriptor does not need to be the full length of the buffer size.

The software advertises valid descriptors for H2C and C2H queues by writing its producer index (PIDX) to the hardware. The status descriptor is the last entry of the descriptor ring, except for a C2H stream ring. The status descriptor carries the consumer index (CIDX) of the hardware so that the driver knows when to reclaim the descriptor and deallocate the buffers in the host.

For the C2H stream mode, C2H descriptors will be reclaimed based on the CMPT queue entry. Typically, this carries one entry per C2H packet, indicating one or more C2H descriptors is consumed. The CMPT queue entry carries enough information for software to claim all the descriptors consumed. Through external logic, this can be extended to carry other kinds of completions or information to the host.

CMPT entries written by the hardware to the ring can be detected by the driver using either the color bit in the descriptor or the status descriptor at the end of the CMPT ring. Each CMPT entry can carry metadata for a C2H stream packet and can also serve as a custom completion or immediate notification for the user application.

The base address of all ring buffers (H2C, C2H, and CMPT) should be aligned to a 4 KB address.

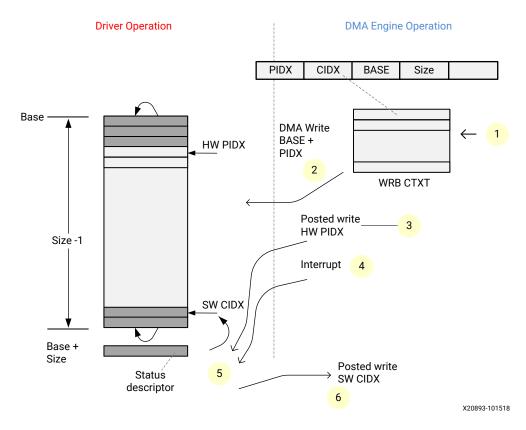

Figure 6: Queue Ring Architecture

The software can program 16 different ring sizes. The ring size for each queue can be selected from context programing. The last queue entry is the descriptor status, and the number of allowable entries is (queue size -1).

For example, if queue size is 8, which contains the entry index 0 to 7, the last entry (index 7) is reserved for status. This index should never be used for PIDX update, and PIDX update should never be equal to CIDX. For this case, if CIDX is 0, the maximum PIDX update would be 6.

In the example above, if traffic has already started and the CIDX is 4, the maximum PIDX update is 3.

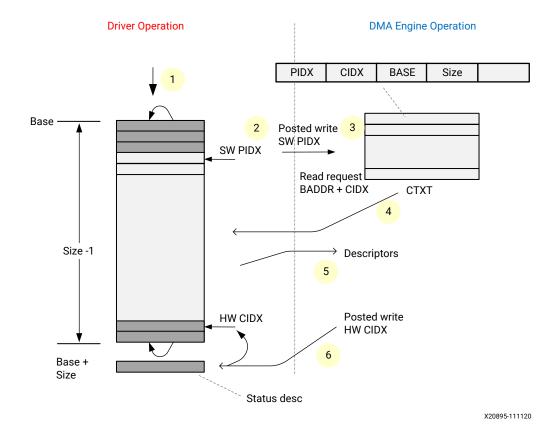

#### **H2C and C2H Queues**

H2C/C2H queues are rings located in host memory. For both type of queues, the producer is software and consumer is the descriptor engine. The software maintains producer index (PIDX) and a copy of hardware consumer index (HW CIDX) to avoid overwriting unread descriptors. The descriptor engine also maintains consumer index (CIDX) and a copy of SW PIDX, which is to make sure the engine does not read unwritten descriptors. The last entry in the queue is dedicated for the status descriptor where the engine writes the HW CIDX and other status.

The engine maintains a total of 2048 H2C and 2048 C2H contexts in local memory. The context stores properties of the queue, such as base address (BADDR), SW PIDX, CIDX, and depth of the queue.

Figure 7: Simple H2C and C2H Queue

The figure above shows the H2C and C2H fetch operation.

- 1. For H2C, the driver writes payload into host buffer, forms the H2C descriptor with the payload buffer information and puts it into H2C queue at the PIDX location. For C2H, the driver forms the descriptor with available buffer space reserved to receive the packet write from the DMA.

- 2. The driver sends the posted write to PIDX register in the descriptor engine for the associated Queue ID (QID) with its current PIDX value.

- Upon reception of the PIDX update, the engine calculates the absolute QID of the pointer update based on address offset and function ID. Using the QID, the engine will fetch the context for the absolute QID from the memory associated with the QDMA.

- 4. The engine determines the number of descriptors that are allowed to be fetched based on the context. The engine calculates the descriptor address using the base address (BADDR), CIDX, and descriptor size, and the engine issues the DMA read request.

- 5. After the descriptor engine receives the read completion from the host memory, the descriptor engine delivers them to the H2C Engine or C2H Engine in internal mode. In case of bypass, the descriptors are sent out to the associated descriptor bypass output interface.

- 6. For memory mapped or H2C stream queues programmed as internal mode, after the fetched descriptor is completely processed, the engine writes the CIDX value to the status descriptor. For queues programmed as bypass mode, user logic controls the write back through bypass in interface. The status descriptor could be moderated based on context settings. C2H stream queues always use the CMPT ring for the completions.

For C2H, the fetch operation is implicit through the CMPT ring.

#### **Completion Queue**

The Completion (CMPT) queue is a ring located in host memory. The consumer is software, and the producer is the CMPT engine. The software maintains the consumer index (CIDX) and a copy of hardware producer index (HW PIDX) to avoid reading unwritten completions. The CMPT engine also maintains PIDX and a copy of software consumer index (SW CIDX) to make sure that the engine does not overwrite unread completions. The last entry in the queue is dedicated for the status descriptor which is where the engine writes the hardware producer index (HW PIDX) and other status.

The engine maintains a total of 2048 CMPT contexts in local memory. The context stores properties of the queue, such as base address, SW CIDX, PIDX, and depth of the queue.

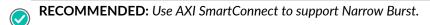

Figure 8: Simple Completion Queue Flow

C2H stream is expected to use the CMPT queue for completions to host, but it can also be used for other types of completions or for sending messages to the driver. The message through the CMPT is guaranteed to not bypass the corresponding C2H stream packet DMA.

The simple flow of DMA CMPT queue operation with respect to the numbering above follows:

- 1. The CMPT engine receives the completion message through the CMPT interface, but the QID for the completion message comes from the C2H stream interface. The engine reads the QID index of CMPT context RAM.

- The DMA writes the CMPT entry to address BASE+PIDX.

- 3. If all conditions are met, optionally writes PIDX to the status descriptor of the CMPT queue with color bit.

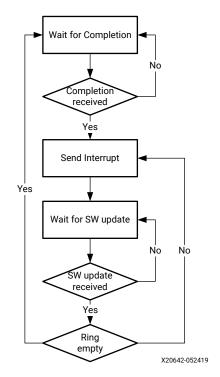

- 4. If interrupt mode is enabled, the CMPT engine generates the interrupt event message to the interrupt module.

- 5. The driver can be in polling or interrupt mode. Either way, the driver identifies the new CMPT entry either by matching the color bit or by comparing the PIDX value in the status descriptor against its current software CIDX value.

6. The driver updates CIDX for that queue. This allows the hardware to reuse the descriptors again. After the software finishes processing the CMPT, that is, before it stops polling or leaving the interrupt handler, the driver issues a write to CIDX update register for the associated queue.

#### **SR-IOV Support**

The QDMA provides an optional feature to support Single Root I/O Virtualization (SR-IOV). The PCI-SIG® Single Root I/O Virtualization and Sharing (SR-IOV) specification (available from *PCI-SIG Specifications* (www.pcisig.com/specifications) standardizes the method for bypassing the VMM involvement in datapath transactions and allows a single endpoint to appear as multiple separate endpoints. SR-IOV classifies the functions as:

- Physical Functions (PF): Full featured PCle<sup>®</sup> functions which include SR-IOV capabilities among others.

- Virtual Functions (VF): PCle functions featuring configuration space with Base Address Registers (BARs) but lacking the full configuration resources and controlled by the PF configuration. The main role of the VF is data transfer.

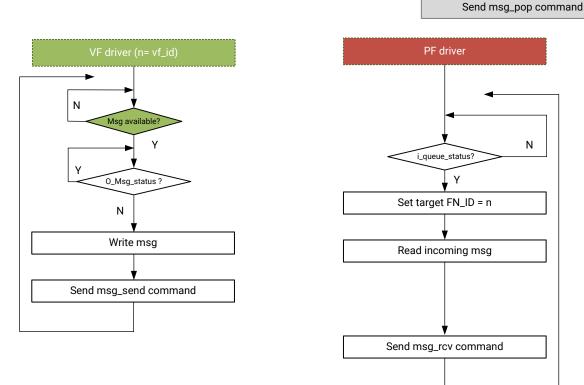

Apart from PCIe defined configuration space, QDMA Subsystem for PCI Express virtualizes data path operations, such as pointer updates for queues, and interrupts. The rest of the management and configuration functionality is deferred to the physical function driver. The Drivers that do not have sufficient privilege must communicate with the privileged Driver through the mailbox interface which is provided in part of the QDMA Subsystem for PCI Express.

Security is an important aspect of virtualization. The QDMA Subsystem for PCI Express offers the following security functionality:

- QDMA allows only privileged PF to configure the per queue context and registers. VFs inform the corresponding PFs of any queue context programming.

- Drivers are allowed to do pointer updates only for the queue allocated to them.

- The system IOMMU can be turned on to check that the DMA access is being requested by PFs or VFs. The ARID comes from queue context programmed by a privileged function.

Any PF or VF can communicate to a PF (not itself) through mailbox. Each function implements one 128B inbox and 128B outbox. These mailboxes are visible to the driver in the DMA BAR (typically BARO) of its own function. At any given time, any function can have one outgoing mailbox and one incoming mailbox message outstanding per function.

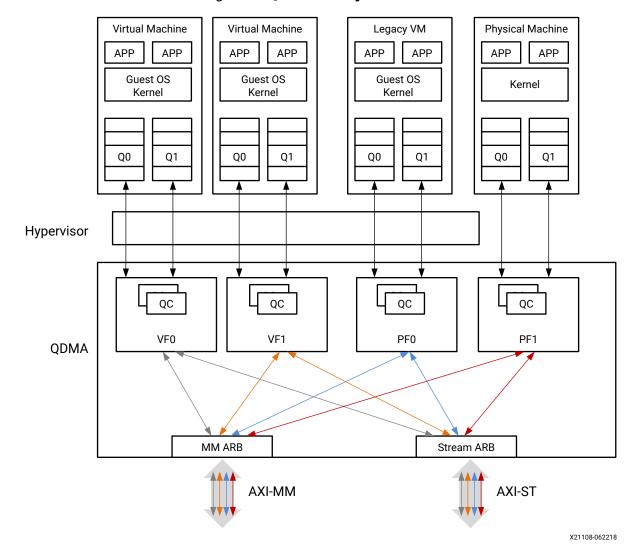

The diagram below shows how a typical system can use QDMA with different functions and operating systems. Different Queues can be allocated to different functions, and each function can transfer DMA packets independent of each other.

Figure 9: **QDMA in a System**

# **QDMA Subsystem Limitations**

The limitations of the QDMA are as follows:

- The DMA supports a maximum of 256 Queues on any VF function.

- Slave Bridge AXI does not support Narrow Burst transfers.

• SRIOV is not supported in bridge mode.

# **Applications**

The QDMA is used in a broad range of networking, computing, and data storage applications. A common usage example for the QDMA is to implement Data Center and Telco applications, such as Compute acceleration, Smart NIC, NVMe, RDMA-enabled NIC (RNIC), server virtualization, and NFV in the user logic. Multiple applications can be implemented to share the QDMA by assigning different queue sets and PCIe functions to each application. These Queues can then be scaled in the user logic to implement rate limiting, traffic priority, and custom work queue entry (WQE).

# **Product Specification**

# **Performance and Resource Utilization**

#### **Performance**

Xilinx provides two example designs for you to experiment with. Standard example design is for functional test only. To generate a example design for performance analysis, use the following Tcl command to generate a performance example design:

```

set_property CONFIG.performance_exdes{true} [get_ips qdma_0]

```

Below are the QDMA register settings recommended by Xilinx for better performance. Performance numbers will vary based on systems and which OS is being used.

- QDMA\_C2H\_INT\_TIMER\_TICK (0xB0C) set to 25. Corresponding to 100 ns (1 tick = 4 ns for 250 MHz user clock)

- C2H trigger mode set to Counter + Timer, with counter set to 64 and timer to match round trip latency. Global register for timer should have a value of 30 for 3  $\mu$ s.

- QDMA GLBL DSC CFG (0x250), max\_desc\_fetch = 6, wb\_int = 5

- QDMA H2C REQ THROT (0xE24), req\_throt\_en\_data = 1, data\_thresh = 0x4000

- QDMA C2H PFCH CFG (0xB08/0xA80/0xA84)

- o evt\_gcnt\_th = (QDMA\_C2H\_PFCH\_CACHE\_DEPTH/2) 2

- pfch\_qcnt = QDMA\_C2H\_PFCH\_CACHE\_DEPTH/2

- $num_pfch = 8$ . A minimum of 8 is recommended. In environments with low number of active queues, programing higher values can help to boost the performance.

- omega pfch\_fl\_th = 256

- QDMA\_C2H\_WRB\_COAL\_CFG (0xB50),

- . max\_buf\_sz = QDMA\_C2H\_CMPT\_COAL\_BUF\_DEPTH (0xBE4)

- $\cdot$  tick\_val = 25

- $\cdot$  tick\_cnt = 5

- TX/RX API burst size = 64, ring depth = 2048. The driver should update TX/RX PIDX in batches of 64.

- PCIe MPS = 256 bytes, MRRS >= 512 bytes, Extended Tag Enabled, Relaxed Ordering Enabled

- The driver will update the completion CIDX in batches of 64 to reduce number of MMIO writes before updating the C2H PIDX

- The driver should update the H2C PIDX in batches of 64, and also update for the last descriptor of the scatter gather list.

- C2H context:

- bypass = 0 (Internal mode)

- frcd\_en = 1

- omega = 1

- $\cdot$  wbk\_en = 1

- . irq\_en = irq\_arm = int\_aggr = 0

- C2H prefetch context:

- omega

- bypass = 0

- valid = 1

- C2H CMPT context:

- en\_stat\_desc = 1

- en\_int = 0 (Poll\_mode)

- . int\_aggr = 0 (Poll mode)

- . trig\_mode = 5

- counter\_idx = corresponding to 64

- timer\_idx = corresponding to 3  $\mu$ s

- o valid = 1

- H2C context:

- bypass = 0 (Internal mode)

- omega frcd\_en = 0

- o fetch\_max = 0

- omega = 1

- $\omega$  wbk\_en = 1

- $\omega$  wbi\_chk = 1

- wbi\_intvl\_en = 1

- . irq\_en = 0 (Poll mode)

- . irq\_arm = 0 (Poll mode)

- . int\_aggr = 0 (Poll mode)

For optimal QDMA streaming performance, packet buffers of the descriptor ring should be aligned to at least 256 bytes.

**RECOMMENDED:** Xilinx recommends that you limit the total outstanding descriptor fetch to be less than 8 KB on the PCIe. For example, limit the outstanding credits across all queues to 512 for a 16B descriptor.

#### Performance in Descriptor Bypass Mode

When the design is configured in descriptor bypass mode, all the above setting apply. The following information provides recommendations to improve performance in bypass mode.

- 1. When bypass in h2c\_byp\_in\_st\_sdi ports is set, the QDMA IP generates the status write back for every packet. Xilinx recommends that this port be asserted once in 32 packets, or 64 packets. And if there are no more descriptors left then assert h2c\_byp\_in\_st\_sdiat the last descriptor. This requirement is per queue basis, and applies to AXI4-MM (H2C and C2H) bypass transfers and AXI4-Stream H2C transfers.

- 2. For AXI-Stream C2H Simple bypass mode, the dsc\_crdt\_in\_fence port should be set to 1 for performance reasons. This recommendation assumes the user design already coalesced credits for each queue and sent them to the IP. In internal mode, set the fence bit in the QDMA\_C2H\_PFCH\_CFG\_2 (0xA84) register.

#### **Resources Utilization**

For QDMA Resource Utilization, see Resource Use web page.

# **QDMA Operations**

# **Descriptor Engine**

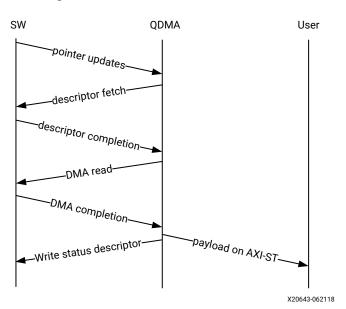

The descriptor engine is responsible for managing the consumer side of the Host to Card (H2C) and Card to Host (C2H) descriptor ring buffers for each queue. The context for each queue determines how the descriptor engine will process each queue individually. When descriptors are available and other conditions are met, the descriptor engine will issue read requests to PCIe to fetch the descriptors. Received descriptors are offloaded to either the descriptor bypass out interface (bypass mode) or delivered directly to a DMA engine (internal mode). When a H2C Stream or Memory Mapped DMA engine completes a descriptor, status can be written back to the status descriptor, an interrupt, and/or a marker response can be generated to inform software and user logic of the current DMA progress. The descriptor engine also provides a Traffic Manager Interface which notifies user logic of certain status for each queue. This allows the user logic to make informed decisions if customization and optimization of DMA behavior is desired.

# **Descriptor Context**

The Descriptor Engine stores per queue configuration, status and control information in descriptor context that can be stored in block RAM or UltraRAM, and the context is indexed by H2C or C2H QID. Prior to enabling the queue, the hardware and credit context must first be cleared. After this is done, the software context can be programmed and the qen bit can be set to enable the queue. After the queue is enabled, the software context should only be updated through the direct mapped address space to update the Producer Index and Interrupt ARM bit, unless the queue is being disabled. The hardware context and credit context contain only status. It is only necessary to interact with the hardware and credit contexts as part of queue initialization in order to clear them to all zeros. Once the queue is enabled, context is dynamically updated by hardware. Any modification of the context through the indirect bus when the queue is enabled can result in unexpected behavior. Reading the context when the queue is enabled is not recommended as it can result in reduced performance.

#### **Related Information**

QDMA\_DMAP\_SEL\_H2C\_DSC\_PIDX[2048] (0x18004) QDMA\_DMAP\_SEL\_C2H\_DSC\_PIDX[2048] (0x18008)

## Software Descriptor Context Structure (0x0 C2H and 0x1 H2C)

The descriptor context is used by the descriptor engine.

Table 5: Software Descriptor Context Structure Definition

| Bit       | Bit Width | Field Name  | Description                                                                                                                                                                                                                  |

|-----------|-----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [255:140] | 116       | reserved    | Reserved. Set to 0s.                                                                                                                                                                                                         |

| [139]     | 1         | int_aggr    | If set, interrupts will be aggregated in interrupt ring.                                                                                                                                                                     |

| [138:128] | [10:0]    | vec         | MSI-X vector used for interrupts for direct interrupt or interrupt aggregation entry for aggregated interrupts.                                                                                                              |

| [127:64]  | 64        | dsc_base    | 4K aligned base address of descriptor ring.                                                                                                                                                                                  |

| [63]      | 1         | is_mm       | This field determines if the queue is Memory Mapped or not. If this field is set, the descriptors will be delivered to associated H2C or C2H MM engine.  1: Memory Mapped 0: Stream                                          |

| [62]      | 1         | mrkr_dis    | If set, disables the marker response in internal mode. Not applicable for C2H ST.                                                                                                                                            |

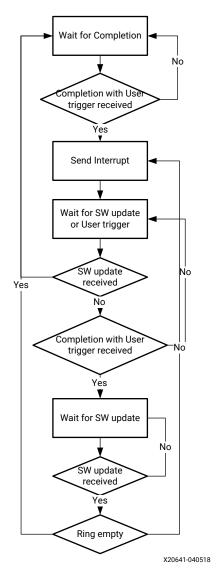

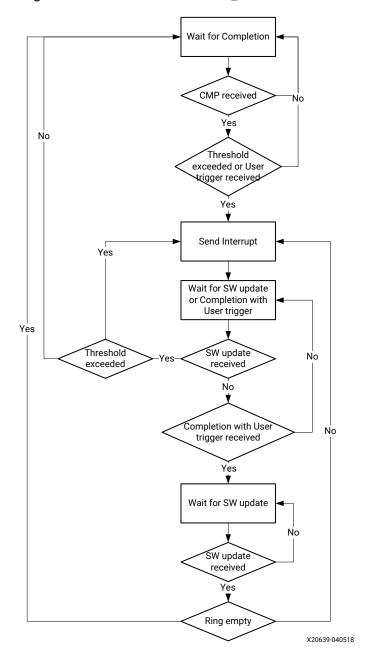

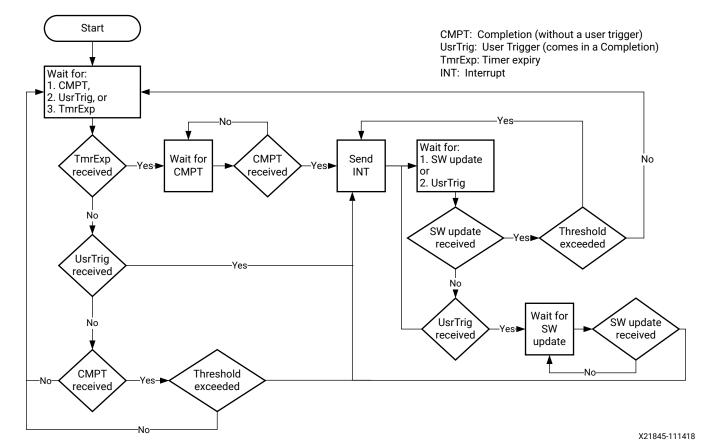

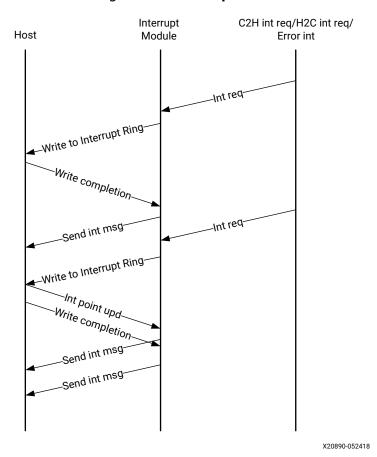

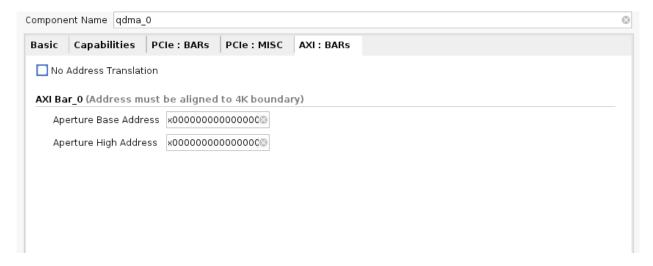

| [61]      | 1         | irq_req     | Interrupt due to error waiting to be sent (waiting for irq_arm). This bit should be cleared when the queue context is initialized.  Not applicable for C2H ST.                                                               |