概述

此開發版當前暫不提供。

請考慮將 PicoZed 作為備選方案。

现金网博e百 描述

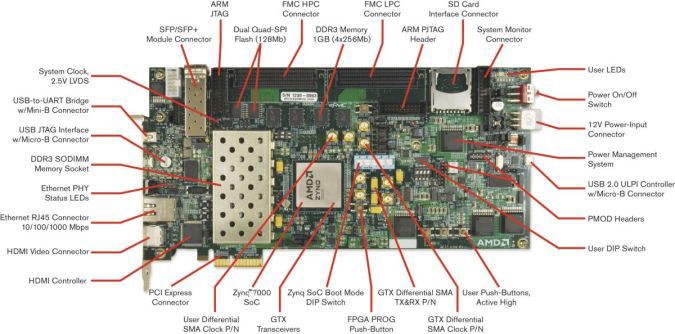

Zynq™ 7000 SoC ZC706 評估套件包含硬件,設計工具, IP 核 以及預驗證參考設計的所有基本元件,包括一個目標設計,可實現完整的嵌入式處理平台和基於收發器的設計-包含 PCIe 。 隨套件提供預驗證參考設計和行業標準 FPGA 夾層連接器(FMC),能夠利用子卡實現升級和定製。請查看 PetaLinux 軟件開發套件頁麵,了解 AMD 處理係統的信息。

主要特性與優勢

- 使用 Zynq 7000 SoC 對嵌入式應用進行快速原型設計以實現優化

- 硬件、設計工具、IP、以及預驗證參考設計

- 演示嵌入式設計,麵向視頻通道

- 高級存儲接口

- 1GB DDR3 組件存儲

- 1GB DDR3 SODIM 存儲器

- 實現 PCIe Gen2x4、SFP+ 和 SMA 對、USB OTG、 UART、 IIC 的串行連接

- 支持包含 Dual ARM Cortex-A9 核處理器的嵌入式處理

- 使用 10-100-1000 Mbps Ethernet (RGMII) 開發網絡應用

- 使用 HDMI 輸出實現視頻顯示應用

- 擴展 I/O, 包含 FPGA Mezzanine Card (FMC) 接口

特色 AMD 器件

包含符合 ROHS 的 ZC706,包括 XC7Z045 FFG900 – 2 SoC

| 邏輯單元 | 350 |

|---|---|

| Block RAM (Mb) | 19.1 |

| DSP Slice | 900 |

| 最大 I/O 引腳 | 362 |

| 最大收發器數量 | 16 |

现金网博e百 信息

開發板特性

包含 ZC706 評估板

通信與網絡

- PCIe Gen2x4

- SFP+ 和 SMA 對

- RGMII 千兆以太網 (PS)

- USB OTG 1 (PS) - 主機 USB

- IIC 總線頭/HUB (PS)

- 支持 CAN 喚醒的 1 CAN (PS)

- USB UART (PS)

擴展連接器

- 第一個 FMC LPC 擴展端口 (1個 GT 接口和 34 對 LVDS 的 LA 總線)

- 第二個 FMC HPC 擴展端口 (8個 GT 接口和 34 對 LVDS 的 LA 總線 – 無 HA 或 HB 總線)

- 雙重 Pmod(與 LED 共享 8 個 I/O)

- 單個 Pmod (4 I/O)

- IIC 支持 8個I/O 訪問

控製 & I/O

- 2個用戶按鈕開關/DIP 開關、2個用戶 LED

- IIC 支持 GPIO 訪問

- SDIO (SD 卡槽)

- 3個用戶按鈕開關2個用戶按鈕開關

- IIC 支持 8個I/O 訪問

- IIC 支持 WTClock 訪問

時鍾技術

- 33MHz PS 係統時鍾

- 200MHz PL 振蕩器(單端與差分)

- 用於外部時鍾(差分)的 SMA 接口

- 帶有2個 SMA 連接器的 GTX 參考時鍾端口

- OBSAI/CPRI - SFP+ 接收時鍾

- EXT 配置時鍾

配置

- 板上配置電路

- 2X16MB 四重 SPI 閃存

- SDIO 卡接口(啟動)

- PC4 和 20 引腳 JTAG 端口

存儲器

- DDR3 組件內存 1GB (PS)

- DDR3 SODIM 存儲1GB (PL)

- 2X16MB 四重 SPI 閃存 (config)

- IIC - 1 KB EEPROM

模擬

- AMS 接口 (模擬) 係統監控器,亦可用於外部傳感器

功耗

- 12 V 牆上適配器

- 具有電流測量功能的電源

附件

ZC706 評估板

包含 XC7Z045 FFG900 -2 SoC

整套 Vivado® Design Suite: Design Edition

Zynq 7000 XC7Z045 SoC 節點鎖定 & 器件鎖定,包含 1 年更新及3d狮王轮盘游戏下载

以太網電纜

ATX PCIe Minifit Jr 電源適配器

USB 適配器

USB Mini 電纜

HDMI 電纜

USB Micro 電纜

電源電線和適配器

資源

設計工具與下載

| 名稱 | 說明 | 許可證類型 | 文件 |

|---|---|---|---|

| Vivado Design Suite | AMD Vivado™ Design Suite 是一款以 IP 核及係統為中心的設計環境,這一全新構建的環境具有革新意義,能夠顯著加速 FPGA 和 SoC 係列器件的設計效率。 | XCZU7EV MPSoC FPGA 的鎖定節點及鎖定器件,1 年內可更新 | 下載 Vivado Design Suite |

| Vitis 統一軟件平台 | 針對 AMD 平台提供全麵的嵌入式軟件開發、硬件加速及調試工具套件。 | 免費 | 下載 Vitis 嵌入式平台 |

| PetaLinux 工具 | 將 Linux 操作係統配置、構建並部署至 AMD 平台。 | 免費 | 下載 Petalinux 工具 |