AMD Vitis™ HLS

- 設計工具

- Vitis 統一軟件平台

- Vitis HLS

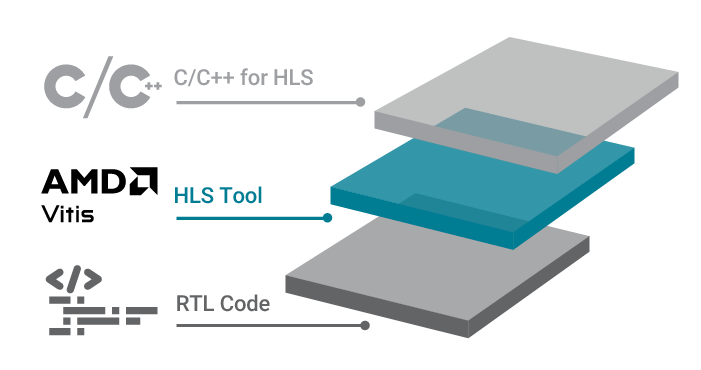

Vitis™ HLS 工具允許用戶通過將 C/C++ 函數綜合成 RTL,輕鬆創建複雜的 FPGA 算法。Vitis HLS 工具與 Vivado™ Design Suite(用於綜合、布置和布線)及 Vitis™ 統一軟件平台(用於所有異構係統設計和應用)高度集成。

- 使用 Vitis HLS 流程,用戶可針對 C 代碼應用指令,創建專門用於所需實現方案的 RTL。

- 不僅可從 C 語言源代碼創建多個設計架構,而且還可啟用用於高質量 Correct-by-Construction RTL 的路徑。

- C 語言仿真可用於驗證設計,支持比基於 RTL 的傳統仿真更快的迭代。

- Vitis HLS 工具具有一係列豐富的分析及調試工具,其可促進設計優化。

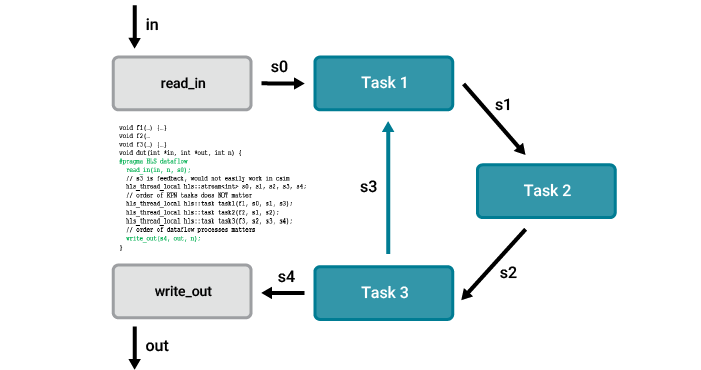

編程模型

Vitis HLS 編程模型

Vitis™ HLS C 語言代碼旨在充分利用 AMD FPGA 架構提供的優勢和特征。

Vitis HLS 工具支持並行編程構念,可為所需的實現方案建模。這些構念包括:

- 允許流程並行的 HLS 任務

- 允許數據並行的 HLS 矢量

- 允許在並行任務之間進行通信的 HLS 流程

- 綜合編譯指示可用來控製結果。這些編譯指示包括流水線、展開、陣列分區以及接口協議等。

- 如欲了解更多詳情,敬請參閱 Vitis 高層次綜合用戶指南的“HLS 編程人員指南”部分。

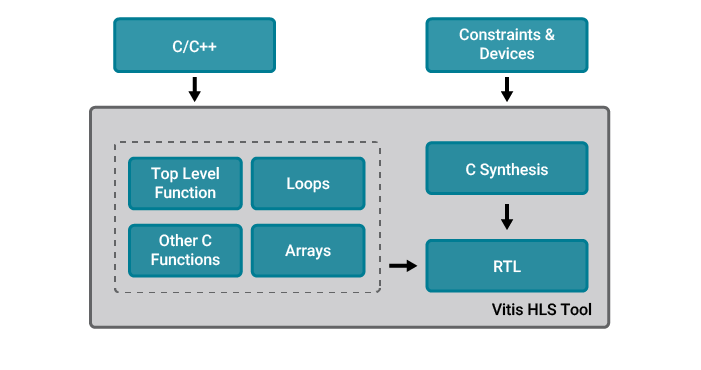

C 至 RTL 的轉換

Vitis HLS 工具將對 C 語言代碼的不同部分執行不同的綜合:

- C/C++ 代碼的頂層函數參數不僅可綜合成 RTL I/O 端口,而且還可通過接口綜合硬件協議自動執行。

- 其它 C 語言函數將綜合至 RTL 模塊中,保持設計層級。

- C 語言函數循環保持滾動或流水線,以提高性能。

- C 語言代碼陣列可指向任何內存資源,如 BRAM、LUTRAM 和 URAM 等。

- 時延、初始化間隔、循環迭代時延和資源利用率等性能指標可使用綜合報告查看。

- Vitis HLS 工具的編譯指示及優化指令允許配置 C/C++ 代碼的綜合結果。

C 至 RTL 的綜合

仿真和驗證

仿真和驗證

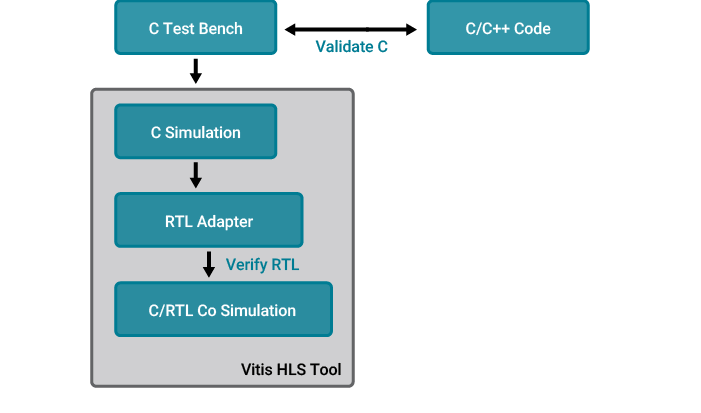

Vitis HLS 工具內建仿真流程,可加速驗證進程:

- C 語言仿真將驗證 C 代碼的功能性。該步驟很快,並會使用 C 語言測試台。

- C/RTL 聯合仿真可重複使用 C 語言測試平台,對所生成的 RTL 進行驗證:驗證 RTL 在功能上是否與 C 語言源代碼相同。

- 該流程集成分析、調試和波形查看功能,以及流行的仿真器支持。

IP 導出

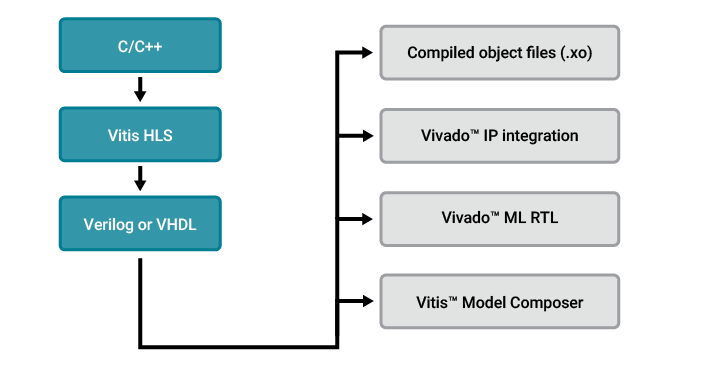

Vitis HLS 工具的輸出是一個 RTL 執行方案,其可打包成一個已編譯的目標文件 (.xo),也可導出至 RTL IP:

- 編譯的目標文件 (.xo) 可用於創建硬件加速函數,用於 Vitis 應用開發流程。

- 該 RTL IP 的使用方式有三種:

- 添加了對 Vivado™ IP Integrator 工具的使用

- 在 Vivado IDE 中作為 RTL 模塊導入

- 在 Vitis Model Composer 中作為單個模塊集,用於 DSP 應用

IP 導出

2024.1 版本亮點

- 新模板程序可簡化圖像和視頻過濾器的 HLS C++ 代碼

全新庫函數向導進入 AMD Vitis 庫 github 庫

- 為 AMD Vivado 設計工具創建“求解器”及“視覺 ”(OpenCV 兼容)IP

- 運行可用庫範例

內存接口 (ap_memory) 的 Pragma 現在可捆綁 AMD Vivado IP Integrator 的端口

最新 HLS 組件比較可並列顯示兩個以上組件的數據記錄

支持用用戶提供程序 RTL 代碼來替換 C++ 函數(黑盒流程)

代碼分析器現在可分解 C++ 結構成員,微調性能分析

適用於 HLS 全局 FSM 編碼和安全狀態選擇的新用戶控製

在 C-Simulation 期間訪問 Clang 消毒器,以執行地址及初始化檢查

2023.2 版本亮點

- 麵向 HLS 組件的最新 Vitis™ 統一 IDE

- 最新 Vitis HLS 許可證要求

- 用於在運行 C 綜合之前獲得性能估計的最新代碼分析器特性

- AXI 接口的增強功能:

- HLS AXI Stream 側通道支持的增強

- 支持用戶可配置的 AXI 主機高速緩存

- 其它增強功能:

- 最新代碼複雜性報告,可在 C 綜合過程中識別設計尺寸問題

- 編譯時間縮短:與 2023.1 相比,2023.2 的平均編譯時間縮短了 20% *

* 基於 2023 年 8 月 10 日在 1000 個 Vitis L2/L3 代碼庫設計間的測試,Vitis HLS 版本 2023.2 與 Vitis HLS 2023.1 相比。測試時的係統配置:Intel Xeon E5-2690 v4(2.6GHz CPU)、256GB RAM、RedHat Enterprise Linux 8.6。實際性能會有所不同。係統生產商可能會改變配置,進而會有不同的結果。-VGL-04

2023.1 版本亮點

- 性能提升*:與 2022.2 相比,2023.1 的平均時延縮短了 5.2%

- 在 Vitis HLS 工具中下載、查看和實例化 L1 庫函數的簡單方法。觀看視頻

- 在 Vitis HLS 工具中增強了對 AXI 事務處理及猝發報告的支持

*截至 2023 年 2 月 12 日,停止在所有 1208 個 Vitis L1 庫 C 代碼設計上執行基準測試。所有設計都使用一個支持 2P Intel Xeon E5-2690 CPU 的係統運行,該 CPU 支持 CentOS Linux,啟用了 SMT 並禁用了 Turbo Boost。預計硬件配置不會影響軟件測試結果。結果可能會因軟件及固件設置和配置而異 — VGL-03

2022.2 版本亮點

- 為數據處理應用編寫“任務級並行”代碼的新方法

- 用戶可使用新的 hls::task 函數顯式定義任務級並行性

- 為純設計數據流(例如分組交換)建模更輕鬆

- 性能與時序增強

- 工具自動推斷展開、流水線、陣列分區以及內聯編譯指示,可提高性能

- 分析與調試增強

- 在所生成的 RTL 代碼中從 C 語言來源綜合打印語句的新特性

- 仿真 RTL 時,允許跟蹤代碼模塊的執行以及一個變量的值

- 簡單易用

-

FFT 和 FIR IP 現在支持 hls::stream 接口

2022.1 版本亮點

- 全新時間線跟蹤查看器

- 顯示設計中所有幸存函數的運行時配置文件,即那些被轉換為模塊的函數

- 查看數據流區域在聯合仿真後的行為特別實用。原生 Vitis™ HLS — 不再需要啟動 xsim 波形查看器

- 全新性能編譯指示

- HLS 您的吞吐量目標是使用 #pragma hls 性能

- 如果可能的話,HLS 將嚐試使用最少的資源來達標

- HLS 將指示所執行的轉換,而且如果不能達標,還將指示限製因素

- 為模塊數據流類型提供陣列分區支持

- hls::stream 增強,其中每個元素都是一個陣列

- 可用於將大型陣列處理分解成更小的流水線片段

2021.2 版本亮點

- 用戶控製的猝發推斷

- 用戶可采用新引入的手動猝發優化功能

- 添加一個新的‘hls::burst_maxi’類型來為手動控製猝發行為提供支持 提供全新 HLS API,與新類類型一起使用。

- 在 HLS 設計中,用戶需要了解 AXI AMBA 協議和硬件事務處理層麵的建模

- 時序與 QoR 增強

- 提高了 HLS 時序估算精度。 當 HLS 報告時序收斂時,Vivado™ RTL 綜合也應該預期滿足時序要求

- EoU 增強

- 在 C 語言綜合報告中添加接口適配器報告

- 用戶需要知道接口適配器對其設計的資源影響

- 接口適配器具有可影響設計 QoR 的可變屬性

- 在綜合報告中添加新章節,以顯示編譯指示列表和編譯指示警告

- 分析與報告增強

- 全新鼠標拖動式縮放功能

- 全新概覽特性,不僅可顯示全圖,而且用戶還可放大整體圖形的各部位

- 所有函數及環路都與它們的仿真數據一起顯示

- 現已在仿真後提供一個新的時間軸跟蹤查看器該查看器不僅可顯示設計的運行時概況,而且還允許用戶保留在 Vitis HLS GUI 中

2021.1 版本亮點

- GUI 中的全新“流程導航器”有助於快速訪問流程階段和報告。環境“綜合、分析、調試”視窗合並到一個默認的通用環境中

- BIND_OP 和 BIND_STORAGE 指令的的全新綜合報告部分

- 全新的綜合後文本報告將反映 GUI 綜合報告中提供的信息

- IP 導出和 Vivado™ 實現運行小部件使用各種選項進行重新設計,可將設置和約束文件傳遞給 Vivado

- 全新函數調用圖查看器可查看函數和環路,其可使用可選熱圖高亮顯示,以檢查 II、時延或 DSP/BRAM 利用熱點

- Versal™ 時序校準以及 DSP 模塊本地浮點運算的全新控製(config_op 的 -precision 選項)

- 可替代的可刷新流水線選項已得到改進(自由運行流水線又稱“frp”)

- 在 Vitis 中,重塑 m_ax 接口應該通過 hls::vector 類型完成

- s_axilite 和 m_axi 數據存儲的全新自定義選項可以是“auto”、“uram”、“bram”或“lutram”,您可以在設計中調整 RAM 利用率

- 在 Vitis 中,為內核引入了一種全新的連續(又稱“永不停止”)運行模式

- 已重新設置 axi_lite 輔助時鍾選項

INSA Lyon 的 Emeraude 研究團隊正在努力為嵌入式音頻係統開發新的信號處理技術。該團隊使用 AMD Vitis HLS 工具實現了超低時延的音頻 DSP 程序。點擊這裏,進一步了解 Vitis HLS 工具如何幫助該團隊在 DSP 至 FPGA 的音頻編譯過程中實現超低時延。

Customer Case Study

使用 Vitis HLS 實現音頻 DSP 至 FPGA 的超低時延

INSA Lyon 的 Emeraude 研究團隊正在努力為嵌入式音頻係統開發新的信號處理技術。該團隊使用 AMD Vitis HLS 工具實現了超低時延的音頻 DSP 程序。點擊這裏,進一步了解 Vitis HLS 工具如何幫助該團隊在 DSP 至 FPGA 的音頻編譯過程中實現超低時延。

Customer Case Study

使用 Vitis HLS 加速設計空間探索

“依我看,AMD Vitis™ HLS 工具的主要優勢是設計空間探索特性。您可通過使用優化指令(流水線以及展開等),用適當的時間生成不同的架構及實現方案。如果使用 VHDL/Verilog 手動編碼,則無法做到這一點。Vitis HLS 的一個良好特性是可以對 HDL 代碼進行聯合仿真和驗證,以確保 HDL 代碼功能正確。”Frank Kesel 博士,德國普福爾茨海姆大學教授

客戶案例研究