- 技術解決方案

- AI 引擎技術

AI 引擎:滿足新一代應用的計算需求

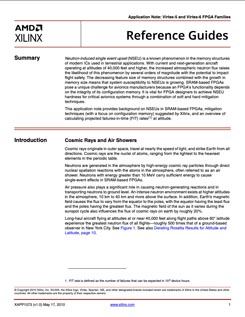

在許多不斷發展的活躍市場上,如 5G 蜂窩網絡、數據中心、汽車和工業等,應用在保持電源效率的同時,不斷推動日益提升的計算加速的發展。隨著摩爾定律和登納德縮放比例定律不再遵循其傳統發展規律,隻向新一代芯片節點發展,就不能像前幾代现金网博e百 那樣,以更好的性能提供更低功耗及更低成本的優勢。

為了應對無線波束形成和機器學習推斷等新一代應用需求的非線性增長,AMD 開發了一項全新的創新處理技術 AI 引擎,該技術是 Versal™ 自適應計算加速平台 (ACAP) 架構的一部分。

AI 引擎架構

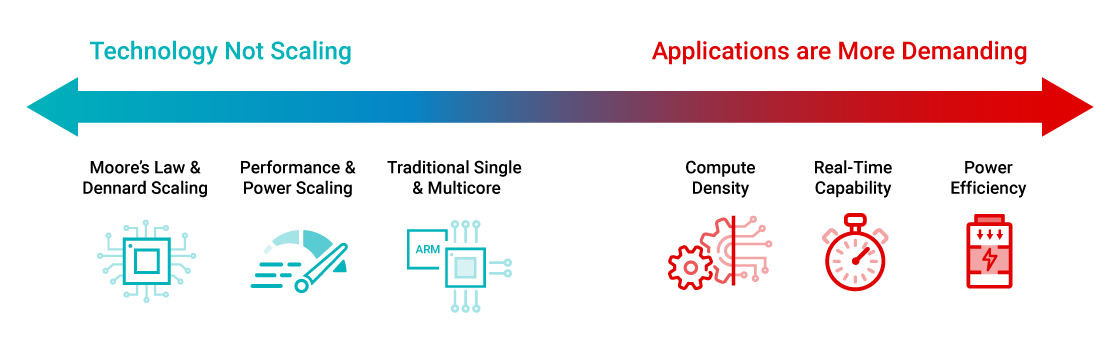

AI 引擎按照由多個 AI 引擎塊組成的 2D 陣列架構,允許在 Versal 现金网博e百 組合中提供可擴展性極高的解決方案,在統一器件中提供的 AI 引擎從 10 秒到 100 秒不等,可充分滿足廣泛應用的計算需求。现金网博e百 優勢包括:

軟件可編程

- C 語言可編程,幾分鍾內即可完成編譯

- 基於庫的設計滿足 ML 框架開發人員的應用需求

確定性

- 專用指令及數據存儲器

- 與 DMA 引擎配對的專用連接,可實現使用 AI 引擎塊之間的連接進行預期數據移動

效率

- 與傳統可編程邏輯 DSP 和 ML 實現方案相比,可將芯片麵積計算密度提高達 8 倍,從而在額定值情況下,可將功耗降低 40%

AI 引擎板塊

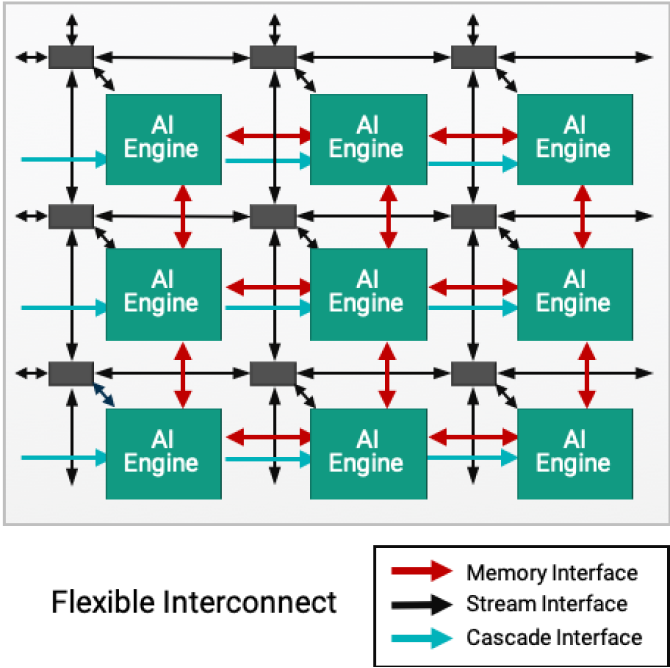

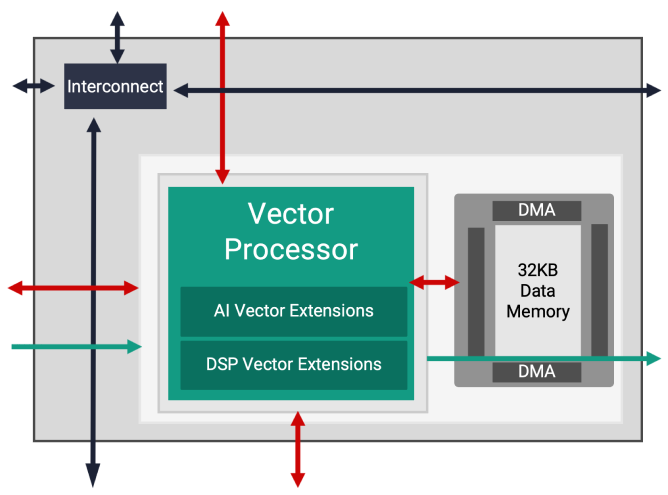

每個 AI 引擎塊都包含一個超長指令字 (VLIW) 的單指令多數據 (SIMD) 向量處理器,其針對機器學習和高級信號處理應用進行了優化。AI 引擎處理器運行頻率可達 1.3GHz,能實現非常高效的高吞吐量和低時延功能。

與 VLIW 向量處理器一樣,每個塊都包含存儲所需指令的程序存儲器、用於存儲數據、權重、激活和係數的本地數據存儲器、一個 RISC 標量處理器和不同的互連模式,可處理不同類型的數據通信。

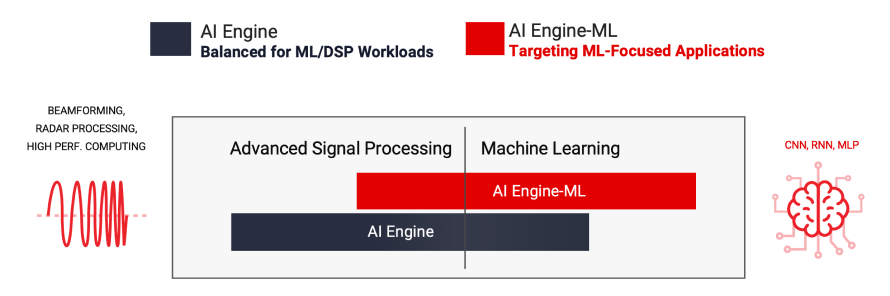

異構工作負載:信號處理和機器學習推斷加速

AMD 提供兩種類型的 AI 引擎:AIE 和 AIE-ML(機器學習 AI 引擎),與上一代 FPGA 相比,這兩種 AI 引擎的性能都得到了顯著提升。AIE 可加速一組更加平衡的工作負載,包括 ML 推斷應用和波束形成及雷達等高級信號處理工作負載,以及需要大量濾波和轉換的其它工作負載。通過增強的 AI 向量擴展以及在 AI 引擎陣列中引入共享內存塊,AIE-ML 可為以 ML 推斷為中心的應用提供優於 AIE 的性能,而 AIE 則可為某些類型的高級信號處理提供優於 AIE-ML 的性能。

AI 引擎 Tile

AIE 可加速一組平衡的工作負載,包括 ML 推斷應用,以及波束形成、雷達、FFT 和濾波器等高級信號處理工作負載。

支持大量工作負載/應用

- 適用於通信的高級 DSP

- 視頻與圖像處理

- 機器學習推斷

原生支持真實、複雜的浮點數據類型

- INT8/16 定點

- CINT16、CINT32 複雜定點

- FP32 浮動數據點

用於實現 FFT 和 FIR 的專用硬件特性

- 每個塊 128 個 INT8 MAC

查閱 Versal ACAP AI 引擎架構手冊,了解更多信息。

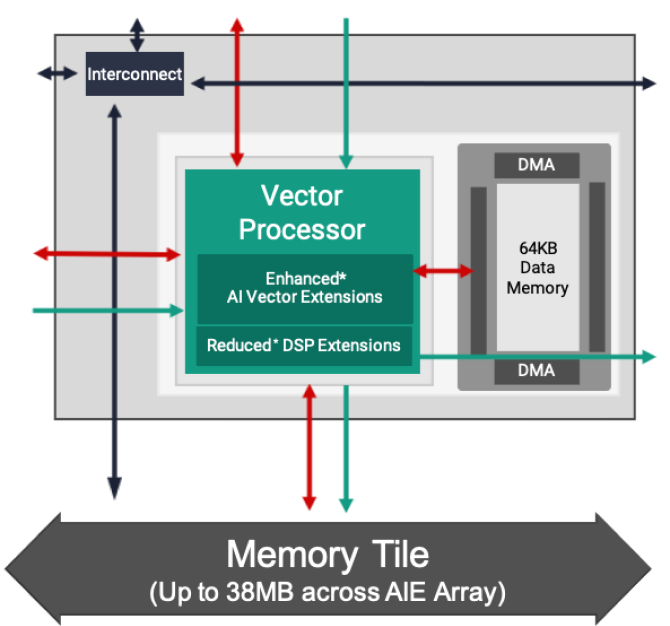

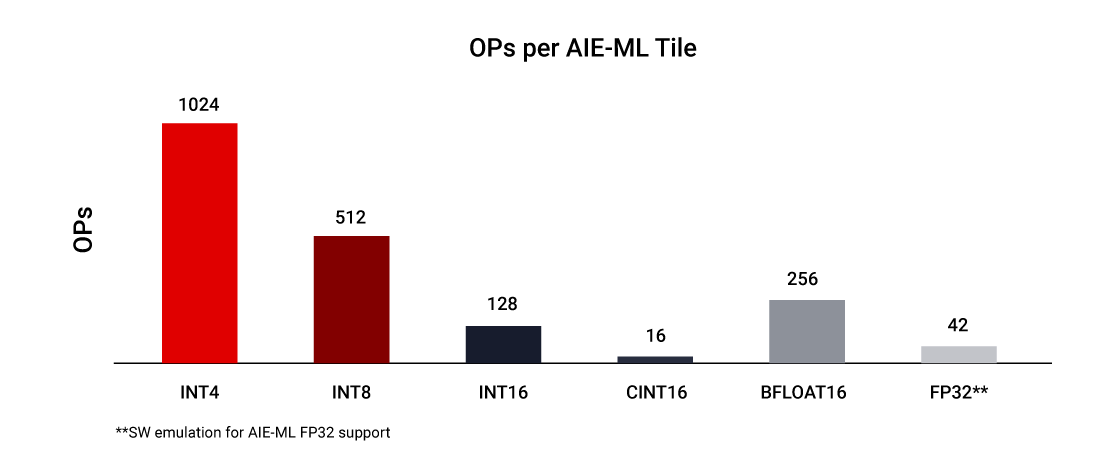

AI Engine-ML 塊

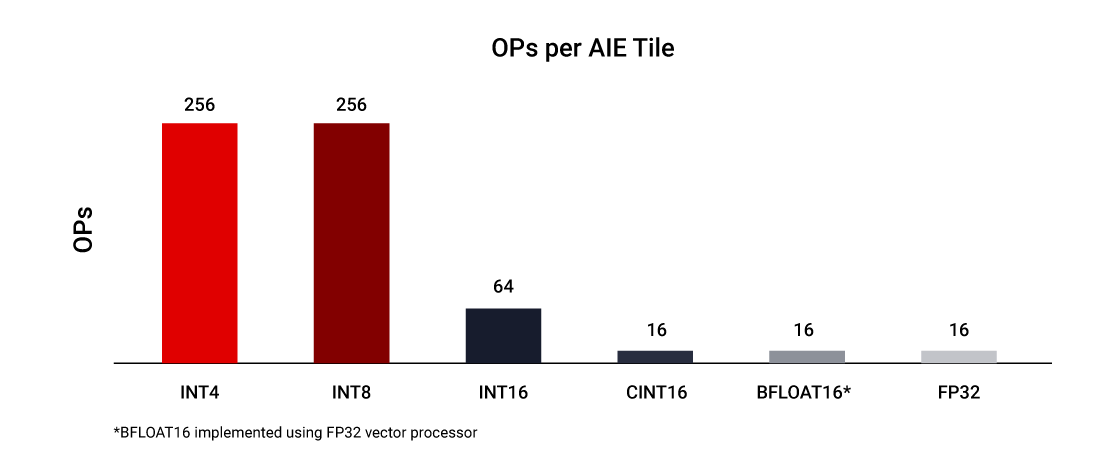

AI Engine-ML 架構針對機器學習進行了優化,可增強計算內核和內存架構。這些優化塊可執行 ML 和高級信號處理,不再強調 INT32 和 CINT32 支持(在雷達處理中常見),以增強以 ML 為重點的應用。

為 ML 數據類型提供更廣泛的原生支持

- INT4

- BFLOAT16

以更低的時延實現 2 倍的 ML 計算

- 每個塊 512 個 INT4 MAC

- 每個塊 256 個 INT8 MAC

增加了用於本地化數據的陣列內存

- 每個塊的本地數據內存增加了 1 倍 (64kB)

- 用於高帶寬共享內存訪問的全新內存塊 (512kB)

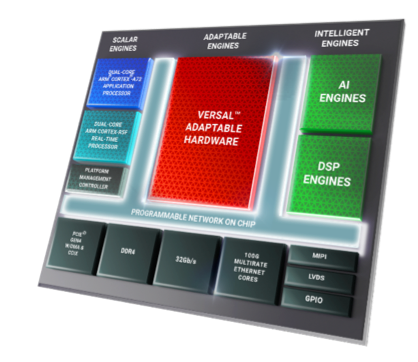

異構平台的一部分

AI 引擎加上靈活應變的引擎(可編程邏輯)和標量引擎(處理器子係統),可在 Versal 自適應計算加速平台 (ACAP) 上形成一個緊密集成的異構架構,其可在軟硬件層麵進行修改,動態滿足廣泛應用及工作負載的需求。

Versal ACAP 架構零基礎構建,具有原生的軟件可編程性,支持高度靈活的、每秒多兆位可編程片上網絡 (NoC),無縫集成所有引擎和重要接口,因此平台不僅在啟動時可用,而且軟件開發人員、數據科學家和硬件開發人員等都可對其進行輕鬆編程。

在 Versal 係列中提供

AI 引擎和 AI Engine-ML 架構在 Versal AI Core 和 Versal AI Edge 器件中提供。

Versal AI Core 係列

Versal AI Core 係列通過 AI 引擎提供突破性的 AI 推斷和無線加速,該引擎提供的計算性能比當前服務器級 CPU 高 100 倍以上。 Versal AI Core ACAP 在 Versal 现金网博e百 係列中具有最高的計算能力,其應用包括數據中心計算、無線波束形成、視頻和圖像處理以及無線測試設備。

Versal AI 邊緣係列

較之領先的 GPU,Versal AI Edge 係列可在邊緣節點提供 4 倍的 AI 單位功耗性能,並適用於功率和熱受限環境。Versal AI Edge 係列不僅提供從智能傳感器到邊緣計算的業界一流可擴展现金网博e百 組合,而且還提供與實時係統中的人工智能創新一起發展的硬件靈活應變性,可加速從傳感器到人工智能,再到實時控製的整個應用。

AI 引擎適用於各種異構工作負載,從無線處理到位於雲端、網絡和邊緣的機器學習,無所不包

數據中心計算

分析圖像和視頻,是數據中心數據爆炸的核心。 工作負載的卷積神經網絡 (CNN) 特性需要數量龐大的計算,通常達數萬億次。AI 引擎經過優化,能夠以低成本和低功耗的方式高效提供這種計算密度。

5G 無線處理

5G 能夠以極低的時延提供前所未有的吞吐量,因此需要顯著增加信號處理。AI 引擎可以在較低的功耗下在無線電單元 (RU) 和分布式單元 (DU) 中執行這種實時信號處理,例如在海量 MIMO 麵板中使用的高級波束形成技術,以提高網絡容量。

ADAS 和自動駕駛

CNN 是一種深度前饋人工神經網絡,常用於分析視覺圖像。隨著計算機廣泛用於從自動駕駛汽車到視頻監控的各個領域,CNN 現已變得至關重要。AI 引擎可為散熱外殼緊密的小型封裝提供所需的計算密度和高效率。

航空航天與國防

在小型封裝中將基於矢量的強大 DSP 引擎與 AI 引擎進行完美融合,可實現各種航空航天與國防係統,其中包括相控陣雷達、預警 (EW)、軍事通信和無人機等。 AI 引擎支持異構工作負載,包括信號處理、信號調節以及多任務負載的 AI 推斷,可提供符合這些任務關鍵型係統的積極尺寸、重量和功耗 (SWaP) 需求的計算效率。

工業

包括機器人和機器視覺在內的工業應用將傳感器融合與 AI/ML 相結合,可在信息源邊緣和附近執行數據處理。盡管環境存在不確定性,但 AI 引擎仍能提高這些實時係統的性能和可靠性。

無線測試設備

實時 DSP 被廣泛用於無線通信測試設備中。AI 引擎架構完美適合處理所有類型的協議實現,包括從數字前端到波束成形和基帶的 5G。

醫療

利用 AI 引擎的醫療保健應用包括用於醫療超聲的高性能並行波束形成器、用於 CT 掃描儀的背投、用於 MRI 機器的圖像重構卸載,以及用於各種臨床及診斷應用的輔助診斷等。

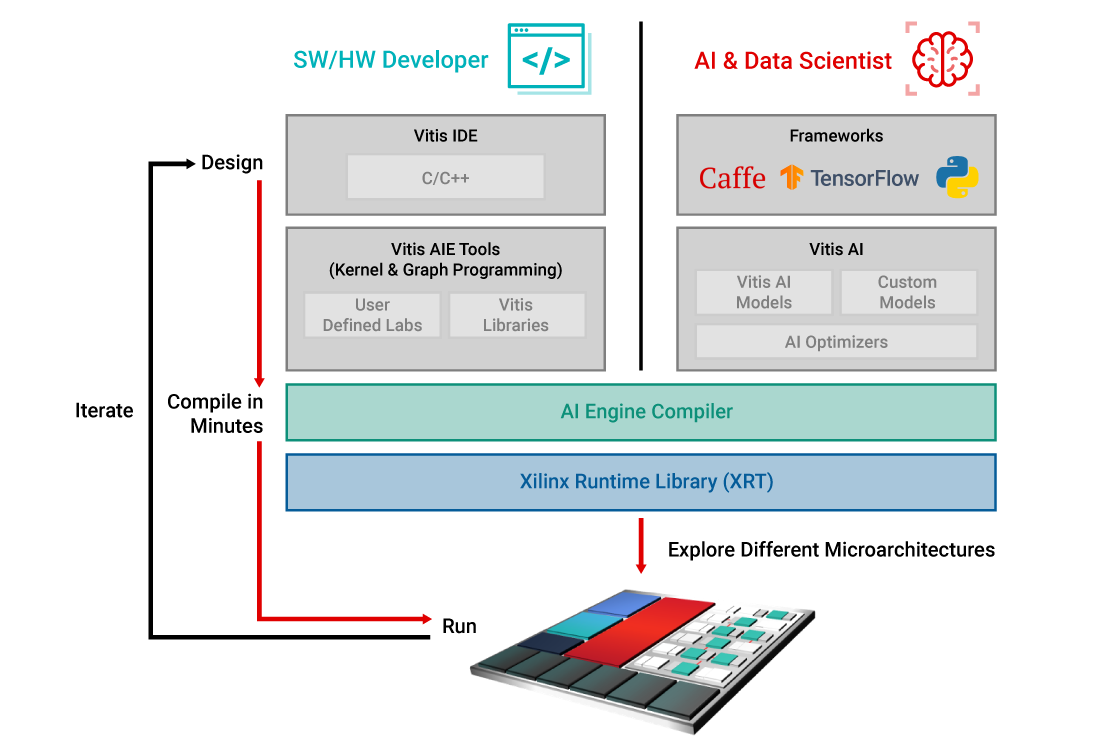

AI 引擎開發流程

AI 引擎零基礎構建,不僅軟件可編程,而且硬件也具有靈活應變性。對於所有開發人員來說,有兩種不同的設計流程可充分發揮這些計算引擎的性能,不僅能在幾分鍾內完成編譯,而且還可快速探索不同的微型架構。這兩種設計流程包括:

- 用於 C/C++ 風格編程的 Vitis™ IDE,適合軟硬件開發人員

- Vitis AI,適用於基於 AI/ML 框架的流程,目標是 AI 及數據科學家

麵向軟硬件開發人員和數據科學家的 AI 引擎庫

AMD 通過 Vitis 加速庫提供的預構建內核可實現:

- 縮短開發周期

- 跨 AI 引擎架構的可移植性,例如 AIE 至 AIE-ML

- 快速了解並采用 AI 引擎技術

- 設計人員能夠集中精力,開發其自己的專有算法

軟硬件開發人員不僅可直接編寫基於矢量處理器的 AI 引擎程序,而且還可在適當的情況下使用 C/C++ 代碼調用預構建庫。

DSP

線性代數

通信

ML Lib

BLAS

視覺與圖像

數據移動器

AI 數據科學家停留在其熟悉的框架環境中,如 PyTorch 和 TensorFlow,可通過 Vitis AI 調用預先構建的 ML 覆蓋,不必直接為 AI 引擎編程。

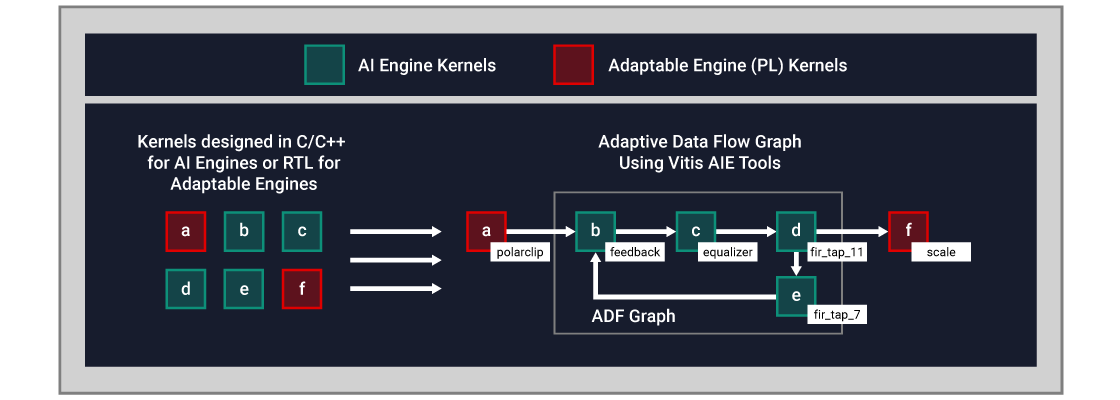

軟硬件開發人員的數據流編程

AI 引擎架構基於數據流技術。處理元件采用有 10 到 100 個模塊的陣列提供,可在整個計算單元中創建統一的程序。對於設計人員來說,嵌入指令來指定整個模塊間的並行機製非常乏味,而且幾乎是不可能的。為了克服這一困難,AI 引擎設計分兩個階段進行:先進行單個內核開發,然後通過自適應數據流 (ADF) 圖形創建,將這些內核連接在整個應用中。

Vitis 提供統一的 IDE 操作空間,可使用 C/C++ 編程代碼和 ADF 圖形設計實現 AI 引擎單內核。具體來說,設計人員可:

- 使用 C/C++ 和 Vitis 庫開發內核,描述特定的計算函數

- 通過 Vitis AI 引擎工具,使用自適應數據流圖 (ADF) 連接內核

默認情況下,單個內核運行在單個 AI 引擎塊上。然而,多個內核可以運行在同一個 AI 引擎塊上,共享應用允許的處理時間。

下麵是一個概念示例:

- AI 引擎內核采用 C/C++ 開發

- 靈活應變引擎中的內核或可編程邏輯 (Pl) 在 RTL 或 Vitis 高層次綜合 (HLS) 中編寫

- 兩個引擎的內核之間的數據流通過 ADF 圖執行

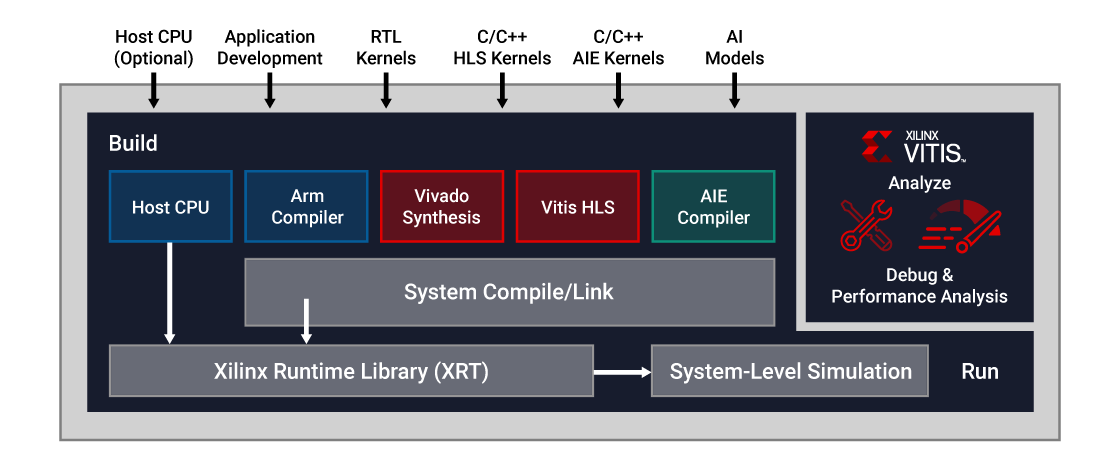

將 AI 引擎設計整合在一個完整的係統中

在 Vitis IDE 中,AI 引擎設計可納入較大的完整係統中,從而可將設計的各個方麵整合在統一的流程中,其中可進行仿真、硬件仿真、調試和部署。

- 專用編譯器主要針對 Versal 平台的不同異構引擎,其中包括標量引擎(Arm® 子係統)、靈活應變的引擎(可編程邏輯)和智能引擎(DSP 和 AI 引擎)等。

- 然後,係統編譯器將這些單獨的代碼塊鏈接在一起,並創建所有的互連,以優化其間的數據移動以及自定義內存層級。此外,該工具套件還可為基於 PCIe® 的係統集成 x86 工具鏈。

- 為了部署應用,Xilinx Runtime 軟件 (XRT) 還提供了與平台及操作係統無關的 API,用於管理設備配置、內存和主機至設備的數據傳輸,以及加速器執行。

- 裝配好第一個原型設計後,可以使用快速事務處理級仿真器或周期精確仿真器仿真應用,並使用性能分析器優化應用,以獲得最佳分區和性能。

- 對結果感到滿意時,就可部署在 Versal 平台上。

下載 Vitis 統一軟件平台

AMD Vitis™ 統一軟件平台提供使用硬件加速技術的全麵內核開發套件與庫。下載 Vitis 統一軟件平台 >

訪問 Vitis GitHub 和 AI 引擎開發頁麵,查看廣泛的 AI 引擎教程,這將幫助您了解技術特性和設計方法。

AI 引擎工具(編譯器和仿真器)都集成在 Vitis IDE 中,需要額外的專用許可證。聯係本地 AMD 銷售代表,了解有關如何訪問 AI 引擎工具和許可的更多信息,您也可以查看聯係銷售表單。

下載 Vitis Model Composer

AMD Vitis Model Composer 是一款基於模型的設計工具,可在 Simulink® 和 MATLAB® 環境中快速進行設計探索。它可促進 AI 引擎 ADF 圖形開發和係統級測試,允許用戶將 RTL 和 HLS 塊與 AI 引擎內核和/或圖形整合在相同的仿真中。利用 Simulink 和 MATLAB 中的信號生成與可視化特性,DSP 工程師可在熟悉的環境中完成設計和調試。如需了解如何將 Versal AI 引擎與 Vitis Model Composer 結合使用,請訪問 AI 引擎資源頁麵 。

購買評估套件或部署平台

VCK190 套件基於 Versal™ AI Core 係列,可幫助設計者使用 AI 引擎和 DSP 引擎開發解決方案,與當前服務器級 CPU 相比,該解決方案可提供超過 100 倍的計算性能。此評估套件擁有快速啟動設計所需的所有組件。

了解更多有關 Versal AI Core 係列 VCK190 評估套件的信息 >

此外,還提供基於 PCIe 的 VCK5000 開發卡,其具有帶 AI 引擎的 Versal Versal AI Core 器件,該開發卡針對數據中心的高吞吐量 AI 推斷精心打造。

培訓課程

AMD 培訓和學習資源提供了實用的實踐技能和基礎知識,可助力真人百家乐游戏开户 在下一個 Versal ACAP 開發項目中充分發揮生產力。課程包括:

Versal ACAP 設計中心

從解決方案規劃到係統集成和驗證,AMD 可從 Versal ACAP 相關的大量資源中自定義並提供所需的資源,以最大程度地提升設計效率。訪問 Versal ACAP 設計中心,以獲取滿足您設計需求的最新內容,並探索 AI 引擎功能和設計方法。

自適應計算 YouTube 頻道

訪問自適應計算開發人員 YouTube 頻道,了解精彩的開發人員對開發人員內容,在這裏,您將找到 AI 引擎視頻和教程,其中包括從頭到尾的 AI 引擎係列。

博客係列 - AI 引擎設計和調試

這個具有極高洞察力的博客係列將帶您逐步了解 AI 引擎的設計流程。從啟動 Vitis 工具,到用設計圖設計第一個 AIE 內核,再到仿真、調試以及在實際硬件中運行,無一例外。

技術文檔

Versal ACAP 設計中心:AI 引擎

該 Versal™ ACAP 設計中心是一個全新的優化選項,可瀏覽基於設計階段的 Versal ACAP 文檔,在這裏您可以了解有關 AI 引擎技術和設計流程的更多詳情。

探索 Versal ACAP 設計中心 / AI 引擎開發