# DMA/Bridge Subsystem for PCI Express v4.1

# **Product Guide**

Vivado Design Suite

PG195 (v4.1) November 16, 2022

Xilinx is creating an environment where employees, customers, and partners feel welcome and included. To that end, we're removing noninclusive language from our products and related collateral. We've launched an internal initiative to remove language that could exclude people or reinforce historical biases, including terms embedded in our software and IPs. You may still find examples of non-inclusive language in our older products as we work to make these changes and align with evolving industry standards. Follow this <u>link</u> for more information.

# Table of Contents

| Chapter 1: Introduction                  |     |

|------------------------------------------|-----|

| -<br>Features                            | 4   |

| IP Facts                                 |     |

| Chapter 2: Overview                      | 6   |

| Feature Summary                          | 8   |

| Applications                             | 8   |

| Unsupported Features                     | 9   |

| Limitations                              | 9   |

| Licensing and Ordering                   |     |

| Chapter 3: Product Specification         | 12  |

| Standards                                |     |

| Performance and Resource Utilization     | 12  |

| Minimum Device Requirements              |     |

| Configurable Components of the Subsystem | 13  |

| XDMA Operations                          | 19  |

| Port Descriptions                        |     |

| Register Space                           |     |

| Chapter 4: Designing with the Subsystem  | 77  |

| Clocking and Resets                      | 77  |

| Tandem Configuration                     | 78  |

| Chapter 5: Design Flow Steps             | 83  |

| Customizing and Generating the Subsystem |     |

| Constraining the Subsystem               | 95  |

| Simulation                               |     |

| Synthesis and Implementation             | 100 |

| Chapter 6: Example Design                | 101 |

| Available Example Designs                |     |

| Customizing and Generating the Example Design                                                                                                                                                                                                                                                                                                                                                                                          |                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

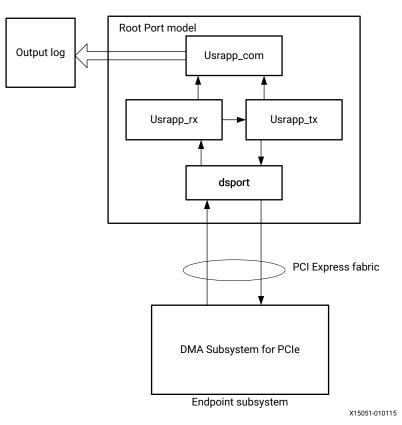

| Chapter 7: Test Bench                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

| Root Port Model Test Bench for Endpoint                                                                                                                                                                                                                                                                                                                                                                                                |                   |

| Appendix A: GT Locations                                                                                                                                                                                                                                                                                                                                                                                                               | 121               |

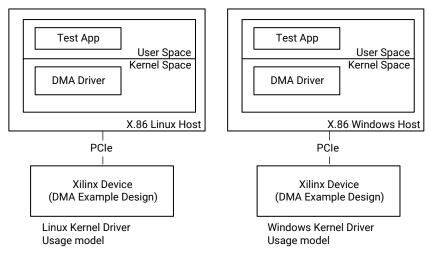

| Appendix B: Application Software Development                                                                                                                                                                                                                                                                                                                                                                                           | 122               |

| Device Drivers                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| Linux Device Driver                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

| Using the Driver                                                                                                                                                                                                                                                                                                                                                                                                                       | 123               |

| Interrupt Processing                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

| Example H2C Flow                                                                                                                                                                                                                                                                                                                                                                                                                       | 124               |

| Example C2H Flow                                                                                                                                                                                                                                                                                                                                                                                                                       | 125               |

| Appendix C: Upgrading                                                                                                                                                                                                                                                                                                                                                                                                                  | 126               |

| New Parameters                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| New Ports                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |

| Appendix D: Debugging                                                                                                                                                                                                                                                                                                                                                                                                                  | 129               |

| Appendix D: Debugging<br>Finding Help on Xilinx.com                                                                                                                                                                                                                                                                                                                                                                                    |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                        | 129               |

| Finding Help on Xilinx.com                                                                                                                                                                                                                                                                                                                                                                                                             | 129<br>130        |

| Finding Help on Xilinx.com<br>Debug Tools<br>Hardware Debug                                                                                                                                                                                                                                                                                                                                                                            | 129<br>130<br>131 |

| Finding Help on Xilinx.com<br>Debug Tools                                                                                                                                                                                                                                                                                                                                                                                              |                   |

| Finding Help on Xilinx.com<br>Debug Tools<br>Hardware Debug<br>Appendix E: Using the Xilinx Virtual Cable to Debug                                                                                                                                                                                                                                                                                                                     |                   |

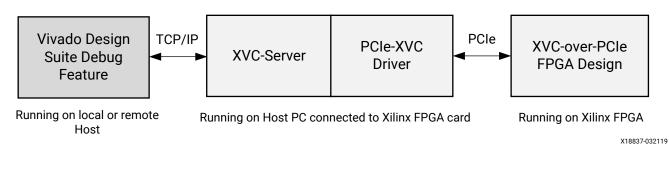

| Finding Help on Xilinx.com<br>Debug Tools<br>Hardware Debug<br>Appendix E: Using the Xilinx Virtual Cable to Debug<br>Overview                                                                                                                                                                                                                                                                                                         |                   |

| Finding Help on Xilinx.com<br>Debug Tools<br>Hardware Debug<br>Appendix E: Using the Xilinx Virtual Cable to Debug<br>Overview<br>Host PC XVC-Server Application                                                                                                                                                                                                                                                                       |                   |

| Finding Help on Xilinx.com<br>Debug Tools<br>Hardware Debug<br>Appendix E: Using the Xilinx Virtual Cable to Debug<br>Overview<br>Host PC XVC-Server Application<br>Host PC XVC-over-PCIe Driver                                                                                                                                                                                                                                       |                   |

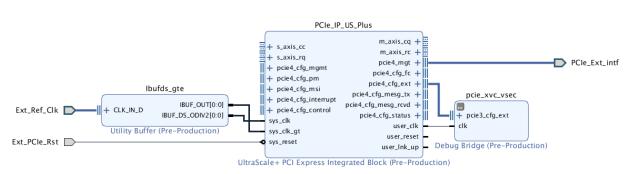

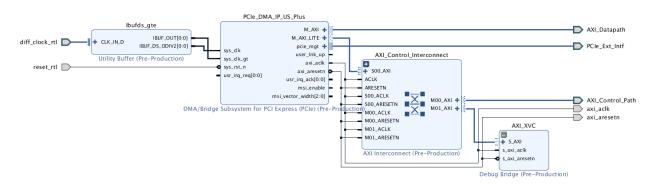

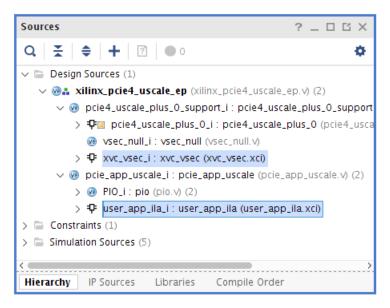

| Finding Help on Xilinx.com<br>Debug Tools<br>Hardware Debug<br>Appendix E: Using the Xilinx Virtual Cable to Debug<br>Overview<br>Host PC XVC-Server Application<br>Host PC XVC-Server Application<br>Host PC XVC-over-PCIe Driver<br>XVC-over-PCIe Enabled FPGA Design<br>Using the PCIe-XVC-VSEC Example Design                                                                                                                      |                   |

| Finding Help on Xilinx.com<br>Debug Tools<br>Hardware Debug<br>Appendix E: Using the Xilinx Virtual Cable to Debug<br>Overview<br>Host PC XVC-Server Application<br>Host PC XVC-Server Application<br>Host PC XVC-over-PCIe Driver<br>XVC-over-PCIe Enabled FPGA Design                                                                                                                                                                |                   |

| Finding Help on Xilinx.com<br>Debug Tools<br>Hardware Debug<br>Appendix E: Using the Xilinx Virtual Cable to Debug<br>Overview<br>Host PC XVC-Server Application<br>Host PC XVC-Server Application<br>Host PC XVC-over-PCIe Driver<br>XVC-over-PCIe Enabled FPGA Design<br>Using the PCIe-XVC-VSEC Example Design<br>Appendix F: Additional Resources and Legal Notices                                                                |                   |

| Finding Help on Xilinx.com<br>Debug Tools<br>Hardware Debug<br>Appendix E: Using the Xilinx Virtual Cable to Debug<br>Overview<br>Host PC XVC-Server Application<br>Host PC XVC-Server Application<br>Host PC XVC-over-PCIe Driver<br>XVC-over-PCIe Enabled FPGA Design<br>Using the PCIe-XVC-VSEC Example Design<br>Appendix F: Additional Resources and Legal Notices<br>Xilinx Resources.                                           |                   |

| Finding Help on Xilinx.com<br>Debug Tools<br>Hardware Debug<br>Appendix E: Using the Xilinx Virtual Cable to Debug<br>Overview<br>Host PC XVC-Server Application<br>Host PC XVC-Server Application<br>Host PC XVC-over-PCIe Driver<br>XVC-over-PCIe Enabled FPGA Design<br>Using the PCIe-XVC-VSEC Example Design<br>Appendix F: Additional Resources and Legal Notices<br>Xilinx Resources<br>Documentation Navigator and Design Hubs |                   |

# AMDA XILINX

# Chapter 1

# Introduction

The Xilinx<sup>®</sup> DMA/Bridge Subsystem for PCI Express<sup>®</sup> (PCIe<sup>®</sup>) implements a high performance, configurable Scatter Gather DMA for use with the PCI Express<sup>®</sup> 2.1 and 3.x Integrated Block. The IP provides a choice between an AXI4 Memory Mapped or AXI4-Stream user interface.

This IP optionally also supports a PCIe AXI Bridge mode which is enabled for only UltraScale+™ devices. For details about PCIe AXI Bridge mode operation, see AXI Bridge for PCI Express Gen3 Subsystem Product Guide (PG194).

This document covers DMA mode operation only.

**Note:** For details about the Versal ACAP subsystem, refer to the Versal ACAP DMA and Bridge Subsystem for PCI Express Product Guide (PG344).

## Features

- Supports UltraScale+<sup>™</sup>, UltraScale<sup>™</sup>, Virtex<sup>®</sup>-7 XT Gen3 (Endpoint), and 7 series 2.1 (Endpoint) Integrated Blocks for PCIe. 7A15T and 7A25T are not supported

- Support for 64, 128, 256, 512-bit datapath (64, and 128-bit datapath only for 7 series Gen2 IP)

- 64-bit source, destination, and descriptor addresses

- Up to four host-to-card (H2C/Read) data channels (up to two for 7 series Gen2 IP)

- Up to four card-to-host (C2H/Write) data channels (up to two for 7 series Gen2 IP)

- Selectable user interface

- 。 Single AXI4 memory mapped (MM) user interface

- 。 AXI4-Stream user interface (each channel has its own AXI4-Stream interface)

- AXI4 Master and AXI4-Lite Master optional interfaces allow for PCIe traffic to bypass the DMA engine

- AXI4-Lite Slave to access DMA status registers

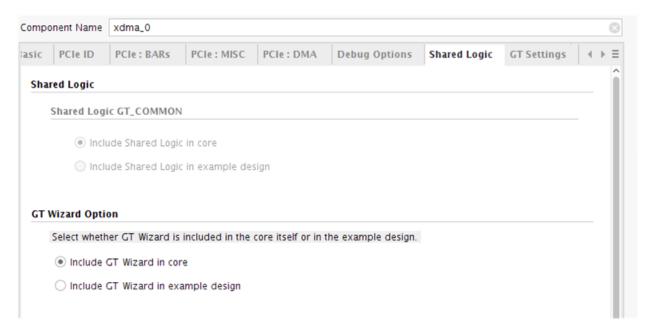

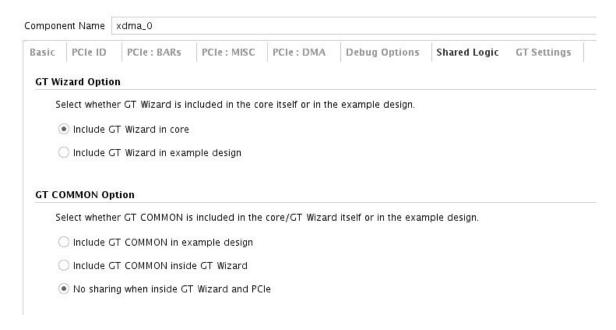

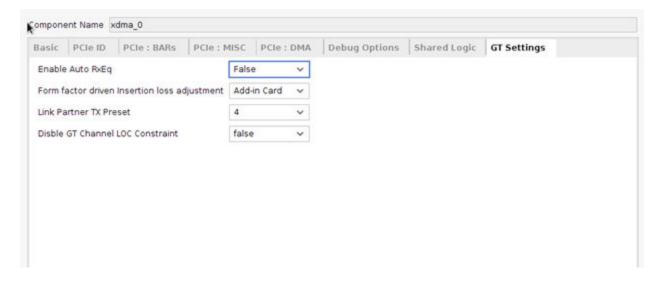

- Scatter Gather descriptor list supporting unlimited list size

- 256 MB max transfer size per descriptor

- Legacy, MSI, and MSI-X interrupts

- Block fetches of contiguous descriptors

- Poll Mode

- Descriptor Bypass interface

- Arbitrary source and destination address

- Parity check or Propagate Parity on AXI bus (not available for 7 series Gen2 IP)

# **IP Facts**

| LogiCORE™ IP Facts Table                                                            |                                                                             |  |  |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| Subsystem Specifics                                                                 |                                                                             |  |  |

| Supported Device Family <sup>1</sup> UltraScale+, UltraScale, 7 series Gen2 devices |                                                                             |  |  |

| Supported User Interfaces                                                           | AXI4 MM, AXI4-Lite, AXI4-Stream                                             |  |  |

| Resources                                                                           | See Resource Utilization web page.                                          |  |  |

|                                                                                     | Provided with Subsystem                                                     |  |  |

| Design Files                                                                        | Encrypted System Verilog                                                    |  |  |

| Example Design                                                                      | Verilog                                                                     |  |  |

| Test Bench                                                                          | Verilog                                                                     |  |  |

| Constraints File                                                                    | XDC                                                                         |  |  |

| Simulation Model                                                                    | Verilog                                                                     |  |  |

| Supported S/W Driver                                                                | Linux and Windows Drivers <sup>2</sup>                                      |  |  |

|                                                                                     | Tested Design Flows <sup>3</sup>                                            |  |  |

| Design Entry                                                                        | Vivado® Design Suite                                                        |  |  |

| Simulation                                                                          | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |  |

| Synthesis                                                                           | Vivado synthesis                                                            |  |  |

| Support                                                                             |                                                                             |  |  |

| Release Notes and Known Issues                                                      | Master Answer Record: AR 65443                                              |  |  |

| All Vivado IP Change Logs                                                           | Master Vivado IP Change Logs: 72775                                         |  |  |

| Xilinx Support web page                                                             |                                                                             |  |  |

#### Notes:

- 1. For a complete list of supported devices, see the  $\mathsf{Vivado}^{\texttt{®}}$  IP catalog.

- 2. For details, see Appendix B: Application Software Development and AR 65444.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

- 4. For Versal ACAP, refer to Versal ACAP DMA and Bridge Subsystem for PCI Express Product Guide (PG344).

# Chapter 2

# AMDA XILINX

# Overview

The DMA/Bridge Subsystem for PCI Express<sup>®</sup> (PCIe<sup>®</sup>) can be configured to be either a highperformance direct memory access (DMA) data mover or a bridge between the PCI Express and AXI memory spaces.

- DMA Data Mover: As a DMA, the core can be configured with either an AXI (memory mapped) interface or with an AXI streaming interface to allow for direct connection to RTL logic. Either interface can be used for high performance block data movement between the PCIe address space and the AXI address space using the provided character driver. In addition to the basic DMA functionality, the DMA supports up to four upstream and downstream channels, the ability for PCIe traffic to bypass the DMA engine (Host DMA Bypass), and an optional descriptor bypass to manage descriptors from the FPGA fabric for applications that demand the highest performance and lowest latency.

- Bridge Between PCle and AXI Memory: When configured as a PCle Bridge, received PCle packets are converted to AXI traffic and received AXI traffic is converted to PCle traffic. The bridge functionality is ideal for AXI peripherals needing a quick and easy way to access a PCI Express subsystem. The bridge functionality can be used as either an Endpoint or as a Root Port. PCle Bridge functionality is only supported for UltraScale+<sup>™</sup> devices. For Bridge only option and for 7 series non-XT device, you should use AXI Memory Mapped to PCI Express (PCle) Gen2. For details see, AXI Memory Mapped to PCI Express (PCle) Gen2 LogiCORE IP Product Guide (PG055). For 7 series XT and UltraScale device, you should use AXI Bridge for PCI Express Gen3. For details, see AXI Bridge for PCI Express Gen3 Subsystem Product Guide (PG194).

This document covers DMA mode operation only.

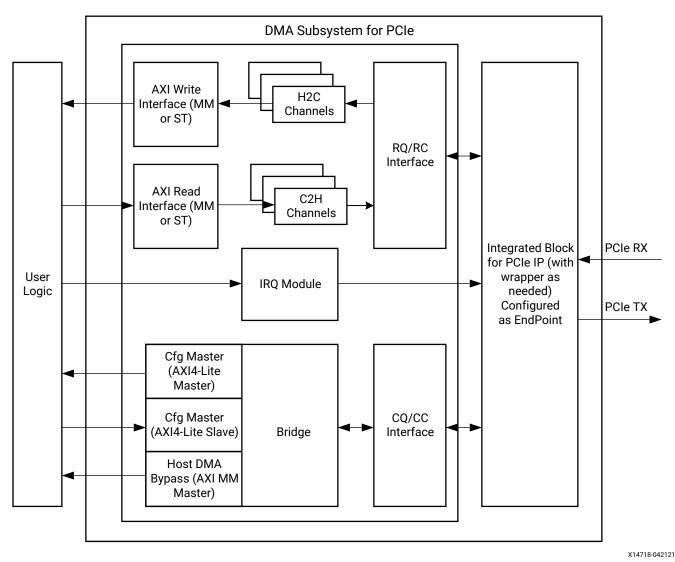

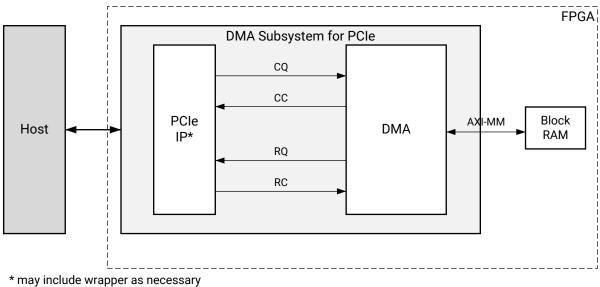

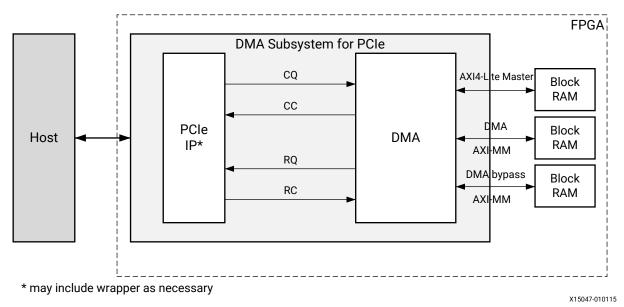

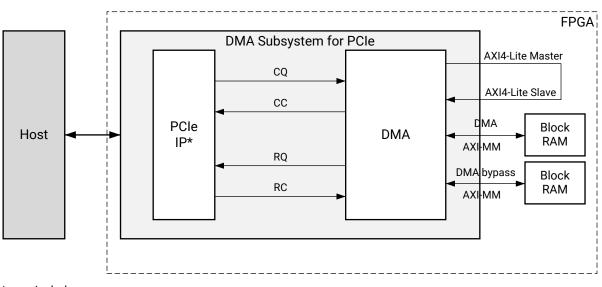

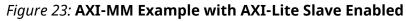

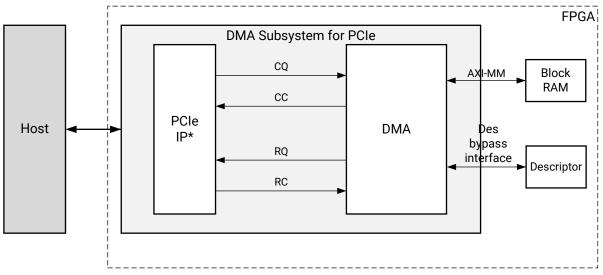

Figure 1: DMA/Bridge Subsystem for PCI Express® Overview

This diagram refers to the Requester Request (RQ)/Requester Completion (RC) interfaces, and the Completer Request (CQ)/Completer Completion (CC) interfaces. For more information about these, see the UltraScale+ Devices Integrated Block for PCI Express LogiCORE IP Product Guide (PG213).

## **Feature Summary**

The DMA/Bridge Subsystem for PCI Express<sup>®</sup> allows for the movement of data between Host memory and the DMA subsystem. It does this by operating on 'descriptors' that contain information about the source, destination and amount of data to transfer. These direct memory transfers can be both in the Host to Card (H2C) and Card to Host (C2H) transfers. The DMA can be configured to have a single AXI4 Master interface shared by all channels or one AXI4-Stream interface for each channel enabled. Memory transfers are specified on a per-channel basis in descriptor linked lists, which the DMA fetches from host memory and processes. Events such as descriptor completion and errors are signaled using interrupts. The core also provides up to 16 user interrupt wires that generate interrupts to the host.

The host is able to directly access the user logic through two interfaces:

- **The AXI4-Lite Master Configuration port:** This port is a fixed 32-bit port and is intended for non-performance-critical access to user configuration and status registers.

- The AXI Memory Mapped Master CQ Bypass port: The width of this port is the same as the DMA channel datapaths and is intended for high-bandwidth access to user memory that might be required in applications such as peer-to-peer transfers.

The user logic is able to access the DMA/Bridge Subsystem for PCIe internal configuration and status registers through an AXI4-Lite Slave Configuration interface. Requests that are mastered on this interface are not forwarded to PCI Express.

# Applications

The core architecture enables a broad range of computing and communications target applications, emphasizing performance, cost, scalability, feature extensibility, and mission-critical reliability. Typical applications include:

- Data communications networks

- Telecommunications networks

- Broadband wired and wireless applications

- Network interface cards

- Chip-to-chip and backplane interface cards

- Server add-in cards for various applications

## **Unsupported Features**

The following features of the standard are not supported by this core:

- Tandem Configuration solutions (Tandem PROM, Tandem PCIe, Tandem with Field Updates, PR over PCIe) are not supported for Virtex<sup>®</sup>-7 XT and 7 series Gen2 devices

- Tandem Configuration is not yet supported for Bridge mode in UltraScale+ devices.

- SR-IOV

- ECRC

- Example design not supported for all configurations

- Narrow burst (not supported on the master interface)

- BAR translation for DMA addresses to the AXI4 Memory Mapped interface

# Limitations

## **PCIe Transaction Type**

The PCIe<sup>®</sup> transactions that can be generated are those that are compatible with the AXI4 specification. The following table lists the supported PCIe transaction types.

#### Table 1: Supported PCIe Transaction Types

| ТХ             | RX                  |

|----------------|---------------------|

| MRd32          | MRd32               |

| MRd64          | MRd64               |

| MWr32          | MWr32               |

| MWr64          | MWr64               |

| Msg(INT/Error) | Msg(SSPL,INT,Error) |

| Cpl            | Cpl                 |

| CpID           | CpID                |

## **PCIe Capability**

For the DMA/Bridge Subsystem for PCI Express<sup>®</sup>, only the following PCIe capabilities are supported due to the AXI4 specification:

• 1 PF

- MSI

- MSI-X

- PM

- AER (only PCIe 3.x core)

DMA/Bridge Subsystem for PCI Express® does not support expansion ROM.

## Others

- Only supports the INCR burst type. Other types result in a Slave Illegal Burst (SIB) interrupt.

- No memory type support (AxCACHE)

- No protection type support (AxPROT)

- No lock type support (AxLOCK)

- No non-contiguous byte enable support (WSTRB)

- For 7 series Gen2 IP, PCIe access from the Host system must be limited to 1DW (4 Bytes) transaction only.

Note: Both AXI Bypass and Register access are limited by this restriction.

### PCIe to DMA Bypass Master

- Only issues the INCR burst type

- Only issues the data, non-secure, and unprivileged protection type

- For 7 series Gen2 IP, limited to 1DW (4 Bytes) transaction only

#### User Interrupt in MSI-X Mode

Users need to program a different vector number for each user interrupts in the IRQ Block User Vector Number register to generate acks for all user interrupts. This generates acks for all user interrupts when there are simultaneous interrupts. When all vector numbers are pointing to the same MSI-X entry, there is only one ack.

# **Licensing and Ordering**

This Xilinx<sup>®</sup> IP module is provided at no additional cost with the Xilinx Vivado<sup>®</sup> Design Suite under the terms of the Xilinx End User License. Information about this and other Xilinx IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx IP modules and tools, contact your local Xilinx sales representative.

For more information, visit the DMA Subsystem for PCI Express product page.

# Chapter 3

# **Product Specification**

The DMA/Bridge Subsystem for PCI Express<sup>®</sup> in conjunction with the Integrated Block for PCI Express IP, provides a highly configurable DMA Subsystem for PCIe, and a high performance DMA solution.

## Standards

The DMA/Bridge Subsystem for PCIe is compliant with the following specifications:

- AMBA AXI4-Stream Protocol Specification (ARM IHI 0051A)

- PCI Express Base Specification v2.1 and v3.0

## **Performance and Resource Utilization**

For DMA Perfomance data, see AR 68049.

For DMA Resource Utilization, see Resource Utilization web page.

# **Minimum Device Requirements**

The following table lists the link widths and supported speed for a given speed grade.

#### Table 2: Minimum Device Requirements

| Capability Link Speed             | Capability Link Width | Supported Speed Grades                        |  |

|-----------------------------------|-----------------------|-----------------------------------------------|--|

| UltraScale+™ Architecture (PCIE4) |                       |                                               |  |

| Gen1/Gen2                         | x1, x2, x4, x8, x16   | -1, -1L, -1LV, -2, -2L, -2LV, -3 <sup>1</sup> |  |

|                                   | x1, x2, x4            | -1, -1L, -1LV, -2, -2L, -2LV, -3 <sup>1</sup> |  |

| Gen3                              | x8                    | -1, -2, -2L, -2LV, -3 <sup>1</sup>            |  |

|                                   | x16                   | -1, -2, -2L, -3 <sup>1</sup>                  |  |

| Capability Link Speed                                                   | Capability Link Width | Supported Speed Grades                           |  |  |  |

|-------------------------------------------------------------------------|-----------------------|--------------------------------------------------|--|--|--|

| Virtex <sup>®</sup> UltraScale+™ Devices with HBM (PCIE4C) <sup>2</sup> |                       |                                                  |  |  |  |

| Gen1/Gen2                                                               | x1, x2, x4, x8, x16   | -1, -2, -2L, -2LV, -3                            |  |  |  |

|                                                                         | x1, x2, x4            | -1, -2, -2L, -2LV, -3                            |  |  |  |

| Gen3                                                                    | ×8                    | -1, -2, -2L, -2LV, -3                            |  |  |  |

|                                                                         | x16                   | -1, -2, -2L, -2LV, -3                            |  |  |  |

| Gen4 <sup>6</sup>                                                       | x1, x2, x4, x8        | -2, -2L, -3                                      |  |  |  |

|                                                                         | UltraScale™ Devices   | •                                                |  |  |  |

| Gen1                                                                    | x1, x2, x4, x8        | -1, -1L, -1LV, -1H, -1HV, -2, -3 <sup>3</sup>    |  |  |  |

| Gen2                                                                    | x1, x2, x4, x8        | -1, -1L, -1LV, -1H, -1HV, -2, -3 <sup>3</sup>    |  |  |  |

| Gen3                                                                    | x1, x2, x4            | -1, -1L, -1LV, -1H, -1HV, -2, -3 <sup>3, 4</sup> |  |  |  |

| Gen3                                                                    | x8                    | -2, -3                                           |  |  |  |

|                                                                         | 7 series Gen3 Devices |                                                  |  |  |  |

| Gen1                                                                    | x1, x2, x4, x8        | -1, -1M, -1I, -2, -2L, -2G, -2I, -3              |  |  |  |

| Gen2                                                                    | x1, x2, x4, x8        | -1, -1M, -1I, -2, -2L, -2G, -2I, -3              |  |  |  |

| Gen3                                                                    | x1, x2, x4, x8        | -2, -2L, -2G, -2I, -3                            |  |  |  |

|                                                                         | 7 series Gen2 Devices |                                                  |  |  |  |

| Gen1                                                                    | x1, x2, x4, x8        | -1 <sup>5</sup> , -2 <sup>5</sup> , -3           |  |  |  |

| Conl                                                                    | x1, x2, x4            | -1 <sup>5</sup> , -2 <sup>5</sup> , -3           |  |  |  |

| Gen2                                                                    | x8                    | -2 <sup>5</sup> , -3                             |  |  |  |

#### Table 2: Minimum Device Requirements (cont'd)

Notes:

1. -1L(0.95V), -1LV(0.90V), -2L(0.85V), -2LV(0.72V).

- 2. Virtex<sup>®</sup> UltraScale+<sup>™</sup> devices with high bandwidth memory (HBM) contain both PCIE4 and PCIE4C blocks. Only the PCIE4C blocks support Gen3 x16 in the -2LV speed grade.

- 3. -1L(0.95V), -1LV(0.90V), -1H(1.0V), -1HV(0.95V).

- 4. The Core Clock Frequency option must be set to 250 MHz for -1, -1LV, -1L, -1H and -1HV speed grades.

- 5. Available -1 speed grades are -1M, -1I, -1Q depending on family selected. Available -2 speed grades are -2, -2G, -2I, -2IL, -2L depending on the family selected.

- 6. For Gen4 mode restrictions, see UltraScale+ Devices Integrated Block for PCI Express LogiCORE IP Product Guide (PG213).

# **Configurable Components of the Subsystem**

Internally, the subsystem can be configured to implement up to eight independent physical DMA engines (up to four H2C and four C2H). These DMA engines can be mapped to individual AXI4-Stream interfaces or a shared AXI4 memory mapped (MM) interface to the user application. On the AXI4 MM interface, the DMA/Bridge Subsystem for PCI Express<sup>®</sup> generates requests and expected completions. The AXI4-Stream interface is data-only.

The type of channel configured determines the transactions on which bus:

- A Host-to-Card (H2C) channel generates read requests to PCIe and provides the data or generates a write request to the user application.

- A Card-to-Host (C2H) channel either waits for data on the user side or generates a read request on the user side and then generates a write request containing the data received to PCIe.

The DMA/Bridge Subsystem for PCIe also enables the host to access the user logic. Write requests that reach 'PCIe to DMA bypass Base Address Register (BAR)' are processed by the DMA. The data from the write request is forwarded to the user application through the  $M_{\rm AXI}$  interface.

The host access to the configuration and status registers in the user logic is provided through an AXI master port. These requests are 32-bit reads or writes. The user application also has access to internal DMA configuration and status registers through an AXI slave port.

When multiple channels for H2C and C2H are enabled, transactions on the AXI4 Master interface are interleaved between all selected channels. Simple round robin protocol is used to service all channels. Transactions granularity depends on host Max Payload Size (MPS), page size, and other host settings.

## Target Bridge

The target bridge receives requests from the host. Based on BARs, the requests are directed to the internal target user through the AXI4-Lite master, or the CQ bypass port. After the downstream user logic has returned data for a non-posted request, the target bridge generates a read completion TLP and sends it to the PCIe IP over the CC bus.

In the following tables, the PCIe BARs selection corresponds to the options set in the PCIe BARs tab in the IP Configuration GUI.

| PCIe BARs Selection<br>During IP<br>Customization                                                   | BAR0 (32-bit) BAR1 (32-bit) |                    | BAR2 (32-bit)      |

|-----------------------------------------------------------------------------------------------------|-----------------------------|--------------------|--------------------|

| Default                                                                                             | DMA                         |                    |                    |

| PCIe to AXI Lite Master<br>enabled                                                                  | PCIe to AXI4-Lite Master    | DMA                |                    |

| PCIe to AXI Lite Master and       PCIe to AXI4-Lite Master         PCIe to DMA Bypass       enabled |                             | DMA                | PCIe to DMA Bypass |

| PCIe to DMA Bypass<br>enabled                                                                       | DMA                         | PCIe to DMA Bypass |                    |

#### Table 3: 32-Bit BARs

#### Table 4: 64-Bit BARs

| PCIe BARs Selection<br>During IP<br>Customization            | BAR0 (64-bit)            | BAR2 (64-bit)      | BAR4 (64-bit)      |

|--------------------------------------------------------------|--------------------------|--------------------|--------------------|

| Default                                                      | DMA                      |                    |                    |

| PCIe to AXI Lite Master<br>enabled                           | PCIe to AXI4-Lite Master | DMA                |                    |

| PCIe to AXI Lite Master and<br>PCIe to DMA Bypass<br>enabled | PCIe to AXI4-Lite Master | DMA                | PCIe to DMA Bypass |

| PCIe to DMA Bypass<br>enabled                                | DMA                      | PCIe to DMA Bypass |                    |

Different combinations of BARs can be selected. The tables above list only 32-bit selections and 64-bit selections for all BARs as an example. You can select different combinations of BARs based on your requirements.

#### **Related Information**

PCIe BARs Tab

## H2C Channel

The previous tables represents PCIe to AXI4-Lite Master, DMA, and PCIe to DMA Bypass for 32bit and 64-bit BAR selections. Each space can be individually selected for 32-bits or 64-bits BAR.

The number of H2C channels is configured in the Vivado<sup>®</sup> Integrated Design Environment (IDE). The H2C channel handles DMA transfers from the host to the card. It is responsible for splitting read requests based on maximum read request size, and available internal resources. The DMA channel maintains a maximum number of outstanding requests based on the RNUM\_RIDS, which is the number of outstanding H2C channel request ID parameter. Each split, if any, of a read request consumes an additional read request entry. A request is outstanding after the DMA channel has issued the read to the PCIe RQ block to when it receives confirmation that the write has completed on the user interface in-order. After a transfer is complete, the DMA channel issues a writeback or interrupt to inform the host.

The H2C channel also splits transaction on both its read and write interfaces. On the read interface to the host, transactions are split to meet the maximum read request size configured, and based on available Data FIFO space. Data FIFO space is allocated at the time of the read request to ensure space for the read completion. The PCIe RC block returns completion data to the allocated Data Buffer locations. To minimize latency, upon receipt of any completion data, the H2C channel begins issuing write requests to the user interface. It also breaks the write requests into maximum payload size. On an AXI4-Stream user interface, this splitting is transparent.

When multiple channels are enabled, transactions on the AXI4 Master interface are interleaved between all selected channels. Simple round robin protocol is used to service all channels. Transactions granularity depends on host Max Payload Size (MPS), page size, and other host settings.

## C2H Channel

The C2H channel handles DMA transfers from the card to the host. The instantiated number of C2H channels is controlled in the Vivado<sup>®</sup> IDE. Similarly the number of outstanding transfers is configured through the WNUM\_RIDS, which is the number of C2H channel request IDs. In an AXI4-Stream configuration, the details of the DMA transfer are set up in advance of receiving data on the AXI4-Stream interface. This is normally accomplished through receiving a DMA descriptor. After the request ID has been prepared and the channel is enabled, the AXI4-Stream interface of the channel can receive data and perform the DMA to the host. In an AXI4 MM interface configuration, the request IDs are allocated as the read requests to the AXI4 MM interface are issued. Similar to the H2C channel, a given request ID is outstanding until the write request has been completed. In the case of the C2H channel, write request completion is when the write request has been issued as indicated by the PCIe IP.

When multiple channels are enabled, transactions on the AXI4 Master interface are interleaved between all selected channels. Simple round robin protocol is used to service all channels. Transactions granularity depends on host MaxPayload Size (MPS), page size, and other host settings.

## AXI4-Lite Master

This module implements the AXI4-Lite master bus protocol. The host can use this interface to generate 32-bit read and 32-bit write requests to the user logic. The read or write request is received over the PCIe to AXI4-Lite master BAR. Read completion data is returned back to the host through the target bridge over the PCIe IP CC bus.

## AXI4-Lite Slave

This module implements the AXI4-Lite slave bus protocol. The user logic can master 32-bit reads or writes on this interface to DMA internal registers only. You cannot access the PCIe integrated block register through this interface. This interface does not generate requests to the host.

## Host-to-Card Bypass Master

Host requests that reach the PCIe to DMA bypass BAR are sent to this module. The bypass master port is an AXI4 MM interface and supports read and write accesses.

## **IRQ Module**

The IRQ module receives a configurable number of interrupt wires from the user logic and one interrupt wire from each DMA channel. This module is responsible for generating an interrupt over PCIe. Support for MSI-X, MSI, and legacy interrupts can be specified during IP configuration.

**Note:** The Host can enable one or more interrupt types from the specified list of supported interrupts during IP configuration. The IP only generates one interrupt type at a given time even when there are more than one enabled. MSI-X interrupt takes precedence over MSI interrupt, and MSI interrupt take precedence over Legacy interrupt. The Host software must not switch (either enable or disable) an interrupt type while there is an interrupt asserted or pending.

#### Legacy Interrupts

Asserting one or more bits of usr\_irq\_req when legacy interrupts are enabled causes the DMA to issue a legacy interrupt over PCle. Multiple bits may be asserted simultaneously but each bit must remain asserted until the corresponding usr\_irq\_ack bit has been asserted. After a usr\_irq\_req bit is asserted, it must remain asserted until both corresponding usr\_irq\_ack bit is asserted and the interrupt is serviced and cleared by the Host. This ensures interrupt pending register within the IP remains asserted when queried by the Host's Interrupt Service Routine (ISR) to determine the source of interrupts. The usr\_irq\_ack assertion indicates the requested interrupt has been sent to the PCle block. You must implement a mechanism in the user application to know when the interrupt routine has been serviced. This detection can be done in many different ways depending on your application and your use of this interrupt pin. This typically involves a register (or array of registers) implemented in the user application that is cleared, read, or modified by the Host software when an interrupt is serviced.

After the usr\_irq\_req bit is deasserted, it cannot be reasserted until the corresponding usr\_irq\_ack bit has been asserted for a second time. This indicates the deassertion message for the legacy interrupt has been sent over PCle. After a second usr\_irq\_ack has occurred, the xdma0\_usr\_irq\_req wire can be reasserted to generate another legacy interrupt.

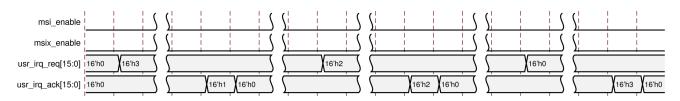

The xdma0\_usr\_irq\_req bit and DMA interrupts can be mapped to legacy interrupt INTA, INTB, INTC, and INTD through the configuration registers. The following figure shows the legacy interrupts.

**Note:** This figure shows only the handshake between xdma0\_usr\_irq\_req and usr\_irq\_ack. Your application might not clear or service the interrupt immediately, in which case, you must keep usr\_irq\_req asserted past usr\_irq\_ack. The figure below shows one possible scenario where usr\_irq\_ackis deasserted at the same cycle for both requests[1:0], which might not be the case in other situations.

## AMDA XILINX

#### Figure 2: Legacy Interrupts

#### MSI and MSI-X Interrupts

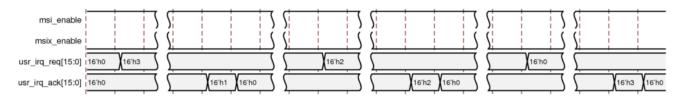

Asserting one or more bits of  $usr\_irq\_req$  causes the generation of an MSI or MSI-X interrupt if MSI or MSI-X is enabled. If both MSI and MSI-X capabilities are enabled, an MSI-X interrupt is generated.

After a usr\_irq\_req bit is asserted, it must remain asserted until the corresponding usr\_irq\_ack bit is asserted and the interrupt has been serviced and cleared by the Host. The usr\_irq\_ack assertion indicates the requested interrupt has been sent to the PCIe block. This will ensure the interrupt pending register within the IP remains asserted when queried by the Host's Interrupt Service Routine (ISR) to determine the source of interrupts. You must implement a mechanism in the user application to know when the interrupt routine has been serviced. This detection can be done in many different ways depending on your application and your use of this interrupt pin. This typically involves a register (or array of registers) implemented in the user application that is cleared, read, or modified by the Host software when an Interrupt is serviced.

Configuration registers are available to map usr\_irq\_req and DMA interrupts to MSI or MSI-X vectors. For MSI-X support, there is also a vector table and PBA table. The following figure shows the MSI interrupt.

Note: This figure shows only the handshake between  $usr\_irq\_req$  and  $usr\_irq\_ack$ . Your application might not clear or service the interrupt immediately, in which case, you must keep  $usr\_irq\_req$  asserted past  $usr\_irq\_ack$ .

#### Figure 3: MSI Interrupts

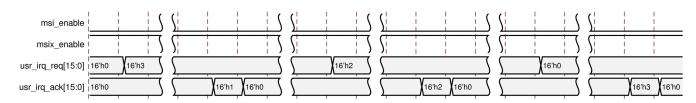

The following figure shows the MSI-X interrupt.

*Note*: This figure shows only the handshake between usr\_irq\_req and usr\_irq\_ack. Your application might not clear or service the interrupt immediately, in which case, you must keep usr\_irq\_req asserted past usr\_irq\_ack.

#### Figure 4: MSI-X Interrupts

For more details, see Interrupt Processing.

## **Config Block**

The config module, the DMA register space which contains PCIe<sup>®</sup> solution IP configuration information and DMA control registers, stores PCIe IP configuration information that is relevant to the DMA/Bridge Subsystem for PCIe. This configuration information can be read through register reads to the appropriate register offset within the config module.

# **XDMA Operations**

## **Quick Start**

At the most basic level, the PCIe<sup>®</sup> DMA engine typically moves data between host memory and memory that resides in the FPGA which is often (but not always) on an add-in card. When data is moved from host memory to the FPGA memory, it is called a Host to Card (H2C) transfer or System to Card (S2C) transfer. Conversely, when data is moved from the FPGA memory to the host memory, it is called a Card to Host (C2H) or Card to System (C2S) transfer.

These terms help delineate which way data is flowing (as opposed to using read and write which can get confusing very quickly). The PCIe DMA engine is simply moving data to or from PCIe address locations.

In typical operation, an application in the host must to move data between the FPGA and host memory. To accomplish this transfer, the host sets up buffer space in system memory and creates descriptors that the DMA engine use to move the data.

The contents of the descriptors will depend on a number of factors, including which user interface is chosen for the DMA engine. If an AXI4-Stream interface is selected, C2H transfers do not use the source address field and H2C fields do not use the destination address. This is because the AXI4-Stream interface is a FIFO type interface that does not use addresses.

If an AXI Memory Mapped interface is selected, then a C2H transfer has the source address as an AXI address and the destination address is the PCIe address. For a H2C transfer, the source address is a PCIe address and the destination address is an AXI address.

The following flow charts show typical transfers for both H2C and C2H transfers when the data interface is selected during IP configuration for an AXI Memory Mapped interface.

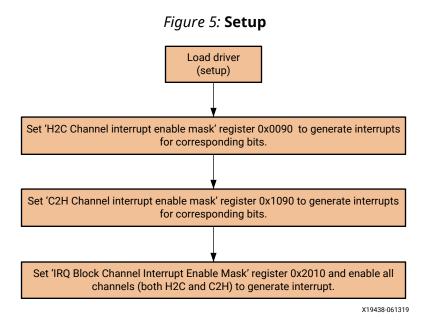

#### Initial Setup For H2C and C2H Transfers

The following figure shows the initial setup for both H2C and C2H transfers.

#### AXI-MM Transfer For H2C

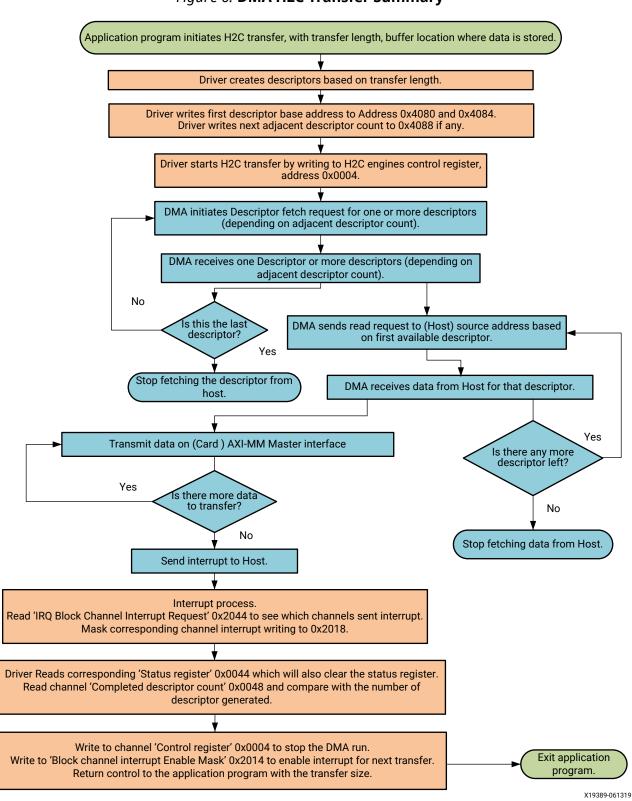

The following figure shows a basic flow chart that explains the data transfer for H2C. The flow chart color coding is as follows: Green is the application program; Orange is the driver; and Blue is the hardware.

Figure 6: DMA H2C Transfer Summary

#### AXI-MM Transfer For C2H

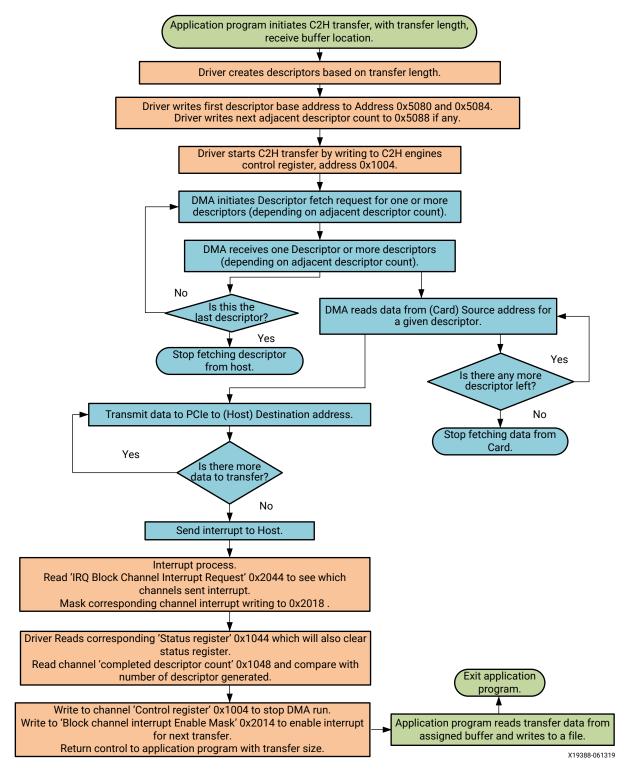

The following figure shows a basic flow chart that explains the data transfer for C2H. The flow chart color coding is as follows: Green is the application program; Orange is the driver; and Blue is the hardware.

#### Figure 7: DMA C2H Transfer Summary

## AMD**7** Xilinx

## Descriptors

The DMA/Bridge Subsystem for PCI Express<sup>®</sup> uses a linked list of descriptors that specify the source, destination, and length of the DMA transfers. Descriptor lists are created by the driver and stored in host memory. The DMA channel is initialized by the driver with a few control registers to begin fetching the descriptor lists and executing the DMA operations.

Descriptors describe the memory transfers that the DMA/Bridge Subsystem for PCIe should perform. Each channel has its own descriptor list. The start address of each channel's descriptor list is initialized in hardware registers by the driver. After the channel is enabled, the descriptor channel begins to fetch descriptors from the initial address. Thereafter, it fetches from the  $Nxt_adr[63:0]$  field of the last descriptor that was fetched. Descriptors must be aligned to a 32 byte boundary.

The size of the initial block of adjacent descriptors are specified with the Dsc\_Adj register. After the initial fetch, the descriptor channel uses the  $Nxt_adj$  field of the last fetched descriptor to determine the number of descriptors at the next descriptor address. A block of adjacent descriptors must not cross a 4K address boundary. The descriptor channel fetches as many descriptors in a single request as it can, limited by MRRS, the number the adjacent descriptors, and the available space in the channel's descriptor buffer.

*Note*: Because MRRS in most host systems is 512 bytes or 1024 bytes, having more than 32 adjacent descriptors is not allowed on a single request. However, the design will allow a maximum 64 descriptors in a single block of adjacent descriptors if needed.

Every descriptor in the descriptor list must accurately describe the descriptor or block of descriptors that follows. In a block of adjacent descriptors, the  $Nxt_adj$  value decrements from the first descriptor to the second to last descriptor which has a value of zero. Likewise, each descriptor in the block points to the next descriptor in the block, except for the last descriptor which might point to a new block or might terminate the list.

Termination of the descriptor list is indicated by the Stop control bit. After a descriptor with the Stop control bit is observed, no further descriptor fetches are issued for that list. The Stop control bit can only be set on the last descriptor of a block.

When using an AXI4 memory mapped interface, DMA addresses to the card are not translated. If the Host does not know the card address map, the descriptor must be assembled in the user logic and submitted to the DMA using the descriptor bypass interface.

| Offset | Fields         |                                                |  |  |  |

|--------|----------------|------------------------------------------------|--|--|--|

| 0x0    | Magic[15:0]    | Magic[15:0] Rsv[1:0] Nxt_adj[5:0] Control[7:0] |  |  |  |

| 0x04   |                | 4'h0, Len[27:0]                                |  |  |  |

| 0x08   | Src_adr[31:0]  |                                                |  |  |  |

| 0x0C   | Src_adr[63:32] |                                                |  |  |  |

#### Table 5: Descriptor Format

#### Table 5: Descriptor Format (cont'd)

| Offset | Fields         |

|--------|----------------|

| 0x10   | Dst_adr[31:0]  |

| 0x14   | Dst_adr[63:32] |

| 0x18   | Nxt_adr[31:0]  |

| 0x1C   | Nxt_adr[63:32] |

#### Table 6: Descriptor Fields

| Offset | Field   | Bit Index | Sub Field | Description                                                                                                                                                                                              |

|--------|---------|-----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0    | Magic   | 15:0      |           | 16'had4b. Code to<br>verify that the driver<br>generated descriptor<br>is valid.                                                                                                                         |

| 0x0    |         | 1:0       |           | Reserved set to 0's                                                                                                                                                                                      |

| 0x0    | Nxt_adj | 5:0       |           | The number of<br>additional adjacent<br>descriptors after the<br>descriptor located at<br>the next descriptor<br>address field.<br>A block of adjacent<br>descriptors cannot<br>cross a 4k boundary.     |

| 0x0    |         | 5, 6, 7   |           | Reserved                                                                                                                                                                                                 |

| 0×0    |         | 4         | EOP       | End of packet for stream interface.                                                                                                                                                                      |

| 0x0    |         | 2, 3      |           | Reserved                                                                                                                                                                                                 |

| 0x0    | Control | 1         | Completed | Set to 1 to interrupt<br>after the engine has<br>completed this<br>descriptor. This<br>requires global<br>IE_DESCRIPTOR_COMP<br>LETED control flag set<br>in the H2C/C2H<br>Channel control<br>register. |

| 0x0    |         | 0         | Stop      | Set to 1 to stop<br>fetching descriptors<br>for this descriptor list.<br>The stop bit can only<br>be set on the last<br>descriptor of an<br>adjacent block of<br>descriptors.                            |

| 0x04   | Length  | 31:28     |           | Reserved set to 0's                                                                                                                                                                                      |

| 0x04   |         | 27:0      |           | Length of the data in bytes.                                                                                                                                                                             |

#### Table 6: Descriptor Fields (cont'd)

| Offset    | Field   | Bit Index | Sub Field | Description                                                                                                      |

|-----------|---------|-----------|-----------|------------------------------------------------------------------------------------------------------------------|

| 0x0C-0x8  | Src_adr | 63:0      |           | Source address for<br>H2C and memory<br>mapped transfers.<br>Metadata writeback<br>address for C2H<br>transfers. |

| 0x14-0x10 | Dst_adr | 63:0      |           | Destination address<br>for C2H and memory<br>mapped transfers. Not<br>used for H2C stream.                       |

| 0x1C-0x18 | Nxt_adr | 63:0      |           | Address of the next descriptor in the list.                                                                      |

The DMA has  $Bit_width * 512$  deep FIFO to hold all descriptors in the descriptor engine. This descriptor FIFO is shared with all selected channels.

• For Gen3x8 with 2H2C and 2C2H design, AXI bit width is 256 bits. FIFO depth is 256 bit \* 512 = 32 B \* 512 = 16 KB (512 descriptors). This FIFO is shared by 4 DMA engines.

#### **Descriptor Bypass**

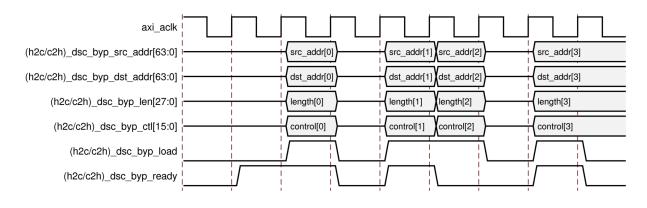

The descriptor fetch engine can be bypassed on a per channel basis through Vivado<sup>®</sup> IDE parameters. A channel with descriptor bypass enabled accepts descriptor from its respective c2h\_dsc\_byp or h2c\_dsc\_byp bus. Before the channel accepts descriptors, the Control register Run bit must be set. The NextDescriptorAddress and NextAdjacentCount, and Magic descriptor fields are not used when descriptors are bypassed. The ie\_descriptor\_stopped bit in Control register bit does not prevent the user logic from writing additional descriptors. All descriptors written to the channel are processed, barring writing of new descriptors when the channel buffer is full.

#### Poll Mode

Each engine is capable of writing back completed descriptor counts to host memory. This allows the driver to poll host memory to determine when the DMA is complete instead of waiting for an interrupt.

For a given DMA engine, the completed descriptor count writeback occurs when the DMA completes a transfer for a descriptor, and ie\_descriptor\_completed and Pollmode\_wb\_enable are set. The completed descriptor count reported is the total number of completed descriptors since the DMA was initiated (not just those descriptors with the Completed flag set). The writeback address is defined by the Pollmode\_hi\_wb\_addr and Pollmode\_lo\_wb\_addr registers.

#### Table 7: Completed Descriptor Count Writeback Format

| Offset | Fields  |      |                              |

|--------|---------|------|------------------------------|

| 0x0    | Sts_err | 7'h0 | Compl_descriptor_count[23:0] |

#### Table 8: Completed Descriptor Count Writeback Fields

| Field                        | Description                                                             |

|------------------------------|-------------------------------------------------------------------------|

| Sts_err                      | The bitwise OR of any error status bits in the channel Status register. |

| Compl_descriptor_count[23:0] | The lower 24 bits of the Complete Descriptor Count register.            |

#### **DMA H2C Stream**

For host-to-card transfers, data is read from the host at the source address, but the destination address in the descriptor is unused. Packets can span multiple descriptors. The termination of a packet is indicated by the EOP control bit. A descriptor with an EOP bit asserts tlast on the AXI4-Stream user interface on the last beat of data.

Data delivered to the AXI4-Stream interface will be packed for each descriptor. tkeep is all 1s except for the last cycle of a data transfer of the descriptor if it is not a multiple of the datapath width. The DMA does not pack data across multiple descriptors.

## DMA C2H Stream

For card-to-host transfers, the data is received from the AXI4-Stream interface and written to the destination address. Packets can span multiple descriptors. The C2H channel accepts data when it is enabled, and has valid descriptors. As data is received, it fills descriptors in order. When a descriptor is filled completely or closed due to an end of packet on the interface, the C2H channel writes back information to the writeback address on the host with pre-defined WB Magic value 16 'h52b4 (Table 10: C2H Stream Writeback Fields), and updated EOP and Length as appropriate. For valid data cycles on the C2H AXI4-Stream interface, all data associated with a given packet must be contiguous.

**Note:** C2H Channel Writeback information is different then Poll mode updates. C2H Channel Writeback information provides the driver current length status of a particular descriptor. This is different from Pollmode\_\*, as is described in Poll Mode.

The tkeep bits for transfers for all except the last data transfer of a packet must be all 1s. On the last transfer of a packet, when tlast is asserted, you can specify a tkeep that is not all 1s to specify a data cycle that is not the full datapath width. The asserted tkeep bits need to be packed to the lsb, indicating contiguous data. When tlast is asserted and all zeroes are on, tkeep is not a valid combination for DMA to function properly.

The length of a C2H Stream descriptor (the size of the destination buffer) must always be a multiple of 64 bytes.

#### Table 9: C2H Stream Writeback Format

| Offset | Fields                                   |  |  |  |

|--------|------------------------------------------|--|--|--|

| 0x0    | WB Magic[15:0] Reserved [14:0] Status[0] |  |  |  |

| 0x04   | Length[31:0]                             |  |  |  |

#### Table 10: C2H Stream Writeback Fields

| Field    | Bit Index | Sub Field | Description                                          |

|----------|-----------|-----------|------------------------------------------------------|

| Status   | 0         | EOP       | End of packet                                        |

| Reserved | 14:0      |           | Reserved                                             |

| WB Magic | 15:0      |           | 16'h52b4. Code to verify the C2H writeback is valid. |

| Length   | 31:0      |           | Length of the data in bytes.                         |

Note: C2H Streaming writeback address cannot cross 4K boundary.

## **Address Alignment**

#### Table 11: Address Alignment

| Interface Type                     | Datapath<br>Width    | Address Restriction                               |

|------------------------------------|----------------------|---------------------------------------------------|

| AXI4 MM                            | 64, 128, 256,<br>512 | None                                              |

| AXI4-Stream                        | 64, 128, 256,<br>512 | None                                              |

| AXI4 MM fixed address <sup>1</sup> | 64                   | Source_addr[2:0] == Destination_addr[2:0] == 3'h0 |

| AXI4 MM fixed address <sup>1</sup> | 128                  | Source_addr[3:0] == Destination_addr[3:0] == 4'h0 |

| AXI4 MM fixed address <sup>1</sup> | 256                  | Source_addr[4:0] == Destination_addr[4:0] == 5'h0 |

| AXI4 MM fixed address <sup>1</sup> | 512                  | Source_addr[5:0] == Destination_addr[5:0]==6'h0   |

#### Notes:

1. For fixed address mode, you must set bit [25] in the control registers.

#### **Related Information**

H2C Channel Control (0x04) C2H Channel Control (0x04)

#### Length Granularity

#### Table 12: Length Granularity

| Interface Type        | Datapath<br>Width    | Length Granularity Restriction |

|-----------------------|----------------------|--------------------------------|

| AXI4 MM               | 64, 128, 256,<br>512 | None                           |

| AXI4-Stream           | 64, 128, 256,<br>512 | None <sup>1</sup>              |

| AXI4 MM fixed address | 64                   | Length[2:0] == 3'h0            |

| AXI4 MM fixed address | 128                  | Length[3:0] == 4'h0            |

| AXI4 MM fixed address | 256                  | Length[4:0] == 5'h0            |

| AXI4 MM fixed address | 512                  | Length[5:0] == 6'h0            |

Notes:

1. Each C2H descriptor must be sized as a multiple of 64 Bytes. However, there are no restrictions to the total number of Bytes in the actual C2H transfer.

#### Parity

Parity checking occurs one of two ways. Set the **Parity Checking** option in the PCIe DMA Tab in the Vivado<sup>®</sup> IDE during core customization:

When **Check Parity** is enabled, the DMA/Bridge Subsystem for PCIe checks for parity on read data from PCIe, and generates parity for write data to the PCIe.

When **Propagate Parity** is enabled, the DMA/Bridge Subsystem for PCIe propagates parity to the user AXI interface. You are responsible for checking and generating parity in the AXI Interface. Parity is valid every clock cycle when a data valid signal is asserted, and parity bits are valid only for valid data bytes. Parity is calculated for every byte; total parity bits are DATA\_WIDTH/8.

- Parity information is sent and received on \*\_tuser ports in AXI4-Stream (AXI\_ST) mode.

- Parity information is sent and received on \*\_ruser and \*\_wuser ports in AXI4 Memory Mapped (AXI-MM) mode.

Odd parity is used for parity checking. By default, parity checking is not enabled.

#### **Related Information**

PCIe DMA Tab

# **Port Descriptions**

**IMPORTANT!** This document covers only DMA mode port descriptions. For AXI Bridge mode, see the AXI Bridge for PCI Express Gen3 Subsystem Product Guide (PG194).

The DMA/Bridge Subsystem for PCI Express<sup>®</sup> connects directly to the integrated block for PCIe. The datapath interfaces to the PCIe integrated block IP are 64, 128, 256 or 512-bits wide, and runs at up to 250 MHz depending on the configuration of the IP. The datapath width applies to all data interfaces except for the AXI4-Lite interfaces. AXI4-Lite interfaces are fixed at 32-bits wide.

Ports associated with this subsystem are described in the following tables.

## **XDMA Global Ports**

| Table 13: Top-Level | Interface Signals |

|---------------------|-------------------|

|---------------------|-------------------|

| Signal Name       | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sys_clk           | I         | 7 series Gen2 and Virtex-7 Gen3: PCIe reference clock. Should be<br>driven from the O port of reference clock IBUFDS_GTE2.<br>UltraScale: DRP clock and internal system clock (Half the frequency of<br>sys_clk_gt if PCIe Reference Clock is 250 MHz, otherwise same<br>frequency as sys_clk_gt frequency). Should be driven by the ODIV2<br>port of reference clock IBUFDS_GTE3.                                                                                                                                                                                                                                                                                   |

| sys_clk_gt        | I         | UltraScale only: PCIe reference clock. Should be driven from the O port of reference clock IBUFDS_GTE3. See the UltraScale Devices Gen3<br>Integrated Block for PCI Express LogiCORE IP Product Guide (PG156), or<br>UltraScale+ Devices Integrated Block for PCI Express LogiCORE IP Product<br>Guide (PG213).                                                                                                                                                                                                                                                                                                                                                      |

| sys_rst_n         | I         | Reset from the PCIe edge connector reset signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| axi_aclk          | 0         | PCIe derived clock output for m_axi* and s_axi* interfaces. axi_aclk is a derived clock from the TXOUTCLK pin from the GT block; it is not expected to run continuously while axi_aresetn is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| axi_aresetn       | 0         | AXI reset signal synchronous with the clock provided on the axi_aclk output. This reset should drive all corresponding AXI Interconnect aresetn signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| dma_bridge_resetn | I         | <ul> <li>Optional pin and available only when SOFT_RESET_EN parameter is set to TRUE. This pin is intended to be user driven reset when link down, Function Level Reset, Dynamic Function eXchange, or another error condition defined by user occurs. It is not required to be toggled during initial link up operation.</li> <li>When used, all PCIe traffic must be in quiesce state. The signal must be asserted for longer than the Completion Timeout value (typically 50 ms).</li> <li>O: Resets all internal Bridge engines and registers as well as asserts the axi_aresetn signal while maintaining PCIe link up.</li> <li>It Normal aparation.</li> </ul> |

|                   |           | <ul> <li>1: Normal operation.</li> <li>See Clocking and Resets for further instruction on using this signal.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| user_lnk_up       | 0         | Output Active-High Identifies that the PCI Express core is linked up with a host device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### Table 13: Top-Level Interface Signals (cont'd)

| Signal Name           | Direction | Description                                                                              |

|-----------------------|-----------|------------------------------------------------------------------------------------------|

| msi_enable            | 0         | Indicates when MSI is enabled.                                                           |

| msi_vector_width[2:0] | 0         | Indicates the size of the MSI field (the number of MSI vectors allocated to the device). |

| msix_enable           | 0         | Indicates when MSI-X is enabled.                                                         |

#### **Related Information**

**Clocking and Resets**

## PCIe Interface Signals

#### Table 14: PCIe Interface Signals

| Signal Name                                 | Direction | Description              |

|---------------------------------------------|-----------|--------------------------|

| pci_exp_rxp[PL_LINK_CAP_MAX_LINK_WIDTH-1:0] | Ι         | PCIe RX serial interface |

| pci_exp_rxn[PL_LINK_CAP_MAX_LINK_WIDTH-1:0] | I         | PCIe RX serial interface |

| pci_exp_txp[PL_LINK_CAP_MAX_LINK_WIDTH-1:0] | 0         | PCIe TX serial interface |

| pci_exp_txn[PL_LINK_CAP_MAX_LINK_WIDTH-1:0] | 0         | PCIe TX serial interface |

### H2C Channel 0-3 AXI4-Stream Interface Signals

| Signal Name <sup>1</sup>                         | Direction | Description                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| m_axis_h2c_tready_ <i>x</i>                      | Ι         | Assertion of this signal by the user logic indicates that it is<br>ready to accept data. Data is transferred across the interface<br>when m_axis_h2c_tready and m_axis_h2c_tvalid are asserted<br>in the same cycle. If the user logic deasserts the signal when<br>the valid signal is High, the DMA keeps the valid signal<br>asserted until the ready signal is asserted. |