Design Flow Assistant

Interactive guide to help you create a development strategy.

Breakthrough Acceleration for 5G, Networking, and Cloud

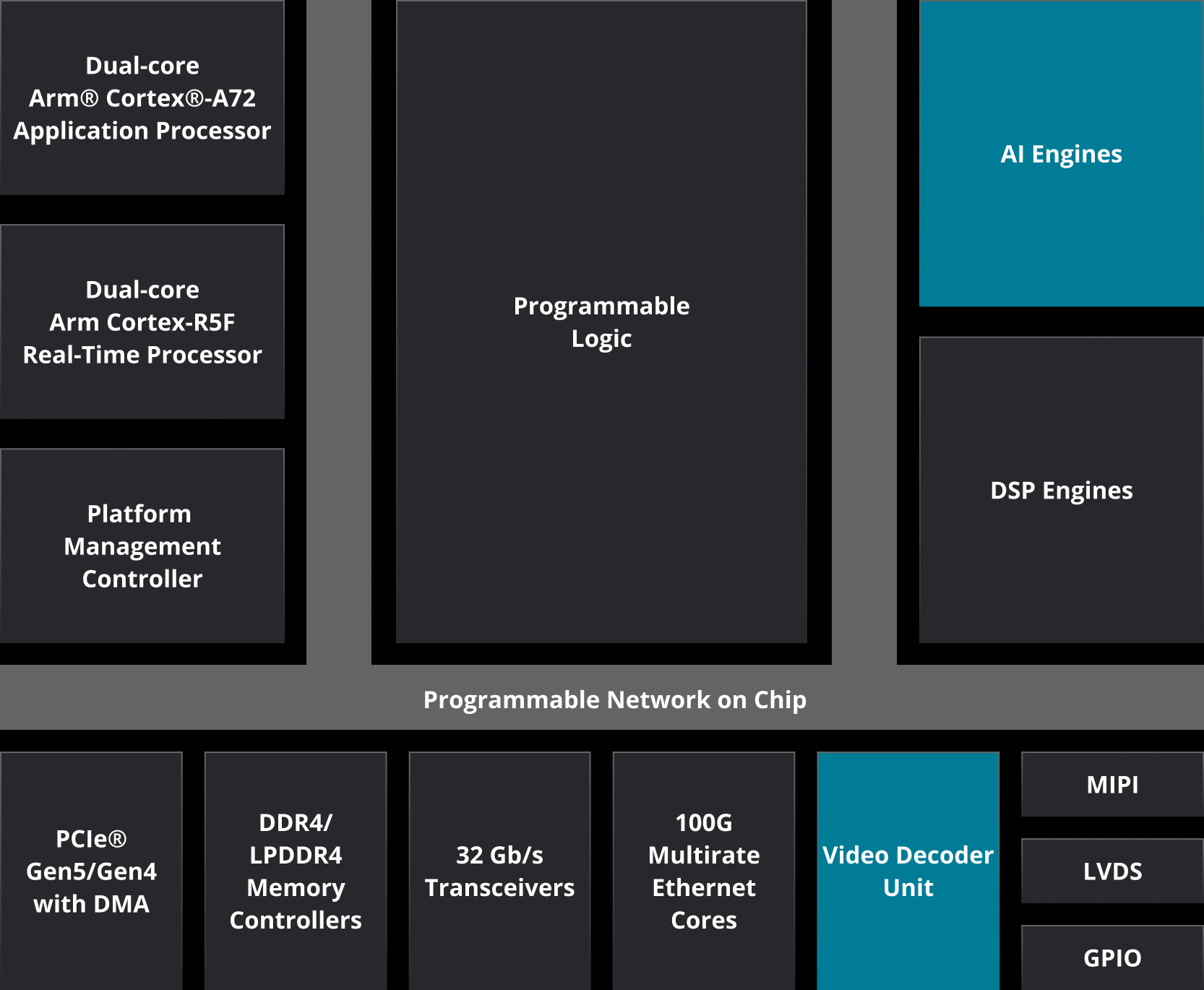

Three scalar processor types are available in Versal adaptive SoCs to support diverse application needs. The application processing unit is ideal for complex applications supported by an OS, and the real-time processing unit is ideal for applications which need low latency, determinism, and real-time control. A separate platform management controller manages system boot, security, and debug.

Programmable logic enables the development of custom computational blocks for ever-changing algorithms. The rearchitected logic in Versal adaptive SoCs provides 4X density per CLB, reducing the need for costly global routing. Loaded with a wide variety of memory elements and tightly coupled with programmable I/O, the programmable logic allows users to create powerful accelerators for any application.

AI Engines provide up to 5X higher compute density for vector-based algorithms. Optimized for real-time DSP and AI/ML computation, AI Engines provide deterministic performance.

Enhanced DSP Engines provide support for new operations and data types, including single and half-precision floating point and complex 18x18 operations.

The Versal Prime series combines PCIe® Gen5/Gen4 compliance, high-performance GPIO, 400G High-Speed Crypto (HSC) Engines*, and multirate Ethernet MACs supporting various Ethernet configurations to maximize connectivity and flexibility. Additionally, Versal Prime series devices feature rearchitected low-latency 32.75 Gb/s transceivers, and certain devices support 58 Gb/s and 112 Gb/s* PAM4 transceivers.

* Only the VM2152 device supports 400G HSC Engines and 112 Gb/s PAM4 transceivers

Power-optimized hardened video decoder units (VDUs) comprise multiple video decoder engines (VDEs) supporting H.264 and H.265 from a single 4Kp60 stream to up to thirty-two 720p15 streams per engine. VDUs are ideal for many image processing applications where multiple video inputs feed a central hub that is both decoding and executing advanced ML algorithms.

The programmable network on chip (NoC) provides an optimized multi-terabit interconnect between the different compute engines and integrated IP blocks present in the Versal adaptive SoC architecture, simplifying timing closure and saving logic resources. The NoC compiler provides a streamlined programming experience while allowing users to manage latency and QoS, ensuring that critical data paths are prioritized.

Beamforming results in enormous signal processing requirements that need to be processed in real time. While adaptable engines are handling status control and data formatting, AI Engines and DSP Engines are processing fixed floating point signal processing workloads for high performance parallel processing.

As convolutional neural networks continue to evolve, the challenge to keep up with increasing computational density requirements can only be addressed by the Versal AI Core series devices, which have AI Engines optimized to efficiently deliver computational density, both cost effectively and power efficiently.

Versal AI Core series devices enable the plethora of new video processing applications being deployed at the edge for Smart Cities, with AI Engines driving real-time license plate, facial recognition, or object classification, video decoder units for video transcoding, and adaptable engines for video scaling, compression, and customization.

Versal AI Core series accelerates parallel beamforming and real-time image processing to create higher quality images and machine-based image analysis to enable physicians and radiologists to make faster and more accurate diagnoses.

Merging powerful vector-based DSP engines with AI engines in a small form factor enables advanced radars, such as active electronically scanned arrays. AI Core series devices provide terabits per second of antenna bandwidth in a single package.

Real-time DSP is used extensively in wireless communications test equipment. Versal AI Engine architecture is well-suited to handle all types of protocol implementations, including 5G from the digital front end to beamforming and baseband.

| VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|

| Application Processing Unit | Dual-core Arm® Cortex®-A72, 48 KB/32 KB L1 Cache w/ parity & ECC; 1 MB L2 Cache w/ ECC | |||||

| Real-time Processing Unit | Dual-core Arm Cortex-R5F, 32 KB/32 KB L1 Cache, and 256 KB TCM w/ECC | |||||

| Memory | 256 KB On-Chip Memory w/ECC | |||||

| Connectivity | Ethernet (x2); USB 2.0 (x1); UART (x2); SPI (x2); I2C (x2); CAN-FD (x2) | |||||

| VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|

| AI Engines | 198 | 304 | 300 | 400 | 0 | 0 |

| AI Engines-ML | 0 | 0 | 0 | 0 | 152 | 304 |

| DSP Engines | 1,032 | 1,312 | 1,600 | 1,968 | 984 | 1,312 |

| VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|

| System Logic Cells (K) | 815 | 981 | 1,586 | 1,968 | 820 | 1,139 |

| LUTs | 372,352 | 448,512 | 725,000 | 899,840 | 375,000 | 520,704 |

| VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|

| NoC Master / NoC Slave Ports | 21 | 21 |

28 | 28 | 21 | 21 |

| DDR Memory Controllers | 3 | 3 |

4 | 4 | 3 | 3 |

| PCIe® w/ DMA (CPM) | 1 x Gen4x16 |

1 x Gen4x16 |

1 x Gen4x16 |

1 x Gen4x16 |

2 x Gen5x8 |

2 x Gen5x8 |

| PCI Express® | 4 x Gen4x8 | 4 x Gen4x8 | 4 x Gen4x8 | 4 x Gen4x8 | 4 x Gen5x4 | 4 x Gen5x4 |

| 100G Multirate Ethernet MAC | 3 | 4 | 4 | 4 | 2 | 2 |

| Video Decoder Engines (VDEs) | - | - | - | - | 2 | 4 |

| GTY Transceivers | 32 | 44 | 44 | 44 | 0 | 0 |

| GTYP Transceivers | 0 | 0 | 0 | 0 | 321 | 321 |

1. 16 GTYP transceivers are dedicated to CPM5 for PCI Express use.

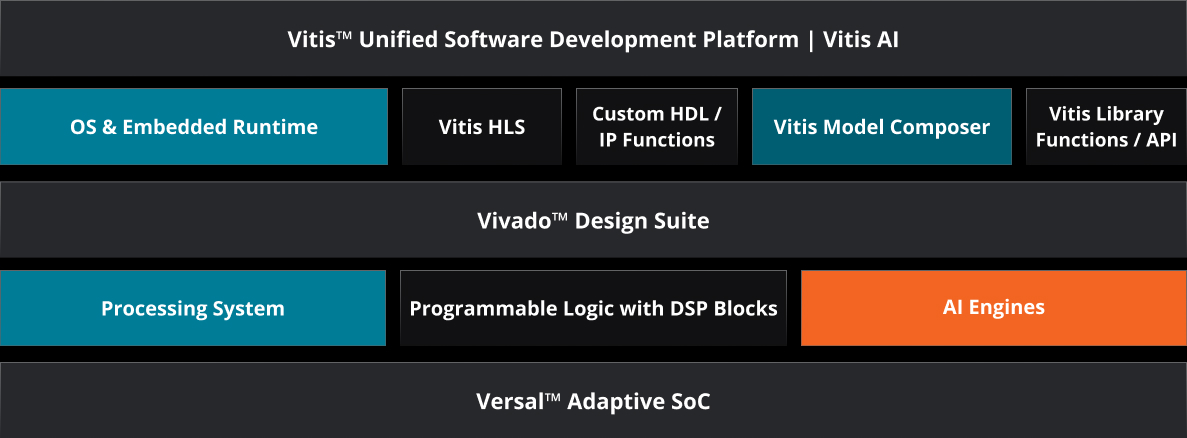

AMD provides a leading software development environment for designing with adaptive SoCs and FPGAs—this includes tools (compilers, simulators, etc.), IP, and solutions.

This environment can reduce development time while allowing developers to achieve high performance per watt. AMD adaptive SoCs & FPGA design tools enable all types of developers from AI scientists, application and algorithm engineers, embedded software developers, and traditional hardware developers to use AMD adaptive computing solutions.

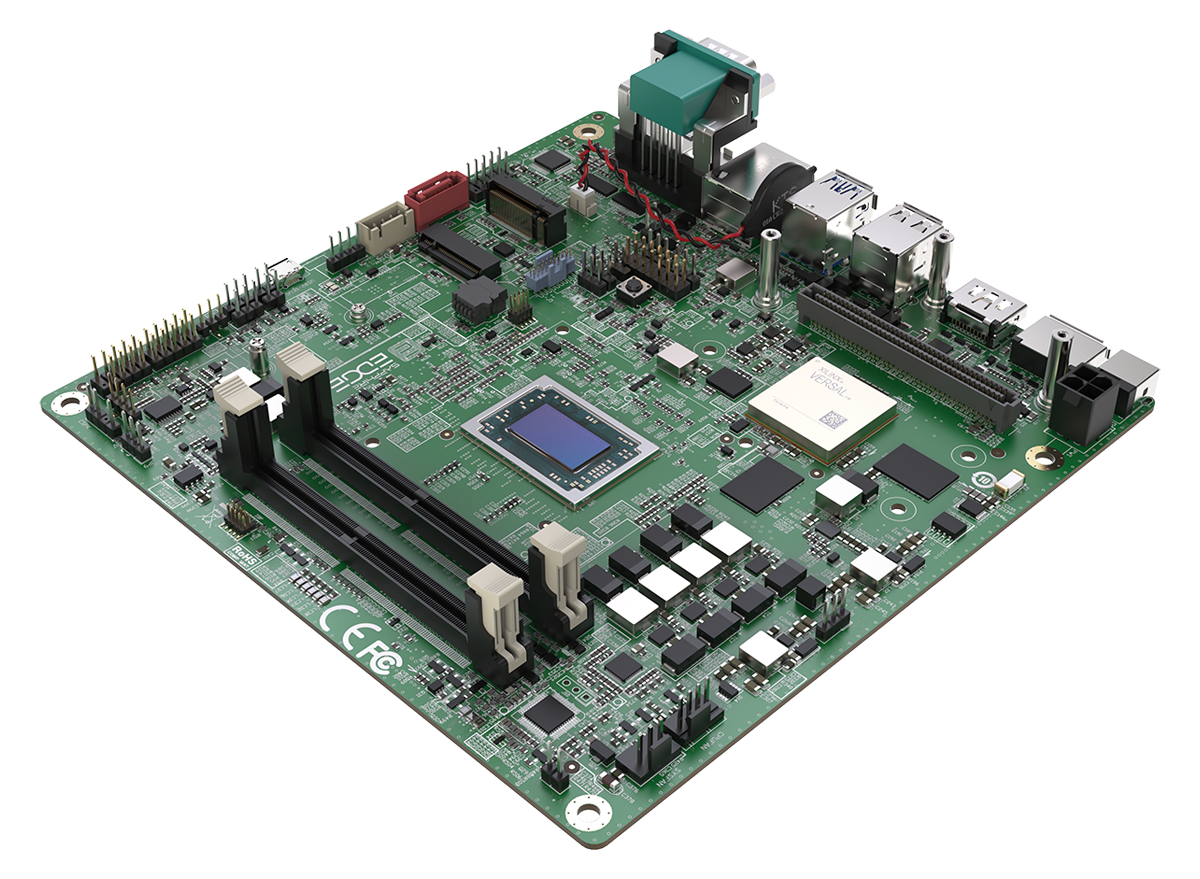

Jump-start your design cycle and achieve fast time-to-market with the proven hardware, software support, tools, design examples, and documentation available for the kit.

Start evaluating Versal AI Core series capabilities today with the VCK190 evaluation kit featuring the VC1902 device. Leveraging the on-chip AI Engines optimized for signal processing and ML inference, this platform is ideal for developing compute-intensive, latency-sensitive DSP and ML applications. Jump-start your design cycle and achieve fast time-to-market with the proven hardware, software support, tools, design examples, and documentation available for the kit.

Join the Versal adaptive SoC notification list to receive the latest news and updates.