Tried. Trusted. Long Lasting.

With typical lifespans extending well past 15 years, you can depend on AMD devices for the life of your design—extending AMD 7 Series FPGAs and adaptive SoCs through 2040 and AMD UltraScale+™ FPGAs and adaptive SoCs through 2045.

AMD Virtex™ UltraScale+™ 32 Gigabit GTY, Power Optimized Transceiver

This video demonstrates the Virtex™ UltraScale+™ FPGA with 32.75G backplane capable, power optimized transceivers. The transceiver displays best-in-class transmit jitter and 3rd generation, customer proven auto-adaptive receiver equalization technology.

AMD Virtex™ UltraScale+™ Product Advantages

AMD Virtex UltraScale+ devices provide the highest performance and integration capabilities in a 16 nm FPGA. AMD 3rd generation 3D ICs use stacked silicon interconnect (SSI) technology to break through the limitations of Moore’s law and deliver the highest signal processing and serial I/O bandwidth to satisfy the most demanding design requirements. It also provides registered inter-die routing lines enabling >600 MHz operation, with abundant and flexible clocking to deliver a virtual monolithic design experience.

As the industry's most capable 16 nm FPGA family, the devices are ideal for compute-intensive applications ranging from 1+ Tb/s networking, machine learning, to radar/early-warning systems.

Key Features and Benefits

3D-on-3D Integration

FinFET with 3D IC for breakthrough density, bandwidth, and massive inter-die connectivity for virtual monolithic design

Enhanced DSP Cores

Up to 38 TOPs (22 TeraMACs) of DSP compute performance are optimized for fixed and floating point compute including INT8 for AI inference

32.75 Gb/s Transceivers

Up to 128 transceivers on a device – backplane, chip-to-optics, and chip-to-chip capable

Integrated Block for PCI Express

Gen3x16 Integrated PCIe® block for 100G applications

Memory

DDR4 support of up to 2,666 Mb/s, up to 500 Mb of on-chip memory caches for increased efficiency and low latency

ASIC-Class Networking IP

150G Interlaken, 100G Ethernet MAC cores for high speed connectivity

Portfolio

Introducing Virtex UltraScale+ family

Applications

Explore New Possibilities with the Virtex UltraScale+ FPGAs

Compute Acceleration

Data centers need to be workload optimized to dynamically change the throughput, latency, and power requirements from a wide range of virtualized software applications. Virtex UltraScale+ FPGAs serve as a scalable, reconfigurable acceleration platform that can be optimized for complex workloads. Massive amounts of raw compute capability and I/O flexibility in Virtex UltraScale+ FPGAs are suited for compute-intensive workloads in data center applications.

5G Baseband

Flexible hardware acceleration, low latency operation, high-speed switching capability are critical in 5G baseband. Virtex UltraScale FPGAs offers dynamic and scalable solutions for evolving 5G infrastructure.

Wired Communications

Up to 128 power-optimized high-speed transceivers and Nx100G networking cores enables 1 Tb line card implementation in a small footprint. Integrated 100G Ethernet MAC with FEC and OTN modes provides a flexible interface to coherent optics to design robust systems.

Radar

The combination of beamforming and other radar functions results in enormous signal processing requirements and precision tracking and/or guidance in a spectrum contested environment. Virtex UltraScale+ FPGAs allow the RADAR designers not have to choose between performance and SWaP-C. Virtex UltraScale+ FPGAs are capable of delivering higher performance by enhanced DSP resources, on-chip memories, and high degrees of interconnectivity. Unlike general-purpose processors, FPGAs can be reprogrammed to change both waveforms and algorithms for more parallel processing.

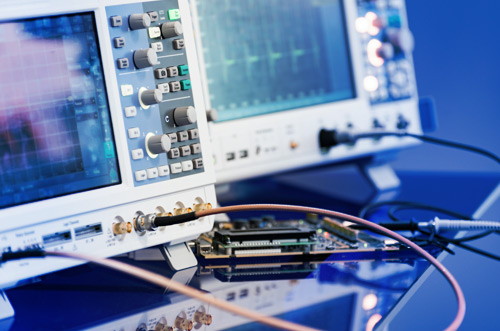

Test & Measurement

With massive DSP bandwidth and high transceiver count, Virtex UltraScale+ FPGAs offer high-performance data handling and analysis for network/protocol analyzers, signal generators, and wired communication testers. Massive on-chip embedded memory are ideal for data staging and coefficient tables & FIFOs.

Product Table

| XCVU3P | XCVU5P | XCVU7P | XCVU9P | XCVU11P | XCVU13P | |

|---|---|---|---|---|---|---|

| System Logic Cells (K) | 862 | 1,314 | 1,724 | 2,586 | 2,835 | 3,780 |

| DSP Slices | 2,280 | 3,474 | 4,560 | 6,840 | 9,216 | 12,288 |

| Memory (Mb) | 115.3 | 168.2 | 230.6 | 345.9 | 341 | 455 |

| GTY/GTM Transceivers (32.75/58 Gb/s) | 40/0 | 80/0 | 80/0 | 120/0 | 96/0 | 128/0 |

| I/O | 520 | 832 | 832 | 832 | 624 | 832 |

Get Started

Jump-start your design cycle and achieve fast time-to-market with the proven hardware, software support, tools, design examples, and documentation available for the kit.

Virtex UltraScale+ FPGA VCU118 Evaluation Kit

The Virtex UltraScale+ FPGA VCU118 Evaluation Kit is the ideal development environment for evaluating the cutting edge Virtex UltraScale+ FPGAs.

Support & Resources

Virtex UltraScale+ FPGA Product Brief

Virtex UltraScale+ FPGAs are capable of pushing the system performance-per-watt envelope, enabling breakthrough speeds with high utilization. High system performance and multiple power reduction innovations make Virtex UltraScale+ FPGAs the logical choice for compute intensive applications.

Contact Sales

Our sales team is here to support you in making the best technology decisions based on your specific needs.