Versal Premium VP1902

Build the next generation of groundbreaking technologies with the world’s largest1 adaptive SoC. The VP1902 device offers 2X the capacity of our previous emulation-class device, the AMD Virtex™ UltraScale+™ VU19P FPGA.

Breakthrough Integration of Power Optimized Cores

Unprecedented levels of integration combining programmable logic, DSP engines, AI Engines, and more application specific IP on the world’s most advanced software programmable adaptive SoC platform.

AI Engines and DSP Engines support a breadth of workloads common in edge applications including AI inference, image processing, and motion control. AI Engines are a breakthrough architecture based on a scalable array of vector processors and distributed memory, delivering breakthrough AI performance/watt. DSP Engines are based on the proven slice architecture in previous-generation Zynq™ adaptive SoCs, now with integrated floating-point support, and are ideal for wireless and image signal processing, data analytics, motion control, and more.

Programmable logic enables the development of custom computational blocks for differentiation, future-proofing, and ever-changing algorithms. Loaded with a wide variety of memory elements and tightly coupled with programmable I/O, the programmable logic allows users to create powerful accelerators for any application.

Three processor types are available for diverse application needs. The application processing unit is ideal for complex applications supported by an OS, and the real-time processing unit is ideal for latency-sensitive applications. A separate platform management controller manages system boot, security, and debug.

800G Networks and Beyond

The Versal Premium series’ 112 Gb/s PAM4 transceivers are central to enabling power-optimized, 800G network systems. The Versal Premium adaptive SoC features a broad selection of 32 Gb/s, 58 Gb/s, and 112 Gb/s transceivers on the same device, allowing vendors to scale mainstream 100G systems, ramp 400G deployment, and position themselves for 800G and beyond.

Line Rate Encryption for Secure Networks

The Versal Premium adaptive SoC delivers 1.6 Tb/s of line rate encryption throughput, making it an ideal platform for secure networks. It features hardened 400G channelized High-Speed Crypto (HSC) Engines in an adaptable platform. The HSC Engine supports the AES-GCM encryption/decryption, MACsec, and IPsec for multi-layered security.

Single Platform for 10G to 800G

The dedicated connectivity IP enables secure multi-terabit Ethernet with support for many data rates and protocols. The mix of 100G and 600G Ethernet cores delivers up to 5 Tb/s of throughput and allows scalability from the access network to metro to core, all on a single platform.

Scalable Chip-to-Chip Interconnect

Integrated Interlaken cores in the device support up to 600 Gb/s with built-in flow control for reliable, high-bandwidth data transmission. With integrated RS-FEC for power-optimized error correction, Versal Premium devices support scalable chip-to-chip interconnect while minimizing the I/O and power overhead for networking systems.

Optimal CPU-to-Accelerator Communication

PCIe® Gen5 accelerates server CPU-to-accelerator communication for next-generation compute applications, while the hardened DMA engines with programmable NoC deliver scalable and turn-key virtualization for workload provisioning and deployment.

Guaranteed QoS and Power Efficiency

The programmable network on chip (NoC) provides an optimized multi-terabit interconnect between the different compute engines and integrated IP blocks in Versal adaptive SoCs, simplifying timing closure and saving logic resources. The NoC compiler provides a streamlined programming experience while allowing users to manage latency and QoS for critical datapaths.

The Versal Premium series delivers industry-leading adaptive signal processing capacity by integrating AI Engines.

Adaptive beamforming for phased radar array performs precision tracking and guidance in a spectrum contested environment. Versal™ Premium devices with AI Engines enable 4X greater signal processing capacity1 than the previous generation, allowing designers to implement more compute-intensive functions beyond beamforming. AI Engines and DSP Engines natively support various data types, including highly efficient single-precision floating-point for greater dynamic range, which is critical in radar applications.

The Versal Premium series provides 112G PAM4 transceivers with power-optimized IP to ensure secure networking from antennas to backend interfaces while easing system integration and lowering latency and power. The innovative, heterogeneous integration in the Versal architecture results in industry-leading reductions in size, weight, and power (SWaP) advantage for many radar system designs.

1: Total equivalent DSP engine capacity vs. Virtex™ UltraScale+™ VU13P FPGA

Due to fast-growing bandwidth demands for 5G wireless, xHaul, PON, and cable access, there is tremendous pressure on the metro/transport networks to aggregate and intelligently process network traffic. Versal™ Premium series provide 112G PAM4 transceivers with dedicated connectivity IP such as 600G channelized multirate Ethernet and integrated 600G Interlaken with FEC to enable thermally efficient designs in complex metro/core transport networks.

With double the compute density of traditional hardware programmable devices, Versal Premium enables hardware differentiation, adaptability to evolving standards, and the ability to infuse AI/ML for tomorrow’s autonomous and intelligent networks.

As a heterogeneous platform, Versal Premium features the world’s highest compute density for adaptable cloud acceleration for a breadth of workloads, including genomics, video transcoding, search, and machine learning.

Dynamic function eXchange (DFX) allows users to swap compute kernels in milliseconds to provision accelerators for the most efficient use of cloud infrastructure. With massive on-chip memory capacity and bandwidth and double the compute density of currently deployed FPGA accelerators, Versal Premium offers superior compute and streamlined orchestration.

Built from the ground up to seamlessly integrate with cloud infrastructure, Versal Premium features an integrated shell that ensures host server and system memory communication is available at boot, allowing accelerator designers to spend less time on connectivity and more time on differentiation.

As data centers scale, data center interconnect (DCI) technologies must evolve to enable high capacity, scalability, and power efficiency. Versal Premium series allows service providers to deploy flexible transport technology by providing scalable transceivers up to 112G, up to 5 Tb/s of ethernet throughput, and 1.6 Tb/s of line-rate encryption for fast and secure connectivity between data centers.

To pioneer network technologies from data center to 5G, vendors need to leverage bleeding-edge communication test equipment to ensure interoperability and robust network traffic management. AI Engines and DSP Engines in the Versal Premium series provide industry-leading signal processing performance and logic capacity to implement the most complex test logic for automated test, data-flow control, tracking, and reporting.

112G PAM4 transceivers have integrated KP4 FEC for emerging protocols as well as interoperability with optics and backplanes. Dedicated channelized multirate Ethernet cores with aggregate throughput of 5 Tb/s feature modularly accessible MAC, PCS, and FEC blocks alongside programmable logic resources for custom error injection and statistical analysis.

| VP1002 | VP1052 | VP1102 | VP1202 | VP1402 | VP1502 | VP2502 | VP1552 | VP1702 | VP1802 | VP2802 | VP1902 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Application Processing Unit | Dual-core Arm® Cortex® A72, 48 KB/32 KB L1 Cache w/ parity & ECC; 1 MB L2 Cache w/ ECC | |||||||||||

| Real-Time Processing Unit | Dual-core Arm Cortex R5F, 32 KB/32 KB L1 Cache, and 256 KB TCM w/ECC | |||||||||||

| Memory | 256 KB On Chip Memory w/ECC | |||||||||||

| Connectivity | Ethernet (x2); UART (x2); CAN FD (x2); USB 2.0 (x1); SPI (x2); I2C (x2) | |||||||||||

| VP1002 | VP1052 |

VP1102 | VP1202 | VP1402 | VP1502 | VP2502 | VP1552 | VP1702 | VP1802 | VP2802 | VP1902 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| AI Engines | - | - | - | - | - | - | 472 |

- | - | - | 472 | - |

| DSP Engines | 1,140 | 1,572 | 1,904 | 3,984 | 2,672 | 7,440 | 7,392 | 7,392 | 10,896 | 14,352 | 14,304 | 6,864 |

| VP1002 | VP1052 | VP1102 | VP1202 | VP1402 | VP1502 | VP2502 | VP1552 | VP1702 | VP1802 | VP2802 | VP1902 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| System Logic Cells (K) | 833 | 1,186 | 1,575 | 1,969 | 2,233 | 3,763 | 3,738 | 3,837 | 5,558 | 7,352 | 7,326 | 18,507 |

| LUTs | 380,800 | 542,080 | 719,872 | 900,224 | 1,020,928 | 1,720,448 | 1,708,672 | 1,753,984 | 2,540,672 | 3,360,896 | 3,349,120 | 8,460,288 |

| VP1002 | VP1052 | VP1102 | VP1202 | VP1402 | VP1502 | VP2502 | VP1552 | VP1702 | VP1802 | VP2802 | VP1902 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| GTY Transceivers (32.75 Gb/s) | 20 | 20 | - | - | - | - | - | - | - | - | - | |

| GTYP Transceivers1 (32.75 Gb/s) | - | - | 8 | 281 | 8 | 281 | 281 | 681 | 281 | 281 | 281 | 128 |

| GTM Transceivers (58G (112G)) | 24 (12) | 36 (18) | 64 (32) | 20 (10) | 96 (64) | 60 (30) | 60 (30) | 20 (10) | 100 (50) | 140 (70) | 140 (70) | 32 (16) |

| PCIe® w/DMA (CPM4) | 2 x Gen4x4 | 2 x Gen4x4 | - | - | - | - | - |

- | - | - | - | - |

| PCIe w/DMA (CPM5) | - |

- |

- | 2 x Gen5x8 | - |

2 x Gen5x8 | 2 x Gen5x8 | 2 x Gen5x8 | 2 x Gen5x8 | 2 x Gen5x8 | 2 x Gen5x8 | - |

| PCI Express® | 1 x Gen4x8 | 1 x Gen4x8 | 2 x Gen5x4 | 2 x Gen5x4 | 2 x Gen5x4 | 2 x Gen5x4 | 2 x Gen5x4 | 8 x Gen5x4 | 2 x Gen5x4 | 2 x Gen5x4 | 2 x Gen5x4 | 16 x Gen5x4 |

| 100G Multirate Ethernet MAC | 3 | 5 | 6 | 2 | 6 |

4 | 4 | 4 | 6 | 8 | 8 | 12 |

| 600G Ethernet MAC | 2 | 3 | 7 | 1 | 11 | 3 | 3 | 1 | 5 | 7 | 7 | 4 |

| 600G Interlaken | 1 | 2 | 0 | 0 | 0 | 1 | 1 | 0 | 2 | 3 | 3 | 0 |

| 400G High-speed Crypto Engines | 1 | 1 | 3 | 1 | 4 | 2 | 2 | 2 | 3 | 4 | 4 | 0 |

1. 16 GTYP transceivers are dedicated to the CPM5 for PCI Express use.

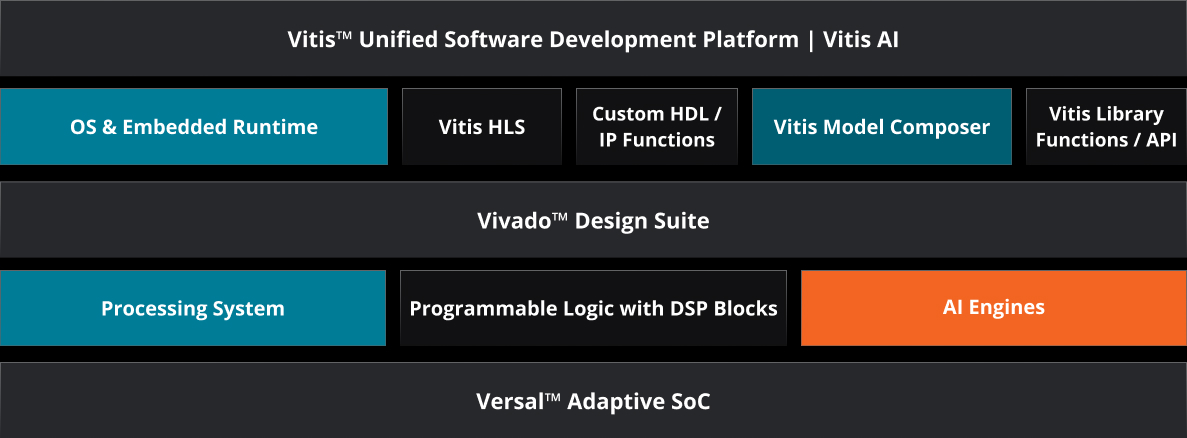

AMD provides a leading software development environment for designing with adaptive SoCs and FPGAs—this includes tools (compilers, simulators, etc.), IP, and solutions.

This environment can reduce development time while allowing developers to achieve high performance per watt. AMD adaptive SoCs & FPGA design tools enable all types of developers from AI scientists, application and algorithm engineers, embedded software developers, and traditional hardware developers to use AMD adaptive computing solutions.

Jump-start your design cycle and achieve fast time-to-market with the proven hardware, software support, tools, design examples, and documentation available for the kit.

Designing high-performance DSP functions targeting AMD Versal™ AI Engines can be done using either the AMD Vitis™ development tools or by using the Vitis Model Composer flow—taking advantage of the simulation and graphical capabilities of the MathWorks Simulink® tool.

Breakthrough Integration of Networked IP on a Power-Optimized, Adaptable Platform

Join the Versal notification list and be the first to receive updates.