# Floating-Point Operator v7.1

# LogiCORE IP Product Guide

Vivado Design Suite

PG060 December 16, 2020

# **Table of Contents**

#### **IP Facts**

#### **Chapter 1: Overview**

| Navigating Content by Design Process | 2 |

|--------------------------------------|---|

| Core Overview                        | 2 |

| Unsupported Features                 | 2 |

| Licensing and Ordering               | 3 |

#### **Chapter 2: Product Specification**

| Standards            | 4 |

|----------------------|---|

| Performance          | 6 |

| Resource Utilization | 7 |

| Port Descriptions    | 8 |

#### **Chapter 3: Designing with the Core**

| General Design Guidelines     | 14 |

|-------------------------------|----|

| Accumulator Design Guidelines | 17 |

| Clocking                      | 19 |

| Resets                        | 20 |

| Protocol Description          | 20 |

#### **Chapter 4: Design Flow Steps**

| Customizing and Generating the Core | 28 |

|-------------------------------------|----|

| Constraining the Core               | 38 |

| Simulation                          | 39 |

| Synthesis and Implementation        | 39 |

#### Chapter 5: C Model

| Features                     | . 40 |

|------------------------------|------|

| Overview                     | . 40 |

| Unpacking and Model Contents | . 41 |

| Installation                 | . 42 |

| C Model Interface            | . 42 |

| Compiling                    | . 62 |

# **E** XILINX<sub>®</sub>

| Linking.            | 63 |

|---------------------|----|

| Dependent Libraries | 64 |

| Example             | 65 |

#### Chapter 6: Test Bench

| Demonstration Test Bench |  |

|--------------------------|--|

|--------------------------|--|

#### Appendix A: Upgrading

| Migrating to the Vivado Design Suite | 69 |

|--------------------------------------|----|

| Upgrading in the Vivado Design Suite | 69 |

#### Appendix B: Debugging

| Finding Help on Xilinx.com  | 73 |

|-----------------------------|----|

| Debug Tools                 | 74 |

| Simulation Debug            | 75 |

| AXI4-Stream Interface Debug | 75 |

#### Appendix C: Additional Resources and Legal Notices

| Xilinx Resources                        | 76 |

|-----------------------------------------|----|

| Documentation Navigator and Design Hubs | 76 |

| References                              | 76 |

| Revision History                        | 77 |

| Please Read: Important Legal Notices    | 78 |

# Introduction

The Xilinx<sup>®</sup> Floating-Point Operator core provides you with the means to perform floating-point arithmetic on an FPGA. The core can be customized for operation, wordlength, latency and interface.

## Features

- Supported operators:

- Multiply

- Add/subtract

- Accumulator

- Fused multiply-add

- Divide

- Square-root

- Comparison

- Reciprocal

- Reciprocal square root

- Absolute value

- Natural logarithm

- Exponential

- Conversion from floating-point to fixed-point

- Conversion from fixed-point to floating-point

- Conversion between floating-point types

- Unfused multiply-add

- Unfused multiply-accumulator

- Accumulator primitive

- Compliance with *IEEE-754 Standard* [Ref 1] (with only minor documented deviations)

- Parameterized fraction and exponent wordlengths for most operators

- Optimizations for speed and latency

Fully synchronous design using a single clock

| LogiCORE IP Facts Table<br>Core Specifics |                                                                             |  |

|-------------------------------------------|-----------------------------------------------------------------------------|--|

|                                           |                                                                             |  |

| Supported User<br>Interfaces              | AXI4-Stream                                                                 |  |

| Resources                                 | Performance and Resource Utilization web<br>page                            |  |

| F                                         | Provided with Core                                                          |  |

| Design Files                              | Encrypted RTL                                                               |  |

| Example Design                            | Not Provided                                                                |  |

| Test Bench                                | VHDL                                                                        |  |

| Constraints File                          | Not Provided                                                                |  |

| Simulation Model                          | Encrypted VHDL, C Model                                                     |  |

| Supported<br>S/W Driver                   | N/A                                                                         |  |

| Те                                        | ested Design Flows <sup>(2)</sup>                                           |  |

| Design Entry                              | Vivado® Design Suite<br>System Generator for DSP                            |  |

| Simulation                                | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |

| Synthesis                                 | Vivado Synthesis                                                            |  |

|                                           | Support                                                                     |  |

| Release Notes and<br>Known Issues         | AR: 54504                                                                   |  |

| All Vivado IP<br>Change Logs              | Master Vivado IP Change Logs: 72775                                         |  |

| )                                         | Kilinx Support web page                                                     |  |

#### Notes:

- 1. For a complete listing of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of third-party tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

## **Navigating Content by Design Process**

Xilinx<sup>®</sup> documentation is organized around a set of standard design processes to help you find relevant content for your current development task. This document covers the following design processes:

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, subsystem functional simulation, and evaluating the Vivado timing, resource and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Port Descriptions

- Clocking

- Resets

- Customizing and Generating the Core

- C Model

### **Core Overview**

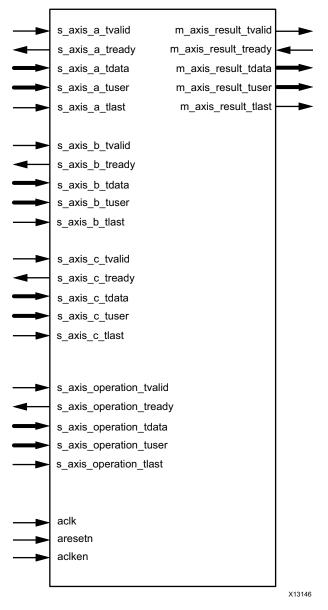

The Xilinx Floating-Point Operator core allows a range of floating-point arithmetic operations to be performed on FPGA. The operation is specified when the core is generated, and each operation variant has a common interface. This interface is shown in Figure 2-1.

## **Unsupported Features**

See Standards.

## **Licensing and Ordering**

This Xilinx LogiCORE<sup>™</sup> IP module is provided at no additional cost with the Xilinx Vivado<sup>®</sup> Design Suite under the terms of the Xilinx End User License. Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# Chapter 2

# **Product Specification**

## Standards

### **IEEE-754 Support**

The Xilinx<sup>®</sup> Floating-Point Operator core complies with much of the *IEEE-754 Standard* [Ref 1]. The deviations generally provide a better trade-off of resources against functionality. Specifically, the core deviates in the following ways:

- Non-Standard Wordlengths

- Denormalized Numbers

- Rounding Modes

- Signaling and Quiet NaNs

#### Non-Standard Wordlengths

The Xilinx Floating-Point Operator core supports a different range of fraction and exponent wordlength than defined in the *IEEE-754 Standard*.

Basic Formats:

- **binary16 (Half Precision Format)** Uses 16 bits, with an 11-bit fraction and 5-bit exponent.

- **binary32 (Single Precision Format)** Uses 32 bits, with a 24-bit fraction and 8-bit exponent.

- **binary64 (Double Precision Format)** Uses 64 bits, with a 53-bit fraction and 11-bit exponent.

- binary128 (Quadruple Format) not supported

Extendable Precision Formats (not available on all operators):

- Uses up to 80 bits.

- Exponent width of 4 to 16 bits.

• Fraction width of 4 to 64 bits

**Note:** Limitations apply based on exponent width. See the Vivado® Integrated Design Environment for actual ranges.

#### **Denormalized Numbers**

The exponent limits the size of numbers that can be represented. It is possible to extend the range for small numbers using the minimum exponent value (0) and allowing the fraction to become denormalized. That is, the hidden bit  $b_0$  becomes zero such that  $b_0.b_1b_2...b_{p-1} < 1$ . Now the value is given by:

$$\mathbf{v} = (-1)^{s} 2^{-\left(2^{w_{e}-1}-2\right)} 0.b_{1}b_{2}...b_{w_{e}-1}$$

These denormalized numbers are extremely small. For example, with single precision the value is bounded  $|v| < 2^{-126}$ . As such, in most practical calculation they do not contribute to the end result. Furthermore, as the denormalized value becomes smaller, it is represented with fewer bits and the relative rounding error introduced by each operation is increased.

The Xilinx Floating-Point Operator core does not support denormalized numbers for most operators. In FPGAs, the dynamic range can be increased using fewer resources by increasing the size of the exponent (and a 1-bit increase for single precision increases the range by 2<sup>256</sup>). If necessary, the overall wordlength of the format can be maintained by an associated decrease in the wordlength of the fraction.

To provide robustness, the core treats denormalized operands as zero with a sign taken from the denormalized number. Results that would have been denormalized are set to an appropriately signed zero.

The exception to the above rules is the absolute value operator, which propagates denormalized operands to the output.

The support for denormalized numbers cannot be switched off on some processors. Therefore, there might be very small differences between values generated by the Floating-Point Operator core and a program running on a conventional processor when numbers are very small. If such differences must be avoided, the arithmetic model on the conventional processor should include a simple check for denormalized numbers. This check should set the output of an operation to zero when denormalized numbers are detected to correctly reflect what happens in the FPGA implementation.

#### **Rounding Modes**

Only the default rounding mode, Round to Nearest (as defined by the *IEEE-754 Standard* [Ref 1]), is supported on most operators. This mode is often referred to as Round to Nearest Even, as values are rounded to the nearest representable value, with ties rounded to the nearest value with a zero least significant bit. The accumulator operator only supports

Round Towards Zero. The float-to-fixed operator uses Round to Nearest which differs from the behavior of the C language when casting floating-point values to integers.

#### Signaling and Quiet NaNs

The *IEEE-754 Standard* requires provision of Signaling and Quiet NaNs. However, the Xilinx Floating-Point Operator core treats all NaNs as Quiet NaNs. When any NaN is supplied as one of the operands to the core, the result is a Quiet NaN, and an invalid operation exception is not raised (as would be the case for signaling NaNs). The exceptions to this rule are floating-point to fixed-point conversion and the absolute value operator. For detailed information of the floating-point to fixed-point conversion, see the behavior of INVALID\_OP. For the absolute value operator, Signaling NaNs are propagated from input to output.

#### Accuracy of Results

Compliance to the *IEEE-754 Standard* requires that elementary arithmetic operations produce results accurate to half of one Unit in the Last Place (ULP). The Xilinx Floating-Point Operator satisfies this requirement for the multiply, add/subtract, fused multiply-add, divide, square-root and conversion operators.

- The reciprocal, reciprocal square-root, logarithm and exponential operators produce results which are accurate to one ULP. The accuracy of the accumulator operator is variable. See Accumulator Design Guidelines. For half precision format, the reciprocal and reciprocal square root operators are accurate to one half ULP.

- The unfused multiply-add and unfused multiply-acc implementations using DSP58 incur rounding after both the mult and add/acc stages and therefore have a minimum accuracy of 1 ULP.

# Performance

### Latency

The latency of most operators can be set between 0 and a maximum value that is dependent upon the parameters chosen. The maximum latency of the Floating-Point Operator core for all operators can be found on the Vivado Integrated Design Environment (IDE).

*Note:* The accumulator operator has a minimum latency of 1 clock cycle.

The maximum latency of the divide and square root operations is Fraction Width + 4, and for compare operation it is two cycles. The float-to-float conversion operation is three cycles when either fraction or exponent width is being reduced; otherwise it is two cycles. It

is two cycles, even when the input and result widths are the same, as the core provides conditioning in this situation. For more information, see Cycles per Operation.

# **Resource Utilization**

For details about performance, visit Performance and Resource Utilization.

# **E** XILINX<sub>®</sub>

# **Port Descriptions**

Figure 2-1: Core Schematic Symbol

The ports employed by the core are shown in Figure 2-1. They are described in more detail in Table 2-1. All control signals are active-High with the exception of aresetn.

Table 2-1:Core Signal Pinout

| Name   | Direction | Description                         |

|--------|-----------|-------------------------------------|

| aclk   | Input     | Rising-edge clock                   |

| aclken | Input     | Active-High clock enable (optional) |

| Name                    | Direction | Description                                                                                                                                |

|-------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| aresetn Input           |           | Active-Low synchronous clear (optional), always takes priority over aclken). This signal must be asserted for a minimum of 2 clock cycles. |

| s_axis_a_tvalid         | Input     | TVALID for channel A                                                                                                                       |

| s_axis_a_tready         | Output    | TREADY for channel A                                                                                                                       |

| s_axis_a_tdata          | Input     | TDATA for channel A. See TDATA Packing for internal structure                                                                              |

| s_axis_a_tuser          | Input     | TUSER for channel A                                                                                                                        |

| s_axis_a_tlast          | Input     | TLAST for channel A                                                                                                                        |

| s_axis_b_tvalid         | Input     | TVALID for channel B                                                                                                                       |

| s_axis_b_tready         | Output    | TREADY for channel B                                                                                                                       |

| s_axis_b_tdata          | Input     | TDATA for channel B. See TDATA Packing for internal structure                                                                              |

| s_axis_b_tuser          | Input     | TUSER for channel B                                                                                                                        |

| s_axis_b_tlast          | Input     | TLAST for channel B                                                                                                                        |

| s_axis_c_tvalid         | Input     | TVALID for channel C                                                                                                                       |

| s_axis_c_tready         | Output    | TREADY for channel C                                                                                                                       |

| s_axis_c_tdata          | Input     | TDATA for channel C. See TDATA Packing for internal structure                                                                              |

| s_axis_c_tuser          | Input     | TUSER for channel C                                                                                                                        |

| s_axis_c_tlast          | Input     | TLAST for channel C                                                                                                                        |

| s_axis_operation_tvalid | Input     | TVALID for channel OPERATION                                                                                                               |

| s_axis_operation_tready | Output    | TREADY for channel OPERATION                                                                                                               |

| s_axis_operation_tdata  | Input     | TDATA for channel OPERATION. See TDATA Packing for internal structure                                                                      |

| s_axis_operation_tuser  | Input     | TUSER for channel OPERATION                                                                                                                |

| s_axis_operation_tlast  | Input     | TLAST for channel OPERATION                                                                                                                |

| m_axis_result_tvalid    | Output    | TVALID for channel RESULT                                                                                                                  |

| m_axis_result_tready    | Input     | TREADY for channel RESULT                                                                                                                  |

| m_axis_result_tdata     | Output    | TDATA for channel RESULT. See TDATA Subfield for internal structure                                                                        |

| m_axis_result_tuser     | Output    | TUSER for channel RESULT                                                                                                                   |

| m_axis_result_tlast     | Output    | TLAST for channel RESULT                                                                                                                   |

#### Table 2-1: Core Signal Pinout (Cont'd)

All AXI4-Stream port names are lower case, but for ease of visualization, upper case is used in this document when referring to port name suffixes, such as TDATA or TLAST.

#### A Channel (s\_axis\_a\_tdata)

Operand A input.

#### B Channel (s\_axis\_b\_tdata)

Operand B input.

#### C Channel (s\_axis\_c\_tdata)

Operand C input.

#### aclk

All signals are synchronous to the aclk input.

#### aclken

When aclken is deasserted, the clock is disabled, and the state of the core and its outputs are maintained.

*Note:* aresetn takes priority over aclken.

#### aresetn

$\checkmark$

When aresetn is asserted, the core control circuits are synchronously set to their initial state. Any incomplete results are discarded, and m\_axis\_result\_tvalid is not generated for them. While aresetn is asserted m\_axis\_result\_tvalid is synchronously deasserted. The core is ready for new input one cycle after aresetn is deasserted, at which point slave channel tvalids are asserted. aresetn takes priority over aclken. If aresetn is required to be gated by aclken, then this can be done externally to the core.

*Note:* See the warning described in Non-Blocking Mode.

**IMPORTANT:** are setn must be driven low for a minimum of two clock cycles to reset the core.

#### **Operation Channel (s\_axis\_operation\_tdata)**

The operation channel is present when add and subtract operations are selected together, or when a programmable comparator is selected. The operations are binary encoded as specified in Table 2-2.

| FP Operation              |                          | s_axis_operation_tdata(5:0) |

|---------------------------|--------------------------|-----------------------------|

|                           | Add                      | 000000                      |

|                           | Subtract                 | 000001                      |

|                           | Unordered <sup>(1)</sup> | 000100                      |

|                           | Less Than                | 001100                      |

| c                         | Equal                    | 010100                      |

| Compare<br>(Programmable) | Less Than or Equal       | 011100                      |

| (FIOGRAMMADIE)            | Greater Than             | 100100                      |

|                           | Not Equal                | 101100                      |

|                           | Greater Than or Equal    | 110100                      |

#### Table 2-2: Encoding of s\_axis\_operation\_tdata

#### Notes:

1. An unordered comparison returns TRUE when either (or both) of the operands are NaN, indicating that the operands' magnitudes cannot be put in size order.

#### Result Channel (m\_axis\_result\_tdata)

If the operation is compare, then the valid bits within the result depend upon the compare operation selected. If the compare operation is one of those listed in Table 2-2, then only the least significant bit of the result indicates whether the comparison is TRUE or FALSE. If the operation is condition code, then the result of the comparison is provided by 4 bits using the encoding summarized in Table 2-3.

#### Table 2-3: Condition Code Summary

| Compare Operation | m_axis_   | result_td | Result |        |                       |

|-------------------|-----------|-----------|--------|--------|-----------------------|

| compare operation | 3 2 1     |           | 0      | Result |                       |

| Programmable      |           |           |        | 0      | A OP B = FALSE        |

|                   |           |           |        | 1      | A OP B = TRUE         |

| Condition Code    | Unordered | >         | <      | EQ     | Meaning               |

|                   | 0         | 0         | 0      | 1      | A = B                 |

|                   | 0         | 0         | 1      | 0      | A < B                 |

|                   | 0         | 1         | 0      | 0      | A > B                 |

|                   | 1         | 0         | 0      | 0      | A, B or both are NaN. |

The following flag signals provide exception information. Additional detail on their behavior can be found in the *IEEE-754 Standard*. The exception flags are not presented as discrete signals in Floating-Point Operator v7.1, but instead are provided in the RESULT channel m\_axis\_result\_tuser subfield. For more details, see Output Result Channel.

The accumulator operator adds two non-standard exception flags: Accumulator Input Overflow, and Accumulator Overflow. For more information about these flags, see Accumulator Design Guidelines.

www.xilinx.com

#### UNDERFLOW

Underflow is signaled when the operation generates a non-zero result which is too small to be represented with the chosen precision. The result is set to zero. Underflow is detected after rounding.

*Note:* A number that becomes denormalized before rounding is set to zero and underflow signaled.

#### **OVERFLOW**

Overflow is signaled when the operation generates a result that is too large to be represented with the chosen precision. For most operators, the output is set to a correctly signed  $\infty$ .

Due to its different rounding mode, the accumulator operator sets the output to the target format's largest finite number with the sign of the pre-rounded result.

#### INVALID\_OP

Invalid general-computational or signaling-computational operations are signaled when the operation performed is invalid. According to the *IEEE-754 Standard* [Ref 1], the following are invalid operations:

- 1. Any operation on a signaling NaN. (This is not relevant to the core as all NaNs are treated as Quiet NaNs).

- 2. Addition or subtraction of infinite values where the sign of the result cannot be determined. For example, magnitude subtraction of infinities such as  $(+\infty) + (-\infty)$ .

- 3. Multiplication, or fused multiply-add, where  $0 \times \infty$ .

- 4. Division where 0/0 or  $\infty/\infty$ .

- 5. Square root if the operand is less than zero. A special case is sqrt(-0), which is defined to be -0 by the *IEEE-754 Standard*.

- 6. When the input of a conversion precludes a faithful representation that cannot otherwise be signaled (for example NaN or infinity).

- 7. Logarithm if the input is less than 0. A special case is log(-0) which is defined to be  $-\infty$ .

When an invalid operation occurs, the associated result is a Quiet NaN. In the case of floating-point to fixed-point conversion, NaN and infinity raise an invalid operation exception. If the operand is out of range, or an infinity, then an overflow exception is raised. By analyzing the two exception signals it is possible to determine which of the three types of operand was converted. (See Table 2-4.)

#### Table 2-4: Invalid Operation Summary

| Operand        | Invalid Operation | Overflow | Result |

|----------------|-------------------|----------|--------|

| + Out of Range | 0                 | 1        | 01111  |

| - Out of Range | 0                 | 1        | 10000  |

| + Infinity     | 1                 | 1        | 01111  |

| - Infinity     | 1                 | 1        | 10000  |

| NaN            | 1                 | 0        | 10000  |

When the operand of a Floating-point to fixed-point conversion is a NaN, the result is set to the most negative representable number. When the operand is infinity or an out-of-range floating-point number, the result is saturated to the most positive or most negative number, depending upon the sign of the operand.

**Note:** Floating-point to fixed-point conversion does not treat a NaN as a Quiet NaN, because NaN is not representable within the resulting fixed-point format, and so can only be indicated through an invalid operation exception.

The absolute value operator does not signal an invalid operation when a Signaling NaN is input, as it is not a general computational or a signaling computational operation.

**Note:** The fused multiply-add operator does not signal an invalid operation when  $0 \times \infty$  + Quiet NaN is performed.

#### DIVIDE\_BY\_ZERO

DIVIDE\_BY\_ZERO is asserted when a divide operation is performed where the divisor is zero and the dividend is a finite non-zero number. The result in this circumstance is a correctly signed infinity.

DIVIDE\_BY\_ZERO is asserted when a logarithm operation is performed where the operand is zero. The result in this circumstance is negative infinity.

www.xilinx.com

# Chapter 3

# Designing with the Core

This chapter includes guidelines and additional information to make designing with the core easier.

## **General Design Guidelines**

The floating-point and fixed-point representations employed by the core are described in Floating-Point Number Representation and Fixed-Point Number Representation.

### **Floating-Point Number Representation**

The core employs a floating-point representation that is a generalization of the *IEEE-754 Standard* [Ref 1] to allow for non-standard sizes. When standard sizes are chosen, the format and special values employed are identical to those described by the *IEEE-754 Standard*.

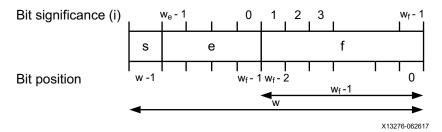

Two parameters have been adopted for the purposes of generalizing the format employed by the Floating-Point Operator core. These specify the total format width and the width of the fractional part. For standard single precision types, the format width is 32 bits and fraction width 24 bits. In the following description, these widths are abbreviated to w and  $w_{f}$ , respectively.

A floating-point number is represented using a sign, exponent, and fraction (which are denoted as 's,' 'E,' and  $b_0.b_1b_2...b_{w_{\ell-1}}$ , respectively).

The value of a floating-point number is given by:  $v = (-1)^{s} 2^{E} b_{0} \cdot b_{1} b_{2} \dots b_{w_{e-1}}$

The binary bits,  $b_i$ , have weighting  $2^{-i}$ , where the most significant bit  $b_0$  is a constant 1. As such, the combination is bounded such that  $1 \le b_0 . b_1 b_2 ... b_{p-1} < 2$  and the number is said to be normalized. To provide increased dynamic range, this quantity is scaled by a positive or negative power of 2 (denoted here as E). The sign bit provides a value that is negative when s = 1, and positive when s = 0.

The binary representation of a floating-point number contains three fields as shown in Figure 3-1.

Figure 3-1: Bit Fields within the Floating-Point Representation

As  $b_0$  is a constant, only the fractional part is retained, that is,  $f = b_1 \dots b_{w_f-1}$ . This requires only  $w_f - 1$  bits. Of the remaining bits, one bit is used to represent the sign, and  $w_e = w - w_f$  bits represent the exponent.

The exponent field, *e*, employs a biased unsigned integer representation, whose value is given by:

$$e = \sum_{i=0}^{w_e-1} e_i 2^i$$

The index, i, of each bit within the exponent field is shown in Figure 3-1.

The signed value of the exponent, E, is obtained by removing the bias, that is,

$$E = e - (2^{W_e - 1} - 1).$$

In reality,  $w_f$  is not the wordlength of the fraction, but the fraction with the hidden bit,  $b_0$ , included. This terminology has been adopted to provide commonality with that used to describe fixed-point parameters (as employed by Xilinx<sup>®</sup> System Generator<sup>™</sup> for DSP).

#### Special Values

Several values for *s*, *e* and *f* have been reserved for representing special numbers, such as Not a Number (NaN), Infinity ( $\infty$ ), Zero (0), and denormalized numbers (see Denormalized Numbers for an explanation of the latter). These special values are summarized in Table 3-1.

| Symbol for<br>Special Value | s Field    | e Field                                 | f Field                                                                                     |

|-----------------------------|------------|-----------------------------------------|---------------------------------------------------------------------------------------------|

|                             |            |                                         | Any non-zero field.                                                                         |

| NaN                         | don't care | $2^{W_e - 1}$ -1 (that is, $e = 1111$ ) | For results that are NaN the most significant bit of fraction is set (that is, $f = 1000$ ) |

| ±∞                          | sign of ∞  | $2^{w_e - 1}$ -1 (that is, $e = 1111$ ) | Zero (that is, $f = 0000$ )                                                                 |

Table 3-1: Special Values

| Symbol for<br>Special Value | s Field           | e Field | f Field                     |

|-----------------------------|-------------------|---------|-----------------------------|

| ± 0                         | sign of 0         | 0       | Zero (that is, $f = 0000$ ) |

| denormalized                | sign of<br>number | 0       | Any non-zero field          |

Table 3-1:Special Values (Cont'd)

In Table 3-1 the sign bit is undefined when a result is a NaN. The core generates NaNs with the sign bit set to 0 (that is, positive). Also, infinity and zero are signed. Where possible, the sign is handled in the same way as finite non-zero numbers. For example, -0 + (-0) = -0, -0 + 0 = 0 and  $-\infty + (-\infty) = -\infty$ . A meaningless operation such as  $-\infty + \infty$  raises an invalid operation exception and produces a NaN as a result.

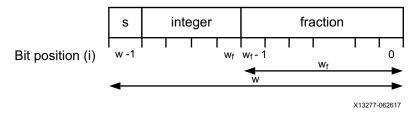

### **Fixed-Point Number Representation**

For the purposes of fixed-point to floating-point conversion, a fixed-point representation is adopted that is consistent with the signed integer type used by Xilinx System Generator for DSP. Fixed-point values are represented using a twos complement number that is weighted by a fixed power of 2. The binary representation of a fixed-point number contains three fields as shown in Figure 3-2 (although it is still a weighted twos complement number).

*Figure 3-2:* Bit Fields within the Fixed-Point Representation

In Figure 3-2, the bit position has been labeled with an index i. Based upon this, the value of a fixed-point number is given by:

$$v = -(b_{w-1})2^{w-1-w_f} + b_{w-2} \dots b_{w_f} \cdot b_{w_f-1} \dots b_1 b_0$$

$$= -(b_{w-1})2^{w-1-w_f} + \sum_{i=1}^{w-2} 2^{i-w_f} b_i$$

For example, a 32-bit signed integer representation is obtained when a total width of 32 and a fraction width of 0 are specified. Round to Nearest is employed within the conversion operations. To provide for the sign bit, the width of the integer field must be at least 1, requiring that the fractional width be no larger than w - 1.

i = 0

The fixed-to-float operator also has the option to perform 32-bit and 64-bit signed and unsigned integer conversions to convert standard software integer data formats to floating point.

# Accumulator Design Guidelines

### **Configuring the Accumulator**

The accumulator operator has been implemented as a floating-point wrapper around a fixed point accumulator to reduce resources and to allow a throughput of one sample per clock cycle. Refer to *An FPGA-specific Approach to Floating-Point Accumulation and Sum-of-Products* [Ref 17] for more information. Three parameters are required to configure the accumulator:

- **Input MSB** The MSB of the largest number that can be accepted.

- **LSB** The LSB of the smallest number that can be accepted. It is also the LSB of the accumulated result.

- **MSB** The MSB of the largest result. It can be up to 54 bits greater than the Input MSB.

These values can be set to fully support the chosen IEEE-754 format, as shown in Table 3-2, allowing the accumulator to process any floating-point number and accumulate without introducing any round-off error. For example, to fully accommodate Single Precision, the Input MSB should be set to 127 and the LSB set to -149.

| Format | MSB                                | LSB                                       |

|--------|------------------------------------|-------------------------------------------|

| Single | 2 <sup>127</sup>                   | 2 <sup>-149</sup>                         |

| Double | 2 <sup>1023</sup>                  | 2 <sup>-1074</sup>                        |

| Custom | 2 <sup>(exponent_width-1)</sup> -1 | 2 <sup>(1-MSB)-(fractional_width-1)</sup> |

Table 3-2: MSB and LSB of the Largest and Smallest IEEE-754 Floating-Point Numbers

Resource usage can be reduced if these parameters are set to match the bounds on the dataset that is used with the accumulator. For example, if the largest value that will be accumulated is 100,000 then the MSB can be set to 17, substantially reducing the width of the accumulator.

The LSB controls the accuracy of the accumulator. Input values with an LSB smaller than the LSB of the accumulator are truncated (Round Towards Zero) introducing a maximum error of  $2^{\text{LSB-1}}$  per accumulation. In the worst case, the lower  $log_2(n)$  bits of the accumulator are incorrect after *n* such accumulations. If accuracy to  $2^x$  is required after *n* accumulations then the LSB needs to be set to  $x - \lceil \log_2(N) \rceil$ . For example, if accuracy to  $2^{-16}$  is required after 1000 accumulations, the LSB needs to be set to  $-16 - \lceil \log_2(1000) \rceil = -26$ .

The MSB of the accumulator sets the maximum value that can be accumulated. The set value can be up to 54 bits greater than the Input MSB, which allows one number to be accumulated every clock cycle for one year at 400 MHz. If the MSB is set to be greater than the maximum value of the IEEE-754 format then the result can cause an IEEE-754 overflow

unless sufficient subtractions occur to bring it back into range (this is for a positive accumulated value. For a negative accumulated value, sufficient additions need to occur.)

### **Denormalized Numbers**

The accumulator is consistent with the other operators in its handling of denormalized values. Denormalized numbers seen on the input are flushed to zero. Denormalized numbers on the output are flushed to zero and the Underflow flag is set. However, denormalized numbers generated in the accumulator are retained within the accumulator to maintain accuracy.

### **Exceptions**

The accumulator handles exceptions in order shown in Table 3-3. All exceptions except for OVERFLOW and UNDERFLOW are unrecoverable.

**Note:** OVERFLOW and UNDERFLOW represent the state of the accumulated value after it has been converted to a floating-point number. Following operations might bring the accumulator back into a valid range so these exceptions are handled on a per-output basis. All other exceptions represent the state of the accumulator itself and recovery is only possible by ending the accumulation.

After an unrecoverable exception occurs, the output value and flags remain set until a new accumulation is started. The output value and flags can subsequently change if an exception above it in the table occurs.

| Exception                                              | Output Value | Flags                | Notes                                                                                                               |

|--------------------------------------------------------|--------------|----------------------|---------------------------------------------------------------------------------------------------------------------|

| NaN Summand                                            | NaN          | None                 | The output is a Quiet NaN, with the sign bit set to 0.                                                              |

| Summand MSB ><br>Input MSB                             | NaN          | ACCUM_INPUT_OVERFLOW | Infinities cannot trigger this exception                                                                            |

| Accumulated<br>value MSB > MSB                         | NaN          | ACCUM_OVERFLOW       |                                                                                                                     |

| $+\infty$ and $-\infty$                                | NaN          | INVALID_OP           |                                                                                                                     |

| +∞ or -∞                                               | +∞ or -∞     | None                 |                                                                                                                     |

| Result larger than<br>IEEE-754 format<br>can represent | ±MAX         | OVERFLOW             | As truncation is used (Round To 0) then the maximum value for the floating-point format is returned, not $\infty$ . |

| Denormalized result                                    | ± 0          | UNDERFLOW            |                                                                                                                     |

Table 3-3: Accumulator Exception Handling

#### Example:

• An  $+\infty$  summand is seen on the A channel.

- The accumulator now outputs  $+\infty$  with no flags until a new accumulation starts, unless a higher priority exception occurs.

- From this point on OVERFLOW and UNDERFLOW are impossible, but any of the exceptions above it in the table can still occur.

- Some time later, but within the same block, a  $-\infty$  summand is seen on the A channel.

- The output value now changes to NaN and INVALID\_OP is set as both  $+\infty$  and  $-\infty$  have been accumulated.

- Some time later, but within the same block, a NaN summand is seen on the A channel.

- The output value remains as NaN but INVALID\_OP is cleared.

- No other exceptions are possible.

### **Starting a New Accumulation**

A floating-point number on the A channel is the first in a new accumulation when either of the following conditions are true:

- It is the first summand after aresetn has been asserted and released.

- It is the first summand after s\_axis\_a\_tlast has been asserted on a valid AXI transfer.

When a new accumulation starts, the exceptions are cleared, the accumulator register is set to zero, and the new summand is combined (added or subtracted) with zero.

### **Accumulator Primitive**

The Accumulator Primitive operation is an alternative accumulator operation. The Accumulator Primitive can be considered as an Add/Subtract operator with the result fed back such that the output P = P +/- A. Due to the difference in internal precision, this implementation can yield different results to the Accumulator operator and so is considered to be a separate operator rather than as an alternative use of resources.

# Clocking

The Floating-Point Operator core uses a single clock, called aclk. All input and output interfaces and internal state are subject to this single clock.

## Resets

The Floating-Point Operator core uses a single, optional, reset input called aresetn. This signal is active-Low and must be asserted for a minimum of two clock cycles to ensure correct operation. aresetn is a global synchronous reset which resets all control states in the core; all data in transit through the core is lost when aresetn is asserted.

# **Protocol Description**

### **AXI4-Stream Considerations**

The conversion to AXI4-Stream interfaces brings standardization and enhances interoperability of Xilinx IP LogiCORE<sup>™</sup> solutions. Other than general control signals such as aclk, aclken and aresetn, all inputs and outputs to and from the Floating-Point Operator core are conveyed using AXI4-Stream channels. A channel consists of TVALID and TDATA always, plus several optional ports and fields. In the Floating-Point Operator, the optional ports supported are TREADY, TLAST and TUSER. Together, TVALID and TREADY perform a handshake to transfer a message, where the payload is TDATA, TUSER and TLAST. The Floating-Point Operator operates on the operands contained in the TDATA fields and outputs the result in the TDATA field of the output channel. The Floating-Point Operator does not use TUSER and TLAST inputs as such, but the core provides the facility to convey these fields with the same latency as for TDATA. This facility is expected to ease use of the Floating-Point Operator in a system. For example, the Floating-Point Operator might be operating on streaming packetized data. In this example, the core could be configured to pass the TLAST of the packetized data channel, thus saving the system designer the effort of constructing a bypass path for this information. For further details on AXI4-Stream interfaces see [Ref 15] and [Ref 16].

*Note:* The accumulator does use TLAST as an input. For more information, see **TLAST in the Accumulator and Accumulator Primitive Operators**.

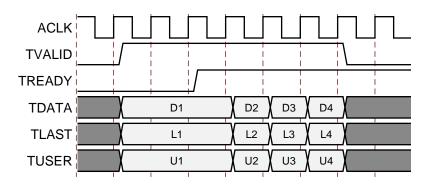

#### Basic Handshake

Figure 3-3 shows the transfer of data in an AXI4-Stream channel. TVALID is driven by the source (master) side of the channel and TREADY is driven by the receiver (slave). TVALID indicates that the value in the payload fields (TDATA, TUSER and TLAST) is valid. TREADY indicates that the slave is ready to receive data. When both TVALID and TREADY are TRUE in a cycle, a transfer occurs. The master and slave set TVALID and TREADY respectively for the next transfer appropriately.

Figure 3-3: Data Transfer in an AXI4-Stream Channel

#### Non-Blocking Mode

The term Non-Blocking means that lack of data on one input channel does not block the execution of an operation if data is received on another input channel. The full flow control of AXI4-Stream is not always required. Blocking or Non-Blocking behavior is selected using the Flow Control parameter or Vivado® Integrated Design Environment field. The core supports a Non-Blocking mode in which the AXI4-Stream channels do not have TREADY, that is, they do not support back pressure. The choice of Blocking or Non-Blocking applies to the whole core, not each channel individually. Channels still have the non-optional TVALID signal, which is analogous to the New Data (ND) signal on many cores prior to the adoption of AXI4-Stream interfaces. Without the facility to block dataflow, the internal implementation is much simplified, so fewer resources are required for this mode.

**RECOMMENDED:** This mode is recommended when moving to this core version from a pre-AXI4-Stream core with minimal change.

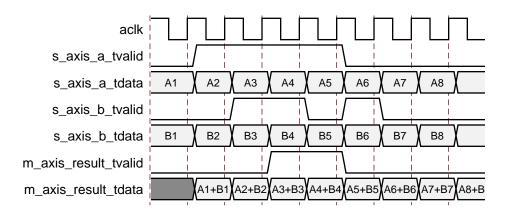

When all of the present input channels receive an active TVALID, an operation is validated and the output TVALID (suitably delayed by the latency of the core) is asserted to qualify the result. Operations occur on every enabled clock cycle and data is presented on the output channel payload fields regardless of TVALID. This is to allow a minimal migration from previous core versions. Figure 3-4 shows the Non-Blocking behavior for a case of an adder with latency of one cycle.

**IMPORTANT:** For performance, aresetn is registered internally, which delays its action by a clock cycle. The effect of this is that any transaction input in the cycle following the de-assertion of aresetn is reset by the action of aresetn, resulting in an output data value of zero. m\_axis\_result\_tvalid is also inactive for this cycle.

Figure 3-4: Non-Blocking Mode

#### **Blocking Mode**

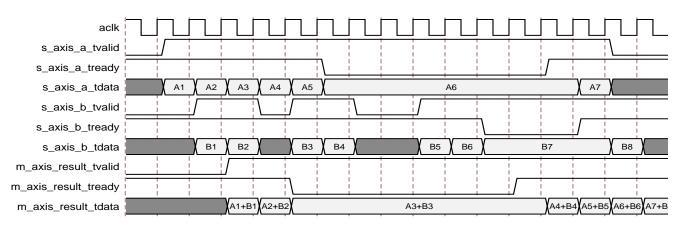

The term Blocking means that operation execution does not occur until fresh data is available on all input channels. The full flow control of AXI4-Stream aids system design because the flow of data is self-regulating. Data loss is prevented by the presence of back pressure (TREADY), so that data is only propagated when the downstream datapath is ready to process the data.

The Floating-Point Operator has one, two or three input channels and one output channel. When all input channels have validated data available, an operation occurs and the result becomes available on the output. If the output is prevented from off-loading data because TREADY is low then data accumulates in the output buffer internal to the core. When this output buffer is nearly full the core stops further operations. This prevents the input buffers from off-loading data for new operations so the input buffers fill as new data is input. When the input buffers fill, their respective TREADYs are deasserted to prevent further input. This is the normal action of back pressure.

The inputs are tied in the sense that each must receive validated data before an operation is prompted. Therefore, there is an additional blocking mechanism, where at least one input channel does not receive validated data while others do. In this case, the validated data is stored in the input buffer of the channel.

After a few cycles of this scenario, the buffer of the channel receiving data fills and TREADY for that channel is deasserted until the starved channel receives some data. Figure 3-5 shows both blocking behavior and back pressure for the case of an adder. The first data on channel A is paired with the first data on channel B, the second with the second and so on. This demonstrates the 'blocking' concept. The diagram further shows how data output is delayed not only by latency, but also by the handshake signal m\_axis\_result\_tready. This is 'back pressure'. Sustained back pressure on the output along with data availability on the inputs eventually leads to a saturation of the core buffers, leading the core to signal that it can no longer accept further input by deasserting the input channel TREADY signals. The minimum latency in this example is 2 cycles, but it should be noted that in Blocking operation latency is not a useful concept. Instead, as the diagram shows, the important idea

is that each channel acts as a queue, ensuring that the first, second, third data samples on each channel are paired with the corresponding samples on the other channels for each operation.

*Note:* The core buffers have a greater capacity than implied by the diagram.

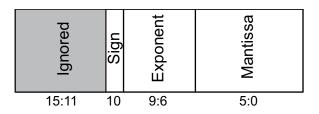

#### TDATA Packing

Fields within an AXI4-Stream interface are not given arbitrary names. Normally, information pertinent to the application is carried in the TDATA field. To ease interoperability with byte-oriented protocols, each subfield within TDATA which could be used independently is first extended, if necessary, to fit a bit field which is a multiple of 8 bits. For example, say the Floating-Point Operator is configured to have an A operand with a custom precision of 11 bits (5 exponent and 6 mantissa bits). The operand would occupy bits (10:0). Bits (15:11) would be ignored. The bits added by byte orientation are ignored by the core and do not result in additional resource use.

#### A, B, and C Input Channels

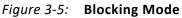

#### TDATA Structure for A, B, and C Channels

Input channels A, B, and C carry data for use in calculations in their TDATA fields. See Figure 3-6.

Figure 3-6: TDATA Structure for A, B, and C Channels

Figure 3-7 illustrates how the previous example of a custom precision input with 11 bits maps to the TDATA channel.

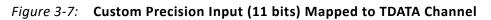

#### **TDATA Structure for OPERATION Channel**

The OPERATION channel exists only when add and subtract operations are selected together, or when a programmable comparator is selected. The binary encoded operation code, as specified in Table 2-2, are 6 bits in length. However, due to the byte-oriented nature of TDATA, this means that TDATA has a width of 8 bits.

Figure 3-8: TDATA Structure for OPERATION Channel

#### TLAST and TUSER Handling

This section covers TLAST and TUSER handling in a variety of scenarios.

# TLAST in All Operators Apart from the Accumulator and Accumulator Primitive Operators

TLAST in AXI4-Stream is used to denote the last transfer of a block of data. The Floating-Point Operator core operates on a per-sample basis where each operation is independent of any other before or after. Because of this, there is no need for TLAST on a Floating-Point Operator core.

The TLAST signal is supported on each channel purely as an optional aid to system design for the scenario in which the data stream being passed through the Floating-Point Operator core does indeed have some packetization, but which is not relevant to the core operation. The facility to pass TLAST removes the burden of matching latency to the TDATA path, which can be variable, through the Floating-Point Operator core.

www.xilinx.com

#### **TLAST in the Accumulator and Accumulator Primitive Operators**

TLAST is used in the accumulator to signal the last sample in a block of data. The next sample received after the one with TLAST asserted is loaded into the accumulator to start a fresh accumulation.

On the result channel, TLAST is used to signal the last result in a block of data. The result with TLAST asserted represents the final accumulation of all of the data in the block.

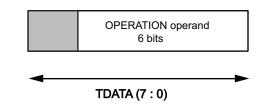

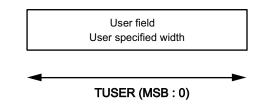

#### TUSER

TUSER is for ancillary information that qualifies or augments the primary data in TDATA. The TUSER signal is supported on each channel purely as an optional aid to system design for the scenario in which the data stream being passed through the Floating-Point Operator core does indeed have some ancillary field, but which is not relevant to the core operation. The facility to pass TUSER removes the burden of matching latency to the TDATA path, which can be variable, through the Floating-Point Operator core.

Figure 3-9: TUSER Structure for A, B, C and OPERATION Channels

#### **TLAST Options**

#### All Operators Apart from the Accumulator Operator

TLAST for each input channel is optional. When present, each input channel can be passed through the Floating-Point Operator core. When more than one channel has TLAST enabled, each input channel can pass a logical AND or logical OR of the TLASTs input. When no TLASTs are present on any input channel, the output channel does not have TLAST either.

#### Accumulator Operator

The accumulator has no TLAST options because TLAST is not optional.

#### **TUSER Options**

TUSER for each input channel is optional. Each has user-selectable width. These fields are concatenated, without any byte-orientation or padding, to form the output channel TUSER field. The TUSER field from channel A forms the least significant portion of the concatenation, then TUSER from channel B, TUSER from channel C, and TUSER from channel OPERATION.

For example, if channels A and OPERATION both have TUSER subfields with widths of 5 and 8 bits respectively, and no exception flag signals (for example, underflow) are selected, the output TUSER is a suitably delayed concatenation of A and OPERATION TUSER fields, 13 bits wide, with A in the least significant 5 bit positions (4 downto 0).

#### **Output Result Channel**

#### **TDATA Subfield**

The internal structure of the RESULT channel TDATA subfield depends on the operation performed by the core.

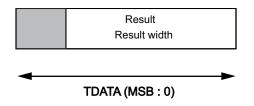

For numerical operations (for example, add, multiply) TDATA contains the numerical result of the operation and is a single floating-point or fixed-point number. The result width is sign-extended to a byte boundary if necessary. This is shown in Figure 3-10.

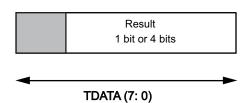

For Comparator operations, the result is either a 4-bit field (Condition Code) or a single bit indicating TRUE or FALSE. In both cases, the result is zero-padded to a byte boundary, as shown in Figure 3-11.

#### **TUSER Subfield**

The TUSER subfield is present if any of the input channels have an (optional) TUSER subfield, or if any of the exception flags (underflow, overflow, invalid operation, divide by zero, Accumulator Input Overflow and Accumulator Overflow) have been selected. The formatting of the TUSER fields is shown in Figure 3-12.

If any field of TUSER is not present, fields in more significant bit positions move down to fill the space. For example, if the overflow exception flag is selected, but the underflow exception flag is not, the overflow exception flag result moves to the least-significant bit position in the TUSER subfield.

No byte alignment is performed on TUSER fields. All fields present are immediately adjacent to one another with no padding between them or at the most significant bit.

Figure 3-10: TDATA Structure for Numerical Result Channel

Figure 3-11: TDATA Structure for Comparator Result Channel

| OPERATION<br>channel<br>User field<br>User specified<br>width, optional | C channel<br>User field<br>User specified<br>width, optional | B channel<br>User field<br>User specified<br>width, optional | A channel<br>User field<br>User specified<br>width, optional | ACCUMULATOR<br>OVERFLOIW<br>(1 bit, optional) | ACCUMULATOR INPUT<br>OVERFLOIW<br>(1 bit, optional) | DIVIDE BY ZERO<br>(1 bit, optional) | INVALID OPERATION<br>(1 bit, optional) | OVERFLOW<br>(1 bit, optional) | UNDERFLOW<br>(1 bit, optional) |

|-------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------|-------------------------------------|----------------------------------------|-------------------------------|--------------------------------|

| ◀                                                                       |                                                              |                                                              |                                                              |                                               |                                                     |                                     |                                        |                               |                                |

TUSER (MSB : LSB)

X13148

Figure 3-12: TUSER Structure for Result Channel

## Chapter 4

# **Design Flow Steps**

This chapter describes customizing and generating the core, constraining the core, and the simulation, synthesis and implementation steps that are specific to this IP core. More detailed information about the standard Vivado® design flows and the IP integrator can be found in the following Vivado Design Suite user guides:

- Vivado Design Suite User Guide: Designing IP Subsystems using IP Integrator (UG994) [Ref 8]

- Vivado Design Suite User Guide: Designing with IP (UG896) [Ref 6]

- Vivado Design Suite User Guide: Getting Started (UG910) [Ref 7]

- Vivado Design Suite User Guide: Logic Simulation (UG900) [Ref 10]

## **Customizing and Generating the Core**

This section includes information about using Xilinx<sup>®</sup> tools to customize and generate the core in the Vivado Design Suite.

If you are customizing and generating the core in the Vivado IP Integrator, see the *Vivado Design Suite User Guide: Designing IP Subsystems using IP Integrator* (UG994) [Ref 8] for detailed information. IP Integrator might auto-compute certain configuration values when validating or generating the design. To check whether the values change, see the description of the parameter in this chapter. To view the parameter value, run the validate\_bd\_design command in the Tcl console.

All fields are visible in the IP Integrator. These fields are set automatically:

- A Precision Type

- Exponent Width

- Fraction Width

You can customize the IP for use in your design by specifying values for the various parameters associated with the IP core using the following steps:

- 1. Select the IP from the IP catalog.

- 2. Double-click the selected IP or select the Customize IP command from the toolbar or right-click menu.

For details, see the Vivado Design Suite User Guide: Designing with IP (UG896) [Ref 6] and the Vivado Design Suite User Guide: Getting Started (UG910) [Ref 7].

If you are customizing and generating the core in the Vivado IP integrator, see *Vivado Design Suite User Guide: Designing IP Subsystems Using IP Integrator* (UG994) [Ref 8] for detailed information. Vivado Integrated Design Environment (IDE) might auto-compute certain configuration values when validating or generating the design, as noted in this section. You can view the parameter value after successful completion of the validate\_bd\_design command.

The Floating-Point Operator core provides several tabs with fields to set the parameter values for the particular instantiation required. This section provides a description of each field.

The Vivado IDE allows configuration of the following:

- Core operation

- Wordlength

- Implementation optimizations, such as use of slices

- Optional pins

### **All Configuration Tabs**

All configuration tabs allow the Component Name to be specified.

#### **Component Name**

The component name is used as the base name of the output files generated for the core. Names must start with a letter and be composed using the following characters: a to z, 0 to 9, and "\_".

### **Operation Selection Tab**

The floating-point operation can be one of the following:

- Add/Subtract

- Accumulators

- Multiply

- Fused Multiply-Add

- Divide

- Reciprocal

- Square-root

- Reciprocal square root

- Absolute value

- Logarithm

- Exponential

- Compare

- Fixed-to-float

- Float-to-fixed

- Float-to-float

- Unfused multiply-add

- Unfused multiply accumulator

- Accumulator primitive

When Add/Subtract, Accumulators, Unfused Multiply-Add, Accumulator Primitive, Unfused Multiply-Accumulator or Fused Multiply-Add is selected, it is possible for the core to perform both operations, or just add or subtract. When both are selected, the operation performed on a particular set of operands is controlled by the s\_axis\_operation channel (with encoding defined in Table 2-2).

When Add/Subtract, Accumulator, Multiply, Fused Multiply-Add, Logarithm or Exponential is selected, the level of slice usage can be specified according to FPGA family as described in the AXI4-Stream Channel Options section.

When Compare is selected, the compare operation can be programmable or fixed. If programmable, then the compare operation performed should be supplied through the s\_axis\_operation channel (with encoding defined in Table 2-2). If a fixed operation is required, then the operation type should be selected.

When Float-to-float conversion is selected, and exponent and fraction widths of the input and result are the same, the core provides a means to condition numbers, that is, convert denormalized numbers to zero, and signaling NaNs to quiet NaNs.

### Precision of Inputs and Precision of Results Tabs

These tabs let you specify the precision of the operand and the precision of the result. Availability of the precision of results depends on the configuration selected on the Operation Selection Tab. (The Precision of Results tab is available only when performing an operand conversion: Fixed-to-Float, Float-to-Fixed and Float-to-Float.)

When targeting a Versal ACAP device, unfused multiply-add and unfused multiply-acc operators using the DSP Engines are available. The Multiply and Add/Subtract operators may also target the native floating-point support of the DSP Engines.

The parameters in these tabs define the number of bits used to represent quantities. The type of the operands and results depend on the operation requested. For fixed-point conversion operations, either the operand or result is fixed-point. For all other operations, the output is specified as a floating-point type.

**Note:** For the condition-code compare operation,  $m_axis\_result\_tdata(3:0)$  indicates the result of the comparison operation. For other compare operations  $m_axis\_result\_tdata(0:0)$  provides the result.

Table 4-1 defines the general limits of the format widths.

| Format Type    | Format Type Fraction Width |     | Exponent/In | teger Width | Width |     |

|----------------|----------------------------|-----|-------------|-------------|-------|-----|

| Format Type    | Min                        | Max | Min         | Max         | Min   | Max |

| Floating-Point | 4                          | 64  | 4           | 16          | 4     | 64  |

| Fixed-Point    | 0                          | 63  | 1           | 64          | 4     | 64  |

#### Table 4-1: General Limits of Width and Fraction Width

There are also some further limits for specific cases which are enforced by the Vivado IDE:

• The exponent width (that is, Total Width-Fraction Width) should be chosen to support normalization of the fractional part. This can be calculated using:

Minimum Exponent Width = ceil [log<sub>2</sub>(Fraction Width+3)] + 1

For example, a 24-bit fractional part requires an exponent of at least 6 bits (for example, {ceil [log<sub>2</sub> (27)]+1}).

• For conversion operations, the exponent width of the floating-point input or output is also constrained by the Total Width of the fixed-point input or output to be a minimum of:

Minimum Exponent Width = ceil[log<sub>2</sub>(Total Width+3)] + 1

For example, a 32-bit integer requires a minimum exponent of 7 bits.

A summary of the width limits imposed by exponent width is provided in Table 4-2.

Table 4-2: Summary of Exponent Width Limits

| Floating-Point Fraction Width or Fixed-Point Total Width | Minimum Exponent Width |

|----------------------------------------------------------|------------------------|

| 4 to 5                                                   | 4                      |

| 6 to 13                                                  | 5                      |

| 14 to 29                                                 | 6                      |

| 30 to 61                                                 | 7                      |

| 61 to 64                                                 | 8                      |

### **Internal Precision Tab**

The Internal Precision tab is used only for the Accumulator. The values in these fields may be dynamically updated by the Vivado IDE when other operators are selected, but they may be safely ignored because these values are used only by the Accumulator operator. The tab allows you specify the following:

- Accumulator MSB

- Accumulator LSB

- Input MSB

See Configuring the Accumulator for more information.

### **Optimizations Tab**

#### Architecture Optimizations

For multiplication (double precision), addition/subtraction and Accumulator operations, it is possible to specify a latency optimized architecture, or speed optimized architecture. The latency optimized architecture offers reduced latency at the expense of increased resources.

#### Implementation Optimizations

- DSP Slice Usage allows the level of slice multiplier use to be specified.

- Block Memory Usage allows the level of Block Memory use to be specified.

#### DSP Slice Usage

The level and type of multiplier usage depends upon the operation. See the Vivado IDE for details on how many DSP Slices are used for each configuration.

#### Block Memory Usage

Block memory usage can be specified for the Exponential operator. Table 4-3 summarizes the options for block memory.

| Table 4-3: | Block Memory Usage for Exponential Operator |

|------------|---------------------------------------------|

|------------|---------------------------------------------|

| Block Memory Usage | Single             | Double             |

|--------------------|--------------------|--------------------|

| No usage           | Distributed memory | Distributed memory |

| Full usage         | 1 RAMB36           | 5 RAMB18           |

A single block memory is also used for the half precision square root, reciprocal and reciprocal square root implementations.

www.xilinx.com

### **Interface Options Tab**

#### Flow Control Options

These parameters allow the AXI4-Stream interface to be optimized to suit the surrounding system.

- Flow Control

- **Blocking** When the core is configured to a Blocking interface, it waits for valid data to be available on all input channels before performing a calculation. Back pressure from downstream modules is possible.

- **NonBlocking** When the core is configured to use a NonBlocking interface, a calculation is performed on each cycle where all input channel TVALIDs are asserted. Back pressure from downstream modules is not possible.

- Optimize Goal

- **Resources** This option reduces the logic resources required by the AXI4-Stream interface, at the expense of maximum achievable clock frequency.

- Performance This option allows maximum performance, at the cost of additional logic required to buffer data in the event of back pressure from downstream modules.

- **RESULT channel has TREADY**

- Unchecking this option removes TREADY signals from the RESULT channel, disabling the ability for downstream modules to signal back pressure to the Floating-Point Operator core and upstream modules.

#### Latency and Rate Configuration

This parameter describes the number of cycles between an operand input and result output. The latency of all operators can be set between 0 and a maximum value that is dependent upon the parameters chosen. IP cores that are intended for many applications, such as the Floating-Point Operator core, are designed to run as fast as the DSP primitives. To achieve this, the fabric logic must be heavily pipelined, leading to relatively high latency. For designs which run at a relatively low frequency, the latency can be reduced while timing can still be met. For instance, if the fully pipelined design with latency=12 can meet timing at 400 MHz, then if the system clock in the user design is 70MHz, for example, then latency can likely be reduced to six and timing can still be met. However, the relationship between latency and achieveable clock speed is not linear. This is because the amount of logic between register stages is roughly the same, so if one register is removed, the achieveable clock frequency drops considerably because one register to register path now has almost double the amount of logic as other register-to-register delays. The advantage of reducing latency when clock speed allows is that the result appears sooner. There is no significant gain in resources other than an inevitable reduction in registers for which there is an ample

www.xilinx.com

supply. For the previous example, Xilinx recommends using latency=12 if the system clock is > 0.5 \* value in the resource and performance section on the Xilinx webpage for the IP core. Other latency values of use are 6, 3, 2 and 1, though minimum may apply due to FIFOs and feedback stages. Therefore, there is not much use in setting latency to 11 for this reason.

*Note:* The Accumulator operator has a minimum latency of 1.

#### **Cycles per Operation**

The Cycles per Operation Vivado IDE parameter describes the minimum number of cycles that must elapse between inputs. This rate can be specified. A value of 1 allows operands to be applied on every clock cycle, and results in a fully-parallel circuit. A value greater than 1 enables hardware reuse. The resources consumed by the core reduces as the number of cycles per operation is increased. A value of 2 approximately halves the resources used. A fully sequential implementation is obtained when the value is equal to Fraction Width+1 for the square-root operation, and Fraction Width+2 for the divide operation.

#### **Control Signals**

Pins for the following global signals are optional:

- ACLKEN Active-High clock enable.

- **ARESETn** Active-Low synchronous reset. Must be driven low for a minimum of two clock cycles to reset the core.

### **Optional Output Fields**

The following exception signals are optional and are added to m\_axis\_result\_tuser when selected:

- UNDERFLOW, OVERFLOW, INVALID\_OPERATION, DIVIDE\_BY\_ZERO, ACCUM\_OVERFLOW (accumulator only) and ACCUM\_INPUT\_OVERFLOW (accumulator only)

- See TLAST and TUSER Handling for information on the internal packing of the exception signals in m\_axis\_result\_tuser.

### AXI4-Stream Channel Options

The following sections allow configuration of additional AXI4-Stream channel features:

- A Channel Options

- Enables TLAST and TUSER input fields for the A operand channel, and allows definition of the TUSER field width.

- B Channel Options

• Enables TLAST and TUSER input fields for the B operand channel (when present), and allows definition of the TUSER field width.

#### • C Channel Options

• Enables TLAST and TUSER input fields for the C operand channel (when present), and allows definition of the TUSER field width.

#### • **OPERATION Channel Options**

- Enables TLAST and TUSER input fields for the OPERATION channel (when present), and allows definition of the TUSER field width.

- Output TLAST Behavior

- When at least one TLAST input is present on the core, this option defines how the m\_axis\_result\_tlast signal should be generated. Options are available to pass any of the input TLAST signals without modification, or to logically OR or AND all input TLASTs.

### **User Parameters**

Table 4-4 shows the relationship between the fields in the Vivado IDE and the User Parameters (which can be viewed in the Tcl Console).

| Vivado IDE Parameter/Value <sup>(1)</sup> | User Parameter/Value <sup>(1)</sup> | Default Value |

|-------------------------------------------|-------------------------------------|---------------|

| Operation Selection                       | operation_type                      | Add_Subtract  |

| Absolute Value                            | Absolute                            |               |

| Accumulator                               | Accumulator                         |               |

| Add/Subtract                              | Add_Subtract                        |               |

| Compare                                   | Compare                             |               |

| Divide                                    | Divide                              |               |

| Exponential                               | Exponential                         |               |

| Fixed-to-float                            | Fixed_to_float                      |               |

| Float-to-fixed                            | Float_to_fixed                      |               |

| Float-to-float                            | Float_to_float                      |               |

| Fused Multiply-Add                        | FMA                                 |               |

| Logarithm                                 | Logarithm                           |               |

| Multiply                                  | Multiply                            |               |

| Reciprocal                                | Reciprocal                          |               |

| Reciprocal Square Root                    | Rec_Square_Root                     |               |

| Square-root                               | Square_root                         |               |

| Unfused Multiply-Add                      | Unfused_Multiply_Add                |               |

#### Table 4-4: Vivado IDE Parameter to User Parameter Relationship

| Vivado IDE Parameter/Value <sup>(1)</sup> | User Parameter/Value <sup>(1)</sup> | Default Value   |  |

|-------------------------------------------|-------------------------------------|-----------------|--|

| Unfused Multiply Accumulator              | Unfused_Multiply_Accumulator        |                 |  |

| Accumulator Primitive                     | Accumulator_Primitive               |                 |  |

| Add/Subtract and FMA Operator options     | add_sub_value                       | Both            |  |

| Compare Operator Options                  | c_compare_operation                 | Programmable    |  |

| Precision of Inputs: A Precision Type     | a_precision_type                    | Single          |  |

| Precision of Inputs: Exponent Width       | c_a_exponent_width                  | 8               |  |

| Precision of Inputs: Fraction Width       | c_a_fraction_width                  | 24              |  |

| Result Precision Type                     | result_precision_type               | Single          |  |

| Precision of Result: Exponent Width       | c_result_exponent_width             | 8               |  |

| Precision of Result: Fraction Width       | c_result_fraction_width             | 24              |  |

| Accumulator MSB                           | c_accum_msb                         | 32              |  |

| Accumulator LSB                           | c_accum_lsb                         | -31             |  |

| Input MSB                                 | c_accum_input_msb                   | 32              |  |

| Architecture Optimizations                | c_optimization                      | Speed_optimized |  |

| High_Speed                                | Speed_Optimised                     |                 |  |

| Low_Latency                               | Low_Latency                         |                 |  |

| DSP Slice Usage                           | c_mult_usage                        | No_Usage        |  |

| Block Memory Usage                        | c_bram_usage                        | No_Usage        |  |

| Flow Control                              | flow_control                        | Blocking        |  |