- 自適應計算3d狮王轮盘游戏下载

- 質量與可靠性

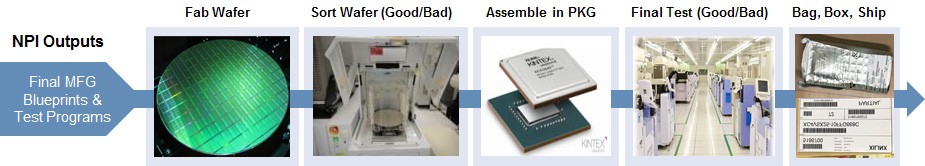

- Quality by Manufacturing

Quality by Manufacturing

AMD pioneered fabless manufacturing and continues to deliver quality products.

AMD pioneered fabless manufacturing and continues to deliver products with zero-defect using industry leading engineering with aligned supplier quality programs.

AMD Corporate Supplier Manual consists of mandatory requirements for the Supplier and AMD. It ensures that there is an adequate exchange of information between both parties, suitable controls over process changes and proactive part/material qualification and reliability analysis.

AMD has a corporate objective of attaining 6-Sigma quality for all products and processes and services; this is achieved through a goal for our suppliers of less than 10 defects per million and a goal of having all key processes at a Cpk of 2.0 or greater. AMD implemented statistical process control (SPC) and maverick control at each critical step in the fabrication process, assembly process and production testing.

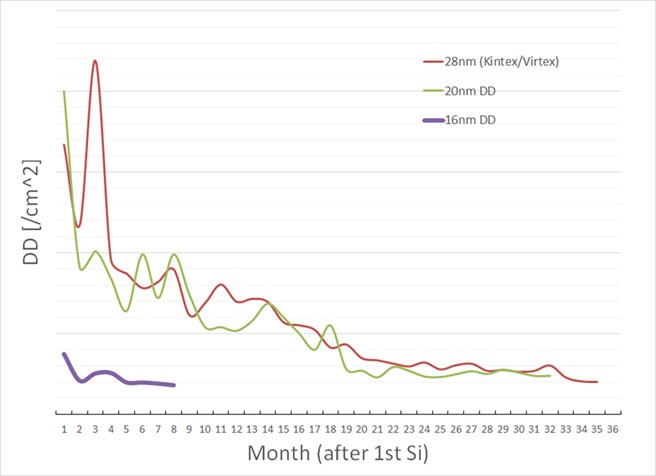

Figure 1. Defect Density (DD) decreases over time due to manufacturing improvements. In 16nm, DD starts low due to numerous improvements learned from previous generations.

Supplier performance is monitored on a regular-basis and ratings evaluated by AMD through key metrics:

- Delivery of product quality

- Customer disruptions including field returns

- Delivery schedule performance

- Special status customer notifications related to quality or delivery issues

AMD invested years of effort using Process and Performance Learning Vehicles (PPLVs) to improve the quality of processes, materials, and techniques.

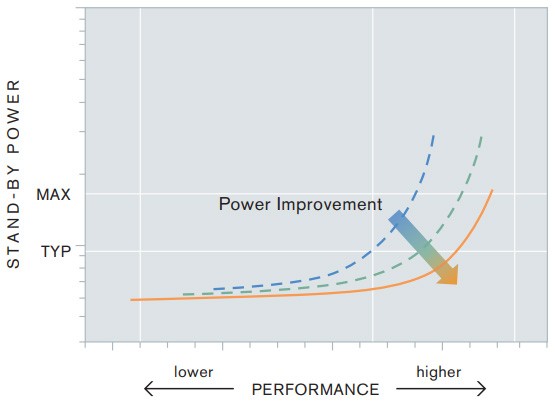

Besides leveraged learnings, AMD introduced tighter controls and improved alignment with foundry and processes. As a result, we achieved robust wafer-level reliability (WLR) and lower defect densities for reduced excursion rates. Currently, AMD 28/20/16nm yield results have exceeded previous generation benchmarks, met production milestones, and achieved power reductions of greater than 50% compared with previous generations.

The High-Performance Low-power (HPL) process at TSMC was pioneered in partnership with AMD and allowed AMD to ship the industry’s first 28nm devices in 2011. Long before customers saw a single 28nm device. For more information, refer to DFM (Design for Manufacturing).

Figure 1. In 2011, AMD was the first in the industry to tape out 28nm. Since then, the 7 series devices have exemplified the resulting HPL process benefits for customers, including lower power and higher yields.

Package Assembly

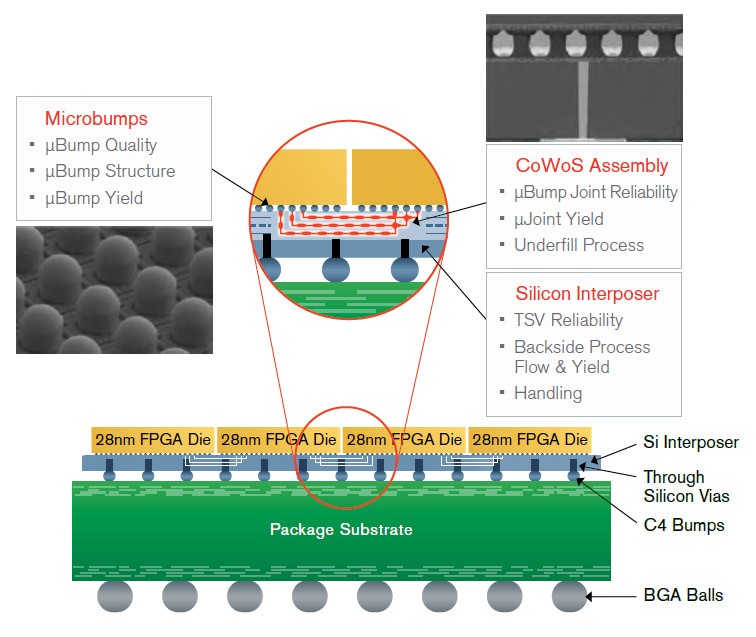

AMD introduced the world’s first 3D FPGA in 28nm – the AMD Virtex 7 FPGA V2000T followed by the Virtex UltraScale FPGA VU440 in 20nm. Both represent a breakthrough in packaging technology and assembly that required very stringent qualification and test. The industry’s second-generation 3D IC required further advancements that AMD and its Supply Chain was able to deliver, including:

- Low-loss organic packaging for robust board-level reliability & optimal signal integrity.

- Optimization of package substrate material and interposer resistivity to achieve 33Gb/s and now 56Gb/s system channel characteristics.

- Design and timing verification of high-performance inter-die interconnects.

- 3D thermal-mechanical modeling and analysis for package reliability, addressing package co-planarity issues and stresses introduced by the interposer.

AMD 3D ICs have exceeded JEDEC reliability required by 4x over the past three generations (28nm, 20nm and 16nm).

Figure 1. Heterogeneous 3D FPGA enabled by SSI Technology.

AMD comprehensive test coverage and a redesigned characterization process allowed the launch of the 28nm families with zero production errata. Circuits are tested for overall voltage, temperature, and frequency ranges. Learning on the AMD 6 series and early learning on the 7 series (28nm) provided deeper collaboration and engagement sooner in the design stage. Yields consisting of 50x more samples with first silicon, along with greater access to engineering boards for verification and characterization, allowed the highest data collection across functional teams compared with previous generations. As a result, the 7 series exceeded 99% of target goals on time without any changes in specifications. Additional enhancements were applied to 20nm and 16nm test and characterization, including Volume-System-Level (VSL) testing.

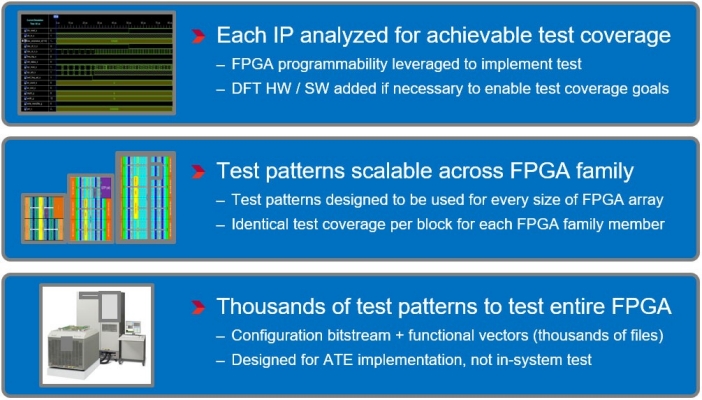

AMD continuously improves the test coverage of its products by implementing various DFT methods.

Operational Excellence with Absolute Quality

AMD has applied its supply chain model across every family and every device in the product portfolio spanning with absolute quality and delivery. Our commitment is further demonstrated by the expansion of our portfolio from FPGAs to the highest capacity 3D ICs, adaptive SoC dual core SoCs, and heterogeneous multi-processing SoCs offering the highest levels of quality, reliability, security and safety.

- Strong supplier management, partnership

- Manufacturing Excellence

- Control and Detection Engine

- Unique 2D barcode for each die enabling “cloud binning” for effective product supply chain

- Stable yield and on-time delivery

- Increased testing at wafer sort and assembled final product.

- Meeting program needs with >15 years

- Long reliable storage capability

AMD smart and robust supply chain methodology enable stability & long-term product availability.

Our proven supply-chain and business continuity plans enable long reliable mapping and planning process with customers which include scenario planning with demand analysis and data triangulation for volatile market.

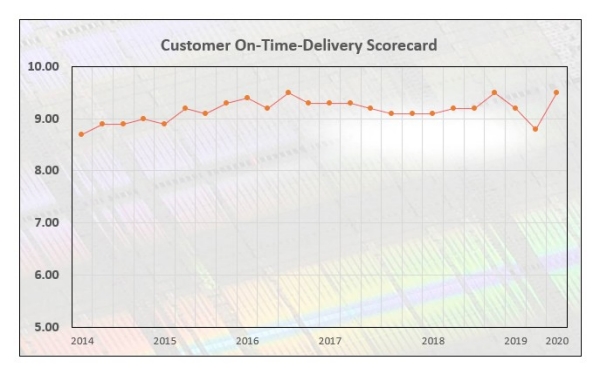

AMD product On-Time-Delivery (OTD) is demonstrated by customer scorecards and direct engagement.

Figure 1: AMD operational excellence is represented by customer scorecard (rating 0 to 10). These are direct customer feedback scores in which 30% are perfect 10s in the last 4 quarters.