AMD Vitis™ 軟件平台的新增功能

AMD Vitis™ 軟件平台 2024.1 版本亮點:

AMD Versal™ AI 引擎 DSP 設計的增強功能

- 為 AMD Versal AI Core 係列增強了 DSP 庫函數

- 麵向 SSR > 1 的時分複用 (TDM) FIR 濾波器函數

- 支持 32 位旋轉的 FFT

- 混合基數 3 及混合基數 5 FFT

- Kronecker 矩陣積

- 基於 Householder 的 QRD 求解器可提高穩定性

- 麵向 SSR > 1 的 DFT

- 最新 DSP 庫函數適用於支持 AIE-ML 的 AMD Versal AI Edge 係列

- 支持 SSR 的通用矩陣向量 (GEMV)

- 支持 SSR 的通用矩陣乘法 (GEMM)

- AIE API 增強

- 支持基數 3/ 基數 5 FFT

- AIE 仿真器增強

- 周期近似仿真功能可通過 PL 實現 AI 引擎設計,無需控製、接口和處理係統 (CIPS) IP 核

- AMD Vitis 分析器支持通過 VCS、Questa、Xcelium 和 Riviera 等第三方仿真器仿真硬件

麵向 Vitis 統一軟件平台的重要改進

- 新器件支持:AMD Versal™ Premium VP1902 自適應 SoC、AMD MicroBlaze™ V 處理器

- 針對 Windows® 環境增強了嵌入式應用開發與 BSP 生成

- 用戶管理流程,調試外部編譯的嵌入式應用

- 最新 Bootgen GUI

- 為平台項目啟用增量構建

AMD Vitis IDE(新 GUI)的主要改進

- 增加了對處理子係統層級調試的支持

- 增加了對項目/工作區導出與導入的支持

- 增加了對 Python 解釋器及 API 的支持

- 新特性預覽頁麵

- 嵌入式、AIE 及平台項目的新文件修改通知

AMD Vitis 新增功能(類別)

為 AMD Versal AI 內核係列增強了 DSP 庫函數

- 麵向 SSR > 1 的時分複用 (TDM) FIR 濾波器函數

- 支持 32 位旋轉的 FFT

- 混合基數 3 及混合基數 5 FFT

- Kronecker 矩陣積

- 基於 Householder 的 QRD 求解器可提高穩定性

- 麵向 SSR > 1 的 DFT

最新 DSP 庫函數適用於支持 AIE-ML 的 AMD Versal AI Edge 係列

- 支持 SSR 的通用矩陣向量 (GEMV)

- 支持 SSR 的通用矩陣乘法 (GEMM)

AIE API 增強

支持 Radix-3/Radix-5 FFT

AI 引擎仿真器增強

- 周期近似仿真功能可通過 PL 實現 AI 引擎設計,無需控製、接口和處理係統 IP 核 (CIPS)。

- Vitis 分析器支持通過 VCS、Questa、Xcelium 和 Riviera 等第三方仿真器仿真硬件

- 將表格從 Vitis 分析器導出為 CSV 格式

- 最新 DSP 函數支持 AMD Vitis Model Composer 中的 AIE 和 AIE-ML

- 時分複用 (TDM) FIR 濾波器函數

- 用於構建 1 GSPS 及更高吞吐量的多相信道器

- DFT/IDFT:提供 SSR 支持

- 針對小尺寸進行了吞吐量/時延轉換的優化

- FFT/IFFT:針對 CINT32 位旋轉提供更廣泛的支持

- 混合基數 FFT/IFFT:提供 AIE-ML 支持

- Model Composer Hub 塊的易用性改進

- 硬件驗證流程增強

- v 2024.1 增強了對 OS 和 MATLAB® 版本的支持:

- RHEL 9

- MATLAB R2023a and R2023b

新的示例設計可在 Github 上找到。

新模板程序可簡化圖像和視頻過濾器的 HLS C++ 代碼

全新庫函數向導進入 AMD Vitis 庫 github 庫

- 為 AMD Vivado 設計工具創建“求解器”及“視覺 ”(OpenCV 兼容)IP

- 運行可用庫範例

內存接口 (ap_memory) 的 Pragma 現在可捆綁 AMD Vivado IP Integrator 的端口

最新 HLS 組件比較可並列顯示兩個以上組件的數據記錄

支持用用戶提供程序 RTL 代碼來替換 C++ 函數(黑盒流程)

代碼分析器現在可分解 C++ 結構成員,微調性能分析

適用於 HLS 全局 FSM 編碼和安全狀態選擇的新用戶控製

在 C-Simulation 期間訪問 Clang 消毒器,以執行地址及初始化檢查

Vitis™ 軟件平台 2023.2 版的亮點:

Versal™ AI 引擎 DSP 設計的增強功能

- 最新 DSP 庫功能

- 為 DSP 功能提供的最新 API 支持

- AI 引擎編譯器及仿真器的新特性

全新的獨立 Vitis 嵌入式軟件

- 為針對 Arm® 嵌入式子係統編寫 C 代碼的設計人員提供的較小獨立式安裝程序

- 提供了所有的嵌入式特性,其中包括 Bootgen 和 XSCT 等實用程序

最新 Vitis 統一集成型設計環境

- 在所有 Vitis 工作流程中提供的一致性 GUI 和 CLI

- 基於 Eclipse Theia 的新一代 GUI 可為提高工作效率提供更優異的靈活性及用戶友好型特性

Vitis 新增功能(類別)

AI 引擎的最新 DSP 庫功能

- 混合基 FFT

- Discrete Fourier Transform (DFT)

- 通用矩陣向量乘法 (GEMV)

為 DSP 功能提供的最新 API 支持

- 支持 cint32 旋轉數據類型的 FFT IP

- 支持 Radix-4 FFT API 的 cint16

- 矢量化的“fix2flt”以及在 API 中執行的“flt2fix”

為 AIE-ML 提供的最新 API 支持

- API 現在在 sliding_mul() 函數中支持 int32/cint32 數據類型

- API 現在在 sliding_mul() 函數中支持 數據類型

- 支持稀疏矩陣乘法所需的所有 AIE API 例程

- AIE 編譯器現在可按輸入輸出支持 2D 及 3D 陣列

- Vitis 分析器現在可生成指導報告來調整 FIFO 大小

- 為多線程仿真器內核及值更改轉儲 (VCD) 分析器加速提供的最新支持

- 與 MATLAB® 環境和 Python 流量生成器的外部接口連接

- 增強的 AXI Stream 模型可為 PLIO 對齊的空/等待周期提供支持

- 更強的設計規則檢查

- 通過高速調試實現的 AI 引擎跟蹤卸載

- 在 Vitis 環境中提供 NoC 及硬 DDRMC 分析支持。

- Vitis 工具現在支持 VEK280 和 Alveo™ V70 AI 推斷加速卡的 AIE-ML 跟蹤

AI 引擎模塊更新

- 可將 AIE-ML 圖形按模塊導入 Vitis Model Composer

- 用於在 Vitis Model Composer 中實現 AIE 和 AIE-ML 的最新 DSPlib 函數

- 在 Simulink® 工具中針對內部信號繪製 AIE 仿真器輸出圖

HLS 內核模塊更新

- 自動測試台生成

- 擴大了 HLS 內核模塊的數據類型支持範圍

Vitis Model Composer 和 Vitis 工具的完美整合

- 直接從 Vitis Model Composer 生成 .xo 和 libadf.a 文件

其它增強功能

- MATLAB® 工具版本支持:R2021a、R2021b Update 6、R2022a Update 6、R2022b

- 為硬件驗證流程提供的其它拓撲

- 從 GitHub 提供的最新示例輔助資料

- HLS 組件的最新 Vitis 統一 IDE

- 最新 Vitis HLS 許可證要求

- 用於在運行 C 綜合之前獲得性能估計的最新代碼分析器特性

- AXI 接口的增強功能:

- 支持 HLS AXI Stream 側通道

- 支持用戶可配置的 AXI 主機高速緩存

- 其它增強功能:

- 最新代碼複雜性報告,可在 C 綜合過程中識別設計尺寸問題

- 編譯時間縮短:與 2023.1 相比,2023.2 的平均編譯時間縮短了 20% *

* 基於 2023 年 8 月 10 日在 1000 個 Vitis L2/L3 代碼庫設計間的測試,Vitis HLS 版本 2023.2 與 Vitis HLS 2023.1 相比。測試時的係統配置:Intel Xeon E5-2690 v4(2.6GHz CPU)、256GB RAM、RedHat Enterprise Linux 8.6。實際性能會有所不同。係統生產商可能會改變配置,進而會有不同的結果。-VGL-04

Vitis 軟件平台 2023.1 版的亮點:

Versal™ AI 引擎 (AIE) 陣列的最新 Vitis™ 庫功能

- DSP 庫函數 — 更多 FIR 過濾器配置

- 求解器庫函數 — 更高性能的增強

Versal AI Core 和 AI Edge 係列的設計流程增強

- 為作為輸入/輸出的 2D 及 3D 陣列提供 AIE 編譯器支持

- 為 FIFO 大小調節提供 AIE 仿真器指導支持,以避免死鎖情況

- AIE 狀態報告增強

- Vitis 分析器的最新默認 GUI

為 Vivado™ 環境的 Vitis 環境導入提供支持

- 幫助 Vitis 及 Vivado 工具開發團隊基於通用接口檢查點並行工作

Vitis 新增功能(類別)

DSP 庫 — FIR 過濾器

- 增強了部分重新采樣器 FIR、單速率 FIR、半頻帶 FIR 和速率變化 FIR,可為係數位寬提供支持,使其大於數據位寬

- 此外,部分重新采樣器 FIR 不僅可使用多個 AIE 塊支持 SSR 工作,而且還可整合係數重新加載特性

求解器庫

- 通過高性能流媒體設計增強了API 性能(大約 300 個塊)

- 為 4D 數據移動設備函數提供 QR 及 Cholesky 分解支持,以幫助從 AIE 陣列讀取或寫入數據

- 除 1D 外,AIE 編譯器現在可按輸入輸出支持 2D 及 3D 陣列。

- AIE 編譯器支持圖中圖構圖(子圖)和條件端口構造。

- 最新 AIE CINT 至 CFLOAT 數據轉換 API。

- AIE 狀態報告增強,可生成一個包含各種信息的文件,這些信息涉及設計中 AIE-ML 及 AIE 塊上的塊、事件以及其它寄存器。

- 通過高速差分對 (HSDP) 卸載 AIE 事件跟蹤,而不是將其存儲在 Versal 器件上的內存中。

- 在 Vitis 環境中提供 NoC 及硬 DDR MC 分析支持。

- AIE 窗口事件跟蹤,可用於檢查應用的特定部分。

- 指導調整 FIFO 大小,以免死鎖。

- 能夠選擇 AIE 仿真器報告的節點,以縮小仿真器 VCD 文件的大小並加速仿真。

- AIE 仿真器現在可生成一個報告(其可在 Vitis 分析器中查看),該報告會顯示哪個 AIE 有內存訪問違規,以及這些違規如何與圖形 C 代碼中的行對應。

- 此外,跟蹤視圖數據可視化現在還支持 AIE-ML 陣列。

- 為針對 Versal AI 引擎的 FIR 過濾器配置提供最新數據類型支持

- 在 Versal 自適應 SoC 中提供針對 DSP58 優化的兩個新浮點函數

- 針對 Versal AI 引擎的所有 Vitis Model Composer 庫函數提供更快的響應時間

- 其它增強功能:

- HLS 內核模塊的增強

- Vitis Model Composer 中心的增強

- 支持 MATLAB 工具 R2021a、R2021b 以及 R2022a 版本

- 性能提升*:與 2022.2 相比,2023.1 的平均時延縮短了 5.2%

- 在 Vitis HLS 工具中下載、查看和實例化 L1 庫函數的簡單方法

- 在 Vitis HLS 工具中增強了對 AXI 事務處理及猝發報告的支持

備注:

* 截至 2023 年 2 月 12 日,停止在所有 1208 個 Vitis L1 庫 C 代碼設計上執行基準測試。所有設計都使用一個支持 2P Intel Xeon E5-2690 CPU 的係統運行,該 CPU 支持 CentOS Linux,啟用了 SMT 並禁用了 Turbo Boost。預計硬件配置不會影響軟件測試結果。結果可能會因軟件及固件設置和配置而異 — VGL-03

Vitis 軟件平台 2022.2 版的亮點:

Versal™ AI 引擎 (AIE) 陣列的最新 Vitis™ 庫功能

- DSP 庫功能 – 增強特性

- 求解器庫功能

- 視覺庫功能

- 超聲波庫功能

Versal AI Core 和 AI Edge 係列的設計流程增強

- 在 AI 引擎陣列中控製內核的相對位置,提升性能和利用率

- AIE x86 仿真器增強,在 x86 仿真器中增強了死鎖條件的建模

- AIE API 增強,增加了基數 3/5 FFT 和矩陣‘x’矢量 API

- 增強了 Versal 設計的分析和調試功能,支持死鎖檢測、更大規模的跟蹤數據收集以及 RTL/Python 測試台

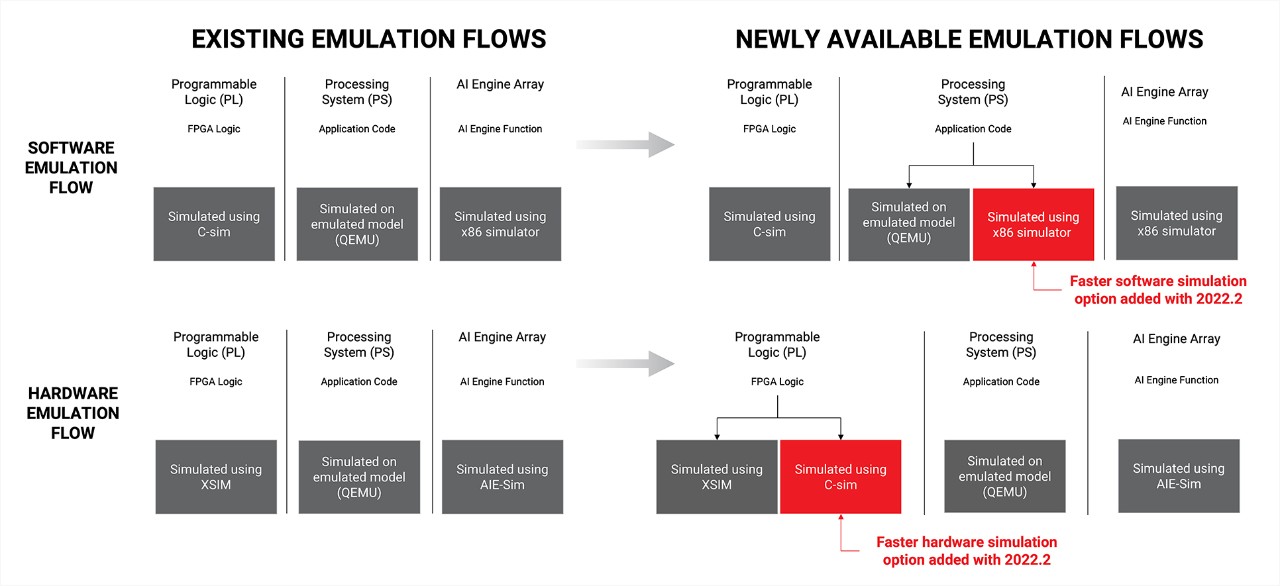

- 在 Vitis 中為異構設計提供了新的仿真選項

Vitis 新增功能(類別)

DSP 庫功能

- AI 引擎上的超級采樣率 (SSR) FIR 濾波器執行方案現在支持係數重新加載特性和動態點大小

- 為目標是 AI 引擎陣列的 FFT 函數新增 FFT 開窗元件

求解器庫函數

- 正交旋轉 (QR) 分解

- Cholesky 分解

視覺庫功能

- 針對 AI 引擎陣列的四個新視頻功能

超聲波庫函數

- 幫助構建醫療超聲設計的各種功能

- 能夠通過添加約束來控製 AI 引擎陣列中內核的相對位置,有助於用戶提高性能和利用率

- 改進了 x86 仿真器中 AIE 死鎖條件的建模

- 新增 AIE API,增加了基數 3/5 FFT 和矩陣‘x’矢量 API

- 在硬件仿真中生成 AI 引擎分析報告

- 使用 AMD 係統調試器 (XSDB) 對 AI 引擎設計以及基於 PL 的設計進行死鎖檢測

- Xilinx 運行時 (XRT) 控製了 AI 引擎事件跟蹤通過 PLIO 的連續卸載

- 支持 x86 主機上麵向軟件仿真的 PS 應用

- 硬件仿真可以使用 SystemC 功能模型而不是 RTL

- 允許用戶使用簡單的 RTL 測試台或基於 Python 腳本的流量生成器仿真 AI 引擎內核

- AI 引擎的狀態可以在使用 Vitis™ 分析儀進行硬件仿真時分析

Vitis 環境 2022.2 全新仿真選項:處理器係統 x86 仿真和 AI 引擎 x86 仿真:可編程邏輯仿真可使用 x86 仿真器執行。

Versal AI 引擎設計的特點

- 能夠為 AI 引擎 DSP 庫模塊設計添加圖形約束,從而可提高利用率和性能

- 為 AI 引擎設計提供周期近似仿真的新功能

- AI 引擎圖形導入模塊可自動檢測運行時參數 (RTP) 端口

- 增強並增加了 DSP 庫模塊

一般功能

- 為使用 PL 及 AIE 陣列的異構係統設計提供了硬件驗證流程支持

- Vitis Model Composer Hub 模塊已更新,現在支持異構設計

- 自動檢測有效的 AI 引擎、HDL 和 HLS 子係統

- 增強的硬件驗證流程以支持僅包含 HDL 模塊的設計和包含適用於 Versal 平台的 HDL-to-AI 引擎 → HDL 模塊的設計

- 增強了“任務級並行”編碼風格支持

- 可提高 C 語言仿真速度及 QoR

- 其它性能及時序增強

- 提高了猝發推斷能力

- 自動推斷 Unroll、Pipeline、Array_Partition 和 inline 編譯指示以實現更好的性能

- 提高了定時精度,能夠以更高的頻率更完美地完成時序收斂

- 其它特性

- 分析和調試:在 C 代碼中插入的 printf,現在即使在 RTL 中綜合之後也支持

- 易用性:新的性能語法可自動實現給定的事務處理時間間隔

- FFT 和 FIR IP 現在支持 HLS::stream 接口

Vitis 軟件平台 2022.1 版的亮點:

麵向 Versal™ ACAP 和 AI 引擎的 Vitis™ 流程提升

- 支持 AMD 基礎 DFX 平台,該平台具有一個靜態區域和一個 DFX 區域

- AIE 分析不僅支持失速/死鎖檢測,而且還可在 Vitis 分析儀中生成 AI 引擎狀態(包括錯誤事件)視圖報告

- x86sim、AIEsim 和軟件仿效中的外部流量生成器靈活度顯著提高,可以非常輕鬆地插入仿真及仿效流程中

- Vitis Model Composer 支持硬件驗證、Linux 和硬件仿真

麵向 DC 和 Vitis HLS 的 Vitis

- Vitis 可為動態區域生成過程提供額外的報告支持,流程報告增強功能包括 3 個全新或更新的報告

- 通過選擇將跟蹤轉移至內存資源(首選)或轉移至 PL 中的 FIFO, Vitis 改進了 PL 分析,因此可獲得更高的性能

- 現在在仿真後提高一個新的時間軸跟蹤查看器,其可顯示運行時配置文件,允許用戶留在 Vitis HLS GUI 中

- 通過新的性能編譯指示或 set_performance_directive,Vitis HLS 現在可支持更高層次的“智能”構造

- Vitis 圖形庫針對性能提供 L3 API 增強功能(可為內核調用節省 1mS 的時間)

Vitis 新增功能(類別)

- 新增基因組學加速庫(L1 和 L2 以及 L3

- 圖形庫:L3 性能提升

- Vitis 數據庫庫、GQE 多功能內核

- 在視覺庫中增加了新的功能

- Vitis AIE 視覺庫增加/增強的新功能

- Vitis AIE DSP 庫,FIR 重采樣器取代 FIR 分數插值器

- Vitis 編解碼器庫最新 API、API jxlEnc、API‘leptonEnc’、API‘resize’、API‘WebpEnc’ Vitis 編解碼器庫最新 API、API jxlEnc、API‘leptonEnc’、API‘resize’、API‘WebpEnc’

- ZLIB 壓縮改進,為 8KB 解決方案提供了定製八核壓縮

- ZLIB 解壓改進,為 8KB 文件大小提供了定製 IP

- 平台功能查詢改進

- HBM 易用性改進,能夠為 M_AXI 內核選擇一個進入 HMSS 的特定 S_AXI 入口點並可從配置文件支持 RAMA 插入

- AI 引擎的硬件自動失速/死鎖檢測分析

- 分析自動狀態輸出

- 分析自動狀態輸出 — 緩衝區

- 分析硬件手動狀態輸出

- 分析手動狀態輸出

- AI 引擎事件跟蹤增強

- 外部流量生成器 AIEsim

- AI 引擎硬件分析改進

- AI 引擎支持廣播窗口

- Vitis AI 引擎編譯器增強了圖形編程模型

- Vitis AI 引擎編譯器 — ADF 圖形的 PLIO/GMIO

- 分析增強,最新時間軸跟蹤查看器

- 編碼風格增強,為模塊流類型提供陣列分區支持

- 編譯指示抽象,最新性能編譯指示(和指令)

- Vitis 內核“單行方式”Vitis HLS — 最新時間軸跟蹤查看器、最新性能編譯指示、模塊流支持窗口

- 顯示設計中所有幸存函數的運行時配置文件,即那些被轉換為模塊的函數

- 查看數據流區域在聯合仿真後的行為特別實用

- 原生 Vitis HLS — 不再需要啟動 xsim 波形查看器(外部工具)

- Vitis 分析儀改進,保存/恢複時間軸定製

- 報告增強、report_qor_assessment、xclbin 時鍾信息、Vivado 自動摘要

- 分析增強,啟用最新 PL 分析基礎架構,可以添加多個 trace_memory 選項來插入多個內存監控器(僅硬件),v++ 鏈接器的示例配置文件不僅可將 SLR0 中所有 CU 的跟蹤數據卸載至 DDR0,而且還可將 SLR1 中所有 CU 的跟蹤數據卸載至 DDR1

- 為 Versal 更新了 Bootgen GUI

- 工具鏈更新

- XSCT,支持 STAPL 並添加鏈接器腳本生成命令

- 係統編譯流程,請參見係統編譯文檔

- 為自動重啟添加軟件仿真支持並為始終運行的內核添加郵箱支持

- 免費運行的內核不需要為 sw-emu 提供 while(1)

- 為外部流量生成器添加軟件仿真支持v

- 硬件仿真可以為流媒體 IP 使用 HLS C 源碼功能模型。

- 增加 API xrt::system,用於嗅探器件數量

- 為日誌消息添加 API xrt::message

- RT 本地 API 主機代碼現在需要

-std=c++17 或 abovev - 為同步執行異步運行添加實驗 xrt::queue API

- xbutil 可以顯示 AIE FIFO 計數器,其有助於調試 AIE 死鎖場景

- xbutil — 清除原有選項。

- xclbinutil — info 可為嵌入式平台提供時鍾信息

- ARM 上的 xbutil 可加載 SOM 圖像

- xbtop xbtop 獨立實用程序,用於顯示類似 linux 的輸出(替換舊版 xbutil -top)

- 提供 XRT 實用程序支持 在 Bash 中使用製表鍵自動完成。

- Alveo 平台更新、可實現更高穩定性的平台更新、板卡管理更新、SC 固件更新工具

- 嵌入式平台,最新 VCK190 DFX 平台:xilinx_vck190_base_dfx_202210_1,現在可使用 Vitis 安裝嵌入式平台, Vivado 新增可定製示例設計:MPSoC 的 Vitis 平台

- 針對可擴展性和易用性對 Vitis Model Composer 中心模塊進行了全麵檢修

- 硬件驗證流程現在除了支持裸機外,還支持 Linux

- “AIE 至 HDL”和“HDL 至 AIE”模塊不再提供 HDL 網關模塊

- 2022.1 版本現在為無法訪問互聯網的客戶提供示例快照。發布新版示例時,該工具將提示用戶從 GitHub 下載

- 為了便於使用,不屬於代碼生成部分的實用程序塊現在以白色為背景顯示

- 為了方便使用,增強並重組了庫瀏覽器

- 支持 RHEL 8.x

- MATLAB 支持 - R2021a / R2021b

Vitis 軟件平台 2021.2 版的亮點:

- 全新特定域開發環境

- 全麵端到端流程支持 VCK5000 和 Varium C1100 卡

- 增強內核工具功能

- Vitis AI Engine Compiler C/C++ 高層次抽象 API、Auto Pragma Inference、Area Group Constraints

- Vitis AI Engine x86simulator 增強功能:跟蹤報告、內存訪問衝突和死鎖檢測

- 包含 Vitis HLS EoU、時序和 QoR 增強、HLS API,用於用戶控製的突發推斷

- Vitis Analyzer 增強功能可提供更好的時間線跟蹤報告、數據可視化、停頓分析

- 麵向 AI 引擎多進程的 Vitis XRT 和麵向 AI 引擎圖形控製的多線程支持

- Vitis IDE & Emulation 支持 AI Engine Trace 和軟件仿真,適用於 AI 引擎應用

- 不同域中 39 個全新 C/C++ 庫涵蓋 DSP、數據分析、視覺、壓縮、數據庫、圖形、安全,……總計超過 1000 個庫函數、數據庫、圖形、安全……

- Vitis Model Composer

- 編譯/仿真時間減少 3 倍,並行編譯將編譯時間銳減 7 倍

- 全新的硬件驗證流程和增強的功能協同仿真

Vitis 新增功能(類別)

注:Vitis 加速庫現已提供,可以單獨下載。它們可以從 GitHub 中下載,也可以直接從 Vitis IDE 中下載。

| 庫 | 2021.1 | 2021.2 | 21.2 版的新增功能 |

|---|---|---|---|

| xf_blas | 167 | 167 | 0 |

| xf_codec | 3 | 3 | 0 |

| xf_DataAnalytics | 33 | 36 | 3 |

| xf_database | 62 | 65 | 3 |

| xf_compression | 78 | 93 | 15 |

| xf_dsp | 94 | 96 | 2 |

| xf_graph | 53 | 59 | 6 |

| xf_hpc | 37 | 37 | 0 |

| xf_fintech | 116 | 116 | 0 |

| xf_security | 135 | 140 | 5 |

| xf_solver | 11 | 11 | 0 |

| xf_sparse | 11 | 11 | 0 |

| xf_utils_hw | 55 | 57 | 2 |

| xf_opencv | 147 | 150 | 3 |

| 總共 | 1002 | 1041 | 39 |

注:對於視覺,隻需計算 L*/tests 中的子文件夾數量,因為每個 API 都針對不同的類型提供多項測試

可編程邏輯 (PL)

- 基於 CLAHE TMO 的端到端單聲道圖像處理 (ISP)

- RGB-IR 和 RGB-IR 圖像處理 (ISP) 流水線

- 全局色調映射 (GTM) 以及使用 GTM 的 ISP 流水線

| 全新功能 | 種類 | 客戶/戰略 | 行業 | 說明 |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | 汽車、ISM | •支持 4x4 RGB-IR 去馬賽克 •主要用於艙內監控係統 •微光監控攝像頭 |

| Mono (CCCC) | ISP | Strategic | 汽車、ISM、A&D | •機器視覺 •低光應用 |

| 全局色調映射 (GTM) | ISP | Strategic | 汽車、ISM、A&D | •擴大了動態範圍,提高了對比度 •與本地色調映射 (LTM) 相比,是一個成本更低的版本 |

| 密度光流算法 TV-L1 | CV | NTT | ISM | •改進了光流對光照、噪聲及遮擋的穩定性 |

AI Engine (AIE)

- BlobFromImage

- 支持批量 3 的背靠背 filter2D

| 全新功能 | 種類 | 客戶/戰略 | 行業 | 說明 |

|---|---|---|---|---|

| RGB-IR | ISP | Seeing Machines | 汽車、ISM | •支持 4x4 RGB-IR 去馬賽克 •主要用於艙內監控係統 •微光監控攝像頭 |

| ML+X | ISP | Strategic | 汽車、ISM、A&D | •ML 幹擾預處理 |

| 高斯金字塔 | CV | Strategic | 汽車、ISM、A&D | •多尺度圖像處理的基礎 |

| 方框濾波器 | CV | Strategic | 汽車、ISM、A&D | •流暢低通濾波器的基本知識 |

基於 Vitis 庫的 Vitis 區塊鏈解決方案

- 以太坊的開創性采礦解決方案

- 使用 C++ 通過 Vitis 庫實現開源與易用性及易於部署性

- 使用 Vitis 庫實現靈活性及可擴展性

- 靈活地開采多種比特幣

- 定製並編譯成硬件

- 高度優化的設計

將 CSV 解析器 API 添加到庫中

- CSV 解析器可解析逗號分隔值文件並生成對象流,其可輕鬆與 DataFrame API 連接

- 新增全新 L2 庫

- Louvain 與重新編號

- 重新編號

- 餘弦相似度支持“權重”特性

- GQE 開始支持異步輸入輸出特性,並提供多卡支持。

- 異步支持允許 FPGA 在部分輸入數據準備就緒時開始處理。

- 多卡支持允許識別多個適合工作的 Alveo 卡。

- ZSTD 多核壓縮

- 不僅創建了全新 ZSTD 多內核架構,而且還使用四核提供了超過 1GB/s 的吞吐量。

- ZSTD 減壓縮優化

- ZSTD 解壓縮針對性能(提高了 20%)和資源(減少至不足 30%)進行了優化

- 針對 IBM 改進了 GZIP/ZLIB 數據流內核

- 定製了靜態及動態壓縮流媒體 IP(4KB 和 8KB)

- 增加了在 TUSER 端口提供壓縮量的功能

- 針對 IBM 改進了 GZIP/ZLIB 解壓縮

- 優化了霍夫曼解碼器,可減少周期不足 1.5K 的時延

- 將資源從超過 9K 銳減至 6.9K

- 添加 ADLR32 校驗和功能

- GZIP 係統編譯器 PoC

- 為 GZIP 壓縮解決方案創建了一個係統編譯器 PoC,並針對 OpenCL 主機進行了基準測試。

- 自 2021 年起,將在 Github 上提供 DSPLib

- 快速傅裏葉變換 (FFT/iFFT)

- 點大小增加到 32k(取決於數據類型)

- 支持數據流 API 和窗口 API。

- 並行供電(0 — 4)

- 不僅允許提高吞吐量,而且還可擴展所支持的點大小的範圍

- FIR 濾波器

- 初始數據流支持單速率非對稱/對稱 FIR

- DDS/Mixer

- 2021.2 提供全新庫單元

發布 KECCAK-256(散列函數)和 CRC32C(校驗和函數)

為調試硬件問題添加了兩個 Data-Mover 實現方案。

- 帶計數器的 LoadDdrToStream:用於通過 AXI 流把 PL 的 DDR 數據加載至 AI 引擎並記錄發送至 AI 引擎的數據數。

- 帶計數器的 StoreStreamToMaster:用於通過 AXI 流從 AI 引擎接收數據並將其保存至 PL 的 DDR,同時記錄發送至 DDR 的數據數。

AI 引擎 API

- 按 C++ 報頭專用文件庫實現,其所提供的類型和運算可轉換為有效的 AI 引擎內嵌原語。

- 提供的可參數化數據類型可實現泛型編程

- 以統一的方式為不同的數據類型實現最常見的運算

- 透明地將高級原語轉換為優化的 AI 引擎內嵌原語

- 提高 AI 引擎架構間的可移植性

AI 引擎 API 將是 AI 引擎內核編程的主要方法

高層次優化

AI 引擎編譯器優化選項

- --xlopt=0,沒有應用優化。

- --xlopt=1,自動計算堆量,從 LLVM IR 分析生成指導。

- --xlopt=2,自動內聯、為展開的環路剝離環路並進行編譯指示插入。

引入 --xlopt=2,以提高性能,默認情況下仍是 --xlopt=1

- 自動內聯

- 如果可行,即使函數沒有聲明為 __inline 或內聯,也會自動內聯函數

- 自動編譯指示插入

- 自動將編譯指示插入到內核代碼中。 (查看下一張幻燈片,了解更多詳情)

語用推斷

必須優化內核

- 減輕用戶添加有效而正確的象棋編譯指示的責任

2021.2 中支持自動推斷五種編譯指示

- 對於性能:

-

用於最內層環路的 Chess_prepare_for_pipelining,以及已知行程計數的外部環路

- Chess_loop_range 用於已知行程計數的環路

- chess_unroll_loop/chess_flatten_loop 用於已知行程計數的最內層環路

- 對於正確性:

- 當行程計數不是展開因子的倍數時,Chess_unroll_loop_preamble

更新了圖形編程模型 PLIO 和 GMIO

模型變化包括:

- “simulation::platform”用法的變化

- 與圖中的 PLIO/GMIO 對象交互,位置可確定輸入輸出。

- 圖中全局 PLIO/GMIO 對象的變化。

- 圍繞圖形連接<>語句的變化。

ADF 圖中的 PLIO/GMIO

當前

- 在全局範圍內寫入 PLIO、GMIO、simulation::platform 和連接

GMIO gm0(“GMIO_In0”, 64, 1);

GMIO gm1(“GMIO_In1”, 64, 1);

…

GMIO gm7(“GMIO_In7”, 64, 1);

PLIO pl0(“PLIO_Out0”, plio_32_bits, “data/output0.txt”, 250.0);

PLIO pl1(“PLIO_Out1”, plio_32_bits, “data/output1.txt”, 250.0);

…

PLIO pl7(“PLIO_Out7”, plio_32_bits, “data/output7.txt”, 250.0);

simulation::platform<8,8> plat(&gm0, &gm1,…, &gm7, &pl0, &pl1,…, &pl7,);

subgraph g;

connect<> net0(plat.src[0], g.in[0]);

connect<> net1(plat.src[1], g.in[1]);

…

connect<> net7(plat.src[7], g.in[7]);

connect<> net8(g.out[0], plat.sink[0]);

connect<> net9(g.out[1], plat.sink[1]);

…

connect<> net15(g.out[7], plat.sink[7]);

其它方法

- 創建頂層圖形並在其中移動 PLIO、GMIO 和連接

- 允許針對環路內部管理連接

類型頂層圖

{

input_gmio gm[8];

output_plio pl[8];

subgraph sg;

topgraph()

{

for (i=0; i<8; i++)

{

gm[i] = input_gmio::create(“GMIO_In”+std::to_string(i), 64, 1);

pl[i] = output_plio::create(“PLIO_Out”+std::to_string(i), plio_32_bits, “data/output”+std::to_string(i)+”.txt”, 250.0);

connect<>(gm[i].out[0], sg.in[i]);

connect<>(sg.out[i], pl[i].in[0]);

}

}

};

topgraph g;

區域組約束改進

能夠在 ADF 圖或約束文件中使用標記,以控製映射器和路由器

- -contain_routing — 當指定的真實值可確保所有路由時,包括 nodeGroup 中包含的節點之間的網,都包含在區域組中。

- -exclusive_routing — 當指定的真實值可確保所有路由時,除了 nodeGroup 的節點之間的網,都可從區域組中排除。

- -exclusive_placement — 當指定的真實值可防止未包含在 nodeGroup 中的所有節點被布置在區域組邊界框中時。

快照

快照是包含與所有內核端口相關的注釋和數據的文本文件

- 數據流、軟件包數據流、級聯數據流

- windows, buffer

- RTP

還包括所有平台端口

- PLIO, GMIO, RTP

允許用戶在不使用調試器和不需要檢測內核代碼的情況下檢查內核端口上的數據流量

死鎖檢測

- 在 x86 仿真中檢測鎖死,無論這種情況是由輸入數據不足引起的,還是由於重新收斂路徑上的 FIFO 深度不平衡引起的,均是如此

- 在 x86 仿真過程中,必須通過指定鎖死停止選項來啟用鎖死停止特性

- 如果仿真因鎖死而停止,則錯誤消息將顯示:您應該使用 -trace --timeout 選項重新運行

內存訪問衝突檢查

與 Valgrind 集成,以便進行內存訪問衝突檢查

- 檢查

- 禁止讀寫

- 讀取未初始化的內存

- 編譯無需特定標記

- 仿真標記可以是兩者中的任何一個

- --valgrind:仿真照常運行而 valgrind 則會顯示一個報告

- --Valgrind-gdb:情況是一樣的,但同時要使用 gdb 調試

追蹤報告

鎖死情況會導致仿真輸出差,難以分析漏洞來源

X86 仿真跟蹤選項允許仿真器為各種時間戳信息提供日誌:

- 內核迭代的開始/結束

- 數據流停止的開始/結束

- 鎖定失速的開始/結束

x86 仿真和 AI 引擎仿真的時間戳不同

用戶控製的猝發推斷

- 對於 Vitis HLS 工具無法滿足自動猝發推斷的使用案例,用戶可以采用新引入的手動猝發優化功能

- 最新類別‘hls::burst_maxi’支持手動控製猝發行為。提供全新 HLS API,與新類別一起使用

- 在 HLS 設計中,用戶需要了解 AXI AMBA 協議和硬件事務處理層麵的建模

時序與 QoR 增強

- 為用戶輸入高層次吞吐量限製提供支持

- 提高了 HLS 時序估算精度。當 HLS 報告時序收斂時,Vivado 的 RTL 綜合也應該預期滿足時序要求

EoU 增強

在 C 語言綜合報告中添加接口適配器報告

- 用戶需要知道接口適配器對其設計的資源影響

- 接口適配器具有可影響設計 QoR 的可變屬性

- 其中一些屬性具有應該向用戶報告的相關用戶控件

- 提供 bind_op 和 bind_storage 報告的文字版本

在綜合報告中添加新章節,以顯示編譯指示列表和編譯指示警告

- 用戶可以輕鬆了解添加的哪些編譯指示有問題。

分析與報告增強

函數調用圖查看器有一些新特性

- 全新鼠標拖動式縮放功能

- 全新概覽特性,不僅可顯示全圖,而且用戶還可放大整體圖形的各部位

- 所有函數及環路都與它們的仿真數據一起顯示

現已在仿真後提供一個新的時間軸跟蹤查看器該查看器可顯示設計的運行時概況,並允許用戶保留在 Vitis HLS GUI 中。

鏈接摘要增強

- 為 AI 引擎、平台和計算單元提供時鍾頻率信息

- 在係統圖和平台圖中提供一個名為時鍾的新表

平台導出增強

- XSA 從 Vivado 導出,不需要原文件位於項目本地

- XSA 從 Vivado 導出,不會改變項目結構

- 對硬件平台項目中使用的 IP 進行打包,而不是對整個 IP 回購進行打包

AI 引擎應用仿真增強

- 為外部測試台集成 AI 仿真提供支持

- 為外部測試台集成 x86 仿真提供支持

- 通過 x86 仿真支持 GDB 調試

- 在 x86 仿真圖中為內核間的數據提供快照支持

- 為 x86sim 的訪問違規檢查提供支持

- 為 x86sim 的鎖死停止提供支持

支持 AI 引擎跟蹤

為 AI 引擎應用提供軟件仿真支持

采用 Verilog / System Verilog 支持外部流量生成器

擴展剖析監控器插入,以監控內存

- 目前,剖析監控器邏輯可以在內核/CU 端口基礎上插入。該特性為用戶提供了直接在內存接口上插入監控器邏輯的選項

- 在內存接口上直接實現的內存帶寬可視化,可以在配置文件報告中反映出來

- 支持 DDR 內存和 PLRAM

- 支持硬件流程

- 要啟用該特性,需要將鏈接項和 xrt 設置為

- memory=all

- data_transfer_trace= coarse|fine or

- opencl_device_counter=true

擴展剖析監控器插入,以監控內存

- 可實現內存接口監控的 vadd 示例

- 包括‘內存 Bank 數據轉移’新表

Vitis Analyzer 增強功能

為非 OpenCL 應用生成的通用配置文件摘要報告

- 為 XRT API 和 HAL API 應用提供相同級別的支持。

- 用戶選擇他們想要創建的報告類型,工具會自動在 Vitis Analyzer 中生成並顯示

將 OpenCL 命令添加到 PL 事件時間軸

- 剖析將增加開銷,XRT 提供在不增加開銷的情況下,在時間軸跟蹤中轉儲 OpenCL 事件的功能。

- Vitis Analyzer 可以處理 XRT 輸出並在時間軸跟蹤視圖中顯示。

- Xocl_debug =true 需要在 xrt.ini 中設置。

在時間軸跟蹤報告中扁平化信號層級

- 在默認情況下,時間軸跟蹤報告以層級方式顯示信號跟蹤

- Vitis Analyzer 提供通過切換“Flatten Signal”符號來扁平化層級的功能

- 為平坦的時間軸跟蹤提供比較波形的支持

Vitis Analyzer — 數據可視化

- 在 AI 引擎設計中顯示 AI 引擎內核的輸入輸出數據

- 幫助調試 AI 引擎設計,顯示輸入輸出數據和時間軸

- 與 AI 仿真器聯合使用

- 支持

- 窗口/數據流/級聯數據類型

- 分組數據流

- 模板化內核

- 數據轉儲實用程序

Vitis Analyzer — AI 引擎失速分析

- Vitis Analyzer 提供可視化功能,幫助用戶識別失速的根源

- 支持

- 性能指標

- 鎖定失速分析

- 數據停止分析

- 級聯失速分析

- 內存失速分析

- 支持流程

- AI 仿真器

- 硬件仿真

Xilinx 運行時庫 (XRT): www.rushcopely.com/xrt

- XRT API

- XRT 本地 API 使用 XRT::ip 為用戶托管的內核控製提供支持

- XRT 實用程序

- xbutil 和 xbmgmt 工具現已成為默認工具

- 要使用原有實用程序,請使用 xbutil --原有實用程序或 xbmgmt --帶原有子命令的原有實用程序

- 新實用程序 xball

- 將 xbutil 或 xbmgmt 命令應用到全部已安裝數據中心卡或過濾部分。 查看 xball — 幫助了解詳情

- 新命令 xbutil configure

- 允許您啟用、禁用或配置 PCIe 主機內存和 PCIe 端對端特性。 查看 XRT 文檔,了解更多詳情

- 所有 XRT 實用程序現在都全局支持 --force 選項,以跳過用戶交互確認

- xbutil 和 xbmgmt 工具現已成為默認工具

- 剖析

-

啟用任何剖析選項時,都會生成一個配置文件摘要報告。

- 所有適用的彙總表及指南都可基於 xrt.ini 文件中啟用的剖析選項生成

- 在設計過程中,監控器添加至內存資源時,會提供用於聚合內存資源信息的新數據傳輸彙總表

- 全新 AIE 剖析度量設置為計算不同 AIE 事件的數量,包括 (1) AIE 中的浮點異常;(2) 平鋪執行計數;以及 (3) 數據流的輸出與獲取

- 嵌入式

- 改進了 zocl 內存管理器,可支持任何 sptag

Vitis XRT 可提供 AI 引擎多進程支持

- C 語言和 C++ API 將定義多個進程的訪問模式,以共享對相同 AI 引擎陣列及圖形的訪問。

- 保護 AI 引擎陣列和圖表免遭不必要的訪問。

- 開啟 AI 引擎陣列和圖形支持三種模式

- 獨占模式(防止任何其它進程訪問)

- 主模式(隻允許其它進程進行非破壞性訪問)

- 共享模式(隻進行非破壞性訪問)

- 考慮何時需要提供多進程支持。例如:

- 防止其他用戶訪問 AI 引擎陣列(獨占訪問)

- 多個用戶分別控製不同的圖形(多應用支持)

- 一個主用戶控製圖形,允許其他用戶探測運行狀態(主用戶訪問和共享訪問)

Vitis XRT 提供 AI 引擎支持狀態

C / C++ API

- C 語言版 API

- 對於 AI 引擎陣列:

- xrtAIEDeviceOpenExclusive(獨占模式)

- xrtAIEDeviceOpen(主要模式)

- xrtAIEDeviceOpenShared(共享模式)

- 對於 AI 引擎圖形:

- xrtGraphOpenExclusive(獨占模式)

- xrtGraphOpen(主要模式)

- xrtGraphOpenShared(共享模式)

- 對於 AI 引擎陣列:

- C++ 版 API

- xrt::aie::設備類型支持構造函數中的訪問模式

enum class access_mode:uint8_t { exclusive = 0;primary = 1, shared = 2 };

- xrt::圖形類型支持構造函數中的訪問模式

enum class access_mode:uint8_t { exclusive = 0;primary = 1, shared = 2 };none = 3 };

- xrt::aie::設備類型支持構造函數中的訪問模式

訪問 Alveo 卡的最新 Vitis 目標平台:

- www.rushcopely.com/alveo 並參閱加速卡的入門部分

- www.rushcopely.com/download 並參閱 Alveo 封裝部分

參閱 UG1120 — Alveo 數據中心加速卡平台用戶指南

AI 引擎 DSP 庫 — 新模塊

- AIE DDS

- AIE Mixer

並行編譯

與 2021.1 相比,縮短了時間(例如,以下數字主要針對 200 MHz TX 鏈):

- 編譯與仿真時間減少了 3 倍

- 編譯時間減少了 7 倍

- 仿真後死區時間從 25s 銳降至大約 0s

約束編輯器增強

- 2021.2 改進的導航

針對固定尺寸的改進

針對可變尺寸模塊的改進

增強的功能協同仿真功能

- 為 AI 引擎輸入導出 Matlab 數據 — xmcVitisWrite

- 將 AI 引擎數據導入 Matlab — xmcVitisRead

- 將 AI 引擎數據導入 Matlab — xxmcVitisRead

其它

- 導入沒有輸入的 AI 引擎或 HLS 內核模塊(來源塊)

- 提供新數據類型支持

- Simulink 本地 int64 和 uint64 適用於 AI 引擎開發而不是 AMD 數據類型 x_sfix64 和 x_ufix64。

- accfloat 和 caccfloat 支持 AI 引擎開發

- 支持 Ubuntu 20.04

- 支持 MATALB 20a、20b、21a(不支持 MATLAB 21b)

- 增加了新示例

- 64 核的雙流 SSR 濾波器示例

- 偽逆 (64x32) — commslib 示例。

- 使用 xmcLibraryPath 命令指向自定義 DSPLib 位置。

- 大量更多增強功能和漏洞修複

Vitis 軟件平台 2021.1 版的亮點:

- 支持 AMD Kria System-on-Module (SOM) KV260 視覺 AI 入門套件。ML(DPU 推斷引擎)+ X(RTL 內核和基於 Vitis HLS 的計算機視覺內核)的完整 Vitis 流程。了解更多 >

- 與 CPU/GPU 相比,在 FPGA 和/或 Versal ACAP 上支持最新 C/C++ Vision、DSP、Graph (Louvain Modularity)、圖像處理 Codec、壓縮(GZIP、Facebook ZSTD、ZLIB whole application acceleration)等眾多性能優化庫。

- Versal ACAP 器件上增強的 Vitis™ Core 開發套件設計流程:AI 引擎設計跟蹤報告的可視化改進、通過 GMIO 進行的 AI 引擎事件跟蹤、增量重新編譯、新增啟動映像向導並支持加密的 AI 引擎源文件

- 最新 Vitis Model Composer 工具可在 MathWorks Simulink® 環境中實現快速設計探索與驗證,從而可實現 AI 引擎和可編程邏輯等模塊的協同仿真、代碼生成以及測試台創建。 了解更多 >

- 全新 Vitis HLS 流程導航 GUI 有助於快速訪問流程相和報告。將綜合、分析及調試視窗融合在通用默認環境中

Vitis 新增功能(類別)

注:Vitis 加速庫現已提供,可以單獨下載。它們可以從 GitHub 中下載,也可以直接從 Vitis IDE 中下載。

- AIE DSP

- DSPLib 作為 Vitis 加速庫的一部分發布在 Github 上

- DSPLib 包含在許多高級信號處理應用中使用的通用可參數化 DSP 功能。所有功能目前都支持具有流接口支持的窗口接口。

FIR 濾波器

功能

命名空間

單速率、非對稱

FIR 濾波器

單速率、對稱

dsplib::fir::sr_sym::fir_sr_sym_graph

插值不對稱

dsplib::fir::interpolate_asym::fir_interpolate_asym_graph

抽取、半帶

dsplib::fir::decimate_hb::fir_decimate_hb_graph

插值、半帶

dsplib::fir::interpolate_hb::fir_interpolate_hb_graph

抽取、不對稱

dsplib::fir::decimate_asym::fir_decimate_asym_graph

插值、分數、不對稱

dsplib::fir::interpolate_fract_asym:: fir_interpolate_fract_asym_graph

抽取、對稱

dsplib::fir::decimate_sym::fir_decimate_sym_graph

FFT/iFFT - DSPLib 包含一種 FFT/iFFT 解決方案。這是一個單通道、單核時間抽取 (DIT),具有可配置點大小、複雜數據類型、級聯長度和 FFT/iFFT 功能的實現。

功能

命名空間

單通道 FFT/iFFT

dsplib::fft::fft_ifft_dit_1ch_graph

矩陣乘法 (GeMM) - DSPLib 包含一個矩陣乘法/GEMM(通用矩陣乘法)解決方案。這支持 2 個矩陣 A 和 B 的矩陣乘法,可配置的輸入數據類型可派生出輸出數據類型。

功能

命名空間

Matrix Mult / GeMM

dsplib::blas::matrix_mult::matrix_mult_graph 小部件實用程序 — 這些小部件不僅支持窗口與數據流之間的轉換(在 DSPLib 函數輸入端)和需要時數據流與窗口之間的轉換(在 DSPLib 函數的輸出端),而且還支持用於在真實數據類型和複雜數據類型之間進行轉換的其它小部件。

功能

命名空間

數據流至窗口/窗口至數據流

dsplib::widget::api_cast::widget_api_cast_graph 真實至複雜/複雜至真實

dsplib:widget::real2complex::widget_real2complex_graph - Vitis Model Composer 支持 DSP 庫功能,可幫助用戶輕鬆將這些功能插入 Matlab/Simulink 環境,以方便執行 AI 引擎 DSP 庫評估和整體 AI 引擎 ADF 圖形開發。

Vitis HPC 庫版本引入了 HLS 原語、預構建內核以及用於 FPGA 上 HPC 應用的軟件 API。這些應用包括:

2D 聲學逆時偏移 (RTM) 時域有限差分 (FDTD) 算法,包括前向內核和後向內核

3D 聲學逆時偏移 (RTM) 時域有限差分 (FDTD) 算法,包括前向內核

多層感知器 (MLP) 組件:激活函數和完全連接的網絡內核

稠密矩陣和稀疏矩陣的預條件共軛梯度 (PCG) 求解器

- Versal AI 引擎首選視覺功能的首次發布:

提供的功能

Filter2D

absdiff

accumulate

accumulate_weighted

addweighted

blobFromImage

colorconversion

convertscaleabs

erode

gaincontrol

gaussian

gaussian

pixelwise_mul

threshold

zero

xfcvDataMovers:實用程序數據轉移,以便輕鬆平鋪高分辨率圖像並將其傳輸至 AI 引擎內核的本地內存。兩種版本

- 使用 PL 內核:以更多 PL 資源為代價,提高吞吐量。

- 使用 GMIO:吞吐量低於 PL 內核版本,但使用 Versal 片上網絡 (NOC),不耗 PL 資源。

- 全新可編程邏輯 (PL) 功能和特性

- ISP 流水線與功能:

- 更新了 2020.2 非 HDR 流水線

- 可改變少數運行時 ISP 參數:紅藍通道的增益參數、AWB 啟用/禁用選項、R、G、B 的伽馬表,以及用於計算最小值和最大值以實現 awb 標準化的 % 像素。

- 伽馬校正和色彩空間轉換 (RGB2YUYV) 是流水線的一部分。

- 最新 2021.1 HDR 流水線:支持 2020.2 流水線 + HDR

- 2 個曝光的 HDR 融合,可使用短曝光幀和長曝光幀之間的數字重疊為傳感器提供支持。

- 支持 4 種拜耳模式:RGGB、BGGR、GRBG 和 GBRB

- HDR 融合 + isp 流水線支持運行時配置,其可返回 RGB 輸出。

- 提取功能:HDR 提取功能是預處理功能,其可將單個數字重疊流作為輸入,返回 2 個輸出曝光幀(SEF、LEF)。

- 2 個曝光的 HDR 融合,可使用短曝光幀和長曝光幀之間的數字重疊為傳感器提供支持。

- 3DLUT:提供輸入輸出映射來控製複雜的顏色運算符,如色相、飽和度和亮度。

- CLAHE:對比度限製自適應直方圖均衡是一種在執行自適應直方圖均衡時限製對比度的方法,不會過度放大近恒定區的對比度。減少了噪聲放大的問題。

- 更新了 2020.2 非 HDR 流水線

- 翻轉:沿水平線和垂直線翻轉圖像。

- 自定義 CCA:自定義版本的連接組件分析算法,用於檢測水果缺陷。 除了計算水果的缺陷部分外,還可計算水果的缺陷像素和水果的總像素

- Canny 更新:Canny 功能現在支持所有圖像的分辨率。

與庫有關的變化

- 所有測試都從使用 OpenCV 3.4.2 升級到 OpenCV 4.4

- 增加了對 Versal Edge 係列 (VCK190) 的支持

- 全新基準測試部分,可為發布的選定流水線/功能提供基準測試輔助組件。

2021.1 版提供了二元語法文本分析:

兩克謂詞 (TGP) 是搜索具有兩個字符的反索引。對於建立了反向索引的數據集,它可以在反向索引的每條記錄中找到匹配的 id。

- 社區檢測:Louvain 模塊化

- 2-Hop 搜索

- 用 L2 內核增加了雙精度稀疏矩陣密集向量乘法 (SpMV) 實現

在 2021.1 版中,GQE 獲得了以下特性搶先體驗支持

64 位連接支持:現在 gqeJoin 內核及其配套 gqePart 內核已擴展至 64 位密鑰及有效負載,可支持更大規模的數據。

支持最初的布隆過濾器:gqeJoin 內核現在提供一種執行布隆過濾器探測的模式。 這可提高某些多節點流程的效率,在這些流程中,一定要在早期階段最大限度減少數據量,這一點非常重要。

這兩個特性現在均可作為 L3 純軟件 API 提供,請查看相應的 L3 測試案例。

- GZIP 多核壓縮:

- 全新 GZIP 多核壓縮流媒體加速器,這是純數據流專用解決方案(自由運行內核),支持 4KB、8KB、16KB 和 32KB 的大量不同模塊大小。

- Facebook ZSTD 壓縮內核:

- 全新 Facebook ZSTD 單核壓縮加速器,模塊大小為 32KB。 多核 ZSTD 壓縮正在進行中(以提高吞吐量)。

- GZIP 低時延解壓縮:

- 新版的 GZIP 解壓,降低了每個模塊的時延,降低了資源(LUT 降低 35%、BRAM 降低 83%)並提高了 FMax。

- 使用 U50 對 ZLIB 整個應用進行加速:

- U50 平台的 L3 GZIP 解決方案,包含 6 個壓縮內核,可滲透整個 PCIe 帶寬。 為它提供高效 GZIP 軟件解決方案,以便為 CPU libz.so庫加速,其可針對最終客戶軟件提供無縫收放 API 級集成,無需重新編譯。

- Versal 平台支持

- 添加 AIE 支持 - 如上

- 2021.1 版本提供的支持:為 BLS 提供的 * RIPEMD160 * 最初支持(不完整)

- 在 2021.1 版本中,將數據轉移器添加至該庫。與基於 C++ 的 API 不同,這一新增組件主要針對那些在基於 HLS 的內核設計方麵缺乏經驗、隻想測試其基於流媒體的設計的設計人員。 數據移動器實際上是一個內核源代碼生成器,可創建一係列通用助手內核來驅動或驗證設計,跟 AIE 器件上的一樣。

- 生產 QoR 指標(Vitis QoR 生成 API)

- 應用內核占用的周期

- 失速周期(從 VCD 文件計算)

- 測量封裝程序中的開銷周期(花在內核之外其它函數上的時間)

- 吞吐量

- 3 個層次的優化 XLOPT=0、1(默認)、2

- xlopt=2 的新功能:

- 環路融合、簡化單個迭代外環路、增強環路剝離啟發式

- 分析 “__restrict” 用法並提供指南

- 增量重新編譯:圖形沒有改變時,隻重新編譯已經修改過的內核

- 分組交換數據 → 多達 32 個分組(限 4 個)

- 全新 DMA FIFO 位置約束(映射器/路由器在不同版本之間的改變不會影響性能)

- 在新的編譯中將映射解決方案用作約束:防止將來的映射變化,其可影響性能

- 將 x86sim 功能支持提升到 aiesim 級別

- 開始在 ADF 圖中淘汰 PL 內核(2021.2 中已完全淘汰)

- GUI 中的全新“流程導航器”有助於快速訪問流程階段和報告。環境“綜合、分析、調試”視窗合並到一個默認的通用環境中

- BIND_OP 和 BIND_STORAGE 指令的的全新綜合報告部分

- 全新的綜合後文本報告將反映 GUI 綜合報告中提供的信息

- IP 導出和 Vivado 實現運行小部件使用各種選項進行重新設計,可將設置和約束文件傳遞給 Vivado

- 全新函數調用圖查看器可查看函數和環路,其可使用可選熱圖高亮顯示,以檢查 II、時延或 DSP/BRAM 利用熱點

- Versal 時序校準以及 DSP 模塊本地浮點運算的全新控製(config_op 的 -precision 選項)

- Vitis HLS 升級指南(之前的 UG1391)現在是 UG1399 的一個章節

- 用戶指南中新增方法部分(UG1399 和網絡)

- 可替代的可刷新流水線選項已得到改進(自由運行流水線又稱“frp”)

- 在 Vitis 中,頂層端口指針現在可以隻映射至 axis -lite 適配器,而不是全局內存

- aggregate 指令現在提供一個“-compact bit”選項,支持最大封包

- 在支持可選調查的幫助菜單中添加了一個“留下反饋意見”條目

- 修複了“幫助頁”選項卡在某些 Linux 係統上不顯示信息的漏洞

- 在 Vitis 中,重塑 m_ax 接口應該通過 hls::vector 類型完成

- s_axilite 和 m_axi 數據存儲的全新自定義選項可以是“auto”、“uram”、“bram”或“lutram”,您可以在設計中調整 RAM 利用率

- 在 Vitis 中,為內核引入了一種全新連續(又稱“永不停止”)運行模式

- 已重新設置 axi_lite 輔助時鍾選項

- 在 Vivado IP 封裝器

- 中增強了對 RTL 內核封裝的支持

- 支持適當方法和文檔的公開现金网博e百 化特性。

RT 管理內核是默認流程。

支持加密的 AIE 源文件作為輸入

AIE 編譯器可以接受加密的 AIE 源文件,v++ 支持其餘流程。

- 為 Versal 器件添加創建啟動映像向導支持

- 對 AI 引擎編程和調試進行了多項改進

- 能夠開關微型代碼標簽

- 源代碼和微代碼之間的靜態交叉探測

- 微碼全視圖

- 當流水線視窗更新數據時,將最後一台 PC 帶入能夠看見的區域

- 在流水線視圖中調整指令數據

- 在反彙編視圖中添加“單指令模式”操作。

- 能夠為平台項目生成默認的 BIF 文件

- SD 和 eMMC 的程序閃存增加了原始模式支持

- 環境中的幫助消息添加到 AI 引擎開發流程中

- 將 GCC 工具鏈版本升級至 10.2

- 用戶可通過外部進程(如 Python / C++)來仿真 AXI-MM 的主/從設備。這可幫助用戶使用 AXI 主/從設備的快速設計時間來仿真設計,無需在開發 AXI 主控器或 VIP 的過程中投入資源。此外,AXI-MM 進程之間的通信還可幫助仿真兩個 FPGA 之間的芯片對芯片連接。

- 為 VCS 啟用 Versal 模型的編譯。

- 平台開發人員可使用獨立應用在平台上運行硬件仿真,以便在早期階段對平台進行測試。

- 用戶覆蓋範圍分析信息和用戶事件信息聚合在配置文件摘要報告中

Vitis Analyzer 顯示了一個關鍵的時序路徑。

Vitis 分析器將顯示簡化版 Vivado GUI 時序報告,無需打開 Vivado 項目或網表。這允許用戶快速導航至失敗的時序路徑。

Vitis Analyzer 多種策略支持

多種策略運行的結果可以在 Vitis 分析器中查看。

- 最新 xrt.ini 開關用於分析與調試

減少大型應用的內存和加載時間

全新配置文件工具使用更少的資源來處理大型 csv 文件,這可減少加載時間以及崩潰問題的發生。

PL 連續跟蹤卸載改進

使用 DDR 或 HBM 作為內存資源來存儲跟蹤數據

循環緩衝區支持大型數據卸載

跟蹤緩衝區大小和卸載間隔可以在 xrt.ini 中設置

提高了 AIE 設計跟蹤報告的可視化

將顯示所有 AIE 輸入(窗口、數據流和級聯數據流等)

支持所有 IO 數據類型

- 穩定的本地 XRT API,不僅可為 AIE 圖形的控製和執行提供 C++ API,而且還支持軟件仿真與跟蹤。

- XRT 提供全新助手 API,可幫助用戶在 $XILINX_XRT/include/CL/cl2xrt.hpp 中將 OpenCL API 升級至 XRT 原生 API。

- XRT 全新 API xrt::device.get_info() 可提取設備屬性

- 大幅改進的新一代 xbutil 和 xbmgmt 實用程序現在是默認的。

- xbutil 可報告電源狀態

- xbmgmt 不僅可支持運行時 clk 擴展,而且還可設置用戶電源閾值,從而可保護電路板和服務器。

- sysfs、xbmgmt 和 xbutil 可報告 Alveo 電路板的 MAC 地址

- xocl 中的 KDS 調度器已經進行重構,顯著提高了數百個進程(同時在多個設備間執行多個計算單元)的吞吐量。對於原有 shell 而言,您可能會注意到吞吐量下降的百分比很小。 請參閱 AR 以獲得正確的解決方案。

- 通過 debugfs /sys/kernel/debug/xclmgmt/ and /sys/kernel/debug/xocl/ 支持 XRT 驅動程序調試跟蹤

在www.rushcopely.com/alveo上訪問 Alveo 加速卡的最新 Vitis 目標平台。 請參考加速器卡(您希望在該卡上部署應用)的入門部分。

請查看 { UG1120 - Alveo 數據中心加速卡平台用戶指南,了解更多詳情,並隨時了解最新 Vitis 目標平台發布的最新信息。

全新平台

- Alveo U200 Gen3x16 XDMA 1RP

- 名稱:xilinx_u200_gen3x16_xdma_1_202110_1

- 特性:從橋接器、P2P、GT 內核、DDR 自動刷新

- Alveo U50 Gen3x16 noDMA 1RP

- 名稱:xilinx_u50_gen3x16_nodma_1_202110_1

- 特性:從橋接器、P2P、GT 內核、時鍾節流

- VCK190 基礎平台支持 DDR 和 LPDDR 上的 ECC;約束變得很簡潔。

- MPSoC 基礎平台將 CMA 量增加到了 1536M。所有 Vitis-AI 模型都可按這個 CMA 量運行。

- 簡化了嵌入式平台創建流程:設備樹生成器可自動生成 ZOCL 節點;XSCT 可生成 BIF 文件。減少了基礎平台源文件。

- 支持 Kubernetes(K8s) 集群:Xilinx FPGA 資源管理器 (XRM) 現在可以與 Kubernetes 一起使用,不僅能在連接至服務器的多個 Alveo 加速卡之間運行和管理計算單元 (CU),而且還能將應用擴展到帶 Alveo 卡的多個服務器上。

- 全麵的約束編輯器可幫助用戶在 Vitis Model Composer 中為 AI 引擎內核指定任何約束。 生成的 ADF 圖將包含這些約束。

- 將 AI 引擎的 FFT 和 IFFT 模塊添加至庫瀏覽器。

- 用戶現在可以使用庫瀏覽器訪問大量 AI 引擎 FIR 模塊變體。

- 能夠使用 FIR 濾波器的輸入端口指定濾波器係數。

- 新增兩個全新的實用程序模塊:“RTP 源”和“可變大小”。

- 增強的 AIE 內核導入塊現在也支持導入模板化的 AI 引擎功能。

- 能夠在 Hub 模塊中為 AI 引擎設計指定 AMD 平台。

- 用戶可通過 Hub 模塊,在運行 AIE 仿真後隨時重啟 Vitis 分析器。

- 用戶現在可以使用 Simulink 數據檢查器繪製周期近似輸出,並查看每個輸出的估計吞吐量。

- 增強了僅使用圖形報頭文件將圖形作為模塊導入的可用性。

- 使用取消按鈕修改進度條

- 當 MATLAB 工作目錄和模型目錄不同時,改進了導入 AI 引擎內核或仿真設計時的可用性。

- 全新 TX Chain 200MHz 示例。

- 全新 2d FFT 示例展示了帶有 HLS、HDL 和 AI 引擎模塊的設計。

- 針對 SSR FIR(改進超過 10 倍)和 SSR FFT 提高了仿真速度。

- 針對 RAM 等內存模塊和 FIFO 提高了仿真速度

- 在黑盒導入流程中使用 VHDL 2008 更新了 Questa 仿真器

- Vitis Model Composer 現在可為 DSP 提供 AMD 係統生成器功能性。一直將 AMD 係統生成器用於 DSP 的用戶可繼續使用 Vitis Model Composer 進行開發。

- MATLAB 支持 - R2020a、R2020b & R2021a

Vitis 軟件平台 2020.2 版的亮點:

- Vitis 2020.2 首次為 Versal ACAP 平台上的應用提供加速和嵌入式軟件開發支持

- Vitis Core 開發套件首次引入 Vitis AI Engine( AI 引擎)編譯器,以編譯用於 Versal AI 引擎的 C / C ++ 應用。AI 引擎是 Versal AI Core 係列的一部分,是計算密集型應用的向量處理器

- 對於加速內核編譯 (Vitis) 和 C/C++ 至 RTL IP 創建流程 (Vivado),默認使用 Vitis HLS。

- 提供 600 多個 FPGA 加速功能,遍布 13 大類性能優化庫。2020.2 版引入全新 Vitis 高性能計算 (HPC) 庫用於加速高性能計算類應用。多項增強或補充功能強化數據分析、圖形庫、線性代數 (BLAS) 庫、稀疏矩陣庫 (Sparse)、安全庫以及數據庫

- 為評估多種實現策略提供支持,充分滿足最終 FPGA 二進製的生成,進一步簡化 Vitis 應用中 RTL 內核的集成

- 針對 Vitis Core 工具,增強了 Git 版本控製、集成式主機內核 profiling 等功能。 了解更多詳情 >

- MATLAB® 和 Simulink® 插件:這是 AMD Model Composer 和 System Generator for DSP 的統一。AI 引擎是一個為 MATLAB 和 Simulink 提供的插件中的新域。

了解更多 >

Vitis 新增功能(類別)

注:Vitis 加速庫現已提供,可以單獨下載。它們可以從 GitHub 中下載,也可以直接從 Vitis IDE 中下載。

- 麵向 HPC 工作負載的 FPGA 加速庫。最初版本側重於地震成像和地球物理仿真使用案例

- 逆時偏移 (RTM) 是一種重要的地震成像技術,可精確表征地下情況。

- 高精度多層感知器 (MLP) — 利用地震反映數據重建地下特性(地震反演)

- 針對單精度浮點數據類型 (FP32) 進行優化,該數據類型是高性能計算應用的重要需求

- 該庫的第一個版本提供:

- L1 模板原語、L1 MLP 激活功能(包括 Sigmoid、Relu 和 Prelu)

- L2 2D RTM 前向內核、2D RTM 後向內核和 3D RTM 前向內核

- L3 支持鏡頭平行的 2D RTM API

全新功能與特性

- 2020.2 ISP 流水線示例設計支持的像素深度達 16 位

- 局部色調映射

- 自動曝光調整

- 量化與混色

- Color Correction Matrix

- 黑度校正

- 鏡頭陰影校正

- 強力特征匹配

- 模式濾波器

- blobFromImage

- 拉普拉斯檢測算子

- 距離轉換

庫基礎架構與其它增強功能

- 所有庫函數都支持 Alveo U50 平台

- 為邊緣和數據中心平台提供的 GUI 支持

- 顏色轉換:支持 RGBX 或第四通道支持

- 數據轉換器中的行步支持

- 刪除 xf_axi_sdata.hpp 文件。Axiconverter 函數現在使用 HLS ap_axi_sdata.h 文件代替。

在全新 AMD 應用商店中推出隨時可用於評估的應用

使用 Vitis 視覺庫開發的 FPGA 加速應用現已在全新的AMD 應用商店中推出,作為容器,可用於在 Nimbix 雲端或本地的 Alveo 加速卡上輕鬆評估和部署

- 使用 Vitis AI 庫中的 ML 推斷引擎和 Vitis 視覺預處理功能進行圖像分類

- 圖像傳感器處理 (ISP) 管道

- Stereo Block Matching

- 文本處理 API。包括兩個主要的 API — 正則表達式匹配和地理 IP 查找。前一個 API 可用於從非結構化數據(如日誌)中提取內容,而後者則通常用於處理 Web 日誌,以通過 IP 地址標注地理信息。該庫提供了一個演示工具,其可將 Apache HTTP 服務器的日誌批量轉換為 JSON 文件。

- 用於內存數據提取的 DataFrame API:DataFrame 廣泛用於數據分析領域的內存數據提取,DataFrame 讀寫 API 應該能夠幫助數據分析內核開發人員更輕鬆地使用 Apache Arrow DataFrame 存儲臨時數據或與開源軟件互動。

- 結構樹的整體方法。可擴展隨機森林,以包括回歸。增加了基於助推方法的梯度助推結構樹,支持分類與回歸。也包含對分類與回歸的 XGBoost 的支持,可利用損失函數的二階導數和正則化。

- 單源最短路徑 API (singleSourceShortestPath): 2020.2 版現在不僅支持 Alveo U50 平台,而且還可為最短路徑信息提供一個新的輸出‘pred32’。

- 頁麵排名 API: 2020.2 版現在支持 Alveo U50 平台,包括兩個名為“pageRankTop”的 API — 一個用於利用單個內存通道,而另一個則用於利用多存儲內存。

- 相似度 API: 3 個全新的 API 覆蓋不同的應用:‘denseSimilarityKernel’針對密集圖應用,‘sparseSimilarityKernel’針對稀疏圖應用,而‘generalSimilarityKernel’則針對兩種支持單核的應用。

- 以下 API 現在支持 Alveo U50 平台:

- 寬度優先搜索 bfs API (bfs)

- 程度計算 API (calcuDegree)

- 互聯組件 API (connectedComponents)

- 將格式從 CSC 轉換至 CSR API (convertCsrCsc)

- 標簽傳播 API (labelPropagation)

- 高可靠互聯組件 API (stronglyConnectedComponents)

- 三角形計數 API (triangleCount)

- 最新 L2 GEMM 內核

- 對於 FP32 數據類型,L3 GEMM 性能從 280 GFLOPS 提高到 340 GFLOPS

- 引入了在 Alveo U280 加速卡上利用 16 個 HBM 通道支持的 FP32 L2 CSCMV 內核(用於 CSC 壓縮稀疏列格式矩陣的稀疏矩陣向量乘法)。

- 2020.2 版不僅可為通用查詢引擎 (GQE) 內核設計帶來非常重要的增強功能與更新,而且還可為 JOIN 和 GROUP-BY AGGREGATE 帶來全新的 3 級 API。

- 作為輸入緩衝區的列:GQE 內核將每個列作為輸入緩衝區,簡化了主機代碼的數據準備。此外,與大量連續內存分配相比,在主機端分配多個緩衝區將減少內存不足的問題,特別是在服務器負載沉重的情況下。

- 用於生成配置位的命令類:L2 層現在提供生成 GQE 內核配置位的命令類。開發人員不再需要深入位圖表來了解在 GQE 流水線中啟用或禁用某個功能時應該切換的位。因此,主機代碼可能會更持久、更不容易出錯。

- 最新 3 級 API:為 JOIN 和 GROUP-BY AGGREGATE 構建最新實驗性 L3 API,以增加 GQE 能夠處理的問題。它們可以基於散列將各種表分解為多個部分,並以良好調度的方式多次調用 GQE 內核。執行策略與執行是分開的,因此數據庫專家可以根據表格統計數據微調執行,不會幹擾 OpenCL 執行部分。

- 使用 Alveo U50 加速 LIBZ 庫

- 無縫加速 libz 標準 API:deflate、compress2 和 uncompress

- 隨時可用的 libz.so 庫,可加速所有主機代碼,無需任何代碼修改

- xzlib 獨立可執行文件適用於 gzip/zlib 壓縮和解壓縮

- ZSTD 解壓縮:提供最新實現的 Facebook ZSTD 算法

- Snappy 雙核心內核:最新實現的穀歌 Snappy 雙核心內核解壓縮算法可為單個文件解壓縮實現吞吐量的 2 倍提升。

- GZIP 壓縮內核:提供全新 GZIP 四核壓縮內核(內建、LZ77、TreeGen、Huffman 編碼器)實現方案。整體資源減少 20% 以上,DDR 帶寬需求減少 50%。

- GZIP 壓縮流媒體內核:提供完全符合標準的 GZIP(包括頁眉和頁腳)實現方案,流媒體免費運行內核。

- Alveo U50 上的 GZIP/ZLIB L3 應用:作為 L3 API 提供的 GZIP/ZLIB 應用,針對 Alveo U50 (HBM) 和 Alveo U250 卡進行了優化。一個 FPGA 二進製文件 (xclbin) 支持 zlib 和 gzip 壓縮及解壓縮格式

- 支持 Alveo U50:所移植的庫函數(LZ4、Snappy、GZIP、ZLIB)支持 Alveo U50 平台。

- 低時延 GZIP/ZLIB 解壓縮:對於 4KB/8KB/16KB 模塊大小而言,初始解壓縮時延從 5K 減少到 2.5K

- API 被修改為完全支持 Vitis HLS 編譯器

- 新簽名生成與驗證算法:DSA、ECC、ECDSA (secp256k1) 和 EdDSA (ed25519)

- 最新校驗與算法:Adler32 和 CRC32。

- 可驗證延遲函數 (VDF) 的評估與驗證:Pietrzak 的 VDF 和 Wesolowski 的 VDF。

- 由 CAS 組成的商業密碼:SM2、SM3 和 SM4。

- 流媒體密碼:XChacha20。

- 對 RSA、GMAC、AES-GCM 和 SHA3 進行優化,以提高其性能和資源利用率。

- 參數解析器(測試版):解析從命令行傳遞的選項與標誌,並提供自動幫助信息生成,使開發人員能夠創建測試案例與用戶應用的統一體驗。

- FIFO 多路複用器:該模塊封裝了一個 FIFO(通過內核代碼中的 hls::stream 實現),以便能夠通過相同的硬件資源傳遞不同類型的數據。數據過寬時,它將自動使用多個周期進行傳輸。該模塊有望使數據流代碼更加緊湊、可讀。

ADF:自適應數據流程

- 編譯器:

- PLIO 或 GMIO 上的事件跟蹤

- 硬件上也支持事件跟蹤

- 熱圖生成:所有 AI 引擎的使用率 %

- 支持 PL 內核和 PLIO 的不同 PL 頻率

- 用於 AI 引擎的 Vitis IDE

- 管道視圖

- 向量寄存器視圖

- 內存視圖東、西北、南

- 外部存儲器

- Vitis HLS 在 Vivado 中可取代 Vivado HLS(在 v2020.1 中,它已經是 Vitis 和 C 語言內核編譯的默認設置)

- 為高級功能端口新增陣列重塑和分區編譯指示

- 該工具現在與 Vitis 和 Vivado 一起安裝在其自己的目錄 ./Vitis_HLS/2020.2 下

- HLS 設計偏移信息已經在 UG1391 中更新

- Vitis HLS 用戶指南是 UG1399,所有內容也在 HTML 中提供

- 在 GitHub 上更新了 設計示例,它們也可以從 Vitis HLS GUI(從“Git 資源庫”子窗口)自動加載,以便能夠直接訪問

- 支持 SIMD 編程

- 通過 bind_storage pragma(僅限 Vivado 流程)支持片上模塊 RAM ECC 標誌,以便監控 RAM 模塊生成的錯誤糾正邏輯

- GUI 簡化了工具欄圖標布局,為界麵和 AXI4 (包括猝發)新增了報告部分

- 非默認選項可以在“解決方案設置”→“一般”→“隻顯示非默認值”間續標記中進行篩選,以便快速查看

- 用戶可以使用 -p 選項在直接從 Tcl 開始的 GUI 中創建並打開一個項目,並將 Tcl 文件按照參數形式傳遞:vitis_hls -p .tcl

- 通過 GUI 對 FIFO 的量進行交互式深度調整

- 現在在 GUI 中可以看到對 AXI 接口的約束性隨機測試

Versal 的專有特性

- Vitis HLS 現在可為 DSP58 模塊的浮點(加法器或乘法器)推斷專用單時鍾周期積累,實現高效的高吞吐量積累

- 針對 Versal 生產目標器件更新的時序庫

- 改進的 RTL 內核整合:增強了在 Vitis 應用中按照內核形式封裝整合 RTL IP 的功能,包括對用戶管理的 RTL 內核的支持(不受 XRT API 控製)以及對 Vivado 中的 IP 打包器的改進,從而支持該流程。

- 時序收斂的多個實現策略:Vitis 編譯器和鏈接器 (v++) 現在支持在硬件構建過程中同時啟動和運行多個 Vivado 實現策略。這不僅可幫助用戶探索和評估所有結果,而且還可幫助他們為最終 FPGA 二進製文件 (xclbin) 的創建選擇最佳策略。

Versal 的專有特性

- 在 2020.2 中,隻要硬件設計不變,aiecompiler 隻有在 AIE 程序修改後才會重新編譯軟件並對其進行更新。v++ 鏈接階段不會重新運行,而是直接轉到封包步驟。這允許用戶在硬件修複後輕鬆快速地針對 AIE 程序進行迭代。

- 提供係統級模板,包括 AIE、PL 和 PS 設計文件。

- AIE 工具特性整合在 Vitis IDE 中,如顯示流水線信息、存儲視圖以及並行編譯等。

- Vitis 項目的版本控製:針對 Vitis 項目與 Git 版本控製整合,可實現在多個開發人員和團隊間協作。

- 對項目層級的改進:加速內核和主機應用現在是頂級係統項目下的獨立項目,有助於用戶對主機應用和硬件內核進行分開編譯。

- 對板級支持包 (BSP) 構建時間的改進:對於具有獨立域的平台項目,板級支持包 (BSP) 驅動程序可進行並行編譯,從而可縮短應用的構建時間。

- 主機應用調試的易用性:處理係統寄存器現在可以作為一個文件,從 Vitis GUI 導出,用於調試。

- 配置文件係統項目:頂級係統項目現在可通過 Vitis GUI 為 Vitis 應用加速流程提供針對指定配置文件特性的更多控製。

- 改進了針對使用硬件仿真創建平台的支持:除了將方框圖作為頂層之外,硬件仿真模式現在還支持平台中的 RTL 來源,其可作為頂層模塊或在沒有封裝的情況,作為方框圖中的參考 RTL。您可以像在 Vivado 中那樣添加 RTL 測試平台。它可為部署之前的驗證設計提供更高的靈活性。

- 在仿真過程中保存信號,以供調試:仿真時將信號保存到 Xilinx 仿真器 (XSIM) 波形文件中。運行硬件仿真時,用戶可將 -wcfg-file-path 傳遞給 launch_hw_emu.sh。

- 仿真支持從橋接特性(Alveo 平台):請參閱 Alveo 平台文檔,了解有關從橋接特性的更多詳情。

- 用於仿真 AXI Stream IO 的 Python/C++ API:在仿真 AXI Stream 內核時,使用簡單的 Python 或 C++ API 通過平台上的 IO 端口提供模擬數據流,使您能夠在設計周期的早些時候仿真和調試支持編程流量模式的完整係統

- 為 U250 Alveo 平台提供 Questa 仿真器支持:除了 Xilinx 仿真器 (XSIM) 外,Vitis 中針對 U250 Alveo 平台的硬件仿真現在還支持 Questa。安裝通過 V++ 配置文件或 Vitis IDE 完成。

- HLS 內核死鎖檢測:使用 v++ config param=compiler.deadlockDetection=true 編譯 HLS 內核,可以在硬件仿真期間檢測到 HLS 內核中的死鎖或活鎖代碼。

Versal 的專有特性

- 第三方仿真器支持(Questa、Xcelium、VCS):除了 Xilinx 仿真器 (XSIM) 之外,Vitis 中針對 Versal 嵌入式平台的硬件仿真現在也支持 Linux 上的第三方仿真器,如 Questa 和 Xcelium 等。早期訪問階段支持 VCS。安裝通過 V++ 配置文件或 Vitis IDE 完成。

- Vitis AI Profiler 數據整合:對於使用深度學習處理單元 (DPU) 執行 AI 推斷的應用而言,您可以在 Vitis 分析器中訪問 Vitis AI Profiler 信息,包括 DPU 吞吐量、DDR 讀寫速率以及時間軸跟蹤信息,以便評估端到端應用加速。

- 查看軟件包總結報告:在 Vitis 分析器中查看軟件包總結報告,從性能和優化的角度全麵了解應用狀態。軟件包總結由 v++ 命令在鏈接構建一個軟件包之後創建,所構建的軟件包可以用於軟件或硬件仿真,也可以引導並在硬件設備上運行。

- 整合的主機和內核配置:Vitis 2020.2 增加了為用戶事件提供 API 配置的功能。除了可用於加速內核的固有配置功能之外,您還可以在主機代碼中調用 Xilinx 運行時庫 (XRT) API 來分析設計的任意部分,並針對總體應用性能優化做出決策。

- 其它增強功能:可在 Vitis 分析器內訪問所有報告間的全局搜索,可靈活地保存/恢複自定義用戶查看性能報告的布局,直觀的指導信息分組可在一個地方查看相關信息,對利用率報告的改進,有助於查看每個超級邏輯區域 (SLR) 上的統計信息,以實現更深入的洞察。

Versal 的專有特性

- 配置文件總結報告將有特定的 AIE 設計條目。更多的 AIE 相關數據將在編譯/運行總結報告中顯示,如 AIE 熱圖,它主要顯示運行在硬件上的內核工作/暫停周期。

- 增強了調試可見性:在 Xilinx 仿真器 (XSIM) 事務處理查看器中提供的 AXI-S 事務處理層麵視圖主要用於硬件仿真設計的 System-C 部分,可在事務處理層麵更好的了解設計,充分滿足調試需求。

- 在實時波形查看器中查看 FIFO 狀態:在硬件仿真期間,可在實時波形查看器中查看用戶級 FIFO 的狀態(在內核代碼中表示為hls:streams),從而可查看靜態 FIFO 深度、FIFO 元素和 FIFO 的使用,以確定加速內核的性能瓶頸

Versal 的專有特性

- 事件跟蹤增強:Vitis 2020.2 在 AIE 事件跟蹤特性上有一些增強功能,例如支持通過 XRT 實現的卸載、支持多個跟蹤流流程的增強功能以及監控 PL/AIE 邊界的功能(即使圖中定義了 PL 內核)等。同時,PL/PS/AIE 事件跟蹤被合並到一個通用時間軸中,可更好地監控整個設計。

注:Xilinx 運行時庫 (XRT) 現已提供,可單獨下載。請參考啟動設計信息,查看下載和安裝說明。

- 增強了對 HBM 平台的支持:利用高帶寬內存 (HBM) 平台的優勢,通過 v++ --sp HBM[#:#] 指定 HBM 存儲的內核端口連接 Xilinx 運行時庫 (XRT) API 還可以自動分配 HBM 存儲並幫助主機應用分配一個或多個任意大小的 HBM 區段 緩衝區 (256Mb+)(在 HBM 區段邊界上)。

- 新一代 AMD 開發板管理實用程序(預覽):新一代 AMD 開發板管理實用程序(xbutil、xbmgmt)現在可預覽。它們可為支持它們的 AMD 平台實現從橋接和 DDR 保留特性。注:這一代開發板管理實用程序將在 2021.1 中移至維護模式,新特性隻添加至新一代實用程序。

Versal 的專有特性

- 新增 AIE 支持,以支持 RTP、錯誤處理、全陣列重新配置和圖形 API。

從 Alveo 軟件包下載選項卡訪問 Alveo 加速卡的最新 Vitis 目標平台

請查看 UG1120 — Alveo 數據中心加速卡平台用戶指南,了解更多詳情,並隨時了解最新 Vitis 目標平台版本的最新動態,因為其即將發布

U200/U250 XDMA 平台

- Alveo 平台 U200 XDMA 2RP — 生產

- 特性:ERT、CMC、PLRAM、DRM 功能的平麵布局圖、XDMA、2RP、P2P、M2M、GT 內核、PCIe 從橋接器和 DDR 自刷新

- Alveo 平台 U250 XDMA 2RP - 量產

- 特性:ERT、CMC、PLRAM、DRM 功能的平麵布局圖、XDMA、2RP、P2P、M2M、GT 內核、PCIe 從橋接器和 DDR 自刷新

Shell 升級 DFX — 2RP(2 個重新配置分區)

- 小型靜態區域:基本

- PCIe 功能性

- 帶內 FPGA 部分重配置

- 全新可重配置分區:Shell

- 更新 DMA 和實用程序功能

- 在不重啟服務器的情況下,在平台之間進行動態倒換

- 第二個可重配置分區:用戶邏輯

- 加速器內核功能

AXI Slave Bridge

- 由內核直接訪問主機內存

- DMA 旁路功能,提供 AXI-Slave 512 位接口,用戶可以提供其自己的數據移動設備

數據保留 — DDR4 自刷新

- 在重新配置過程中使用 DDR4 自刷新提供在 FPGA 內存中保留的數據環境

- 避免複製到作為不同 XCLBIN 的臨時存儲的主機 RAM 上

- 最大限度減少大型數據集的移動

注:嵌入式平台的 Vitis 目標平台(包括預先構建的 linux 內核、根文件係統和 sysroot)現已提供,可在 Vitis 嵌入式平台選項卡上單獨下載

- ZYNQ 7000 和 ZYNQ UltraScale+ MPSoC 基礎平台功能保持不變,但重新構建了平台源代碼。為了便於理解,對目錄進行了重命名;多個平台之間的通用源文件組合在一起。重複使用平台源代碼並將其移植到新平台上會更便捷。

- 當從源代碼構建平台時,除了從頭編譯 PetaLinux 之外,如果用戶使用下載的通用軟件組件,則增加了一種全新的端到端編譯方法。在構建平台時,用戶可以指向這些組件並跳過 PetaLinux 編譯。

VCK190 平台有靈活的 DDR + LPDDR 內存子係統,支持加速內核的 63 種中斷。它可以與 Vitis 內核開發套件一起使用,滿足應用加速與嵌入式處理器軟件開發需求,如 Versal AI 引擎程序員指南 (UG1076) 所述。該平台支持各種設計開發,包括:

- AI 引擎圖和內核

- 可編程邏輯內核

- 主機應用,目標是運行在 Versal 器件中的 Arm 處理器上的 Linux 或裸機操作係統。

- 請參考 Vitis / Versal ACAP 平台入門,了解更多信息。

- 支持 Kubernetes(K8s) 集群:Xilinx FPGA 資源管理器 (XRM) 現在可以與 Kubernetes 一起使用,不僅能在連接至服務器的多個 Alveo 加速卡之間運行和管理計算單元 (CU),而且還能將應用擴展到帶 Alveo 卡的多個服務器上。