# Alveo Data Center Accelerator Card Platforms

# User Guide

UG1120 (v1.9) August 26, 2022

Xilinx is creating an environment where employees, customers, and partners feel welcome and included. To that end, we're removing noninclusive language from our products and related collateral. We've launched an internal initiative to remove language that could exclude people or reinforce historical biases, including terms embedded in our software and IPs. You may still find examples of non-inclusive language in our older products as we work to make these changes and align with evolving industry standards. Follow this <u>link</u> for more information.

# AMDA XILINX

# Table of Contents

| Chapter 1: Overview                                                    | 3  |

|------------------------------------------------------------------------|----|

| Chapter 2: DMA Configurations                                          | 5  |

| Chapter 3: Platform Naming and Life Cycle<br>Package Naming Convention |    |

| Chapter 4: Platform Features                                           | 9  |

| Chapter 5: Alveo Platforms                                             | 10 |

| Alveo PCIe Information                                                 |    |

| U50 and U50LV                                                          | 11 |

| U55C                                                                   | 19 |

| U200                                                                   |    |

| U250                                                                   |    |

| U280                                                                   |    |

| Appendix A: Additional Resources and Legal Notices                     |    |

| Xilinx Resources                                                       | 36 |

| Documentation Navigator and Design Hubs                                | 36 |

| References                                                             | 36 |

| Revision History                                                       |    |

| Please Read: Important Legal Notices                                   | 40 |

# AMDA XILINX

## Chapter 1

# Overview

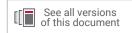

Xilinx Alveo<sup>™</sup> Data Center accelerator cards are PCI Express<sup>®</sup> compliant cards designed to accelerate compute-intensive applications such as machine learning, data analytics, and video processing in a server or workstation. The Vitis<sup>™</sup> core development kit provides verified platforms defining all the required hardware and software interfaces (shown in gray in the following figure), allowing you to design custom acceleration applications (shown in white) that are easily integrated into the Vitis programming model.

**IMPORTANT!** For 2022.1, there are numerous platform changes, and support for some platforms being discontinued. For more information, see Answer Record **33838**.

#### Figure 1: Platform Overview

X23444-012720

On the Xilinx device, a platform consists of a static region and a dynamic region. The static region of the platform provides the basic infrastructure for the card to communicate with the host and hardware support for the kernel. It includes the following features:

• Host Interface (HIF): PCIe endpoint to enable communication with external PCIe host.

- Direct Memory Access (DMA): XDMA IP and AXI Protocol Firewall IP.

- **Clock, Reset, and Isolation (CRI):** Basic clocking and reset for card bring-up and operation. Reset and Dynamic Function eXchange isolation structure are required for isolation during partial bitstream download.

- Card Management Peripheral (CMP): Peripherals responsible for board health and diagnostics, debug, and programming.

- Card Management Controller (CMC): UART/I2C communication to satellite controller (MSP432), QSFP, sensors and manages firmware updates from the host (over PCIe).

- Embedded RunTime Scheduler (ERT): Schedule and monitor compute units during kernel execution.

| Xilinx Device                               |

|---------------------------------------------|

| Dynamic Region                              |

| CMP CMC ERT<br>HIF DMA CRI<br>Static Region |

#### Figure 2: Dynamic and Static Regions In a Platform

X23445-012720

Accelerated kernels go into the dynamic region. The features and resources available for accelerated kernels are described in Chapter 5: Alveo Platforms.

## Chapter 2

# AMD7 XILINX

# **DMA** Configurations

#### **DMA Features**

Xilinx<sup>®</sup> provides a high-performance platform configuration to design custom acceleration applications with XDMA, providing:

- Memory-mapped DMA transfer

- High-bandwidth transfers

- Kernel support for memory-mapped AXI4

#### **Table 1: DMA Customization Features**

| Feature               | XDMA                                                                            |  |

|-----------------------|---------------------------------------------------------------------------------|--|

| Host interface        | Gen3 x16 w/ 512-bit data path                                                   |  |

| Data path             | 512-bit wide memory-mapped AXI4                                                 |  |

| DMA transactions      | Memory-mapped transfers between on card DDR4/HBM/PLRAM memories                 |  |

| Maximum transfer size | 256 MB                                                                          |  |

| DDR4 channels         | U200/U250: 4x DDR4 16 GB (64 GB maximum)<br>U280: 2x DDR4 16 GB (32 GB maximum) |  |

| НВМ                   | U50/U50LV/U280: 1x HBM 8 GB<br>U55C: 1x HBM 16 GB                               |  |

## Chapter 3

# Platform Naming and Life Cycle

## **Package Naming Convention**

Currently, Alveo<sup>™</sup> Data Center accelerator card platforms are delivered through three types of Linux installation packages outlined in the following table.

#### Table 2: Platform Installation Package Types

| Package   | Description                                                                                                            |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------|--|--|

| Partition | Contains a device bitstream that implements part of the deployment platform in the Alveo Data Center accelerator card. |  |  |

| Validate  | Contains code to validate a platform installation and Alveo Data Center accelerator card setup.                        |  |  |

| Firmware  | Contains compiled SC and CMC firmware binary files.                                                                    |  |  |

The following section describes the package naming convention for partition and validate types. They differ slightly from firmware.

#### Partition and Validate Package Naming

The partition and validate installation package names are generated by concatenating the following elements:

<name>\_<version>-<release>-<architecture>[-<OS version>].<extension>

Each element consists of one or more sub-elements and are further described in the following table.

| Element      | Sub-element  | Description                                                                                                                                                                                               | Examples                    |

|--------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Name         | Company      | Vendor name                                                                                                                                                                                               | xilinx                      |

|              | Card         | Card name                                                                                                                                                                                                 | u50<br>u250                 |

|              | Chassis      | Connectivity to the server                                                                                                                                                                                | gen3x16-xdma<br>gen3x4-xdma |

|              | Partition    | Partition name distinguishes the partition type and can be one of base, shell or validate.                                                                                                                | base<br>shell<br>validate   |

| Version      | Iteration(s) | Version of chassis.<br>Dot separated list of one or more integers.<br>Increments when the corresponding chassis<br>interface changes.                                                                     | 2<br>1.1                    |

| Release      | Release      | Integer release number.                                                                                                                                                                                   | 2200000                     |

| Architecture | Architecture | Indicates the architecture the package is built<br>for.<br>noarch – No Architecture<br>all                                                                                                                | noarch<br>all               |

| OS Version   | OS Version   | Only present for Ubuntu packages (as the opener to this block).<br>Indicates supported Ubuntu version for some packages.<br>New packages will support all Ubuntu releases and are denoted as <i>all</i> . | 18.04<br>all                |

| Extension    | Extension    | Package file extension                                                                                                                                                                                    | RPM<br>DEB                  |

| Table 3: Partition a | nd Validate Package | <b>Element Fields</b> |

|----------------------|---------------------|-----------------------|

|----------------------|---------------------|-----------------------|

The following is an example of a deployment installation package.

xilinx-u50-gen3x4-xdma-base\_2-2902115\_all.deb

Once a deployment partition package is installed, you can use XRT commands xbmgmt and xbutil to display the partition installed on the card.

Because the version number indicates compatibility with other partitions, the release number is not displayed. The following is the displayed partition name for the example package.

xilinx\_u50\_gen3x4\_xdma\_base\_2

#### Firmware Package Naming

Firmware (SC and CMC) installation package names are generated by concatenating the following elements:

<name>-<version>-<release>-<architecture>[-<OS version>].<extension>

Each element consists of one or more sub-elements as listed in the following table.

Ē

| Element      | Sub-element  | Description                                                                                                                                                                           | Examples             |

|--------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Name         | Company      | Vendor name                                                                                                                                                                           | xilinx               |

|              | Product      | Firmware product name                                                                                                                                                                 | cmc<br>sc-fw         |

|              | Card         | Card name                                                                                                                                                                             | u250<br>u50          |

| Version      | Version      | Firmware version number. Three integers joined by dots.                                                                                                                               | 1.0.13<br>4.3.9      |

| Release      | Release      | CMC firmware uses an integer. SC firmware uses an alpha-numeric number separated with a dot.                                                                                          | 2500000<br>1.a9fc625 |

| Architecture | Architecture | Indicates the architecture the package is built for.<br>noarch – No Architecture<br>all                                                                                               | noarch<br>all        |

| OS Version   | OS Version   | Only present for Ubuntu packages.<br>Indicates the supported Ubuntu version for some<br>packages.<br>New packages will support all Ubuntu releases and are<br>denoted as <i>all</i> . | 18.04<br>all         |

| Extension    | Extension    | Package file extension                                                                                                                                                                | RPM<br>DEB           |

#### Table 4: Firmware Package Element Fields

The following are examples of <code>cmc</code> and <code>sc-fw</code> package names:

xilinx-cmc-u50\_1.0.40-3398385\_all.deb

xilinx-sc-fw-u50\_5.2.18-1.bf9ba46\_all.deb

## Chapter 4

# AMD7 XILINX

# **Platform Features**

Different platform releases can include one or more of the following features. Features use resources in the static region of the platform.

Chapter 5: Alveo Platforms lists the features supported by each platform.

#### Table 5: Feature Types

| Feature | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2P     | Shorthand for PCIe <sup>®</sup> peer-to-peer communication. Enables direct DMA transfer of data between two Alveo Data Center accelerator cards via the PCIe bus without temporarily buffering data within the host DDR memory. Without this feature the host CPU and memory are used for card-to-card communication. For more information, see XRT documentation on PCIe Peer-to-Peer (P2P). |

| M2M     | Enabling on-card data transfers between card memory resources. Platforms that do not support this feature only transfer memory through host CPU and memory. For more information, see XRT documentation on Memory-to-Memory (M2M) support.                                                                                                                                                    |

| НМ      | Shorthand for PCIe host memory transfers. The AXI subordinate interface allows the card FPGA to directly read and write to host memory, bypassing the DMA. For more information, see XRT documentation on PCIe host memory.                                                                                                                                                                   |

| DFX     | Dynamic function eXchange (DFX) technology allows the card to change functionality on the fly<br><i>without</i> power-cycling the server, which enables some platforms to reconfigure DMA links.<br>Current platforms come in one of two DFX variants.                                                                                                                                        |

|         | • <b>DFX-1RP:</b> The PCIe core and the DMA engine are combined and reside in the static region of the platform. These are also known as one stage platforms.                                                                                                                                                                                                                                 |

|         | • <b>DFX-2RP:</b> The PCIe core resides in the static region of the FPGA (also known as the base) while the DMA engine is dynamically loaded into a new reconfiguration region used by the shell partition. These are also known as two stage platforms.                                                                                                                                      |

|         | For more information, see Alveo Platform Loading Overview in XRT Documentation.                                                                                                                                                                                                                                                                                                               |

| GT      | Shorthand for Gigabit Transceiver (GT) kernel connection. This platform allows for transceiver connection of user-provided MAC within an RTL-kernel for in-line QSFP networking access.                                                                                                                                                                                                       |

## Chapter 5

# AMD7 XILINX

# Alveo Platforms

This section outlines the accelerator cards for data centers and the available target platforms. A target platform provides the firmware for the accelerator card running in a specific configuration. A target platform must be installed with Xilinx Runtime (XRT).

The following table lists the available target platforms per Alveo<sup>™</sup> Data Center accelerator card. For each platform, it details the release name, available features (see Chapter 4: Platform Features), and tool support. There can be more than one target platform for a given card.

**RECOMMENDED:** Only the following target platforms are supported on the latest tools. Any device or platform that is not listed is not supported on the latest tools.

**IMPORTANT!** Xilinx strongly recommends using the latest platform release. For 2022.1, there are numerous platform changes, and support for some platforms being discontinued. For more information, see Answer Record 33838.

| Card Release Name |                                                   |     | Features |     |     | Tool Support |                |        |        |        |

|-------------------|---------------------------------------------------|-----|----------|-----|-----|--------------|----------------|--------|--------|--------|

| Caru              | Caru Release Name                                 |     | M2M      | нм  | DFX | GT           | 2020.2         | 2021.1 | 2021.2 | 2022.1 |

|                   | U50 Gen3x16 XDMA<br>base_5 Platform               | Yes | -        | Yes | 1RP | Yes          | -              | -      | -      | Yes    |

| U50               | U50 Gen3x16 NoDMA<br>base_1 Platform <sup>1</sup> | Yes | -        | Yes | 1RP | Yes          | -              | Yes    | Yes    | Yes    |

|                   | U50 Gen3x4 XDMA<br>base_2 Platform <sup>1</sup>   | -   | -        | -   | 1RP | Yes          | Yes            | Yes    | Yes    | Yes    |

| U50LV             | U50LV Gen3x4 XDMA<br>base_2 Platform <sup>1</sup> | -   | -        | -   | 1RP | Yes          | Yes            | Yes    | Yes    | Yes    |

| U55C              | U55C Gen3x16 XDMA<br>base_3 Platform              | Yes | -        | Yes | 1RP | Yes          | -              | -      | -      | Yes    |

| U200              | U200 Gen3x16 XDMA<br>base_2 Platform              | Yes | Yes      | Yes | 1RP | Yes          | -              | Yes    | Yes    | Yes    |

| U250              | U250 Gen3x16 XDMA 4_1<br>Platform                 | Yes | Yes      | Yes | 2RP | Yes          | -              | -      | -      | Yes    |

| 0230              | U250 Gen3x16 XDMA 2_1<br>Platform                 | Yes | Yes      | Yes | 2RP | Yes          | 2020.2_pu<br>1 | Yes    | Yes    | Yes    |

| U280              | U280 Gen3x16 XDMA<br>base_1 Platform              | Yes | -        | Yes | 1RP | Yes          | _              | _      | _      | Yes    |

#### Table 6: Available Platforms

#### Notes:

1. Does not have a fix for the warm boot issue described in Answer Record.

## **Alveo PCIe Information**

To view PCIe information for Alveo Data Center accelerator cards, see Appendix A in the Alveo Card Out-of-Band Management Specification for Server BMC documentation.

### U50 and U50LV

**TIP:** While U50 and U50LV cards are similar, they operate with different voltages, as shown below. It is necessary to only use the platform associated with the respective card.

- U50 supports  $V_{NORM}$  where  $V_{CCINT} = 0.85V$

- U50LV supports  $V_{LOW}$  where  $V_{CCINT} = 0.72V$

The complete technical specifications are available in the Alveo U50 Data Center Accelerator Cards Data Sheet (DS965).

### AMDZI XILINX

### U50 Gen3x16 XDMA base\_5 Platform

- Platform name: xilinx\_u50\_gen3x16\_xdma\_base\_5

- Supported by: Vitis tools 2022.1

- Platform UUID: 4465409525b4c06aec6d0b479d3febe8

- Interface UUID: 16e2362f82d2feab35529da27134b76d

- Release Date: April 2022

- Created by: 2022.1 tools

- Supported XRT versions: 2022.1, with support planned through 2022

- Satellite controller (SC) FW release: Initial release 5.0.27

Updated to 5.2.18 with the April 2022 update

- Link speed: Gen3 x16

- Target card: A-U50-P00G-PQ-G

For more information, see Alveo U50 Data Center Accelerator Card.

• **Release Notes:** Change log and known issues for the platform and the SC and CMC firmware are available in the *Alveo U50 Master Release Notes Answer Record* 75163.

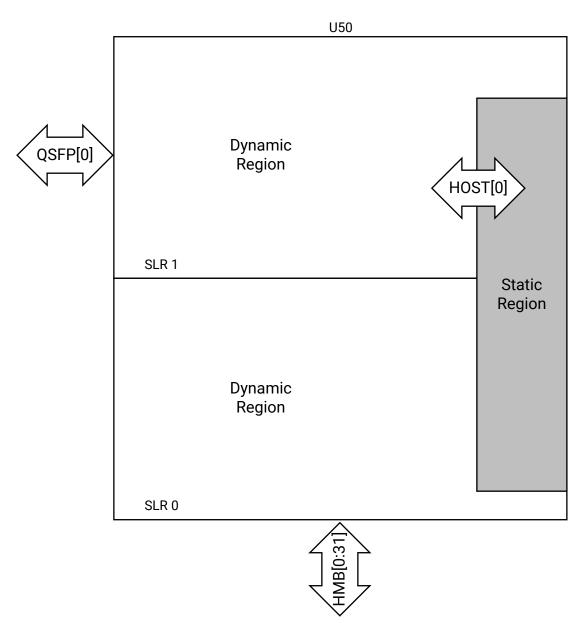

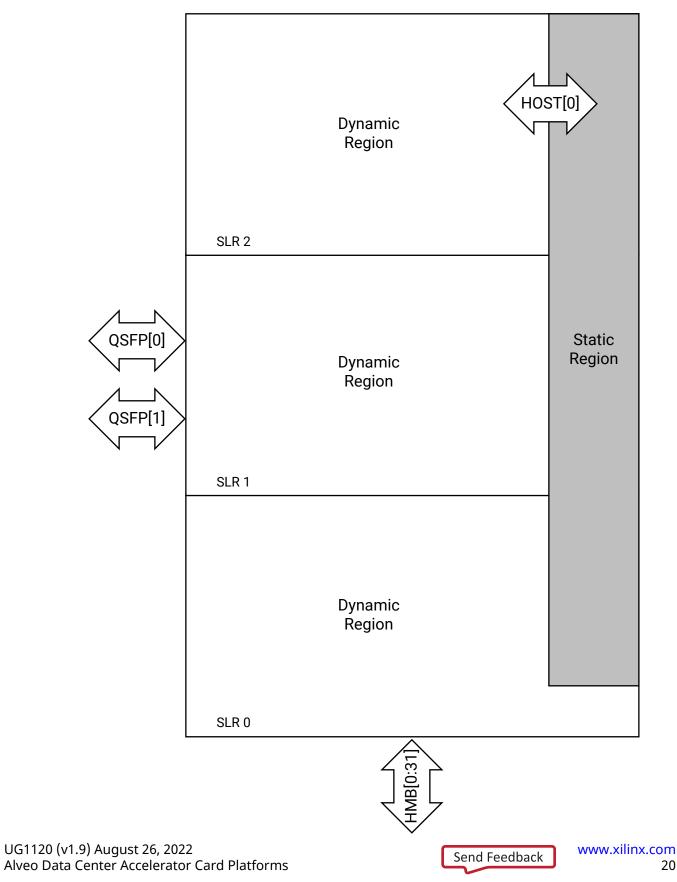

The platform implements the device floorplan shown in the following figure and uses resources across the multiple super logic regions (SLR) of the device. The static and dynamic regions are shown across the SLRs, along with the available HBM memory connections associated with SLRO.

Figure 3: Floorplan

To get the same information for development platforms, after you install the Vitis<sup>™</sup> unified software platform, use the platforminfo command utility. It reports information on interfaces, clocks, valid SLRs, allocated resources, and memory in a structured format. For more information, see platforminfo Utility in the Application Acceleration Development flow of the Vitis Unified Software Platform Documentation (UG1416).

#### Memory

The Alveo U50 Data Center accelerator card has 8 GB of high-bandwidth memory (HBM) accessible through 32 pseudo channels. In addition, it is possible to use the device logic resources for small, fast, on-chip memory accesses as PLRAM. The following table lists the allocation of memory resources per SLR.

Note: For details on assigning kernels to HBM memory channels see Mapping Kernel Ports to Memory.

#### Table 7: Available Memory Resources per SLR

| Resources                                | SLR0                         | SLR1                         |

|------------------------------------------|------------------------------|------------------------------|

| PLRAM memory channels (system port name) | PLRAM[0:1] (128K, block RAM) | PLRAM[2:3] (128K, block RAM) |

| HBM memory channels (system port name)   | HBM [0:31] (8 GB)            | No connections               |

#### **Card Thermal and Electrical Protections**

With the xilinx\_u50\_gen3x16\_xdma\_5\_202210\_1 platform, there are protections to ensure production cards operate within electrical and thermal limits while running acceleration kernels. The following table defines the power and thermal thresholds used to trigger each protection. These protections take three forms and are triggered when the respective thresholds are crossed:

- Clock throttling

- Clock shutdown

- Card shutdown

Clock throttling protection reduces the kernel clock frequencies when any sensor reaches or exceeds their respective clock throttling threshold as listed in the following table. It is a dynamic process that lowers the clock frequencies while power exceeds the associated threshold. By lowering the clock frequencies, clock throttling reduces the required power and subsequently generated heat. Only when all sensor values fall below their respective clock throttling threshold values will the application clocks be restored to full performance.

Clock shutdown shuts down the kernel clocks when any sensor reaches or exceeds their respective clock shutdown threshold given in the following table and will cause an AXI firewall trip that can crash the application on the host. Because the card ends up in an unknown state the XRT driver will issue a command to reset the card. It typically takes a couple minutes until the card is usable again.

Card shutdown removes power to the FPGA when any sensor reaches or exceeds their respective shutdown threshold and will pull the card off the PCIe bus. Power to the SC will remain on. No AXI firewall trip will be issued. A cold reboot of the server is required to recover. The shutdown thresholds listed in the following table are higher than the clock shutdown thresholds and protect the card from damage.

**TIP:** Review the Linux dmesg command output to determine if a protection was activated. An example of the clock shut down messaging is shown:

```

[ 777.531353] clock.m clock.m.23068673: dev ffff97a9e5c3c810,

clock_status_check: Critical temperature or power event, kernel clocks

have been stopped.

```

#### Table 8: Thermal and Electrical Protection Thresholds

| Sensor Description                       | tion Clock Throttling Clock Shutdown<br>Threshold Threshold |                   | Shutdown Threshold |  |  |

|------------------------------------------|-------------------------------------------------------------|-------------------|--------------------|--|--|

| 12V PEX power                            | 62W                                                         | 65W               | N/A                |  |  |

| 3V3 PEX power                            | 9.9W                                                        | 11W               | N/A                |  |  |

| V <sub>CCINT</sub> current               | 56,000 mA                                                   | N/A               | 60,000 mA          |  |  |

| V <sub>CCINT</sub> temperature           | 105°C                                                       | 110°C             | 125°C              |  |  |

| Maximum temperature of device<br>and HBM | 92°C                                                        | 97°C              | 107°C              |  |  |

| QSFP temperature                         | N/A                                                         | 85°C <sup>1</sup> | 90°C <sup>1</sup>  |  |  |

Notes:

1. Refer to QSFP module data sheet.

#### Clocking

The platform provides a 300 MHz default clock to run the accelerator.

#### **Available Resources After Platform Installation**

The following table lists the available resources in the dynamic region of each SLR. It represents the total device resources after subtracting those used by the static region.

#### Table 9: xilinx\_u50\_gen3x16\_xdma\_5\_202210\_1 Platform Resource Availability Per SLR

| Resource       | SLR0 | SLR1 |

|----------------|------|------|

| CLB LUT        | 351K | 353K |

| CLB register   | 703K | 707K |

| Block RAM tile | 552  | 564  |

| UltraRAM       | 272  | 272  |

| DSP            | 2352 | 2568 |

#### **Deployment Platform Installation**

To run applications with this platform, download the deployment installation packages corresponding to your OS listed in the following table. Then, use the installation procedures described in *Alveo U50 Data Center Accelerator Card Installation Guide* (UG1370).

## *Table 10:* xilinx\_u50\_gen3x16\_xdma\_5\_202210\_1 Deployment Platform Installation Download Links

| OS            | Download Link                                                                                                               |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| Ubuntu        | https://www.xilinx.com/bin/public/openDownload?filename=xilinx-u50-gen3x16-<br>xdma_2022.1_2022_0415_2123-all.deb.tar.gz    |  |  |

| RedHat/CentOS | https://www.xilinx.com/bin/public/openDownload?filename=xilinx-u50-gen3x16-<br>xdma_2022.1_2022_0415_2123-noarch.rpm.tar.gz |  |  |

Accelerated applications have software dependencies. Work with your accelerated application provider to determine which XRT version to install.

#### **Development Platform Installation**

For developing applications for use with the Alveo Data Center accelerator cards you must install and use the Vitis software platform. To set up an accelerator card for use in the development environment, follow the installation steps in:

- Vitis Software Platform Installation in the Vitis Unified Software Platform Documentation (UG1416)

- Installing Xilinx Runtime in the Vitis Unified Software Platform Documentation (UG1416)

### U50 Gen3x16 NoDMA base\_1 Platform

- Platform name: xilinx\_u50\_gen3x16\_nodma\_base\_1

- Platform UUID: 4429B71A-27E2-5E65-E708-E17D6FF2DF93

- Interface UUID: B56495F8-1F2A-0E27-FF1F-ABFDC441D260

- Release Date: June 2021

- Created by: 2020.2 tools

- **Supported XRT versions:** 2021.1 through 2022.1, with support planned through 2022

- Satellite controller (SC) FW release: Initial release 5.2.6

Updated to 5.2.15 with the October 2021 update

- Link speed: Gen3 x16

- Target card: A-U50-P00G-PQ-G

For more information, see Alveo U50 Data Center Accelerator Card.

• **Release Notes:** Change log and known issues for the platform and the SC and CMC firmware are available in the *Alveo U50 Master Release Notes Answer Record* 75163.

The xilinx\_u50\_gen3x16\_nodma\_base\_1 is an application-specific platform. It provides direct access to host memory requiring the user logic for data movement. This platform requires pre-allocation of host memory. For more information, refer to XRT Host Memory Documentation.

### U50 Gen3x4 XDMA base\_2 Platform

- Platform name: xilinx\_u50\_gen3x4\_xdma\_base\_2

- Platform UUID: 447C677D-83C3-FFCA-029E-19DE0CC7D7E9

- Interface UUID: 4CDA0BA9-AB64-B59C-535A-DADF2E0B1930

- Release Date: June 2020

- Created by: 2020.1 tools

- Supported XRT versions: 2020.1 through 2022.1, with support planned through 2022

- Satellite controller (SC) FW release: Initial release 5.0.27

Updated to 5.2.15 with the October 2021 update

- Link speed: Gen3 x4

- Target card: A-U50-P00G-PQ-G

For more information, see Alveo U50 Data Center Accelerator Card.

• **Release Notes:** Change log and known issues for the platform and the SC and CMC firmware are available in the *Alveo U50 Master Release Notes Answer Record* 75163.

The xilinx\_u50\_gen3x4\_xdma\_base\_2 is an application specific platform used with machine learning and video transcode application solutions. An application solution combines the platform and application into a single solution. Because application specific platforms are only used with an application, no Vitis development platform is provided.

### U50LV Gen3x4 XDMA base\_2 Platform

- **Platform name:** xilinx\_u50lv\_gen3x4\_xdma\_base\_2

- Platform UUID: CA1BD561-0169-A52C-E463-B3300DF98172

- Interface UUID: 05A5E9D4-E079-740E-76C7-499FEEC81DB3

- Release Date: June 2020

- Created by: 2020.1 tools

- Supported XRT versions: 2020.1 through 2022.1, with support planned through 2022

- Satellite controller (SC) FW release: Initial release 5.0.27

Updated to 5.2.15 with the October 2021 update

- Link speed: Gen3 x4

- Target card: A-U50-P00G-LV-G

For more information, see Alveo U50 Data Center Accelerator Card.

• **Release Notes:** Change log and known issues for the platform and the SC and CMC firmware are available in the *Alveo U50 Master Release Notes Answer Record* 75163.

This is an application specific platform used with machine learning and video transcode application solutions. An application solution combines the platform and application into a single solution. Because application specific platforms are only used with an application, no Vitis development platform is provided.

# U55C

### U55C Gen3x16 XDMA base\_3 Platform

- Platform name: xilinx\_u55c\_gen3x16\_xdma\_base\_3

- Supported by: Vitis tools 2022.1

- Platform UUID: 97088961feaeda9152a21d9dfd63ccef

- Interface UUID: b7ac1abe1e3e1cb686d5a81232452676

- Release Date: April 2022

- Created by: 2022.1 tools

- **Supported XRT version:** 2022.1, with support planned through 2022

- Satellite controller (SC) FW release: Initial release 7.1.14

Updated to 7.1.17 with the April 2022 update

- Link speed: Gen3 x16

- Target card:

A-U55C-P00G-PQ-G

• **Release Notes:** Change log and known issues for the platform and the SC and CMC firmware are available in the *Alveo U50 Master Release Notes Answer Record* 75163.

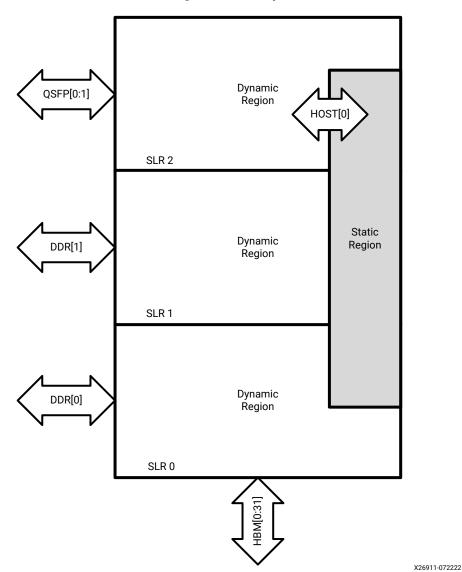

The platform implements the device floor plan shown in the following figure and uses resources across the multiple super logic regions (SLR) of the device. The static and dynamic regions are shown across the SLRs, along with the available HBM memory connections associated with SLRO.

20

### XILINX

#### **Platform Details**

To get the same information for development platforms, if you install the Vitis unified software platform, use the platforminfo command utility. It reports information on interfaces, clocks, valid SLRs, allocated resources, and memory in a structured format. For more information, see platforminfo Utility in the Application Acceleration Development flow of the Vitis Unified Software Platform Documentation (UG1416).

#### Memory

The Alveo U55C card has access to a total of 16 GB high-bandwidth memory (HBM) accessible through 32 pseudo channels. In addition, it is possible to use device logic resources for small, fast, on-chip memory accesses as PLRAM. The following table lists the allocation of memory resources per SLR.

*Note*: For details on assigning kernels to HBM memory channels see Mapping Kernel Ports to Memory.

#### Table 11: Available Memory Resources per SLR

| Resources                                | SLR 0                             | SLR 1                             | SLR 2                             |

|------------------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|

| HBM memory channel (system port name)    | HBM[0:31] (16 GB)                 | No connections                    | No connections                    |

| PLRAM memory channels (system port name) | PLRAM[0:1] (128K per<br>instance) | PLRAM[2:3] (128K per<br>instance) | PLRAM[4:5] (128K per<br>instance) |

| Host memory channels (system port name)  | No connections                    | No connections                    | HOST[0] 16 GB on host             |

#### Clocking

The platform provides a 300 MHz default clock to run the accelerator.

#### Available Resources After Platform Installation

The following table lists the available resources in the dynamic region of each SLR. It represents the total device resources after subtracting those used by the static region.

# Table 12: xilinx\_u55c\_gen3x16\_xdma\_3\_202210\_1 Platform Resource Availability per SLR

| Area           | SLR0   | SLR1   | SLR2   |

|----------------|--------|--------|--------|

| Block RAM tile | 600    | 576    | 600    |

| CLB LUT        | 386880 | 364320 | 395040 |

| CLB Register   | 773760 | 728640 | 790080 |

| DSP            | 2664   | 2784   | 2928   |

| UltraRAM       | 320    | 320    | 320    |

#### **Deployment Platform Installation**

To run applications with this platform, download the deployment installation packages corresponding to your OS listed in the following table. Then, use the installation procedures described in *Alveo U55C Data Center Accelerator Card Installation Guide* (UG1468).

# *Table 13:* xilinx\_u55c\_gen3x16\_xdma\_3\_202210\_1 Deployment Platform Installation Download Links

| OS            | Download Link                                                                                                                |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ubuntu        | https://www.xilinx.com/bin/public/openDownload?filename=xilinx-u55c-gen3x16-<br>xdma_2022.1_2022_0415_2123-all.deb.tar.gz    |  |  |

| Redhat/CentOS | https://www.xilinx.com/bin/public/openDownload?filename=xilinx-u55c-gen3x16-<br>xdma_2022.1_2022_0415_2123-noarch.rpm.tar.gz |  |  |

Accelerated applications have software dependencies. Work with your accelerated application provider to determine which XRT version to install.

#### **Development Platform Installation**

For developing applications for use with the Alveo Data Center accelerator cards you must install and use the Vitis software platform. To set up an accelerator card for use in the development environment, follow the installation steps in:

- Vitis Software Platform Installation in the Vitis Unified Software Platform Documentation (UG1416)

- Installing Xilinx Runtime in the Vitis Unified Software Platform Documentation (UG1416)

### U200

### U200 Gen3x16 XDMA base\_2 Platform

- **Platform name:** xilinx\_u200\_gen3x16\_xdma\_base\_2

- Supported by: Vitis tools 2021.1 through 2022.1, with support planned through 2022

- Platform UUID: 0dd37306b7f657a3bd57680fe9dad3a1

- Interface UUID: 0b095b81fa2be6bd452472b1c1474f18

- Release Date: April 2022

- Created by: 2021.1 tools

- Supported XRT versions: 2021.1 through 2022.1, with support planned through 2022

• Satellite controller (SC) FW release: Initial release 4.6.11

Updated to 4.6.20 with the April 2022 update

- Link speed: PCle Gen3 x16

- Target cards:

- A-U200-A64G-PQ-G

- A-U200-P64G-PQ-G

For more information, see Alveo U200 Data Center Accelerator Card.

• **Release Notes:** Change log and known issues for the platform and the SC and CMC firmware are available in the *Alveo U200 Master Release Notes Answer Record* 75172.

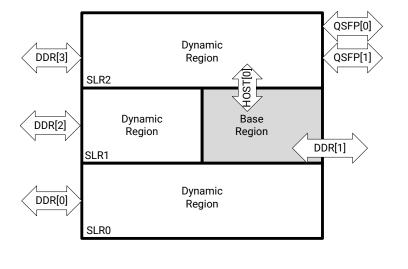

The platform implements the device floorplan shown in the following figure and uses resources across the multiple super logic regions (SLR) of the device. The static and dynamic regions are shown across the FPGA SLRs, along with the available DDR memory connections associated with each SLR.

X25465-062021

To get the same information for development platforms, after you install the Vitis unified software platform, use the platforminfo command utility. It reports information on interfaces, clocks, valid SLRs, allocated resources, and memory in a structured format. For more information, see platforminfo Utility in the Application Acceleration Development flow of the Vitis Unified Software Platform Documentation (UG1416).

#### Memory

The Alveo U200 card has a total of four available DDR memory banks. All but DDR[1] are located in the dynamic region. In addition, it is possible to use the device logic resources for small, fast, on-chip memory accesses as PLRAM. The following table lists the allocation of memory resources per SLR.

**Note:** For details on assigning kernels to DDR memory channels, see Kernel SLR and DDR Memory Assignments in the Application Acceleration Development flow of the Vitis Unified Software Platform Documentation (UG1416).

| Resources                                   | SLR 0                      | SLR 1                                                                         | SLR 2                     |

|---------------------------------------------|----------------------------|-------------------------------------------------------------------------------|---------------------------|

| DDR memory channels<br>(system port name)   | DDR[0] (16 GB DDR4)        | DDR[1] (16 GB DDR4, static<br>region)<br>DDR[2] (16 GB DDR4,<br>dynamic area) | DDR[3] (16 GB DDR4)       |

| PLRAM memory channels<br>(system port name) | PLRAM[0] (128K, Block RAM) | PLRAM[1] (128K Block RAM)                                                     | PLRAM[2] (128K Block RAM) |

| Host memory channels<br>(system port name)  | No connections             | No connections                                                                | HOST[0] 16 GB on host     |

#### Clocking

The platform provides a 300 MHz default clock to run the accelerator.

#### Available Resources After Platform Installation

The following table lists the available resources in the dynamic region of each SLR. It represents the total device resources after subtracting those used by the static region.

# Table 15: xilinx\_u200\_gen3x16\_xdma\_base\_2\_202020\_1 Platform Resource Availability Per SLR

| Resource       | SLR 0 | SLR 1 | SLR 2 |

|----------------|-------|-------|-------|

| CLB LUT        | 388K  | 205K  | 385K  |

| CLB register   | 776K  | 410K  | 770K  |

| Block RAM tile | 720   | 420   | 720   |

| UltraRAM       | 320   | 160   | 320   |

| DSP            | 2280  | 1320  | 2280  |

#### **Deployment Platform Installation**

To run applications with this platform, download the deployment installation packages corresponding to your OS listed in the following table. Then, use the installation procedures described in *Getting Started with Alveo Data Center Accelerator Cards* (UG1301).

# *Table 16:* xilinx\_u200\_gen3x16\_xdma\_base\_2\_202020\_1 Deployment Platform Installation Download Links

| OS            | Download Link                                                                                                                |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ubuntu        | https://www.xilinx.com/bin/public/openDownload?filename=xilinx-u200-gen3x16-<br>xdma_2022.1_2022_0415_2123-all.deb.tar.gz    |  |  |

| Redhat/CentOS | https://www.xilinx.com/bin/public/openDownload?filename=xilinx-u200-gen3x16-<br>xdma_2022.1_2022_0415_2123-noarch.rpm.tar.gz |  |  |

Accelerated applications have software dependencies. Work with your accelerated application provider to determine which XRT version to install.

#### **Development Platform Installation**

For developing applications for use with the Alveo Data Center accelerator cards you must install and use the Vitis software platform. To set up an accelerator card for use in the development environment, follow the installation steps in:

- Vitis Software Platform Installation in the Vitis Unified Software Platform Documentation (UG1416)

- Installing Xilinx Runtime in the Vitis Unified Software Platform Documentation (UG1416)

### U250

### U250 Gen3x16 XDMA 4\_1 Platform

- **Platform name:** xilinx\_u250\_gen3x16\_xdma\_4\_1

- Supported by: Vitis tools 2022.1 with support planned through 2022

- Logic UUID: F8DAC62E-49D9-B0AA-E9FC-6F260D9D0DFB

- Interface UUID: 807A580E-5F50-7D48-484D-26C2217AA787

- Release Date: April 2022

- Created by: 2022.1 tools

- Supported XRT versions: 2022.1

- Satellite controller (SC) FW release: Initial release 4.6.6

Updated to 4.6.20 with the April 2022 update

• Link speed: Gen3 x16

- Target cards:

- A-U250-A64G-PQ-G

- A-U250-P64G-PQ-G

For more information, see Alveo U250 Data Center Accelerator Card.

• **Release Notes:** Change log and known issues for the platform and the SC and CMC firmware are available in the *Alveo U250 Master Release Notes Answer Record* **75180**.

#### **Platform Details**

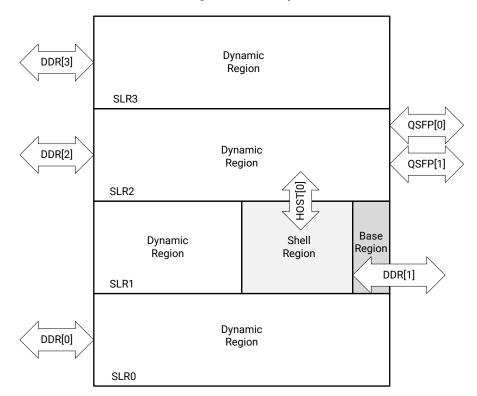

xilinx\_u250\_gen3x16\_xdma\_4\_1 is a DFX-2RP two-stage platform, which consists of both a base and shell partition. The platform implements the device floorplan shown in the following figure and uses resources across the multiple super logic regions (SLR) of the device. The static and dynamic regions are shown across the SLRs, along with the available DDR memory connections associated with each SLR.

Figure 6: Floorplan

X24918-121020

To get the same information for development platforms, if you install the Vitis unified software platform, use the platforminfo command utility. It reports information on interfaces, clocks, valid SLRs, allocated resources, and memory in a structured format. For more information, see platforminfo Utility in the Application Acceleration Development flow of the Vitis Unified Software Platform Documentation (UG1416).

*Note*: Prior to running an application on this DFX-2RP platform, it is necessary to first program the shell partition. For more information, see 75975.

#### Memory

The Alveo U250 card has a total of four available DDR memory banks. In addition, it is possible to use device logic resources for small, fast, on-chip memory accesses as PLRAM. The following table lists the allocation of memory resources per SLR.

**Note:** For details on assigning kernels to DDR memory channels, see Kernel SLR and DDR Memory Assignments in the Application Acceleration Development flow of the Vitis Unified Software Platform Documentation (UG1416).

| Resources                                      | SLR 0                         | SLR 1                        | SLR 2                        | SLR3                         |

|------------------------------------------------|-------------------------------|------------------------------|------------------------------|------------------------------|

| DDR memory channels<br>(system port name)      | DDR[0] (16 GB DDR4)           | DDR[1] (16 GB DDR4)          | DDR[2] (16 GB DDR4)          | DDR[3] (16 GB DDR4)          |

| PLRAM memory<br>channels (system port<br>name) | PLRAM[0] (128K, Block<br>RAM) | PLRAM[1] (128K Block<br>RAM) | PLRAM[2] (128K Block<br>RAM) | PLRAM[3] (128K Block<br>RAM) |

| Host memory<br>channels (system port<br>name)  | No connections                | No connections               | HOST[0] 16 GB on host        | No connections               |

#### Table 17: Available Memory Resources per SLR

#### Clocking

The platform provides a 300 MHz default clock to run the accelerator.

#### Available Resources After Platform Installation

The following table lists the available resources in the dynamic region of each SLR. It represents the total device resources after subtracting those used by the static region.

#### Table 18: xilinx\_u250\_gen3x16\_xdma\_4\_1 Platform Resource Availability per SLR

| Resource       | SLR 0 | SLR 1 | SLR 2 | SLR 3 |

|----------------|-------|-------|-------|-------|

| CLB LUT        | 420K  | 205K  | 407K  | 424K  |

| CLB register   | 840K  | 411K  | 815K  | 849K  |

| Block RAM tile | 668   | 384   | 660   | 672   |

| UltraRAM       | 312   | 128   | 308   | 320   |

| DSP            | 3032  | 1536  | 2994  | 3072  |

#### **Deployment Platform Installation**

To run applications with this platform, download the deployment installation packages corresponding to your OS listed in the following table. Then, use the installation procedures described in *Getting Started with Alveo Data Center Accelerator Cards* (UG1301).

*Note*: Prior to running an application on DFX-2RP platforms, it is necessary to first program the shell partition. For more information, see 75975.

# *Table 19:* xilinx\_u250\_gen3x16\_xdma\_4\_1 Deployment Platform Installation Download Links

| OS            | Download Link                                                                                                                |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ubuntu        | https://www.xilinx.com/bin/public/openDownload?filename=xilinx-u250-gen3x16-<br>xdma_2022.1_2022_0415_2123-all.deb.tar.gz    |  |  |

| RedHat/CentOS | https://www.xilinx.com/bin/public/openDownload?filename=xilinx-u250-gen3x16-<br>xdma_2022.1_2022_0415_2123-noarch.rpm.tar.gz |  |  |

Accelerated applications have software dependencies. Work with your accelerated application provider to determine which XRT version to install.

#### **Development Platform Installation**

For developing applications for use with the Alveo Data Center accelerator cards you must install and use the Vitis software platform. To set up an accelerator card for use in the development environment, follow the installation steps in:

- Vitis Software Platform Installation in the Vitis Unified Software Platform Documentation (UG1416)

- Installing Xilinx Runtime in the Vitis Unified Software Platform Documentation (UG1416)

### U250 Gen3x16 XDMA 2\_1 Platform

This platform is intended to be used with Microsoft Azure. For access, and additional details, please visit the website at Microsoft Azure.

- Platform name: xilinx\_u250\_gen3x16\_xdma\_2\_1

- Supported by: Vitis tools 2020.2

- Logic UUID: C3AD6B03-7144-8CA9-494E-D5B672C7092A

- Interface UUID: 13DB7987-A2D8-1BFF-743A-71ED8DF67C17

- Release Date: April 2021

- Created by: 2020.1 tools

- Supported XRT versions: 202020.2.8.832

- Satellite controller (SC) FW release: Initial release 4.5.0

- Link speed: Gen3 x16

- Target cards:

- A-U250-A64G-PQ-G

- A-U250-P64G-PQ-G

For more information, see Alveo U250 Data Center Accelerator Card.

• **Release Notes:** Change log and known issues for the platform and the SC and CMC firmware are available in the *Alveo U250 Master Release Notes Answer Record* 75180.

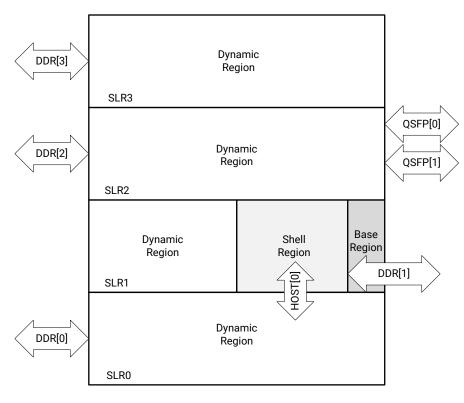

#### **Platform Details**

The platform implements the device floorplan shown in the following figure and uses resources across the multiple super logic regions (SLR) of the device. The static and dynamic regions are shown across the SLRs, along with the available DDR memory connections associated with each SLR.

*Figure 7:* **Floorplan**

X25226-032621

To get the same information for development platforms, if you install the Vitis unified software platform, use the platforminfo command utility. It reports information on interfaces, clocks, valid SLRs, allocated resources, and memory in a structured format. For more information, see platforminfo Utility in the Application Acceleration Development flow of the Vitis Unified Software Platform Documentation (UG1416).

*Note*: Prior to running an application on DFX-2RP platforms, it is necessary to first program the shell partition. For more information, see 75975.

#### Memory

The Alveo U250 card has a total of four available DDR memory banks. In addition, it is possible to use device logic resources for small, fast, on-chip memory accesses as PLRAM. The following table lists the allocation of memory resources per SLR.

**Note:** For details on assigning kernels to DDR memory channels, see Kernel SLR and DDR Memory Assignments in the Application Acceleration Development flow of the Vitis Unified Software Platform Documentation (UG1416).

| Resources                                      | SLR 0                         | SLR 1                         | SLR 2                         | SLR3                          |

|------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

| DDR memory channels<br>(system port name)      | DDR[0] (16 GB DDR4)           | DDR[1] (16 GB DDR4)           | DDR[2] (16 GB DDR4)           | DDR[3] (16 GB DDR4)           |

| PLRAM memory<br>channels (system port<br>name) | PLRAM[0] (128K, Block<br>RAM) | PLRAM[1] (128K, Block<br>RAM) | PLRAM[2] (128K, Block<br>RAM) | PLRAM[3] (128K, Block<br>RAM) |

| Host memory<br>channels (system port<br>name)  | HOST[0] 16 GB on host         | No connections                | No connections                | No connections                |

#### Table 20: Available Memory Resources per SLR

#### Clocking

The platform provides a 300 MHz default clock to run the accelerator.

#### Available Resources After Platform Installation

The following table lists the available resources in the dynamic region of each SLR. It represents the total device resources after subtracting those used by the static region.

#### Table 21: xilinx\_u250\_gen3x16\_xdma\_2\_1 Platform Resource Availability per SLR

| Resource       | SLR 0 | SLR 1 | SLR 2 | SLR 3 |

|----------------|-------|-------|-------|-------|

| CLB LUT        | 419K  | 205K  | 410K  | 424K  |

| CLB register   | 839K  | 410K  | 819K  | 848K  |

| Block RAM tile | 668   | 384   | 664   | 672   |

| UltraRAM       | 312   | 128   | 308   | 320   |

| DSP            | 3032  | 1536  | 3016  | 3072  |

#### **Deployment Platform Installation**

To run applications with this platform, download the deployment installation packages corresponding to your OS listed in the following table. Then, use the installation procedures described in *Getting Started with Alveo Data Center Accelerator Cards* (UG1301).

*Note*: Prior to running an application on DFX-2RP platforms, it is necessary to first program the shell partition. For more information, see 75975.

Accelerated applications have software dependencies. Work with your accelerated application provider to determine which XRT version to install.

#### **Development Platform Installation**

For developing applications for use with the Alveo Data Center accelerator cards you must install and use the Vitis software platform. To set up an accelerator card for use in the development environment, follow the installation steps in:

- Vitis Software Platform Installation in the Vitis Unified Software Platform Documentation (UG1416)

- Installing Xilinx Runtime in the Vitis Unified Software Platform Documentation (UG1416)

### U280

### U280 Gen3x16 XDMA base\_1 Platform

- Platform name: xilinx\_u280\_gen3x16\_xdma\_base\_1

- Supported by: Vitis tools 2022.1.1

- Logic UUID: 283BAB8F-654D-8674-968F-4DA57F7FA5D7

- Interface UUID: FB2B2C5A-19ED-6359-3FEA-95F51FBC8EB9

- Release Date:

- Created by: 2022.1.1 tools

- Supported XRT versions: 2022.1 with support planned through 2023

- Satellite controller (SC) FW release:

Initial release 4.3.27

- Link speed: Gen3 x16

- Target cards:

- A-U280-A32G-DEV-G

- A-U280-P32G-PQ-G

For more information, see Alveo U280 Data Center Accelerator Card.

• **Release Notes:** Change log and known issues for the platform and the SC and CMC firmware are available in the *Alveo U280 Master Release Notes Answer Record* **75183**.

#### **Platform Details**

The platform implements the device floorplan shown in the following figure and uses resources across the multiple super logic regions (SLR) of the device. The static and dynamic regions are shown across the SLRs, along with the available DDR memory connections associated with each SLR.

### AMDA XILINX

*Figure 8:* **Floorplan**

To get the same information for development platforms, if you install the Vitis unified software platform, use the platforminfo command utility. It reports information on interfaces, clocks, valid SLRs, allocated resources, and memory in a structured format. For more information, see platforminfo Utility in the Application Acceleration Development flow of the Vitis Unified Software Platform Documentation (UG1416).

#### Memory

The Alveo U280 card has access to a total of 32 GB DDR memory and 8 GB HBM. The DDR memory banks are accessible through two memory controllers and the HBM is accessible through 32 pseudo channels. In addition, it is possible to use device logic resources for small, fast, on-chip memory accesses as PLRAM. The following table lists the allocation of memory resources per SLR.

**Note:** For details on assigning kernels to DDR memory channels, see Kernel SLR and DDR Memory Assignments in the Application Acceleration Development flow of the Vitis Unified Software Platform Documentation (UG1416).

#### Table 22: Available Memory Resources per SLR

| Resources                                | SLR 0                           | SLR 1                           | SLR 2                           |

|------------------------------------------|---------------------------------|---------------------------------|---------------------------------|

| DDR memory channels (system port name)   | DDR[0] (16 GB DDR4)             | DDR[1] (16 GB DDR4)             | No resources                    |

| HBM memory channels (system port name)   | HBM[0:31] (8 GB)                | No resources                    | No resources                    |

| PLRAM memory channels (system port name) | PLRAM[0:1] (128K,<br>Block RAM) | PLRAM[2:3] (128K,<br>Block RAM) | PLRAM[4:5] (128K,<br>Block RAM) |

#### Clocking

The platform provides a 300 MHz default clock to run the accelerator.

#### Available Resources After Platform Installation

The following table lists the available resources in the dynamic region of each SLR. It represents the total device resources after subtracting those used by the static region.

#### Table 23: xilinx\_u280\_gen3x16\_xdma\_base\_1 Platform Resource Availability per SLR

| Resource     | SLR 0 | SLR 1 | SLR 2 |

|--------------|-------|-------|-------|

| CLB LUT      | 386K  | 364K  | 381K  |

| CLB register | 773K  | 729K  | 763K  |

| BRAM36       | 600   | 576   | 600   |

| URAM         | 320   | 320   | 320   |

| DSP          | 2664  | 2784  | 2856  |

#### **Deployment Platform Installation**

To run applications with this platform, download the deployment installation packages corresponding to your OS listed in the following table. Then, use the installation procedures described in *Getting Started with Alveo Data Center Accelerator Cards* (UG1301).

## *Table 24:* xilinx\_u280\_gen3x16\_xdma\_base\_1 Deployment Platform Installation Download Links

| OS            | Download Link                                                                                                                |

|---------------|------------------------------------------------------------------------------------------------------------------------------|

| Ubuntu        | https://www.xilinx.com/bin/public/openDownload?filename=xilinx-u280-gen3x16-<br>xdma_2022.1_2022_0804_1110-all.deb.tar.gz    |

| Redhat/CentOS | https://www.xilinx.com/bin/public/openDownload?filename=xilinx-u280-gen3x16-<br>xdma_2022.1_2022_0804_1110-noarch.rpm.tar.gz |

Accelerated applications have software dependencies. Work with your accelerated application provider to determine which XRT version to install.

#### **Development Platform Installation**

For developing applications for use with the Alveo Data Center accelerator cards you must install and use the Vitis software platform. To set up an accelerator card for use in the development environment, follow the installation steps in:

- Vitis Software Platform Installation in the Vitis Unified Software Platform Documentation (UG1416)

- Installing Xilinx Runtime in the Vitis Unified Software Platform Documentation (UG1416)

## Appendix A

# Additional Resources and Legal Notices

## **Xilinx Resources**

For support resources such as Answers, Documentation, Downloads, and Forums, see Xilinx Support.

## **Documentation Navigator and Design Hubs**

Xilinx<sup>®</sup> Documentation Navigator (DocNav) provides access to Xilinx documents, videos, and support resources, which you can filter and search to find information. To open DocNav:

- From the Vivado<sup>®</sup> IDE, select Help → Documentation and Tutorials.

- On Windows, select Start → All Programs → Xilinx Design Tools → DocNav.

- At the Linux command prompt, enter docnav.

Xilinx Design Hubs provide links to documentation organized by design tasks and other topics, which you can use to learn key concepts and address frequently asked questions. To access the Design Hubs:

- In DocNav, click the **Design Hubs View** tab.

- On the Xilinx website, see the Design Hubs page.

Note: For more information on DocNav, see the Documentation Navigator page on the Xilinx website.

## References

These documents provide supplemental material useful with this guide:

Send Feedback

#### U50

- 1. Alveo U50 Data Center Accelerator Cards Data Sheet (DS965)

- 2. Alveo U50 Data Center Accelerator Card Installation Guide (UG1370)

- 3. Vitis Unified Software Platform Documentation

#### U55C

- 1. Alveo U55C Data Center Accelerator Cards Data Sheet (DS978)

- 2. Alveo U55C Data Center Accelerator Card Installation Guide (UG1468)

- 3. Vitis Unified Software Platform Documentation

#### U200

- 1. Alveo U200 and U250 Data Center Accelerator Cards Data Sheet (DS962)

- 2. Getting Started with Alveo Data Center Accelerator Cards (UG1301)

- 3. Vitis Unified Software Platform Documentation

#### U250

- 1. Alveo U200 and U250 Data Center Accelerator Cards Data Sheet (DS962)

- 2. Getting Started with Alveo Data Center Accelerator Cards (UG1301)

- 3. Vitis Unified Software Platform Documentation

#### U280

- 1. Alveo U280 Data Center Accelerator Cards Data Sheet (DS963)

- 2. Getting Started with Alveo Data Center Accelerator Cards (UG1301)

- 3. Vitis Unified Software Platform Documentation

## **Revision History**

The following table shows the revision history for this document.

| Section                                                    | Revision Summary                |  |

|------------------------------------------------------------|---------------------------------|--|

| 08/26/2022 Version 1.9                                     |                                 |  |

| Chapter 5: Alveo Platforms Updated for the 2022.1 release. |                                 |  |

| U280 Gen3x16 XDMA base_1 Platform                          | Updated for the 2022.1 release. |  |

| Section                                            | Revision Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 04/29/2022                                         | Version 1.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Chapter 5: Alveo Platforms                         | Updated with supported platforms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Chapter 5: Alveo Platforms                         | <ul> <li>Updated with supported platforms.</li> <li>Added new platforms: <ul> <li>U50 Gen3x16 XDMA base_5 Platform</li> <li>U55C Gen3x16 XDMA base_3 Platform</li> <li>U200 Gen3x16 XDMA base_2 Platform</li> <li>U250 Gen3x16 XDMA 4_1 Platform</li> </ul> </li> <li>Removed deprecated platforms: <ul> <li>U50 Gen3x16 XDMA 201920_3 Platform</li> <li>U55C Gen3x16 XDMA 2_202110_1 Platform</li> <li>U200 XDMA 201830_2 Platform</li> <li>U200 Gen3x16 XDMA 1_202110_1 Platform</li> <li>U250 XDMA 201830 2 Platform</li> </ul> </li> </ul> |  |

|                                                    | <ul> <li>U250 Gen3x16 XDMA 3_1 Platform</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                                    | For more information, see this Answer Record.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Platform Naming Convention Prior to 2020.1         | Removed topic because 2020.1 platforms and earlier have been deprecated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Package Naming Convention 2020.1 Release and Later | Renamed from <i>Platform Naming Convention 2020.1 Release</i><br><i>and Later.</i><br>Ubuntu 16.04 is no longer supported and is removed from<br>OS version examples.                                                                                                                                                                                                                                                                                                                                                                          |  |

| 12/10/2021                                         | Version 1.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Chapter 5: Alveo Platforms                         | <ul> <li>Updated information about available platforms.</li> <li>Updated:</li> <li>U55C Gen3x16 XDMA base_2 Platform</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| All platforms                                      | Where present, added initial release SC firmware version and update SC firmware version.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                                    | Where present, updated URAM to UltraRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 10/29/2021 Version 1.6                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Chapter 5: Alveo Platforms                         | <ul> <li>Updated information about available platforms.</li> <li>Added: <ul> <li>U55C Gen3x16 XDMA base_2 Platform</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 07/30/2021                                         | Version 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Chapter 5: Alveo Platforms                         | <ul> <li>Updated information about available platforms.</li> <li>Added: <ul> <li>U50 Gen3x16 NoDMA base_1 Platform</li> <li>U200 Gen3x16 XDMA base_1 Platform</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                           |  |

| All platforms                                      | Where present, changed <i>Timestamp</i> to <i>Platform UUID</i> and <i>Interface UUID</i> , which better correspond to values in XRT.                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 04/23/2021                                         | Version 1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Chapter 5: Alveo Platforms                         | Updated available platforms. <ul> <li>Added: U250 Gen3x16 XDMA 2_1 Platform</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Section                                   | Revision Summary                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 4: Platform Features              | <ul> <li>Slave-bridge (SB) feature renamed to host memory (HM).</li> <li>Added: Gigabit Transceiver (GT)</li> <li>Updated: Slave-bridge (SB) renamed to host memory (HM).</li> </ul>                                                                                                                                                                                                                                                |

| Chapter 5: Alveo Platforms                | Under <i>Tool Support</i> , removed 2021.2 column.                                                                                                                                                                                                                                                                                                                                                                                  |

| Alveo PCIe Information                    | Replaced content with link to Appendix A in the Alveo Card<br>Out-of-Band Management Specification for Server BMC<br>documentation, which provides the same information.                                                                                                                                                                                                                                                            |

| U250 Gen3x16 XDMA 3_1 Platform            | Added target card: A-U250-P64G-PQ-G                                                                                                                                                                                                                                                                                                                                                                                                 |