軟件開發套件(SDK)

注:自 2019.2 起,SDKSDSoC™ 和 SDAccel™ 開發環境被整合為一個多用途的 Vitis™ 統一軟件平台,用於應用加速和嵌入式軟件開發。SDK 不會有 2019.2 或更高版本。

軟件開發套件 (SDK) 是集成型設計環境,可在任何 AMD 獲獎微處理器上創建嵌入式應用: Zynq™ UltraScale+ MPSoC、Zynq 7000 SoC、和業界領先的 MicroBlaze™ 軟核微處理器。SDK 是首款應用 IDE,可實現真正的同質及異構多處理器設計、調試和性能分析。優勢包括:

- 支持 Zynq UltraScale+ MPSoC、 Zynq 7000 SoC、和 MicroBlaze

- 隨 Vivado 設計套件提供給嵌入式軟件開發人員,也可單獨免費下載獲取。

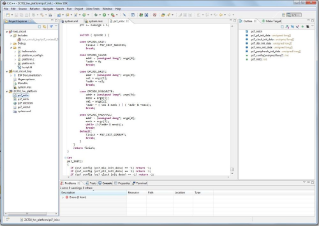

- 基於 Eclipse 4.5.0 和 CDT 8.8.0 (自 2016.3 版起)

- 完整的集成設計環境 (IDE) 可直接用於連接 Vivado 嵌入式硬件設計環境

- 實現完整的軟件設計和調試流程支持,包括全新多處理器和硬件/軟件協調試功能

- 編輯器、編譯器、生成工具、閃存管理和 JTAG 調試集成

- 整套庫與器件驅動

- 作為 RTOS 集成的 FreeRTOS 現已針對所有平台提供

- 軟件命令行工具 (XSCT) 用於腳本

係統調試程序

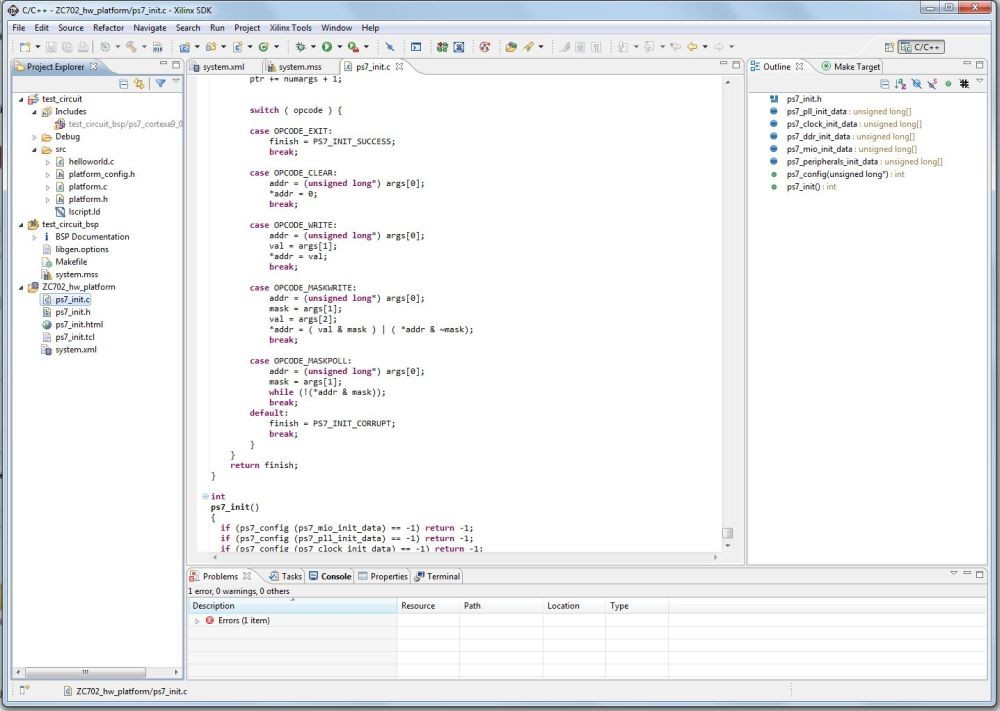

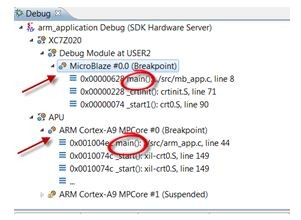

AMD 係統調試器是一款支持 Zynq UltraScale+ MPSoC、Zynq 7000 SoC 和 MicroBlaze 核的集成型調試器。可使用 XSCT 通過命令行獲得,也可在調試應用的 SDK GUI 中獲得。它支持所有常見的調試特性,如設置斷點或觀察點、通過程序執行步進、查看程序變量和堆棧以及查看係統中存儲器的內容等。還可以在同一調試環境中同時調試多處理器係統中不同處理器上的程序。例如在基於 Zynq 或基於 Zynq UltraScale+ 的設計中,係統調試器可通過單個 JTAG 線纜在同一個調試會話中顯示兩個 ARM CPU 和多個 MicroBlaze 軟處理器,從而可在硬件化處理係統和已添加至可編程邏輯中的任何附加處理係統之間實現前所未有的深入觀察。

- 基於開源目標通信框架 (TCF)

- 同質和異構多處理器支持

- 層次分析

- 裸機與 Linux 開發,包括 Linux OS-Aware 調試

- 支持 SMP 和 AMP 設計

- 關聯每個內核的硬件與軟件斷點。

- 支持 NEON™ 庫

除了全功能標準軟件調試工具的所有特性外, 該係統調試工具還可在 PS 的處理器與 PL 的處理器及硬件之間實現交叉觸發。軟件編程工具可通過直觀的 GUI 設置向 PL 上的外部處理器或硬件發出觸發或從這些組件接受觸發的條件。 不僅可采集數據,而且還可在不同的工具中顯示,從而可在調試過程中提供幫助。

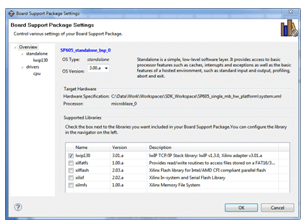

定製設計感知

SDK 了解 Vivado 設計套件中定義的定製嵌入式硬件設計。在該設計基礎上,係統會自動配置一些重要的參數,其中包括存儲器映射、外設寄存設置、工具和庫路徑、編譯器選項、JTAG 和閃存設置、調試器連接以及Linux、裸機板支持包 (BSP)。 該定製的設計感知預配置與自動生成的關鍵係統軟件完美地整合在了一起,您隻需花費少量的學習時間便可快速進行軟件開發了。

驅動程序和庫

SDK 為所有支持的 AMD IP 硬核提供了可用戶定製的驅動程序,並提供了符合 POSIX 規範的內核庫、網絡和文件處理庫。這些庫和驅動程序可以根據功能需要、存儲器要求和硬件功能為定製設計進行縮放。

軟件特性描述

SDK 提供了性能分析工具,可幫助用戶識別因在可編程邏輯中和在處理器上的交互而可能造成的代碼瓶頸。支持分級特性描述,能讓用戶查看是什麼調用了函數、或者什麼調用函數對處理器性能的影響最大。

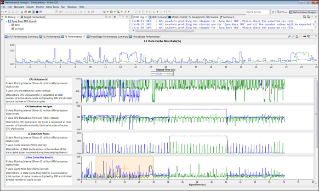

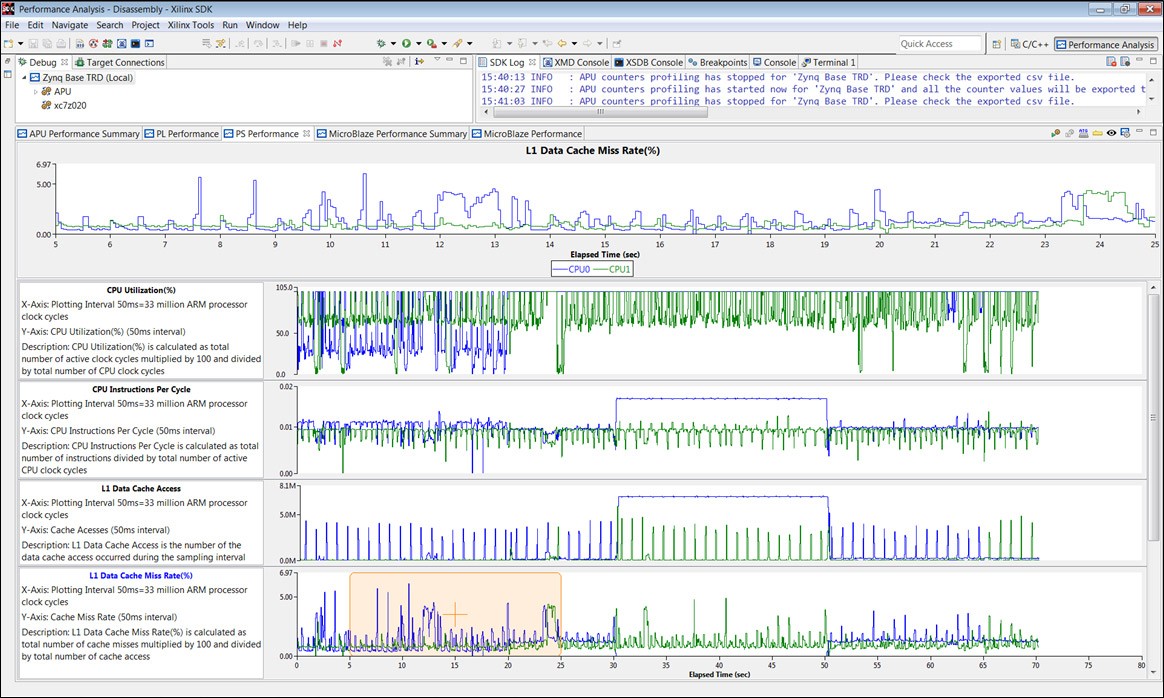

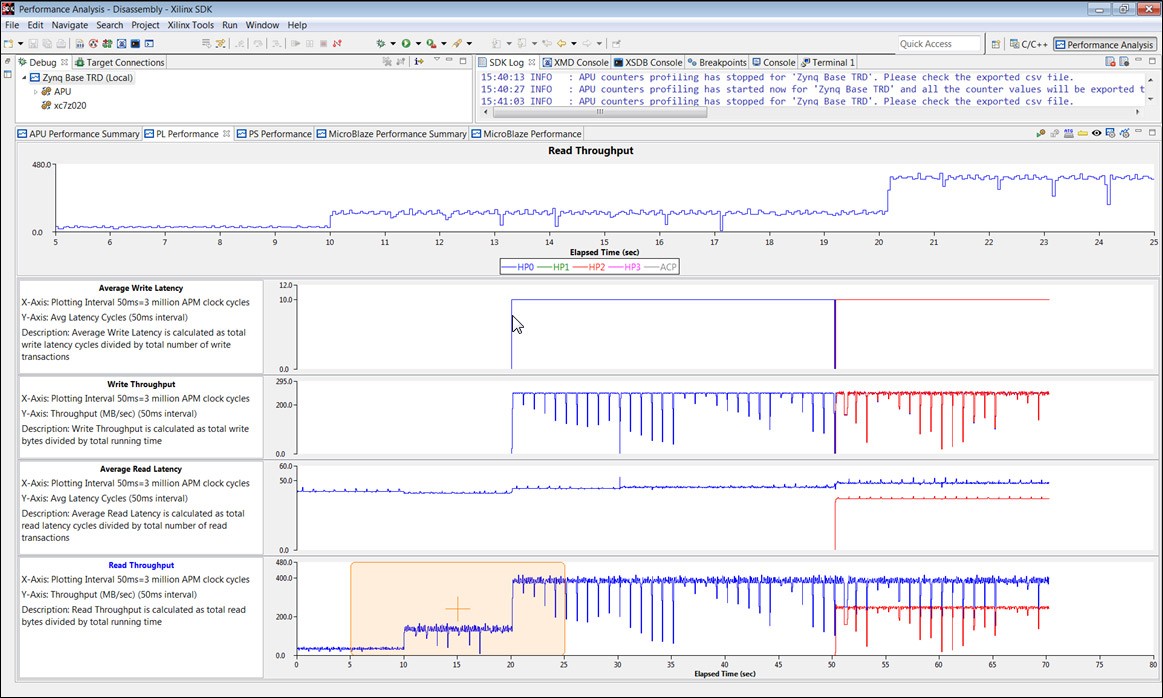

係統性能分析和優化

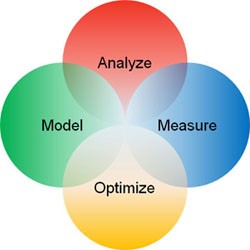

創建高性能 SoC 係統需要時間,還要了解軟件和外設之間的交互情況。 幫助您收集性能數據、實現係統可視化的工具對於滿足性能目標要求至關重要。AMD 係統性能分析工具箱(XSDK 中提供)可幫助您對係統進行建模、評測、分析和優化。在新的性能視圖中,您能查看:

- 處理器使用率

- 每個工作周期的指令

- 高速緩存未命中/擊中率

- 讀寫時延和 PL 到 PS 接口的帶寬

係統性能分析工具箱幫助您與係統互動,能調節係統達到您所需的性能目標。

利用上述工具,您能快速發現瓶頸,並就如何進行係統軟硬件分區設定假設性情境。您用 AXI 流量生成器可對 IP 塊進行性能建模,在完成前這些 IP 塊會在可編程邏輯中。完成分析後,就可通過優化軟件源代碼、拆分處理器和可編程邏輯之間的功能或者將全部功能遷移到可編程邏輯上來提高性能。