隔離設計流程

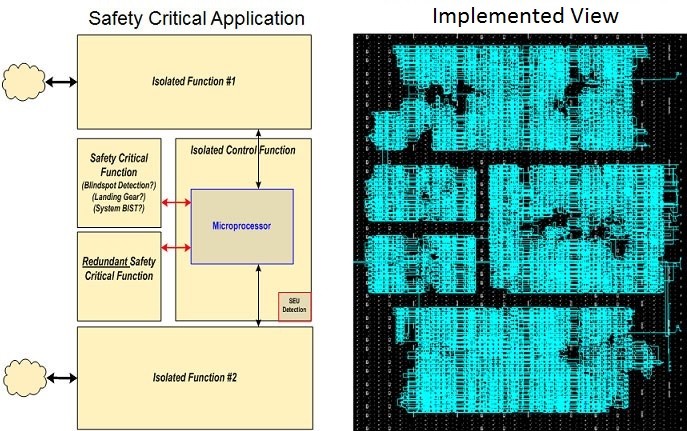

安全關鍵應用中的故障容錯

通過容錯設計掌控係統失效模式需要確保故障傳播可控的實現方法。AMD 隔離設計流程(IDF)通過多種技術提供了在 FPGA 模塊層次的容錯,並實現了單芯片容錯,這些技術包括:

- 模塊化冗餘

- 看門狗報警

- 根據安全級別隔離

- 安全去除測試邏輯隔離

隔離設計流程率先用於政府密碼係統,後也適用於航空電子設備、功能安全相關的電子现金网博e百 、工業機器人、關鍵基礎設施、金融係統和其他高安全、高可用性、高可靠性的係統。隔離設計流程是可靠性技術係列的一部分,通過適當組合可提供無與倫比的可靠性、性能和成本效率。

除了政府級別加密係統的悠久服務傳統,IDF也是 AMD IEC61508 (工業功能安全) 標準工具鏈的組成部分。此外,它可以幫助现金网博e百 滿足 ISO26262 規範要求(汽車性能安全)。

器件和軟件支持

* 僅 7S50

IDF 方法

文檔和參考設計

Virtex 5 FPGA

- Virtex 5 SCC

XAPP1134 "Developing Secure Designs Using the Virtex 5 Family” - 可幫助 FPGA 設計者實現容錯係統 SCC 技術的 AMD 隔離設計流程。 - 使用 ISE 11.4 / 11.5 Design Suite 的 SCC

XAPP1135 "Single Chip Crypto Lab Using PR/ISO Flow with the Virtex 5 Family" - 可幫助 FPGA 設計者使用 ISE 11.4 / 11.5 Design Suite 實現容錯係統 SCC 技術的 AMD 隔離設計流程。 - XAPP1135 參考設計和應用筆記

XAPP1105 " Single Chip Crypto Lab Using PR/ISO Flow with the Virtex 5 Family for ISE Design Suite 12.1" - 可幫助 FPGA 設計者使用 ISE 12.1 / 12.4 Design Suite 實現容錯係統 SCC 技術的 AMD 隔離設計流程。

Spartan 6 FPGA

- 麵向 Spartan 6 的隔離設計流程(IDF)

XAPP1145 "Developing Secure Designs with the Spartan 6 Family Using the Isolation Design Flow" - 有助於 FPGA 設計師實現安全設計。 - 使用 ISE 12.4 Design Suite 的隔離設計流程實驗(Isolation Design Flow Lab)

XAPP1104 "Implementation of a Fail-Safe Design in the Spartan 6 Family Using ISE Design Suite 12.4' - 可幫助 FPGA 設計者使用隔離設計流程實現安全設計。

7係列 FPGA

ISE Design Suite

- 麵向 7 係列的隔離設計流程(IDF)規則/指南

XAPP1086 "Developing Secure and Reliable Single FPGA Designs with The AMD Isolation Design Flow for Fault-Tolerant Systems 7 Series FPGAs Using the Isolation Design Flow" - 可幫助 FPGA 設計者實現安全可靠的設計。 - Kintex 7: 使用 ISE 14.4 Design Suite 的隔離設計流程 (IDF) 實驗

XAPP1085 "7 Series Isolation Design Flow Lab Using ISE Design Suite 14.4", 可幫助 FPGA 設計者使用隔離設計流程實現安全設計。

Vivado Design Suite

- 麵向 7 係列 (Vivado 工具) 的隔離設計流程(IDF)規則/指南

XAPP1222 "Isolation Design Flow for The AMD Isolation Design Flow for Fault-Tolerant Systems 7 Series FPGAs or Zynq 7000 SoCs (Vivado Tools)"可幫助 FPGA 設計人員實現安全可靠的設計。 - Zynq 7000: Vivado 隔離設計流程 (IDF) 實驗

XAPP1256 "Zynq 7000 SoC Isolation Design Flow Lab (Vivado Design Suite 2015.2)" - 可幫助 FPGA 設計者使用隔離設計流程實現安全設計。

UltraScale+ FPGAs & Zynq UltraScale+

Vivado Design Suite

- 麵向 UltraScale+ 的隔離設計流程(IDF)規則/指南

XAPP1335 "Isolation Design Flow for Zynq UltraScale+" 介紹了如何使用適用於容錯係統 IDF 的 AMD 隔離設計流程以及適用於容錯係統的 AMD 隔離設計流程 Vivado Design Suite 來實現安全或安全關鍵型設計。 - Vivado 隔離驗證器用戶指南 Vivado 隔離驗證器用戶指南

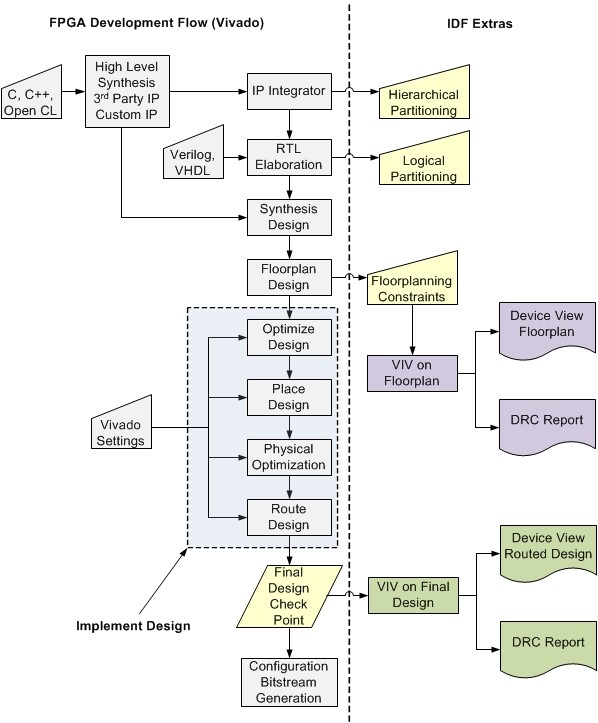

從 Vivado 2018.3 開始,Vivado 隔離驗證器 (VIV) 將與 Vivado 版本集成,支持 UltraScale+ 器件(包括 Zynq UltraScale+)。本文檔主要介紹如何在 FPGA/PL 設計中使用新的 Vivado 隔離驗證器 (VIV) 來驗證隔離。 - Zynq UltraScale+ 的隔離設計實例

Zynq UltraScale+ 的 XAPP1336 隔離設計實例

介紹如何將低功率域 (LPD) 作為一個通道和 PL 中的一個三模冗餘 MicroBlaze 來創建和實現單片通用 2 通道係統。

驗證工具

IDF 驗證工具 (IVT and VIV) 驗證 FPGA 設計劃分為隔離區域,滿足故障保險設計的嚴格標準。IVT 和 VIV 用於 FPGA 設計周期的兩個階段。IVT 先是用在設計流程早期,針對布局規劃和引腳分配,執行一係列設計規則檢查。設計完成後,再次使用IVT,所需隔離已置入設計。

隔離驗證工具 (IVT) ISE Design Suite

IVT 為可執行文件,運行於 ISE 之外,但完全在 ISE 環境中。IVT 作為一組設計規則檢查 (DRC) 運行,需要證明運行的設計是隔離的。它輸出設計和詳細文本報告的圖形顯示。

- IVT.zip 文件包含:

- IVT 可執行文件

- 版本說明和安裝指南

- 許可協議

- 實驗

注意: IVT 現有版本支持 、 Virtex 5、Spartan 6、 和 7 係列 FPGA 和 SoC

- 下載 IVT 包 (ZIP)

Vivado 隔離驗證 (VIV) Vivado Design Suite

VIV 是基於 Tcl 的腳本,集成 Vivado DRC 引擎。它本質上是一係列 DRC,加載到 Vivado - 執行證明設計隔離所需的所有檢查。與 ISE 前身 IVT 不同的是,VIV 集成了利用 Vivado GUI 用戶友好性的開發工具,但仍然保持獨立的開發路徑。其輸出集成至 Vivado DRC GUI 顯示以及由 Vivado DRC 引擎啟動的文本輸出

- VIV.zip 文件包含:

- VIV Script

- 版本說明和安裝指南

- 許可協議

- Lab (即將推出)

注意: VIV 現有版本支持 Vivado 2015.1 或更高版本中的 7 係列 FPGA 和 SoC。

- 下載 VIV 包 (ZIP)

注意:從 2018.2 開始,Vivado 隔離驗證器將與 Vivado 設計套件版本集成,而且這支持 UltraScale+ 器件(包括 Zynq UltraScale+)。了解更多信息,請參考 UG1291: Vivado Isolation Verifier 用戶指南。