Xilinx Platform Studio(XPS)

Xilinx Platform Studio (XPS) 是 ISE 嵌入式版本 Design Suite 的關鍵組件,可幫助硬件設計人員方便地構建、連接和配置嵌入式處理器係統,能充分滿足從簡單狀態機到成熟的 32 位 RISC 微處理器係統的需求。

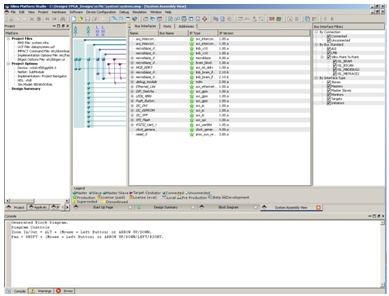

XPS 采用圖形設計視圖和通過設計校正的高級向導能幫助開發人員一步步完成創建定製係統所需的步驟,且用時不過幾分鍾而已。

XPS 的真正潛力體現在它能配置和集成 AMD 嵌入式 IP 核目錄中的即插即用 IP 核以及定製和第三方 Verilog 及 VHDL 設計。

固件和軟件真人百家乐游戏开户 受益於 XPS 與 SDK 的集成,從而能自動生成關鍵的係統軟件,如引導載入程序、裸金屬 BSP 和 Linux BSP 等。上述功能可確保 OS 移植和應用開發能及時啟動,而不會因為固件開發而延誤。

Zynq™ 7000 SoC 通過集成 ARM Cortex A9 雙核微處理器和具有以太網、I2C、SDIO、USB 和 CAN 等功能的硬外設集,從而可提供 SoC 的尖端功能,並配套提供 AMD 可編程邏輯,能將定製軟外設、邏輯、器件和加速器進行實例化。XPS 通過易於使用的圖形向導可加速 Zynq 器件設計的方方麵麵,包括用於硬外設的時鍾域設置、中斷、DMA 和外部連接以及用於可編程邏輯中軟外設的接口連接等。 這意味著設計人員能立即啟動定製設計,而無需擔心接口或連接的定義不兼容。

- AXI 接口

- 通用型 32 位 AXI 主/從端口

- 高速 32/64 位 AXI 從端口

- 64 位 AXI 加速器連接端口

- 通用 DMA 控製器

- 係統、外設、跟蹤和調試時鍾

- 硬型 Zynq-EPP 外設接口

- Quad SPI/SRAM/NOR/NAND Flash

- 千兆位級以太網

- USB 2.0

- 安全數字

- UART

- I2C

- SPI

- CAN

- GPIO

- 中斷

- 外設連接至多路複用 I/O

Microblaze™ 具有出色的可擴展性和可定製潛力,能夠滿足 8 位狀態機到複雜 SoC 型 32 位 RISC 設計的要求,並且可支持各種項目的具體處理要求。工程師利用 XPS 集成預驗證的處理器內部 IP(如流水線、時鍾、計時器和中斷控製器)和處理器外設 IP 核(如存儲器控製器、USB、CAN 總線、I2C、以太網、FPU 等)可創建出成百上千種不同的 Microblaze 設計(通過 AMD 嵌入式 IP catalog 提供)。這種現有的處理器配置功能結合集成第三方 RTL 和定製 IP 塊的功能,能夠幫助工程師推出真正獨特的定製設計,從而充分滿足具體的需求。

XPS 在定製處理器設計中支持 AMD 嵌入式 IP catalog 下 IP 核的拖放集成。這種 IP 核包括外設、器件和加速器,如 AXI 橋接器、GPIO、PLBV4.6 橋接器、BRAM 和外部存儲器控製器、串行外設和 QuadSPI 接口、模數轉換器、圖形、時鍾和計時器、UART、I2C、中斷控製器乃至更多。

雖然 AMD 目錄中的外設可創建多種係統,通常我們仍需要為新功能創建並導入定製外設。AMD 的創建和導入外設向導能讓硬件設計人員用 Verilog 或 VHDL(也可二者同時使用,針對混合語言設計)創建 AXI(第四版)外設並導入到 XPS 項目中,連接於任何 AXI4-Lite、AXI4(啟用 Burst)和 AXI4-Stream 接口。該向導還能讓您集成 PLB(4.6 版本)或 FSL 外設 PLB 設計。導入 XPS 時,定製外設的管理與 AMD 嵌入式 IP 核目錄提供的現有模塊一樣。

XPS 可簡化每個 IO 引腳的連接或內部可編程邏輯端點到適當端點的連接。 XPS 能方便地管理連接,通過物理接口連接片外,也可連接到可編程邏輯中的其它器件,確保適當路由、信號和電壓軌的準確性。對 Zynq 7000 SoC 器件係列而言,XPS 還能夠管理內置 IO 多路複用器的配置,可路由處理係統器件到適當的輸出引腳。

采用 AMD FPGA 或 Zynq 7000 SoC 等可編程邏輯創建的定製設計需要定製固件全程管理定製硬件,從一級啟動到器件實例化(比特流)到初始化直到器件具體接口(通過軟件堆棧)。由於固件開發和定製硬件設計之間的嚴格相關性,這種固件的創建可能非常具有挑戰性。XPS 同 SDK 共享硬件、項目和針對具體設計的信息,而 SDK 則能自動配置、構建和部署針對具體設計的關鍵固件,包括:

- 第一級引導載入程序

- 安全軟件(引導載入程序、固件)

- 比特流管理

對來自 AMD 嵌入式 IP 核目錄的器件,SDK 還能自動生成金屬裸麵驅動程序和 BSP,可加入無 OS 的代碼或 RTOS,也可生成 Linux 驅動程序和 BSP。這樣,XPS 就能讓設計人員基本不用再擔心固件和低級 BSP 開發問題了,避免為啟動、OS 和應用開發操心。

XPS 的優勢

| AMD - 硬件感知 |

|

| AMD 嵌入式 IP Catalog 集成 |

|

| 圖形配置向導 |

|

| 確保正確的連接功能 |

|

| 集成/連接至 AMD 工具流程 |

|