# Vivado Design Suite Tutorial

## **Power Analysis and Optimization**

UG997 (v2022.2) October 19, 2022

Xilinx is creating an environment where employees, customers, and partners feel welcome and included. To that end, we're removing noninclusive language from our products and related collateral. We've launched an internal initiative to remove language that could exclude people or reinforce historical biases, including terms embedded in our software and IPs. You may still find examples of non-inclusive language in our older products as we work to make these changes and align with evolving industry standards. Follow this <u>link</u> for more information.

# AMD7 XILINX

# Table of Contents

| Lab 1: Power Analysis and Optimization Tutorial                                           | 4  |

|-------------------------------------------------------------------------------------------|----|

| Software Requirements                                                                     |    |

| Locating Tutorial Design Files                                                            | 4  |

| Lab 2: Running Power Analysis in the Vivado Tool                                          | 6  |

| Introduction                                                                              |    |

| Designing with Versal                                                                     |    |

| Designing with UltraScale+                                                                |    |

| Conclusion                                                                                |    |

| Lab 3: Running Timing Simulation and Estimating Power                                     | 30 |

| Introduction                                                                              |    |

| Step 1: Configuring and Running the Timing Simulation using Vivado Simulator              |    |

| Step 2: Running Report Power in Vectorless Mode                                           |    |

| Step 3: Running Report Power with Vivado Simulator SAIF Data                              | 33 |

| Generating a SAIF File using Questa Advanced Simulator                                    | 35 |

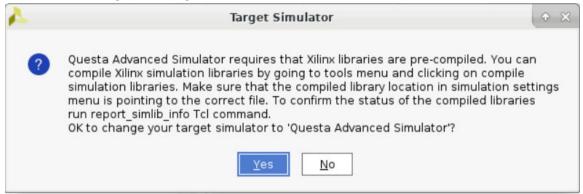

| Step 1: Configuring and Running Timing Simulation in Questa Advanced Simulator            | 37 |

| Step 2: Running Report Power in Vectorless Mode                                           | 39 |

| Step 3: Running Report Power with Questa Advanced Simulator SAIF Data                     |    |

| Conclusion                                                                                | 41 |

| Lab 4: Performing Power Optimization                                                      | 42 |

| Introduction                                                                              |    |

| Step 1: Setting Up Options to Run Power Optimization                                      | 42 |

| Step 2: Running report_power_opt to Examine User/Design Specific Power                    |    |

| Optimizations                                                                             | 44 |

| Step 3: Running report_power to Examine Power Savings                                     | 46 |

| Step 4: Turning Off Optimizations on Specific Signals and Rerunning the<br>Implementation |    |

| Step 5: Running report_power_opt to Examine Tool Optimizations Again                      |    |

| Step 6: Saving Power using UltraScale+ Block RAM in Cascaded Mode                         |    |

| Conclusion                                                                                |    |

|                                                                                           |    |

| Appendix A: Additional Resources and Legal Notices | 50 |

|----------------------------------------------------|----|

| Xilinx Resources                                   |    |

| Documentation Navigator and Design Hubs            |    |

| References                                         | 50 |

| Revision History                                   | 51 |

| Please Read: Important Legal Notices               | 51 |

I ab 1

# Power Analysis and Optimization Tutorial

This tutorial introduces the power analysis and optimization model recommended for use with the Xilinx<sup>®</sup> Vivado<sup>®</sup> Integrated Design Environment (IDE). The tutorial describes the basic steps involved in taking a small example design from RTL to implementation, estimating power through the different stages, and using simulation data to enhance the accuracy of the power analysis. It also describes the steps involved in using the power optimization tools in the design.

VIDEO: The Vivado Design Suite Quick Take Video: Power Estimation and Analysis Using Vivado shows bow the Vivado Design Suite can help you to estimate power consumption in your design and reviews best practices for getting the most accurate estimation.

VIDEO: The Vivado Design Suite QuickTake Video: Power Optimization Using Vivado describes the factors 0 that affect power consumption in an FPGA, shows how the Vivado Design Suite helps to minimize power consumption in your design, and looks at some advanced control and best practices for getting the most out of Vivado power optimization.

### Software Requirements

This tutorial requires the latest Vivado Design Suite software is installed. For installation instructions and information, see the Vivado Design Suite User Guide: Release Notes, Installation, and Licensing (UG973).

### **Locating Tutorial Design Files**

1. Download the reference design files:

ug997-vivado-power-analysis-optimization-tutorial.zip

2. Extract the zip file contents into any write-accessible location.

This tutorial refers to the location of the extracted ug997-vivado-power-analysisoptimization-tutorial.zip file contents as <Extract\_Dir>.

f IM

**IMPORTANT!** You will modify the tutorial design data while working through this tutorial. Use a new copy of the original data each time you start this tutorial.

The ug997-vivado-power-analysis-optimization-tutorial.zip file includes a readme file which contains the details and version history of the design files along with the folders of Versal<sup>®</sup> ACAP and UltraScale+<sup>™</sup> design files.

### UltraScale+ Tutorial Design Files

You can find a separate UltraScale+ folder containing the UltraScale+ tutorial design files in the contents of the zip file.

The following table describes the contents of the UltraScale+<sup>™</sup> tutorial design files:

| Files                      | Description                                               |

|----------------------------|-----------------------------------------------------------|

| /src                       | Contains the design HDL and testbench for the simulation. |

| /src/dut_fpga.v            | Top module for the design.                                |

| /src/dut.v                 | Other design blocks.                                      |

| /src/Cascade_bram.v        |                                                           |

| /src/Noncascade_bram.v     |                                                           |

| /src/bram_top_cascade.v    |                                                           |

| /src/bram_top_noncascade.v |                                                           |

| /src/bram_tdp_cas.v        |                                                           |

| /src/bram_tdp_noncas.v     |                                                           |

| dut_fpga_zcu102.xdc        | Contains clocking and timing constraints for the design.  |

| /src/testbench.v           | Testbench for simulating the design.                      |

### **Versal Device Tutorial Design Files**

You can find a separate Versal folder containing the Versal device tutorial design files in the contents of the zip file.

The following table describes the contents of the Versal device tutorial design files:

#### Table 1: Example table

| Files      | Description                           |

|------------|---------------------------------------|

| design.tcl | Tcl script to create design using IPI |

Lab 2

# Running Power Analysis in the Vivado Tool

### Introduction

In this lab, you learn about the Power Analysis and Optimization features in the Vivado<sup>®</sup> IDE. The lab walks you through the project creation and power analysis steps at the synthesis stage, using the Vivado Report Power feature in the vectorless mode. It also demonstrates using the Switching Activity Interchange Format (SAIF) file that is generated from the Post-Synthesis Functional simulation for Vivado report power analysis.

You will analyze power of the design in Vivado IDE. Then you will examine some of the major features in the Report Power window and closely examine some power specific Tcl commands. You will also learn how to simulate the design in the timing simulation stage using both the Vivado simulator and Questa Advanced Simulator to create a SAIF file.

You will also learn how to achieve power optimization after <code>opt\_design</code> in the Vivado IDE. You will examine the power optimization report and selectively turn power optimizations ON or OFF on specific signals, nets, modules, or hierarchy.

```

AMDA

XILINX

```

### **Designing with Versal**

### **Step 1: Creating a New Project**

IP integrator (IPI) is used to create the design.

On Linux, do the following.

1. Go to the directory where the lab materials are stored:

```

cd <Extract_Dir>/Versal (for Versal devices)

```

2. Launch Vivado IDE: vivado

On Windows, do the following.

3. Launch the Vivado IDE by selecting Start → All Programs → Xilinx Design Tools → Vivado 2022.x → Vivado 2022.x (x denotes the latest version of Vivado 2022 IDE).

As an alternative, click the Vivado 2022.x Desktop icon to start the Vivado IDE.

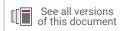

The Vivado IDE Getting Started page contains links to open or create projects, and to view documentation.

- 4. In the Getting Started page, click in Tcl Console to type the command.

- 5. Type the following command to generate a block design (BD): source <Extract\_Dir/</pre> Versal/design.tcl.

Note: It might take a moment for the design to initialize in Vivado IDE.

### AMD7 XILINX

| Tcl Console                                                                                  | ? _ 🗆 🖒 X |

|----------------------------------------------------------------------------------------------|-----------|

|                                                                                              |           |

| ⊖ start_gui<br>⊖ Warning: Tried to connect to session manager, Could not open network socket | Â         |

| source C:\vivado_pover_tutorial\design.tcl                                                   | 0         |

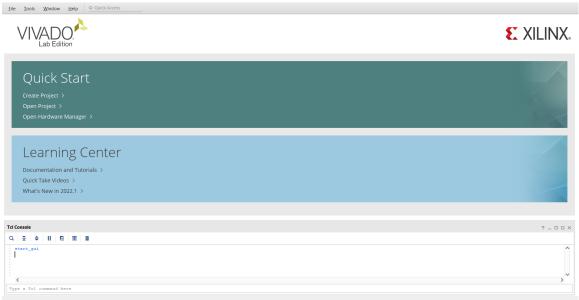

- 6. When the block design is generated, you can find the block design file (design\_1.bd) in the Sources window. A top-level HDL wrapper around the block design is needed because a BD source cannot be synthesized.

- 7. To generate HDL wrapper:

- a. Right-click on your block design source file (design\_1.bd) under Design Sources drop-down.

- b. Click Create HDL Wrapper option.

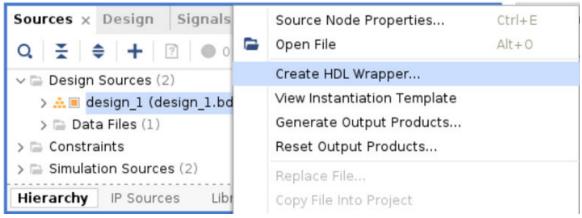

c. In the Create HDL Wrapper dialog box, select Let Vivado manage wrapper and autoupdate option and click OK.

The design is now ready for synthesis.

### AMD XILINX

### Step 2: Synthesizing the Design

- 1. Click **Run Synthesis** in the Flow Navigator.

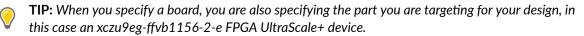

- 2. The Synthesis Completed dialog box appears after synthesis is completed on the design.

| 💫 Synthesis Completed 🛛 🗠 🗙                               |

|-----------------------------------------------------------|

| <b>i</b> Synthesis successfully completed.<br><b>Next</b> |

| O <u>R</u> un Implementation                              |

| Open Synthesized Design                                   |

| ◯ <u>V</u> iew Reports                                    |

| Don't show this dialog again                              |

| OK Cancel                                                 |

3. Select **Open Synthesized Design** in the Synthesis Completed dialog box and then click **OK** to open the synthesized design.

### Step 3: Report Power Setup

Vivado IDE allows you to specify the input data to the Report Power tool to enhance the accuracy of the power analysis.

In Vivado IDE, you can configure thermal, environmental, and power supply options to mimic the board level settings as closely as possible. For information on setting these options, see the *Vivado Design Suite User Guide: Power Analysis and Optimization* (UG907).

- 1. In the main menu bar, select **Reports**  $\rightarrow$  **Report Power**.

- 2. Examine the Environment tab in the Report Power dialog box.

|      | DЛ |

|------|----|

| XILI | NX |

| nvironment         | power_1 Power Supply | switching | <u>O</u> utput |      |            | 0 |

|--------------------|----------------------|-----------|----------------|------|------------|---|

| Device Settir      | ngs                  |           |                |      |            |   |

| Temp grad          | e:                   | extended  | ~              |      |            |   |

| Pro <u>c</u> ess:  |                      | maximum   | ~              |      |            |   |

| Environment        | Settings             |           |                |      |            |   |

| Output <u>L</u> oa | d:                   |           | 0 🌲            | pF   | [0 - 10000 | ] |

| [] Junction        | temperature:         |           | 100.0          | °C   |            |   |

| Ambient te         | mperature:           |           | 25 🌲           | °C   |            |   |

| Effective          | e ØJA:               |           | 5.163          | °C/W | [0-100]    |   |

|                    |                      |           |                |      |            |   |

|                    |                      |           |                |      |            |   |

|                    |                      |           |                |      |            |   |

|                    |                      |           |                |      |            |   |

|                    |                      |           |                |      |            |   |

3. In the Environment tab, set **Process** to maximum for worst case power analysis. Examine the Power Supply tab.

**IMPORTANT!** By default, Vivado Report Power uses nominal values for voltage supply sources. Voltage is a large factor contributing to both static and dynamic power. For the most accurate analysis, ensure that actual voltage values are entered for each supply. Similarly, ensure that the temperature and other environmental factors match the actual operating conditions.

| AM   | DЛ |

|------|----|

| XILI | NX |

| timate power consun<br>vc1902-vsva2197-2M |            | n the netlist design and part    | A |

|-------------------------------------------|------------|----------------------------------|---|

| Res <u>u</u> lts name: powe               | r_1        |                                  | 0 |

| Environment Po                            | wer Supply | <u>S</u> witching <u>O</u> utput |   |

| Design Power Budge                        | et   w     |                                  |   |

| Settings                                  |            |                                  |   |

| Vcci <u>n</u> t:                          | 0.800 🌲 V  | [0.775 - 0.825]                  | ^ |

| VCC_SOC:                                  | 0.800 🗘 V  | [0.775 - 0.825]                  |   |

| VCC_IO:                                   | 0.800 🗘 V  | [0.775 - 0.825]                  |   |

| VCCRAM:                                   | 0.800 🗘 V  | [0.775 - 0.825]                  |   |

| Vccaux:                                   | 1.500 🗘 V  | [1.425 - 1.575]                  |   |

| VCC_PMC:                                  | 0.800 🗘 V  | [0.775 - 0.825]                  |   |

| VCC0 <u>5</u> 03:                         | 3.300 🗘 V  | [3.135 - 3.465]                  |   |

| VCC0_5 <u>0</u> 0:                        | 3.300 🌲 V  | [3.135 - 3.465]                  |   |

| VCC0_50 <u>1</u> :                        | 3.300 🗘 V  | [3.135 - 3.465]                  |   |

| VCC0_50 <u>2</u> :                        | 3.300 🗘 V  | [3.135 - 3.465]                  |   |

| VCCAUX_PMC:                               | 1.500 🗘 V  | [1.425 - 1.575]                  |   |

| VCCAUX_SMON:                              | 1.500 🌲 V  | [1.425 - 1.575]                  |   |

| VCC_PSLP:                                 | 0.800 🗘 V  | [0.775 - 0.825]                  | ~ |

| Legend                                    |            |                                  |   |

| User Defined                              | Calculated | Default                          |   |

4. In the Switching tab, expand Constrained Clocks and examine the constrained clocks in the design.

IMPORTANT! Make sure all the relevant clocks in the design are constrained. All the design clocks must be defined using *create\_clock* or *create\_generated\_clock* XDC constraints, so that Report Power recognizes the clocks.

Make sure that the Default toggle rate is set to 12.5% and Default Static Probability is set to 0.5. This is applied to primary input ports (non-clock) and black box outputs.

| XILINX |  |

|--------|--|

|                                         |                                     | Power            |           | 2 20      | 0        |

|-----------------------------------------|-------------------------------------|------------------|-----------|-----------|----------|

| timate power cons<br>vc1902-vsva2197-2  |                                     | on the net       | list desi | gn and pa | art      |

| Res <u>u</u> lts name: pov              | wer_l                               |                  |           |           |          |

| Environment P                           | ower Supply                         | <u>S</u> witchi  | ng 🖸      | utput     |          |

| Beset switching<br>Switching Activity f | g activity before<br>for Resets: No | report pov<br>ne | wer       | *         |          |

| Simulation Setti                        | ngs                                 |                  |           |           |          |

| Simulation activ                        | vity file (.saif):                  |                  |           |           |          |

| Default Activity                        | Settings                            |                  |           |           |          |

| Default toggle                          | rate:                               | 12.5             | [0 - 100  | 0]        |          |

| Default Static F                        | robability:                         | 0.5              | [0.0 - 1  | .0]       |          |

| Enable Rate Set                         | tings                               |                  |           |           |          |

|                                         | S                                   | Static Prob      | ability   | Τος       | gle Rate |

| BRAM Port Ena                           | ble:                                |                  | [0.0 - 1  | .0]       | [0 - 1   |

| BRAM Write Ena                          | able:                               |                  | [0.0 - 1  | .0]       | [0 - 1   |

| Bidi Output Por                         | t Enable:                           |                  | [0.0 - 1  | .0]       | [0 - 1   |

| Toggle Rate Set                         | tings                               |                  |           |           |          |

|                                         | 5                                   | Static Prob      | ability   | Тор       | gle Rate |

| Primary Output                          | S:                                  |                  | [0.0 - 1  | .0]       | [0 - 1   |

| Logic                                   |                                     |                  |           |           |          |

| Registers:                              |                                     |                  | [0.0 - 1  | .0]       | [0 - 1   |

| C 000000000000000000000000000000000000  |                                     |                  |           |           |          |

- 5. In the Output tab of the Report Power dialog box, specify **Export to file** as power\_1.pwr.

- Specify the Output XPE file as power\_1.xpe. After creating this file, when Report Power runs, you can import the file and its results into the Xilinx Power Estimator. For information on importing the file into the Xilinx Power Estimator, see the Xilinx Power Estimator User Guide (UG440).

- 7. Specify the RPX file by setting Interactive report file as power\_1.rpx to write the results of the Report Power command. The saved RPX file can be reloaded using the **Reports** → **Open Interactive Report** command to provide interaction or cross-probing with the open design.

| A |                                      |                           | Report  | Power            |                  |                | •     | × |

|---|--------------------------------------|---------------------------|---------|------------------|------------------|----------------|-------|---|

| E | Estimate power c<br>«cvc1902-vsva219 | onsumption<br>97-2MP-e-S. | based o | n the netlis     | at design and    | l part         |       |   |

|   | Res <u>u</u> lts name:               | power_1                   |         |                  |                  |                | Ø     |   |

|   | <u>E</u> nvironment                  | Power S                   | upply   | <u>s</u> witchin | g <u>O</u> utput |                |       |   |

|   | ✓ Output XPE                         | file:                     | power_  | 1.xpe            |                  | 6              |       |   |

|   | ✓ Interactive                        | report file:              | power_  | 1.rpx            |                  | 6              |       |   |

|   | 🕑 Export to fi                       | e:                        | power_  | 1.pwr            |                  | 6              |       |   |

|   |                                      |                           | Output  | file format:     | ● <u>TXT</u>     | ⊖x <u>m</u> l  |       |   |

|   |                                      |                           |         |                  | Overwrite        | ○ <u>А</u> рре | nd    |   |

|   |                                      |                           |         |                  |                  |                |       |   |

|   |                                      |                           |         |                  |                  |                |       |   |

|   |                                      |                           |         |                  |                  |                |       |   |

|   |                                      |                           |         |                  |                  |                |       |   |

|   |                                      |                           |         |                  |                  |                |       |   |

|   |                                      |                           |         |                  |                  |                |       |   |

|   |                                      |                           |         |                  |                  |                |       |   |

|   |                                      |                           |         |                  |                  |                |       |   |

|   |                                      |                           |         |                  |                  |                |       |   |

|   |                                      |                           |         |                  |                  |                |       |   |

|   |                                      |                           |         |                  |                  |                |       |   |

|   |                                      |                           |         |                  |                  |                |       |   |

|   |                                      |                           |         |                  |                  |                |       |   |

|   | ?                                    |                           |         |                  | ОК               | C              | ancel | ] |

### Legends in Report Power Tool

The following legends appear consistently in the Report Power tool:

- **Constraint:** Displays when the nets are defined as clock with timing constraints. The defined frequency of a clock determines the switching activity.

- **Simulation:** Displays when the nets with switching activities are derived from simulation's .saif file.

- User Defined: Displays when the nets with user set switching activities are derived from set\_switching\_activity power Tcl command.

- Estimated: Displays when the nets with switching activities are generated by report\_power vectorless propagation engine.

- **Default:** Displays when the nets include default switching activities. If you use set\_switching\_activity on input port nets or on internal nets before running report\_power (vectorless propagation), the report tool displays the default.

### **Step 4: Running Report Power**

1. Click **OK** on the Report Power dialog box.

This runs the report\_power command.

2. Examine the power report, power\_1, that is generated in the Power window in Vivado IDE.

**Note:** Due to continuous accuracy improvements in Vivado tools, the actual power numbers you see might be slightly different than the ones that appear in the following figures.

| Power                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                   |           |                                    |                                                                 |  |  |  | ? _ 🗆 🖓 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------|-----------------------------------------------------------------|--|--|--|---------|

| Q ≚ ♦ C 📕                                                                                                                                                                                                                                                                                                                           | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                   |           |                                    |                                                                 |  |  |  |         |

| Settings<br>Summay (30.017 W, Margin: N/A)<br>Power Supply<br>V Utilization Details<br>Hierarchical (3.573 W)<br>Clocks (0.007 W)<br>> Sat/Reset (0 W)<br>Set/Reset (0 W)<br>Set/Reset (0 W)<br>Clock Manager (0.23 W)<br>V0 (1.213 W)<br>OTY (0.465 W)<br>> VOC_DDRMC (0.315 W)<br>NOC (0.21 W)<br>DDRMC (0.106 W)<br>PS (1.337 W) | Power estimation from Synthesized<br>derived from constraints files, simi<br>vectorless analysis. Note: these et<br>can change after implementation.<br><b>Total On-Chip Power:</b><br><b>Design Power Budget:</b><br><b>Power Budget Margin:</b><br><b>Junction Temperature:</b><br><b>Thermal Margin:</b><br>Effective 8JA:<br>Power supplied to off-chip devices:<br>Confidence level:<br>Launch Power Constraint Advisor t<br>invalid switching activity | Jation files or           30.017 W           Not Specified           N/A           100.0°C           0.0°C (26.1 W)           2.5°C/W           0 W           Low | On-Chip P | Dynamic:<br>6%<br>34%<br>13%<br>9% | Clocks:<br>Logic:<br>XPLL:<br>I/O:<br>GTY:<br>NOC_DDRMC:<br>PS: |  |  |  |         |

- 3. Examine the power breakdown in the power report by block type (Logic, GTY, I/O, etc.).

- 4. Examine the current consumption by individual rails in the Power Supply view.

| Power                                   |               |             |           |             |            |             |            |              |         | ? _ 🗆 🖓    |

|-----------------------------------------|---------------|-------------|-----------|-------------|------------|-------------|------------|--------------|---------|------------|

| Q ¥ ♦ C 🖬                               | Power Supply  |             |           |             |            |             |            | User Defined | Default | Calculated |

| Settings                                | Supply Source | Voltage (V) | Total (A) | Dynamic (A) | Static (A) | Budget (A)  | Margin (A) |              |         |            |

| Summary (30.017 W, Margin: N/A)         | Vccint        | 0.800       | 26.237    | 0.162       | 26.075     | Unspecified | NA         |              |         |            |

| Power Supply                            | VCC_SOC       | 0.800       | 3.599     | 0.394       | 3.205      | Unspecified | NA         |              |         |            |

| <ul> <li>Utilization Details</li> </ul> | VCC_IO        | 0.800       | 1.034     | 0.719       | 0.315      | Unspecified | NA         |              |         |            |

| Hierarchical (3.573 W)                  | VCCRAM        | 0.800       | 0.272     | 0.000       | 0.272      | Unspecified | NA         |              |         |            |

| Clocks (0.007 W)                        | Vccaux        | 1.500       | 3.634     | 0.240       | 3.394      | Unspecified | NA         |              |         |            |

| Signals (0 W)                           | VCC_PMC       | 0.800       | 0.355     | 0.265       | 0.090      | Unspecified | NA         |              |         |            |

| Data (0 W)                              | VCC0_503      | 3.300       | 0.300     | 0.000       | 0.300      | Unspecified | NA         |              |         |            |

| Clock Enable (0 W)                      | VCC0_500      | 1.800       | 0.058     | 0.058       | 0.000      | Unspecified | NA         |              |         |            |

| Set/Reset (0 W)                         | VCC0_501      | 1.800       | 0.000     | 0.000       | 0.000      | Unspecified | NA         |              |         |            |

| Logic (0.006 W)                         | VCC0 502      | 1.800       | 0.331     | 0.031       | 0.300      | Unspecified | NA         |              |         |            |

| Clock Manager (0.23 W)                  | VCCAUX PMC    | 1.500       | 0.270     | 0.068       | 0.202      | Unspecified | NA         |              |         |            |

| VO (1.213 W)                            | VCCAUX_SMON   | 1.500       | 0.104     | 0.000       | 0.104      | Unspecified | NA         |              |         |            |

| GTY (0.465 W)                           | VCC_PSLP      | 0.800       | 0.430     | 0.215       | 0.216      | Unspecified | NA         |              |         |            |

| V NOC_DDRMC (0.315 W)<br>NOC (0.21 W)   | VCC PSFP      | 0.800       | 2.391     | 0.865       | 1.525      | Unspecified | NA         |              |         |            |

| DDRMC (0.106 W)                         | Vcco33        | 3.300       | 0.000     | 0.000       | 0.000      | Unspecified | NA         |              |         |            |

| PS (1.337 W)                            | Vcco25        | 2.500       | 0.000     | 0.000       | 0.000      | Unspecified | NA         |              |         |            |

| F3 (1.337 W)                            | Vcco18        | 1.800       | 0.000     | 0.000       | 0.000      | Unspecified | NA         |              |         |            |

|                                         | Vcco15        | 1.500       | 0.410     | 0.001       | 0.409      | Unspecified | NA         |              |         |            |

|                                         | Vcco135       | 1.350       | 0.000     | 0.000       | 0.000      | Unspecified | NA         |              |         |            |

|                                         | Vcco12        | 1.200       | 0.448     | 0.422       | 0.026      | Unspecified | NA         |              |         |            |

|                                         | Vccoll        | 1.100       | 0.000     | 0.000       | 0.000      | Unspecified | NA         |              |         |            |

|                                         | Vcco10        | 1.000       | 0.000     | 0.000       | 0.000      | Unspecified | NA         |              |         |            |

|                                         | VCC FUSE      | 1.800       | 0.000     | 0.000       | 0.000      | Unspecified | NA         |              |         |            |

|                                         | VCC BATT      | 1.500       | 0.000     | 0.000       | 0.000      | Unspecified | NA         |              |         |            |

|                                         | GTY AVCCAUX   | 1.500       | 0.066     | 0.002       | 0.064      | Unspecified | NA         |              |         |            |

|                                         | GTY AVCC      | 0.880       | 0.481     | 0.118       | 0.363      | Unspecified | NA         |              |         |            |

|                                         | GTY_AVTT      | 1.200       | 0.531     | 0.202       | 0.329      | Unspecified | NA         |              |         |            |

5. Examine the hierarchical breakdown of the power in the **Utilization Details** → **Hierarchical** view.

| ower                                   |                            |                           |            |           |                   |          |         |         |         |           |               | ? _ 🗆   |

|----------------------------------------|----------------------------|---------------------------|------------|-----------|-------------------|----------|---------|---------|---------|-----------|---------------|---------|

| Q ¥ ♦ C 🖬                              | 🔍 🔮 Hierarchical           |                           |            |           |                   |          |         |         |         |           |               |         |

| Settings                               | Utilization                | Name                      | Clocks (W) | Logic (W) | Clock Manager (W) | XPLL (W) | I/O (W) | GTY (W) | NOC (W) | DDRMC (W) | NOC_DDRMC (W) | PS (W)  |

| Summary (30.017 W, Margin: N/A)        | 3.573 W (12% of total)     | N design_1_wrapper        |            |           |                   |          |         |         |         |           |               |         |

| Power Supply                           | 3.573 W (12% of total)     | I design_1_i (design_1)   | 0.007      | 0.006     | 0.23              | 0.23     | 1.213   | 0.465   | 0.21    | 0.106     | 0.315         | 1.337   |

| Utilization Details                    | > 🔲 1.762 W (6% of total)  | 🚺 axi_noc_0 (design_1_ax  | 0.004      | <0.001    | 0.23              | 0.23     | 1.213   | < 0.001 | 0.21    | 0.106     | 0.315         | < 0.001 |

| Hierarchical (3.573 W)                 | > 🛯 1.341 W (4% of total)  | 🚺 versal_cips_0 (design_1 | <0.001     | 0.004     | <0.001            | < 0.001  | < 0.001 | < 0.001 | < 0.001 | <0.001    | <0.001        | 1.337   |

| Clocks (0.007 W)                       | > 0.467 W (2% of total)    | I gt_quad_base_0 (desig   | 0.001      | 0.001     | <0.001            | < 0.001  | < 0.001 | 0.465   | < 0.001 | < 0.001   | < 0.001       | < 0.001 |

| ✓ Signals (0 W)                        | >   0.002 W (<1% of total) | I axis_vio_0 (design_1_ax | 0.001      | 0.001     | < 0.001           | < 0.001  | < 0.001 | < 0.001 | < 0.001 | < 0.001   | < 0.001       | < 0.001 |

| Data (0 W)                             | > 0.001 W (<1% of total)   | I gt_bridge_ip_0 (design_ | 0.001      | 0.001     | <0.001            | < 0.001  | < 0.001 | < 0.001 | < 0.001 | <0.001    | < 0.001       | < 0.001 |

| Clock Enable (0 W)                     | <0.001 W (<1% of total)    | 🖴 Leaf Cells (3)          |            |           |                   |          |         |         |         |           |               |         |

| Set/Reset (0 W)                        |                            |                           |            |           |                   |          |         |         |         |           |               |         |

| Logic (0.006 W)                        |                            |                           |            |           |                   |          |         |         |         |           |               |         |

| Clock Manager (0.23 W)                 |                            |                           |            |           |                   |          |         |         |         |           |               |         |

| VO (1.213 W)                           |                            |                           |            |           |                   |          |         |         |         |           |               |         |

|                                        |                            |                           |            |           |                   |          |         |         |         |           |               |         |

| GTY (0.465 W)                          |                            |                           |            |           |                   |          |         |         |         |           |               |         |

|                                        |                            |                           |            |           |                   |          |         |         |         |           |               |         |

| GTY (0.465 W)                          |                            |                           |            |           |                   |          |         |         |         |           |               |         |

| GTY (0.465 W)<br>~ NOC_DDRMC (0.315 W) |                            |                           |            |           |                   |          |         |         |         |           |               |         |

6. Examine the Clocks view and the various Signals views (Data, Clock Enable and Set/Reset).

| Power                                   |                                               |                                                                                         |                 |        |                         | ? _ 🗆         | 1 P X |

|-----------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|--------|-------------------------|---------------|-------|

| Q 素 ≑ C 📓                               | Q 🔮 Clocks                                    |                                                                                         |                 |        | Constra                 | int 🗌 Calcula | ated  |

| Settings                                | Utilization                                   | Name                                                                                    | Frequency (MHz) | Buffer | Clock Buffer Enable (%) | Enable Signal | Fan   |

| Summary (30.017 W, Margin: N/A)         | <ul> <li>0.007 W (&lt;1% of total)</li> </ul> | N design_1_wrapper                                                                      |                 |        |                         |               |       |

| Power Supply                            | > 0.003 W (<1% of total)                      | <pre>_ design_1_i/versal_cips_0/inst/pspmc_0/inst/pmc_pl_ref_clk[0]</pre>               | 100.000         | N/A    | N/A                     | N/A           | 3     |

| <ul> <li>Utilization Details</li> </ul> | > 0.001 W (<1% of total)                      | <pre>_ design_1_i/axi_noc_0/inst/MC0_ddrc/inst/noc_ddr4_phy/inst/pll_clk_xpll</pre>     | 3200.000        | N/A    | N/A                     | N/A           |       |

| Hierarchical (3.573 W)                  | > 0.001 W (<1% of total)                      | <pre>_ design_1_i/axi_noc_0/inst/MC0_ddrc/inst/noc_ddr4_phy/inst/pll_clktoxphy[0]</pre> | 3200.000        | N/A    | N/A                     | N/A           |       |

| Clocks (0.007 W)                        | > 0.001 W (<1% of total)                      | <pre>_ design_1_i/axi_noc_0/inst/MC0_ddrc/inst/noc_ddr4_phy/inst/pll_clktoxphy[2]</pre> | 3200.000        | N/A    | N/A                     | N/A           |       |

| ✓ Signals (0 W)                         | > 0.001 W (<1% of total)                      | design_1_i/axi_noc_0/inst/MC0_ddrc/inst/noc_ddr4_phy/inst/bank1_xpll0_fifo_rd_clk       | 800.000         | N/A    | N/A                     | N/A           |       |

| Data (0 W)                              | > <0.001 W (<1% of total)                     | <pre>_ design_1_i/axi_noc_0/inst/MC0_ddrc/inst/noc_ddr4_phy/inst/bank1_clkout0</pre>    | 800.000         | N/A    | N/A                     | N/A           |       |

| Clock Enable (0 W)                      | > <0.001 W (<1% of total)                     | design_1_l/axi_noc_0/inst/MC0_ddrc/inst/noc_ddr4_phy/inst/mc_clk_xpll                   | 800.000         | N/A    | N/A                     | N/A           |       |

| Set/Reset (0 W)                         | > <0.001 W (<1% of total)                     | ddr4 dimm1 sma clk clk p                                                                | 200.000         | N/A    | N/A                     | N/A           |       |

| Logic (0.006 W)                         |                                               |                                                                                         |                 |        |                         |               |       |

| Clock Manager (0.23 W)                  |                                               |                                                                                         |                 |        |                         |               |       |

| 1/0 (1.213 W)                           |                                               |                                                                                         |                 |        |                         |               |       |

| GTY (0.465 W)                           |                                               |                                                                                         |                 |        |                         |               |       |

| VOC_DDRMC (0.315 W)                     |                                               |                                                                                         |                 |        |                         |               |       |

| NOC (0.21 W)                            |                                               |                                                                                         |                 |        |                         |               |       |

| DDRMC (0.106 W)                         |                                               |                                                                                         |                 |        |                         |               |       |

| PS (1.337 W)                            |                                               |                                                                                         |                 |        |                         |               |       |

|                                         |                                               |                                                                                         |                 |        |                         |               |       |

### Step 5: Implementing the Design

This tutorial helps you understand power analysis with and without power optimization. In this step, you will run Implementation without power optimization.

- 1. In the Flow Navigator, click Run Implementation.

- 2. When the Save Project dialog box is displayed before launching implementation, click **Don't Save**.

### Designing with UltraScale+

### **Step 1: Creating a New Project**

To create a project, use the New Project wizard to name the project, to add RTL source files and constraints, and to specify the target device.

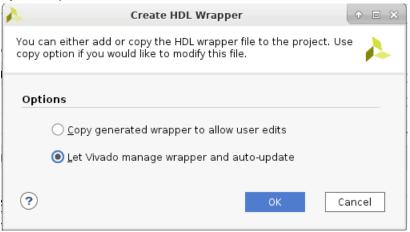

On Linux, do the following.

1. Go to the directory where the lab materials are stored:

cd <Extract\_Dir>/UltraScale+ (for UltraScale+ devices)

2. Launch Vivado IDE: vivado

| Eile Iools Window Help Q. Quick Access                                                            |           |

|---------------------------------------------------------------------------------------------------|-----------|

|                                                                                                   | £ XILINX. |

| Quick Start<br>Create Project ><br>Open Project ><br>Open Hardware Manager >                      |           |

| Learning Center<br>Documentation and Tutorials ><br>Quick Take Videos ><br>What's New in 2022.1 > |           |

| Td Console<br>Q 😤 ♦ II 🕢                                                                          | ? _ D & X |

| start_gui                                                                                         | ,<br>,    |

On Windows, do the following.

3. Launch the Vivado IDE by selecting Start → All Programs → Xilinx Design Tools → Vivado 2022.x → Vivado 2022.x (x denotes the latest version of Vivado 2022 IDE).

As an alternative, click Vivado 2022.x Desktop icon to start the Vivado IDE.

The Vivado IDE Getting Started page contains links to open or create projects and to view documentation.

- 4. In the Getting Started page, click **Create New Project** to start the New Project wizard.

- 5. Click **Next** to continue to the next screen.

| AM   | DЛ |

|------|----|

| XILI | NX |

| 🝌 New Vivado Lab      | Edition Project                                         | ×      |

|-----------------------|---------------------------------------------------------|--------|

| Specify the name a    | nd location for a new Vivado Lab Edition project.       | 4      |

| <u>P</u> roject name: | vivado_power_tutorial                                   | 8      |

| Project location:     | C:/vivado_power_tutorial                                | © ···· |

| Create project        | subdirectory                                            |        |

| Project will be cre   | ated at: C:/vivado_power_tutorial/vivado_power_tutorial |        |

|                       |                                                         |        |

|                       |                                                         |        |

|                       |                                                         |        |

|                       |                                                         |        |

|                       |                                                         |        |

|                       |                                                         |        |

|                       |                                                         |        |

|                       |                                                         |        |

|                       | ок                                                      | Cancel |

- 6. In the Project Name page, name the new project vivado\_power\_tutorial and enter the project location (C:\Vivado\_Power\_Tutorial). Make sure to check the **Create project** subdirectory option and click Next.

- 7. In the Project Type page, specify the type of project to create as **RTL Project** and make sure to uncheck the **Do not specify sources at this time** option. Click **Next**.

- 8. In the Add Sources page, do the following.

- a. Set Target Language to Verilog and Simulator language to Mixed.

- b. Click the Add Files button.

- c. In the Add Source Files dialog box, navigate to the <Extract\_Dir>/UltraScale

+/src directory.

- d. Select all of the Verilog (.v) source files, and click OK.

- e. In the Add Sources page, change the HDL Source For the  ${\tt testbench.v}$  file to Simulation only.

$\times$

#### 🝌 New Project

#### Add Sources

| -   _                            | •   •       | +                     |                |                          |                                             |  |

|----------------------------------|-------------|-----------------------|----------------|--------------------------|---------------------------------------------|--|

|                                  | Index       | Name                  | Library        | HDL Source For           | Location                                    |  |

| •                                | 1           | Cascaded_bram.v       | xil_defaultlib | Synthesis & Simulation 🔹 | C:/vivado_power_tutorial/UltraScalePlus/src |  |

| •                                | 2           | Noncascade_bram.v     | xil_defaultlib | Synthesis & Simulation 🔹 | C:/vivado_power_tutorial/UltraScalePlus/src |  |

| •                                | 3           | bram_tdp_cas.v        | xil_defaultlib | Synthesis & Simulation 🔹 | C:/vivado_power_tutorial/UltraScalePlus/src |  |

| •                                | 4           | bram_tdp_noncas.v     | xil_defaultlib | Synthesis & Simulation 🔹 | C:/vivado_power_tutorial/UltraScalePlus/src |  |

| •                                | 5           | bram_top_cascade.v    | xil_defaultlib | Synthesis & Simulation 🔹 | C:/vivado_power_tutorial/UltraScalePlus/src |  |

| •                                | 6           | bram_top_noncascade.v | xil_defaultlib | Synthesis & Simulation 🔹 | C:/vivado_power_tutorial/UltraScalePlus/src |  |

| •                                | 7           | dut.v                 | xil_defaultlib | Synthesis & Simulation 🔹 | C:/vivado_power_tutorial/UltraScalePlus/src |  |

| •                                | 8           | dut_fpga.v            | xil_defaultlib | Synthesis & Simulation 🔹 | C:/vivado_power_tutorial/UltraScalePlus/src |  |

| •                                | 9           | testbench.v           | xil_defaultlib | Simulation only          | C:/vivado_power_tutorial/UltraScalePlus/src |  |

| C <b>opy <u>s</u><br/>Add sc</b> | ources into | subdirectories        | <u>A</u> dd F  |                          | <u>C</u> reate File                         |  |

| let lan                          | iguage: V   | erilog 🗸 Simulator    | language: Mix  | ed 🗸                     |                                             |  |

- f. Verify that the files are added and **Copy sources into project** is checked. Click **Next**.

- 9. In the Add Constraints (optional) page, click Add Files and select dut\_fpga\_zcu102.xdc in the file browser. In the directory structure, you will find the dut\_fpga\_zcu102.xdc file below the /src folder.

- 10. Click **Next** to continue.

- 11. In the Default Part page, click **Boards** and select Zynq UltraScale+ ZCU102 Evaluation Board.

12. Review the New Project Summary page. Verify that the data appears as expected, per the steps above, and click **Finish**.

Note: It might take a moment for the project to initialize in the Vivado IDE.

### AMD**Z**I XILINX

| <u>File Edit Flow Tools Reports</u>       | Wurgen refert Ten Teh                                                                             | luick Access                            |                                                                                | Ready                                      |

|-------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------|

| 🖻 + + E E X 🕨 I                           |                                                                                                   |                                         |                                                                                | 📰 Default Layout 🗸 🗸                       |

| low Navigator — — ₹ ≑ ?                   | PROJECT MANAGER - power_tutorial1                                                                 |                                         |                                                                                | ?                                          |

| PROJECT MANAGER                           | Sources ? _ □ ◻ ×                                                                                 | Project Summary                         |                                                                                | ? 🗆 🗆 X                                    |

| Settings                                  |                                                                                                   | Overview   Dashboar                     | d                                                                              | 1000                                       |

| Language Templates                        | >  Design Sources (1) >  Constraints (1)                                                          | Settings Edit                           |                                                                                |                                            |

| 👎 IP Catalog                              | <pre>&gt; Simulation Sources (1) &gt; _ sim_1 (1)</pre>                                           | Project name:<br>Project location:      | power_tutorial1<br>/proj/dsv.xhd/uditr/POWER/Repo/ug997/usp/power_tutorial1    |                                            |

| IP INTEGRATOR                             | > 🚍 Utility Sources                                                                               | Product family:                         | Zynq UltraScale+ MPSoCs                                                        |                                            |

| Create Block Design<br>Open Block Design  | Hierarchy Libraries Com4 ▶ ≣                                                                      | Project part:<br>Top module name:       | Zynq UltraScale+ ZCU102 Evaluation Board (xczu9eg-ffvb1156-2-e)<br>Not defined | 1                                          |

| Generate Block Design                     | Properties ? _ 🗆 🖾 ×                                                                              | Target language:<br>Simulator language: | Verilog<br>Mixed                                                               |                                            |

| SIMULATION                                | ♦   ♦   ♦                                                                                         | Board Part                              |                                                                                |                                            |

| Run Simulation                            |                                                                                                   | Display name:                           | Zyng UltraScale+ ZCU102 Evaluation Board                                       |                                            |

| RTL ANALYSIS                              | Select an object to see properties                                                                | Board part name:<br>Board revision:     | xilinx.com:zcu102:part0:3.4                                                    |                                            |

| > Open Elaborated Design                  |                                                                                                   | Connectors:                             | 1.1<br>No connections                                                          |                                            |

| SYNTHESIS                                 | Tcl Console Messages Log R                                                                        | eports Design Runs                      | ×                                                                              | ? _ 🗆 🖾                                    |

| Run Synthesis     Open Synthesized Design | Q   ★   ♦         ≪   ▶   ≫   +                                                                   | F %                                     |                                                                                |                                            |

|                                           | Name         Constraints         Status           ∨ ▷ synth 1         constrs 1         Not start |                                         | THS WBSS TPWS Total Power Failed Routes LUT FF BRAM URAM DSP Star              | t Elapsed Run Strategy<br>Vivado Synthesis |

| IMPLEMENTATION  Run Implementation        | ▷ impl_1 constrs_1 Not start                                                                      | ed                                      |                                                                                | Vivado Implemen                            |

| > Open Implemented Design                 |                                                                                                   |                                         |                                                                                |                                            |

13. In the Settings dialog box (**Tools** → **Settings** → **Tool Settings** → **Project**), enter the tutorial project directory in the Specify project directory field, so that all reports are saved in the tutorial project directory. Then click **OK**.

Now, the design is ready for synthesis.

### Step 2: Synthesizing the Design

- 1. Click Run Synthesis in the Flow Navigator.

- 2. The Synthesis Completed dialog box appears after the synthesis is completed on the design.

3. Select **Open Synthesized Design** in the Synthesis Completed dialog box to open the synthesized design. Click **OK**.

### **Step 3: Report Power Setup**

For infomration on setting up report power, refer to the Step 3: Report Power Setup section in Designing with Versal.

### **Step 4: Running Report Power**

For information on running the report power, refer to the Step 4: Running Report Power section in Designing with Versal.

### **Step 5: Viewing the Power Properties**

This step walks you through the process of getting the display of static probability and toggle rate for a signal in the property window.

- 1. Note the total power (Total On-Chip Power) in the Power Report Summary view.

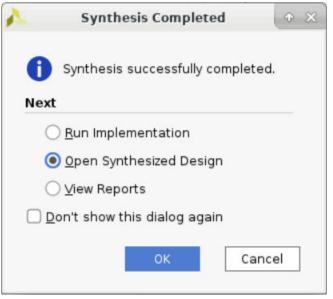

- 2. Click the Set/Reset item in the Power Report.

- 3. Click on the dut/dut\_reset signal.

4. Note that there is a Power view in the Net Properties window that displays the net properties for the dut/dut\_reset signal. Click on Load Power Properties to get the power information for the first time.

| Net Properties                                |             |                |       | ?     | _ 🗆 🕫 🗙 |

|-----------------------------------------------|-------------|----------------|-------|-------|---------|

| ∫ dut_reset                                   |             |                |       | -     | + 0     |

| Output                                        |             |                |       |       |         |

| Toggle rate: 0.0 %<br>Static probability: 0.0 |             |                |       |       |         |

|                                               | Edit Proper | ties           |       |       |         |

| General Properties Connectivity               | Power All   | ases Cell Pins | Nodes | Tiles | Pips    |

5. Note that the Toggle rate is 0% and the Static probability is 0 for the dut/dut\_reset signal, indicating that reset is always de-asserted in the design.

### **Step 6: Editing Power Properties and Refining the Power Analysis**

Assume that the reset is asserted for 10% of the cycles in this design. Switching activity can be set accordingly to re-estimate the power.

- 1. In the Net Properties window, click the Edit Properties button.

- 2. In the Edit Power Properties dialog box, change the Toggle rate to 4% and the Static probability to 0.1.

| roperties  | •           |

|------------|-------------|

| lut_reset. | - 🍌         |

|            |             |

| 4.000 🌲    | %           |

| 0.1  🌲     | [0.0 - 1.0] |

| ОК         | Cancel      |

|            | 4.000 ‡     |

- 3. Click OK.

- 4. In the Net Properties window, observe that the Toggle Rate and Static Probability values turn a different color to indicate that they are user defined.

| Net Properties $\times$             | Clock Regions   | ? _ 🗆 🖸                               |

|-------------------------------------|-----------------|---------------------------------------|

| _ dut_reset                         |                 | $\leftarrow   \Rightarrow   \diamond$ |

| Output                              |                 |                                       |

| Toggle rate:<br>Static probability: | 4.0 %<br>0.1    |                                       |

| Legend: 📃 User Defi                 | ned             |                                       |

|                                     |                 | _                                     |

|                                     | Edit Properties |                                       |

| General Propertie                   | s Connectivity  | Power Aliases 4 ▶ ≣                   |

You can also observe the equivalent Tcl command that is executed in the Tcl Console.

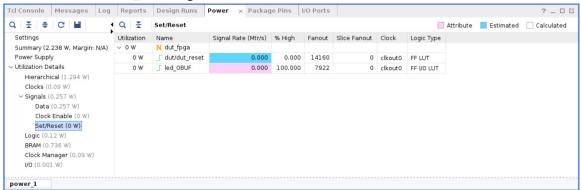

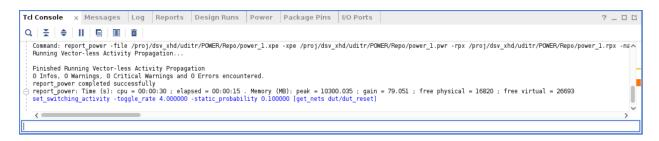

- 5. Re-run Report Power (**Reports**  $\rightarrow$  **Report Power**).

- 6. Change the Output text File and Output XPE File in the Output tab to **power\_2.pwr** and **power\_2.xpe** respectively.

- 7. In the Switching tab, set Switching Activity for Resets: to None. Then click OK.

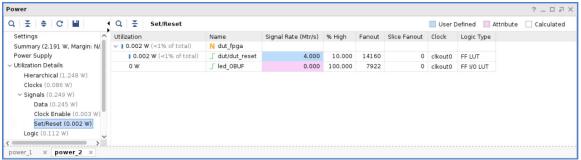

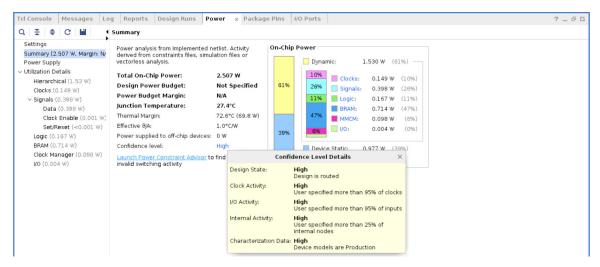

- 8. In the Power window, note the change in total power reported in the power\_2 report compared to the power\_1 report. The total power has decreased due to the change in the Signal Rate for the dut/dut\_reset signal. Because the signal is a reset signal, an increase in its activity will significantly reduce the activity of other signals in the design. The Signal Rate of the dut/dut\_reset signal is now color coded as being User Defined in both, the properties window and the Set/Reset view of the Power Report.

Xilinx recommends you to double-check the signal rates and percentage high (%High) values of high impact I/O ports, control signals (such as resets and clock enables) and high fanout nets. This is an opportunity to guide the Report Power tool towards the accurate power estimation.

See the Vivado Design Suite User Guide: Power Analysis and Optimization (UG907) for more information on switching activity.

**TIP:** In the Tcl console, use the *set\_switching\_activity* command to change the signal rate and static probability of signals and use *report\_switching\_activity* to query the values that are set on the signals.

```

set_switching_activity -signal_rate 4 -static_probability 0.1 \

[get_nets dut/dut_reset]

report_switching_activity [get_nets dut/dut_reset]

```

**IMPORTANT!** Switching activity can also be specified in terms of toggle rate. Toggle rate is always associated with a clock. The primary ports can be associated with a specific clock using the set\_input\_delay and set\_output\_delay commands. If no clock association is found, Report Power will associate the ports with respect to the capturing clock.

For a clock of 100 MHz and a toggle rate of 4, the equivalent signal rate will be 4 MTr/s (signal\_rate = toggle\_rate \* Freq =  $4 \times 100$  MHz ).

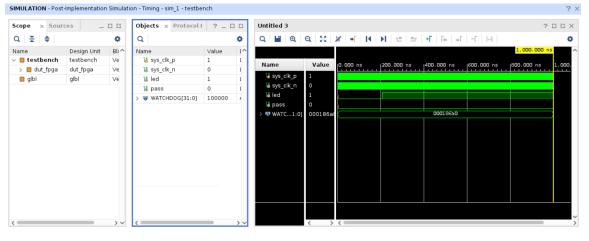

### Step 7: Running Functional Simulation with SAIF Output

Now that you have created a Vivado Design Suite project for the tutorial design, you can set up and launch the Vivado simulator to run post-synthesis functional simulation. Simulation will generate a switching activity interchange format file (SAIF) that will enable you to do more accurate power estimation on your design.

- 1. In the Flow Navigator, click **Settings** to open the Settings dialog box and set the simulation properties in the Simulation section.

- 2. In the Simulation section of Settings dialog box, note that the following Simulation defaults are automatically set for you based on the design files:

- Simulator language: Mixed

- Simulation set: **sim\_1**

- Simulation top-module name: testbench

#### Lab 2: Running Power Analysis in the Vivado Tool

| Q-                            | Simulation                    |         |                  |         |          |      |  |

|-------------------------------|-------------------------------|---------|------------------|---------|----------|------|--|

| Project Settings              | Specify various settings as   | sociate | ed to Simulation | n       |          | 1    |  |

| General                       |                               |         |                  |         |          |      |  |

| Simulation                    | Target simulator:             | V       | /ivado Simulator |         |          | ~    |  |

| Elaboration                   | Simulator language:           | N       | lixed            |         |          | ~    |  |

| Synthesis                     |                               | Te la   | lixed            |         |          | ~    |  |

| Implementation                | Simulation set:               |         | 🖕 sim_1          |         |          |      |  |

| Bitstream<br>> IP             |                               |         | estbench         | ench 💿  |          |      |  |

|                               | Generate simulation sc        | ipts o  | nlv              |         |          |      |  |

| Tool Settings                 |                               |         |                  |         |          |      |  |

| Project                       | Compilation Elabora           | ion     | Simulation       | Netlist | Advanced | 1    |  |

| IP Defaults<br>> Vivado Store | compliation clabora           | .1011   | Sindiación       | Nethst  | Advanced |      |  |

| Source File                   | Verilog options:              |         |                  |         |          |      |  |

| Display                       |                               |         |                  |         |          | = 11 |  |

| Help                          | <u>G</u> enerics/Parameters o | otions  | :                |         |          |      |  |

| > Text Editor                 | xsim.compile.tcl.pre          |         |                  |         |          |      |  |

| 3rd Party Simulators          | xsim.compile.xvhdl.no         | sort    |                  | 6       |          |      |  |

| > Colors                      | xsim.compile.xvlog.no         | sort    |                  |         |          |      |  |

| Selection Rules               | xsim.compile.xvlog.rel        | эх      |                  |         |          |      |  |

| Shortcuts                     | xsim.compile.xvhdl.rel        | эх      |                  |         |          |      |  |

| > Strategies                  | xsim.compile.xsc.more         | _optic  | ons              |         |          |      |  |

| > Remote Hosts                | xsim.compile.xvlog.mo         | re_opt  | tions            |         |          |      |  |

| > Window Behavior             | xsim.compile.xvhdl.mc         | re_opt  | tions            |         |          |      |  |

|                               | Select an option above to     | see a   | a description of | it      |          | _    |  |

- 3. In the Elaboration tab of the Simulation section, make sure the xsim.elaborate.debug\_level is set to **typical**, which is the default value.

- 4. In the Simulation tab, enter the SAIF file name as power\_tutorial\_func.saif for xsim.simulate.saif. Observe that the xsim.simulate.runtime is 1000 ns.

- 5. Make sure to check the xsim.simulate.log\_all\_signals box.

- 6. Click OK.

AMD**A** Xilinx

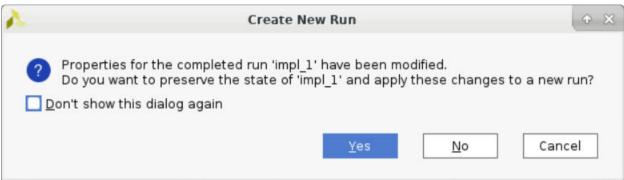

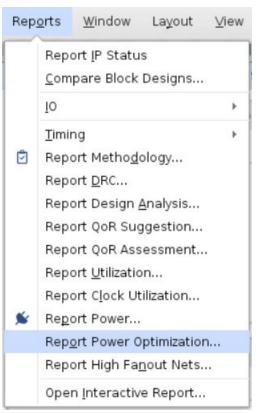

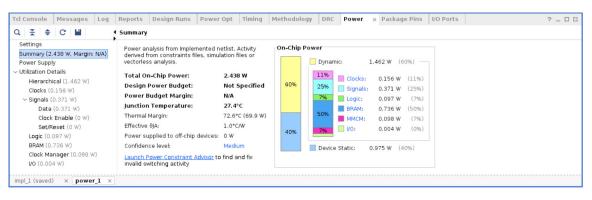

| Simulation<br>Specify various settings assoc<br>Target simulator: | iated to Simulatio                                                                                                                                                                                                                                                                                                                                                                              | n                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |