# Vivado Design Suite User Guide

## Designing IP Subsystems Using IP Integrator

Vivado Design Suite

UG994 (v2022.2) October 19, 2022

Xilinx is creating an environment where employees, customers, and partners feel welcome and included. To that end, we're removing noninclusive language from our products and related collateral. We've launched an internal initiative to remove language that could exclude people or reinforce historical biases, including terms embedded in our software and IPs. You may still find examples of non-inclusive language in our older products as we work to make these changes and align with evolving industry standards. Follow this <u>link</u> for more information.

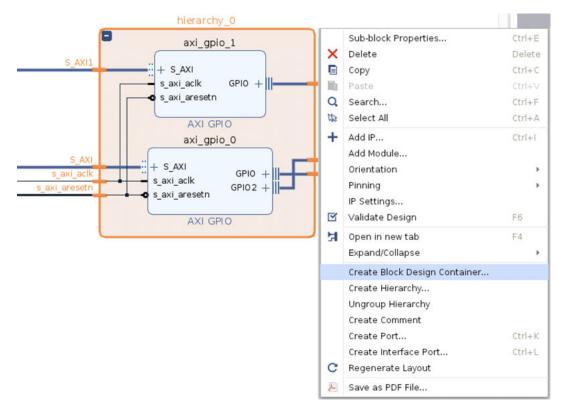

# Table of Contents

| Chapter 1: Getting Started with Vivado IP Integrator              | 6   |

|-------------------------------------------------------------------|-----|

| Navigating Content by Design Process                              |     |

| Chapter 2: Creating a Plack Design                                | 0   |

| Chapter 2: Creating a Block Design                                |     |

| Creating a Project                                                |     |

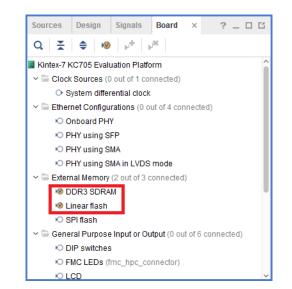

| Creating a Block Design                                           |     |

| Designing with IP Integrator                                      |     |

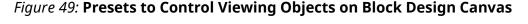

| Working with Presets to Control Block Design Views                |     |

| Hierarchical IP in IP Integrator<br>InterConnect vs. SmartConnect |     |

| Glue Logic IP in IP Integrator                                    |     |

| About On-Disk Objects and In-Memory Objects                       |     |

| Running Design Rule Checks                                        |     |

| Finding Objects in a Block Design                                 |     |

|                                                                   |     |

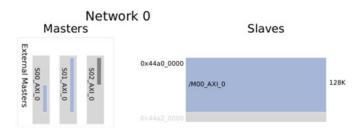

| Chapter 3: Addressing for Block Designs                           | 82  |

| Addressing Overview                                               |     |

| Addressing Structure                                              |     |

| Concepts                                                          | 83  |

| Using the Address Editor                                          | 84  |

| Address Map                                                       | 96  |

| Block Diagram Addressing View                                     | 100 |

| Common Addressing-Related Critical Warnings and Errors            | 101 |

| Chapter 4: Working with Block Designs                             | 102 |

| Generating Output Products                                        |     |

| Integrating the Block Design into a Top-Level Design              |     |

| Adding Existing Block Designs                                     |     |

| Adding and Associating an ELF File to an Embedded Design          |     |

| Saving a Block Design with a New Name                             |     |

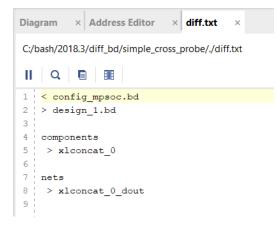

| Comparing Two Block Designs                                       |     |

| Packaging a Block Design                                          |     |

|                                                                   |     |

| Chapter 5: Collaborative Design in IP Integrator          |                 |

|-----------------------------------------------------------|-----------------|

| Modular Design with Block Design Containers               |                 |

| Creating Block Design Containers                          | 137             |

| Working with Block Design Containers                      |                 |

| Design Re-Use with Block Design Containers                | 145             |

| Revision Control for Block Designs                        | 146             |

| Chapter 6: Cross-Probing Timing Paths                     | 149             |

| Chapter 7: Propagating Parameters in IP Integrator        | 151             |

| Using Bus Interfaces                                      |                 |

| Parameter Propagation                                     | 156             |

| Parameters in the Customization GUI                       | 157             |

| Chapter 8: Debugging IP Integrator Designs                | 160             |

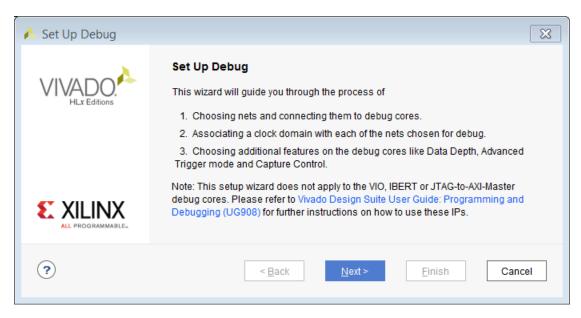

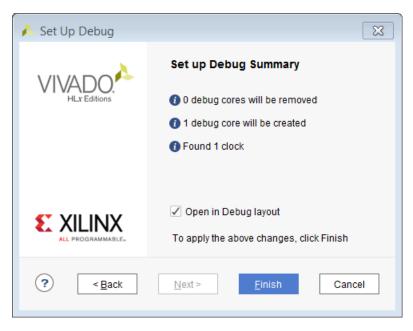

| Using the HDL Instantiation Flow in IP Integrator         | 161             |

| Using the Netlist Insertion Flow                          |                 |

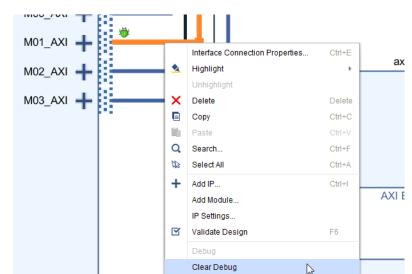

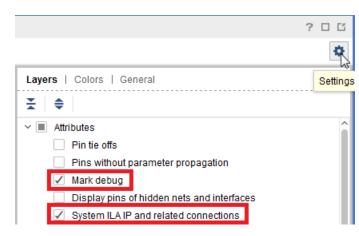

| Removing Debug Logic after Debug                          | 191             |

| Parameter Mismatch Example                                | 193             |

| Chapter 9: Using Tcl Scripts to Create Projects and Block | Designs 194     |

| Exporting a Block Design to a Tcl Script in the IDE       |                 |

| Saving Vivado Project Information in a Tcl File           | 197             |

| Chapter 10: Using IP Integrator in Non-Project Mode       | 201             |

| Creating a Flow in Non-Project Mode                       | 201             |

| Chapter 11: Updating Designs for a New Release            | 205             |

| Upgrading a Block Design in Project Mode                  |                 |

| Upgrading a Block Design in Non-Project Mode              | 209             |

| Selectively Upgrading IP in Block Designs                 | 210             |

| Chapter 12: Using the Platform Board Flow in IP Integrat  | t <b>or</b> 220 |

| Selecting a Target Board                                  |                 |

| Downloading Board Files from GitHub Using the Vivado      |                 |

| Creating a Block Design to Use the Board Flow             |                 |

| Completing Connections in the Block Design                |                 |

| Archiving a Project When Board Flow is Used               |                 |

Send Feedback

| Chapter 13: Using Third-Party Synthesis Tools in IP Integra | tor 233  |

|-------------------------------------------------------------|----------|

| Setting the Block Design as Out-of-Context Module           | 233      |

| Creating an HDL or EDIF Netlist in Synplify                 | 235      |

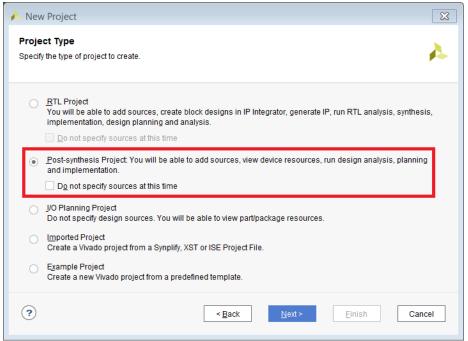

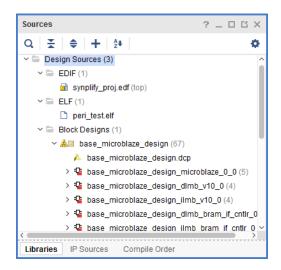

| Creating a Post-Synthesis Project in Vivado                 | 235      |

| Adding Top-Level Constraints                                | 237      |

| Adding an ELF File                                          | 238      |

| Implementing the Design                                     | 239      |

| Chapter 14: Referencing RTL Modules                         |          |

| Referencing a Module                                        | 242      |

| XCI Inferencing                                             |          |

| IP and Reference Module Differences                         | 250      |

| Inferring Generics/Parameters in an RTL Module              | 252      |

| Inferring Control Signals in a RTL Module                   |          |

| Inferring AXI Interfaces                                    | 257      |

| Prioritizing Interfaces for Automatic Inference             | 260      |

| HDL Parameters for Interface Inference                      |          |

| Editing the RTL Module After Instantiation                  |          |

| Module Reference in a Non-Project Flow                      |          |

| X_MODULE_SPEC Attribute                                     | 271      |

| Reusing a Block Design Containing a Module Reference        |          |

| Handling Constraints in RTL Modules                         |          |

| Limitations of the Module Reference Feature                 |          |

| Chapter 15: Creating Vitis Platforms Using Vivado/IP Integ  | rator278 |

| Creating the Platform Project in Vivado                     | 278      |

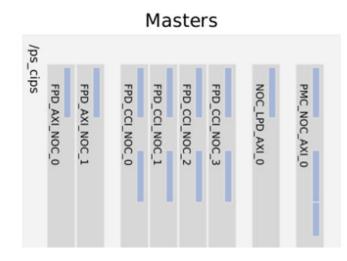

| Setting Up Platform (PFM) Interfaces and Properties         | 280      |

| Working with Platform Setup Window                          |          |

| Interface Type Settings                                     | 282      |

| Exporting Platforms to Vitis                                |          |

| Supported Project Structures to Export to Vitis             | 285      |

| Chapter 16: Versal Designs with IP Integrator               | 286      |

| Creating a Design with CIPS IP                              |          |

| Creating a Design with NoC IP                               |          |

| Creating a Design with GT IP                                |          |

| Creating a Design with Other IP                             | 290      |

|                                                             |          |

Send Feedback

| Appendix A: Additional Resources and Legal Notices | 293 |

|----------------------------------------------------|-----|

| Xilinx Resources                                   | 293 |

| Solution Centers                                   |     |

| Documentation Navigator and Design Hubs            | 293 |

| References                                         | 294 |

| Training Resources                                 | 295 |

| Revision History                                   | 295 |

| Please Read: Important Legal Notices               | 296 |

## Chapter 1

# AMD7 XILINX

## Getting Started with Vivado IP Integrator

As FPGAs become larger and more complex, and as design schedules become shorter, use of third-party IP and design reuse is becoming mandatory. Xilinx<sup>®</sup> recognizes the challenges designers face, and to aid designers with design and reuse issues, has created a powerful feature within the Vivado<sup>®</sup> Design Suite called the Vivado<sup>®</sup> IP Integrator.

The Vivado IP integrator lets you create complex system designs by instantiating and interconnecting IP from the Vivado IP catalog on a design canvas. You can create designs interactively through the IP integrator canvas GUI or programmatically through a Tcl programming interface. Designs are typically constructed at the interface level (for enhanced productivity) but may also be manipulated at the port level (for precision design manipulation).

An interface is a grouping of signals that share a common function. An AXI4-Lite master, for example, contains a large number of individual signals plus multiple buses, which are all required to make a connection. If each signal or bus is visible individually on an IP symbol, the symbol is visually very complex. By grouping these signals and buses into an interface, the following advantages can be realized:

- A single connection in IP integrator (or Tcl command) creates a master to slave connection.

- The graphical representation of this connection is a simple, single connection.

- Design Rule Checks (DRCs) that are aware of the specific interface can be run to assure that all the required signals are connected properly.

A key strength of IP Integrator is that it provides a Tcl command language extension mechanism for its automation services so that system design tasks, such as parameter propagation, can be optimized per-IP or application domain.

Additionally, IP Integrator implements dynamic, run-time DRCs to ensure that connections between the IP in an IP integrator design are compatible and that the IP themselves are properly configured.

## Navigating Content by Design Process

Xilinx<sup>®</sup> documentation is organized around a set of standard design processes to help you find relevant content for your current development task. All Versal<sup>®</sup> ACAP design process Design Hubs and the Design Flow Assistant materials can be found on the Xilinx.com website. This document covers the following design processes:

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, functional simulation, and evaluating the Vivado<sup>®</sup> timing, resource use, and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Chapter 2: Creating a Block Design

- Chapter 3: Addressing for Block Designs

- Chapter 4: Working with Block Designs

- Chapter 12: Using the Platform Board Flow in IP Integrator

- Chapter 13: Using Third-Party Synthesis Tools in IP Integrator

- **Board System Design:** Designing a PCB through schematics and board layout. Also involves power, thermal, and signal integrity considerations. Topics in this document that apply to this design process include:

- Chapter 10: Using IP Integrator in Non-Project Mode

# AMDA XILINX

## Chapter 2

# Creating a Block Design

This chapter describes the basic features and functionality of Vivado<sup>®</sup> IP integrator.

## **Creating a Project**

You can create entire designs using IP integrator; however, the typical design consists of HDL, IP, and IP integrator block designs (BDs). This section is an introduction to creating a new IP integrator-based design.

To create a project, click **Create Project** in the Vivado<sup>®</sup> IDE graphical user interface (GUI), as shown in the following figure.

#### Figure 1: Create Project

The Vivado Design Suite supports many different types of design projects. See this link in the Vivado Design Suite User Guide: System-Level Design Entry (UG895) for more information.

To add or create a BD in a project, create an RTL project, or select **Example Project**. You can add HDL design files, user constraints, and other types of design source files to the project using the New Project wizard.

| Nev    | v Project                                                                                                                                                                     | 2            |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Proje  | ect Type                                                                                                                                                                      |              |

| Specif | y the type of project to create.                                                                                                                                              | P            |

| ۲      | <u>B</u> TL Project<br>You will be able to add sources, create block designs in IP Integrator, generate<br>analysis, synthesis, implementation, design planning and analysis. | IP, run RTL  |

|        | Do not specify sources at this time                                                                                                                                           |              |

| 0      | Post-synthesis Project You will be able to add sources, view device resources analysis, planning and implementation.                                                          | , run design |

|        | Do not specify sources at this time                                                                                                                                           |              |

| 0      | J/O Planning Project<br>Do not specify design sources. You will be able to view part/package resources                                                                        | s.           |

| 0      | Imported Project<br>Create a Vivado project from a Synplify, XST or ISE Project File.                                                                                         |              |

| 0      | Example Project<br>Create a new Vivado project from a predefined template.                                                                                                    |              |

| -      |                                                                                                                                                                               |              |

| ?      | < Back Next > Einish                                                                                                                                                          | Cancel       |

#### Figure 2: New Project Wizard

After adding design sources, existing IP, and design constraints, you can also select the default Xilinx<sup>®</sup> device or platform board to target for the project, as shown in the following figure. For more information, see Chapter 12: Using the Platform Board Flow in IP Integrator.

**IMPORTANT!** The Vivado<sup>®</sup> tools support multiple versions of Xilinx target boards, so carefully select your target hardware.

**Note:** Click the blue command links to see more information about the Tcl commands in the Vivado Design Suite Tcl Command Reference Guide (UG835).

You can use the Tcl equivalent commands for creating a project, which are a combination of the create\_project and set\_property commands:

```

create_project <project_name> <project_path> -part <part>

set_property BOARD_PART <board_part> [current_project]

set_property TARGET_LANGUAGE <vhdl/verilog> [current_project]

```

**Note:** When displaying the Tcl commands in this document, the <> characters are used to designate variables that are specific to your design. Do not include the <> symbols in the command string.

See the Vivado Design Suite Tcl Command Reference Guide (UG835) for information on specific Tcl commands.

| Reset All Filters Vendor: All  Vame: All                                                                       |                |                    |

|----------------------------------------------------------------------------------------------------------------|----------------|--------------------|

| Vendor: All 🗸 Name: All                                                                                        |                |                    |

|                                                                                                                | ~              | Board Rev: Latest  |

| Q X + I                                                                                                        |                |                    |

| Search: Q. V                                                                                                   |                |                    |

| Display Name Preview Status V                                                                                  | /endor File Ve | rsion Part         |

| Virtex Ultrascale+ HBM VCU128 Evaluation Platform Installed x                                                  | ilinx.com 1.0  | xcvu37p-fsvh2892-2 |

| Virtex Ultrascale+ 56G VCU129 Evaluation Platform Installed x                                                  | ilinx.com 1.0  | xcvu29p-fsga2577-2 |

| Artik-7 AC701 Evaluation Platform                                                                              |                |                    |

| Add Companion Card Connections Installed x                                                                     | ilinx.com 1.4  | xc7a200tfbg676-2   |

| Kintex-7 KC705 Evaluation Platform                                                                             |                |                    |

| Add Companion Card Connections Installed x                                                                     | ilinx.com 1.6  | xc7k325tffg900-2   |

| the second s |                |                    |

## **Creating a Block Design**

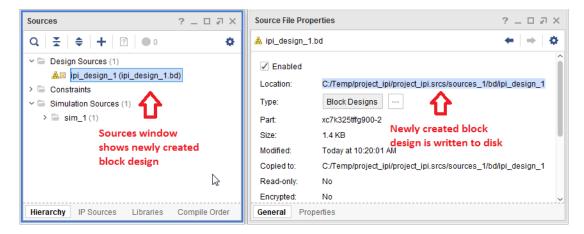

You can create a block design (BD) inside the current project directory, or outside of the project directory structure. A common use case for creating the BD outside of a project is to use the BD in non-project mode, or to use it in multiple projects, or to use it in a team-based design flow.

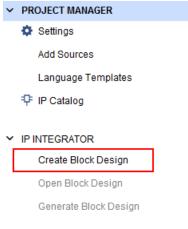

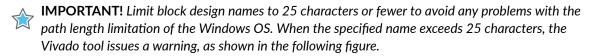

To create a new BD:

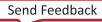

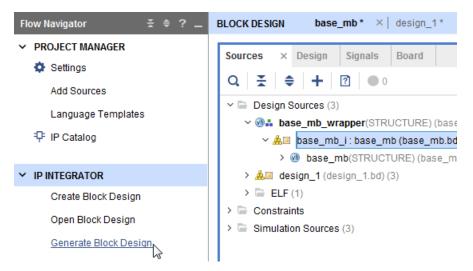

1. In the Flow Navigator, click **Create Block Design** under the IP INTEGRATOR section, as shown in the following figure.

The Create Block Design dialog box opens, as shown in the following figure.

| 🔥 Create Block Des                   | sign                               | ×      |  |  |

|--------------------------------------|------------------------------------|--------|--|--|

| Please specify name of block design. |                                    |        |  |  |

|                                      |                                    |        |  |  |

| Design name:                         | my_ipi_design                      | 8      |  |  |

| D <u>i</u> rectory:                  | 🛜 <local project="" to=""></local> | ~      |  |  |

| Specify source set:                  | 🚍 Design Sources                   | ~      |  |  |

| ?                                    | ОК                                 | Cancel |  |  |

2. Specify the Design name, Directory, and Specify source set for the design.

The default value for the Directory field is <Local to Project>. To override the default value, click **Directory** and select **Choose Location**.

3. Click OK.

The equivalent Tcl command to create a BD is create\_bd\_design. The syntax of the command is as follows:

create\_bd\_design <your\_design\_name>

The Create Block Design creates an empty BD on disk, which is not automatically removed if the BD is closed without saving.

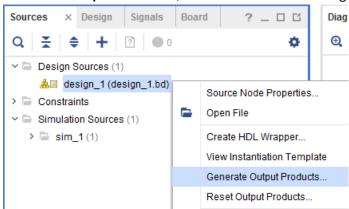

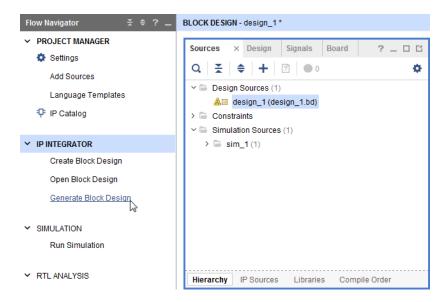

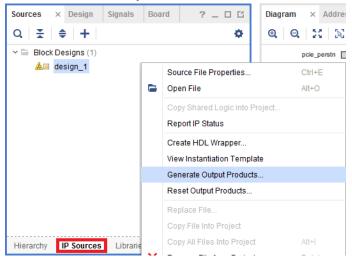

- 4. If you want to remove a newly-created Block Design, then manually delete the empty BD from the Sources window of the Vivado IDE by doing one of the following:

- Right-click the block design, and select **Remove File from Project**.

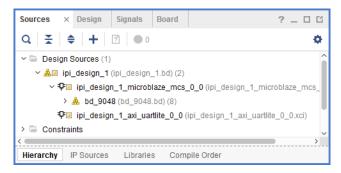

| Sources                     |                             | ? _ 🗆      | Ľ |  |  |  |

|-----------------------------|-----------------------------|------------|---|--|--|--|

| Q   ¥   <b>≑</b>   <b>+</b> | ? 0                         |            | - |  |  |  |

| 🗸 🚞 Design Sources (        | 1)                          |            |   |  |  |  |

| design ما الد               | lesian 1.bd)                |            |   |  |  |  |

| > 🚍 Constraints             | Source Node Properties      | Ctrl+E     |   |  |  |  |

| > 🚍 Simulation Si 🗧         | Open File                   | Alt+0      |   |  |  |  |

| > 🚍 Utility Source          | Create HDL Wrapper          |            |   |  |  |  |

|                             | View Instantiation Template |            |   |  |  |  |

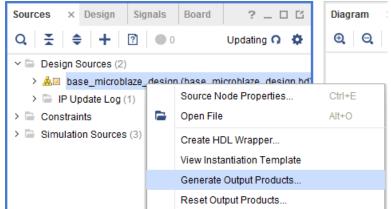

|                             | Generate Output Products    |            |   |  |  |  |

|                             | Reset Output Products       |            |   |  |  |  |

|                             | Replace File                |            |   |  |  |  |

| _                           | Copy File Into Project      |            |   |  |  |  |

| _                           | Copy All Files Into Project | Alt+I      |   |  |  |  |

| Hierarchy IP S ×            | Remove File from Project    | Delete     |   |  |  |  |

|                             | Enable File                 | Alt+Equals | - |  |  |  |

| Tcl Console M               | Disable File                | Alt+Minus  |   |  |  |  |

|                             |                             |            |   |  |  |  |

• Use the remove\_files Tcl command, shown as follows:

```

remove_files <project_name>/<project_name>.srcs/sources_1/bd/<bd_name>/

<bd_name>.bd

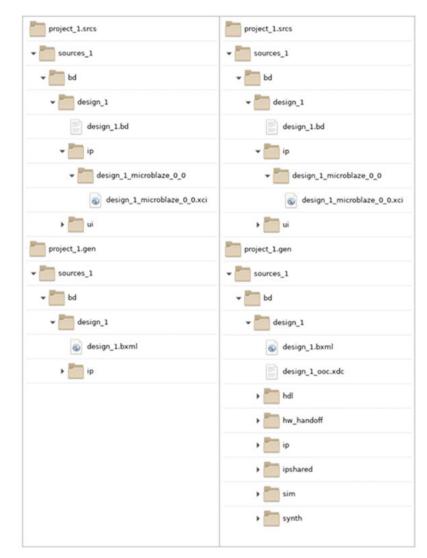

file delete -force <project_name>/<project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name></project_name>.srcs/sources_1/bd/<bd_name>

```

**Note:** Starting in Vivado Design Suite version 2018.3, the block design file format has changed from XML to JSON. When you open a block design that uses the older XML schema in Vivado 2018.3 or later, click **Save** to convert the format from XML to JSON. The following INFO message notifies you of the schema change.

INFO: [BD 41-2124] The block design file <block\_design.bd> has changed from an XML format to a JSON format. All flows are expected to work as in prior versions of Vivado. Please contact your Xilinx Support representative, in case of any issues.

**IMPORTANT!** The format conversion from XML to JSON occurs only during a Save operation.

## **Designing with IP Integrator**

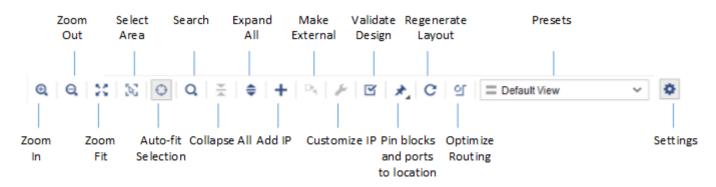

After you create a block design, the Vivado IP integrator provides a design canvas that you can use to construct your design. This canvas can be re-sized in the Vivado IDE. You can double-click the design canvas tab at the upper-left corner of the diagram to increase the size of the diagram.

When you double-click the tab again, the view returns to the default layout. You can move the

design canvas to a separate monitor by clicking the Float <sup>12</sup> button in the upper-right corner of the diagram, and moving the window as needed.

The following sections describe the procedures required to create a block design in the design canvas.

### Adding IP Modules to the Design Canvas

You can add IP modules to a diagram in the following ways:

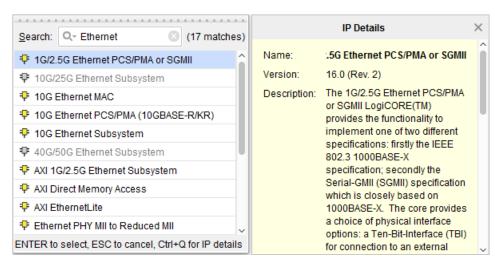

1. Right-click in the diagram, and select Add IP.

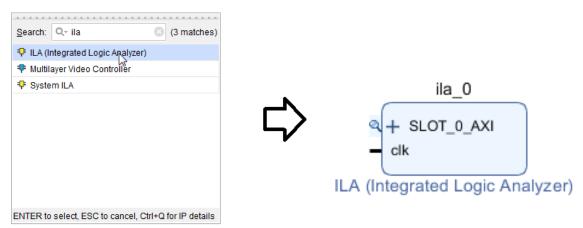

A searchable IP catalog opens, as shown in the following figure.

## AMD**Z** XILINX

| Search: Q-                                         |      |              | IP Details                                                           | × |

|----------------------------------------------------|------|--------------|----------------------------------------------------------------------|---|

|                                                    |      | Name:        | 5G Ethernet PCS/PMA or SGMII                                         |   |

| 👎 2D Graphics Accelerator Bit Block Transfer       | Ш    | Version:     | 16.0 (Rev. 2)                                                        |   |

| ₽ 3GPP LTE Channel Estimator                       |      | Description: | The 1G/2.5G Ethernet PCS/PMA                                         |   |

| 3GPP LTE MIMO Decoder                              |      |              | or SGMII LogiCORE(TM)<br>provides the functionality to               |   |

| 3GPP LTE MIMO Encoder                              |      |              | implement one of two different                                       |   |

| 3GPPLTE Turbo Encoder                              |      |              | specifications: firstly the IEEE<br>802.3 1000BASE-X                 |   |

| 👎 3GPP Mixed Mode Turbo Decoder                    |      |              | specification; secondly the                                          |   |

| 👎 3GPP Turbo Encoder                               |      |              | Serial-GMII (SGMII) specification<br>which is closely based on       |   |

| 7 Series Integrated Block for PCI Express          |      |              | 1000BASE-X. The core provides                                        |   |

| 👎 10G/25G Ethernet Subsystem                       | ~    |              | a choice of physical interface<br>options: a Ten-Bit-Interface (TBI) |   |

| ENTER to select, ESC to cancel, Ctrl+Q for IP deta | ails |              | for connection to an external                                        |   |

**TIP:** To enable the IP Details window of the IP catalog, press **Ctrl+Q** in the IP catalog window.

2. Type in a few letters of the IP name in the Search filter at the top of the catalog.

IP modules matching the search string display.

- 3. Select the IP to add by doing one of the following:

- To add a single IP, you can either click the IP name, and press **Enter** on your keyboard, or double-click the IP name.

- To add multiple IP to the BD, you can highlight the additional desired IP (**Ctrl**+ click), and press **Enter**.

You can also add IP to the BD by opening the IP catalog from the Project Manager menu in the Flow Navigator. Use the Search field to find specific IP in the IP catalog window as well.

| Cores   Inte     | rfaces                                                                                                                                                                                                 |                     |           |                  |          |                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------|------------------|----------|----------------------------------|

| <b>X   ♦  </b> ≇ | 🎽 🔩 🎤 🖉 🕲 🚱 🔍 🕰 Micro                                                                                                                                                                                  |                     | 8         |                  |          |                                  |

| Name             |                                                                                                                                                                                                        | ^1 AXI4             |           | Status           | License  | VLNV                             |

| ~ 🖻 Vivado F     | Repository                                                                                                                                                                                             |                     |           |                  |          |                                  |

| 🗠 🗁 Emb          | edded Processing                                                                                                                                                                                       |                     |           |                  |          |                                  |

| ~ 🖻 De           | ebug & Verification                                                                                                                                                                                    |                     |           |                  |          |                                  |

| <b></b>          | MicroBlaze Debug Module (MDM)                                                                                                                                                                          | AXI4, AXI4          | Stream    | Production       | Included | xilinx.com:ip:mdm:3.2            |

| Y 🖨 Pr           | ocessor                                                                                                                                                                                                |                     |           |                  |          |                                  |

| ę                | MicroBlaze                                                                                                                                                                                             | AXI4, AXI4          | Stream    | Production       | Included | xilinx.com:ip:microblaze:10.0    |

| ÷                | MicroBlaze MCS                                                                                                                                                                                         |                     |           | Production       | Included | xilinx.com:ip:microblaze_mcs:3.0 |

|                  |                                                                                                                                                                                                        |                     |           |                  |          |                                  |

| Details          |                                                                                                                                                                                                        |                     |           |                  |          |                                  |

| Name:            | MicroBlaze                                                                                                                                                                                             |                     |           |                  |          |                                  |

| Version:         | 10.0 (Rev. 2)                                                                                                                                                                                          |                     |           |                  |          |                                  |

| Interfaces:      | AXI4, AXI4-Stream                                                                                                                                                                                      |                     |           |                  |          |                                  |

| Description:     | The MicroBlaze 32 bit soft processor core, providing an instruc<br>Instruction and Data-side cache with AXI interfaces, Floating-P<br>IP Integrator, to enable export to the Xilinx Software Developme | oint unit (FPU), Me | mory Mana | agement Unit (MM |          |                                  |

4. Double-click on a listed IP to add it to the open BD.

5. Float the IP catalog by clicking the **Float** button <sup>L</sup> at the upper-right corner of the catalog window. Then drag and drop the IP of your choice from the IP catalog in the BD canvas.

**TIP:** Different fields associated with an IP such as Name, Version, Status, License, and Vendor (VLNV) identification can be enabled by right-clicking in the displayed Header column of the IP catalog and enabling and disabling the appropriate fields.

Multiple IP can be added to the BD canvas at once by selecting multiple IP in the IP catalog and using one of the methods described above.

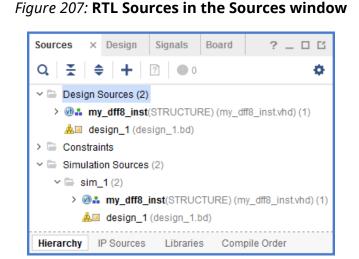

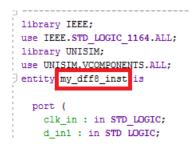

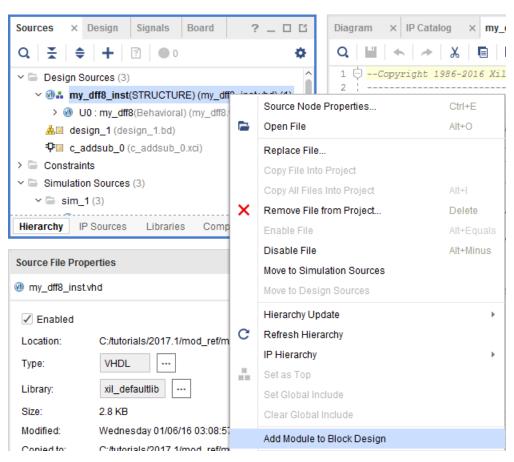

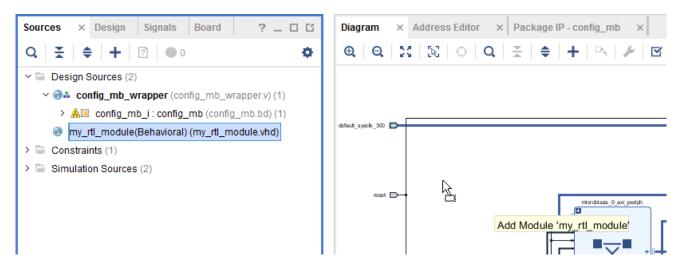

## Adding RTL Modules to the Block Design

Using the *Module Reference* feature of the Vivado IP integrator you can quickly add a module or entity defined in an HDL source file directly into your BD. To add an RTL module, the source file must already be loaded into the project, as described at this link in the Vivado Design Suite User Guide: System-Level Design Entry (UG895).

From within the BD, select the **Add Module** command from either the right-click or the context menu of the design canvas. The Add Module dialog box displays a list of all valid modules defined in the RTL source files that you have previously added to the project.

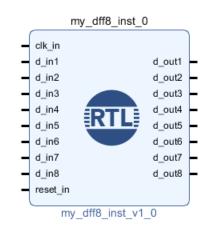

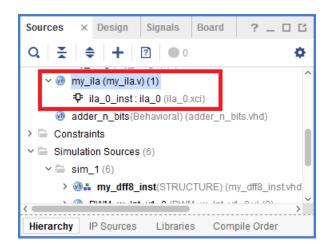

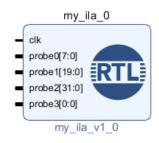

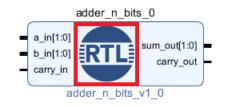

Select one from the list to instantiate it into the BD. The Vivado tools add the module to the BD, and you can make connections to it just as you would with any other IP in the design. The added RTL module displays in the BD with special markings that identify it as an RTL referenced module, as shown in the following figure. This is also referred to as *RTL on Canvas*. See Chapter 14: Referencing RTL Modules, for more information on this feature.

#### Figure 4: Modules Referenced from an RTL Source File

### **Making Connections**

When you create a design in IP integrator, you add blocks to the diagram, configure the blocks as needed, make interface-level or simple-net connections, and add interface or simple ports.

Making connections in IP integrator is designed to be simple. As you move the cursor near an interface or pin connector on an IP block, the cursor changes into a pencil. You can then click an interface or pin connector in an IP block, hold down the left-mouse button, and then draw the connection to the destination block.

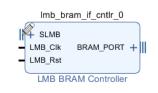

A signal or bus-level connection is shown as a narrow connection line on a symbol. Buses are treated identically to individual signals for connection purposes. An interface-level connection is indicated by a more prominent connection box on a symbol, as shown on the SLMB interface pin in the following figure.

Figure 5: Pins on a Symbol

When you are making connections, a green check mark appears next to any compatible destination connections, highlighting the potential connections for the signal or interface.

#### Figure 6: Signal or Bus Connection on a Symbol

When signals are grouped as an interface, you can quickly connect all of the signals and buses of the interface with other compatible interface pins. The compatible interfaces are also identified by a green check mark. Xilinx<sup>®</sup> provides many interface definitions, including standardized AXI protocols and other industry standard signaling; however, some legacy or custom implementations have unique IP signaling protocols. You can define your own interface and capture the expected set of signals, and ensure that those signals exist between IP. For more information, see this link in *Vivado Design Suite User Guide: Creating and Packaging Custom IP* (UG1118).

### **Connecting Interface Signals**

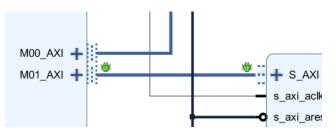

To connect to the individual signals or buses that are part of an interface pin, you can expand the interface pin to display those individual signals. Clicking the + symbol on the interface expands the interface to display its contents.

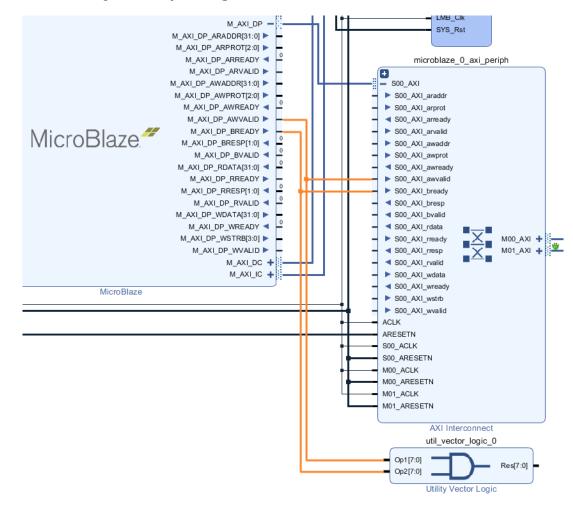

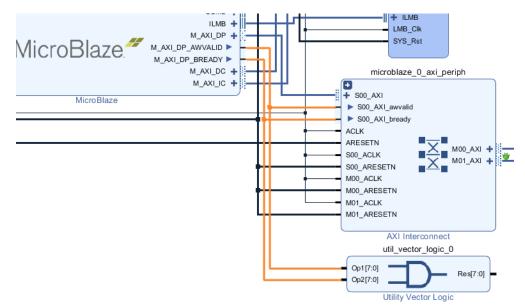

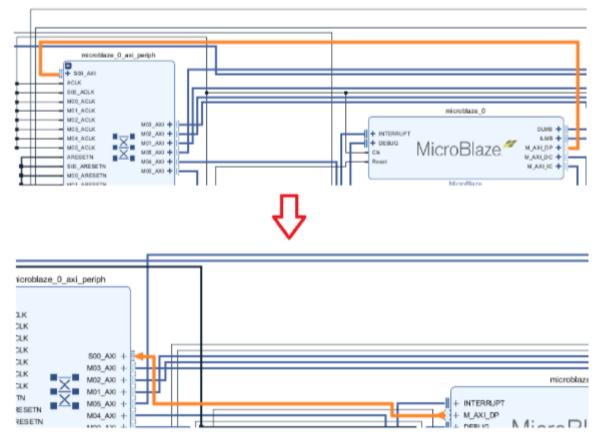

In the following figure, you can see that the interface pin M\_AXI\_DP on the microblaze\_0 instance is connected to the S00\_AXI interface pin on the microblaze\_0\_axi\_periph instance. In addition, two individual signals of the interface (AWVALID and BREADY) are connected to a third instance, util\_vector\_logic\_0, to AND the signals.

When individual signals of an interface are separately connected from the rest of the interface, the signals must include all of the pins needed to complete the connection. In the example shown in the following figure, both the master and slave AXI interface pins are expanded to enable connection to the individual AWVALID and BREADY signals, as well as connecting to the pins of the Utility Vector Logic cell.

**IMPORTANT!** Individually connected interface signals are no longer connected as part of the interface in the BD. The individual signal is essentially removed from the interface. The entire signal must be manually connected.

#### Figure 7: Expanding the Interface to Make a Connection

When connections to an interface pin are overridden by connection to individual signals or bus pins of the interface, the Vivado tool issues a warning similar to the following:

WARNING: [BD 41-1306] The connection to interface pin /microblaze\_0/ $M_AXI_DP_AWVALID$  is being overridden by the user. This pin will not be connected as a part of interface connection  $M_AXI_DP$ .

This warning should be expected because the connection is no longer be included as a part of the interface, and you must manually complete the connection.

After making connections to signals or buses inside of an interface pin, you can collapse the interface to shrink the block and hide the details of the pin. Clicking on the - symbol on an expanded interface pin collapses it to hide its contents.

As seen in the following figure, the separately connected signals or buses of the interface continue to be shown as needed to properly display the connections of the BD.

#### Figure 8: Collapsing the Interface

### **External Connections**

You can connect signals and interfaces to external I/O ports as follows:

- Making Ports External

- Creating Ports

- Creating Interface Ports

The following sections describe these options.

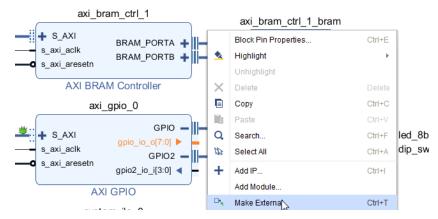

#### **Making Ports External**

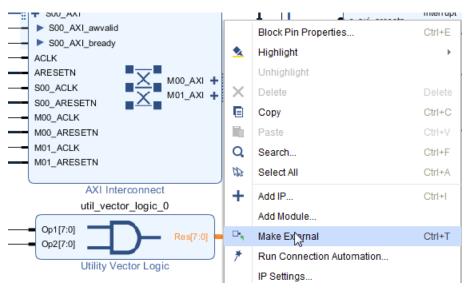

- 1. To connect signals or interfaces to external ports on a diagram, first select a pin, bus, or interface connection, as shown in the following figure.

- 2. Right-click and select Make External.

You can also select **Ctrl + Click** to select multiple pins and invoke the Make External command for all pins at one time.

This command ties a pin on an IP to an I/O port on the BD. IP Integrator connects the port on the IP to an external I/O.

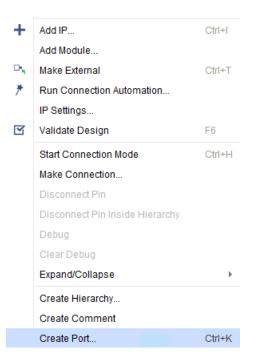

#### **Creating Ports**

1. To use the Create Port option, right-click and select **Create Port**, as shown in the following figure.

This feature is used for connecting individual signals, such as a clock, reset, and uart\_txd. The Create Port option gives you more control in specifying the input and output, the bit-width and the type (for example clk, reset, interrupt, data, and clock enable).

## AMDZI XILINX

The Create Port dialog box opens, as shown in the following figure.

| 🏊 Create Port          |                         |                | ×      |

|------------------------|-------------------------|----------------|--------|

| Create port and conne  | ect it to selected pi   | ins and ports  | 2      |

|                        |                         |                |        |

| Port name:             | CLK                     |                | 8      |

| Direction:             | Input 🗸                 |                |        |

| Туре:                  | Clock                   | ~              |        |

| <u>C</u> reate vector: | from                    | 31 🌲 to        | 0 🌲    |

| Frequency (MHz):       | 100                     |                | 8      |

| Interrupt type:        | • Level                 | ◯ <u>E</u> dge |        |

| Sensitivity:           | <u>A</u> ctive High     | Active Low     |        |

| ✓ Connect to 'CLI      | <u>K</u> ' selected pin |                |        |

| ?                      |                         | ОК             | Cancel |

|                        |                         |                |        |

2. Specify the Port name, the Direction, such as Input, Output or Bidirectional, and the Type (for example Clock, Reset, Interrupt, Data, ClockEnable, or Custom type). For clock ports you must specify a Frequency value in MHz. If you are using the Tcl flow to create the clock port, you must use the -freq\_hz argument to specify a frequency value. If you do not provide a -freq\_hz value, the following warning message appears.

```

WARNING: [BD 5-670] It is required to provide a frequency value for a user created input clock port. Please use the <-freq_hz $freq_val> argument of the create_bd_port command. ie create_bd_port -dir I -type clk -freq_hz 100000000 clkin /my_clock1

```

You can also create a bit-vector by checking the Create vector field and then selecting the appropriate bit-width. You can also specify the Interrupt type and Sensitivity for interrupt pins. Likewise, you can specify the Polarity of the reset ports. Finally, use the Connect to <pin\_name> selected pin check box to connect to an existing pin of a cell in the block design.

#### **Creating Interface Ports**

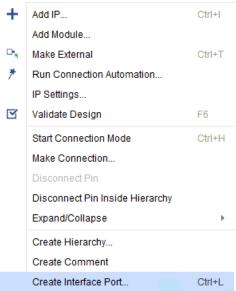

To use the create interface port option:

1. Right-click and select Create Interface Port, as shown in the following figure.

This command creates ports on the interface pins which are groupings of signals that share a common function. The Create Interface Port command gives more control in terms of specifying the interface type and the mode (master/slave).

2. In the Create Interface Port dialog box, shown in the following figure, specify the interface name, the Vendor, Library, Name, and Version (VLNV) field, and the mode field such as MASTER or SLAVE.

## AMD**Z** XILINX

| 🍐 Create Interface    | e Port 🗾                             |  |

|-----------------------|--------------------------------------|--|

| Create interface port | L 👗                                  |  |

|                       | · · ·                                |  |

| Interface name:       | S00_AXI 🙁                            |  |

| VLNV:                 | xilinx.com:interface:aximm_rtl:1.0 v |  |

| <u>M</u> ode:         | SLAVE                                |  |

| ✓ Connect to see      |                                      |  |

| ?                     | MONITOR OK Cancel                    |  |

3. Double-click external ports to see their properties, and modify them.

In the following figure, the port shown is a clock input source, so you can specify different properties, such as frequency, phase, clock domain, any bus interface, the associated clock enable, associated reset and associated asynchronous reset (frequency).

| 🍌 Customize Port       | X                    |

|------------------------|----------------------|

| intf_clock_v1_0 (1.0)  | 4                    |

| Component Name ACLK    | (                    |

| Frequency (MHz)        | 10 🙁                 |

| Phase                  | 0.000                |

| Clk Domain             | ny_ipi_design_ACLK 📀 |

| Associated Busif       |                      |

| Associated Clken       | 0 🙁                  |

| Associated Reset       |                      |

| Associated Async Reset | 0                    |

|                        |                      |

| [                      | OK Cancel            |

4. On an AXI interface, double-click the port to open the port configuration dialog box.

| ximm (1.0)          |                                       | - |

|---------------------|---------------------------------------|---|

| Show disabled ports | Component Name M00_AXI                |   |

|                     | Basic User Signals Advanced           |   |

|                     | Protocol AXI4 ~                       |   |

|                     | Data Width 32 🗸                       |   |

|                     | Addr Width 32 (1 - 64)                |   |

|                     | Max Burst Length 256 (1 - 256)        | I |

|                     | Num Write Outstanding 2 [0 - 32]      |   |

|                     | Num Read Outstanding 2 [0 - 32]       |   |

| const[0:0]          | Supports Narrow Burst [0 - 1]         |   |

|                     | Id Width 0                            |   |

|                     | Read Write Mode                       |   |

|                     | ● READ WRITE ○ READ ONLY ○ WRITE ONLY |   |

|                     | Frequency 10000000                    |   |

|                     | Clk Domain                            |   |

|                     | Phase 0.000                           |   |

|                     |                                       |   |

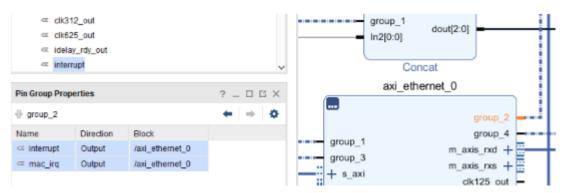

### Handling Interrupts

AMDA XILINX

Interrupt handling depends upon the selected processor.

- For a MicroBlaze<sup>™</sup> processor, the AXI Interrupt Controller IP must be used to manage interrupts.

- For a Zynq<sup>®</sup>-7000 SoC processor or the Zynq MPSoC, the Generic Interrupt Controller block within the Zynq processor handles the interrupt.

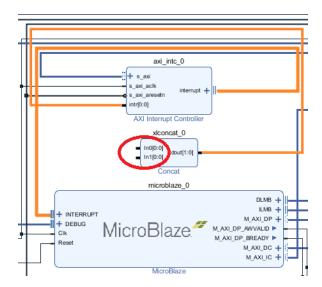

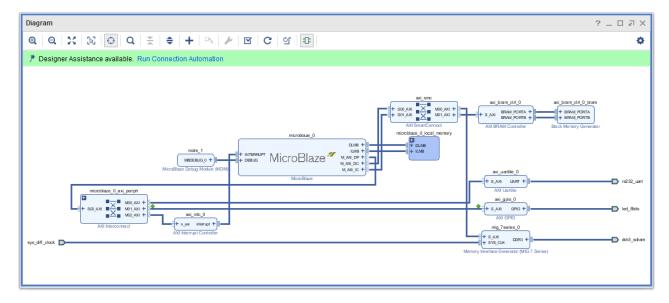

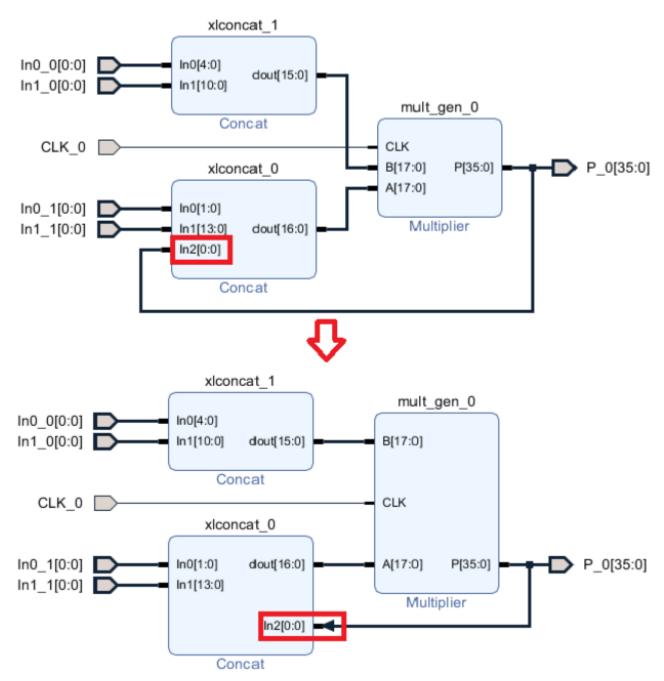

Regardless of the processor used in the design, a Concat IP consolidates and drives the interrupt pins. See the previous Concat section for the brief description provided in this guide.

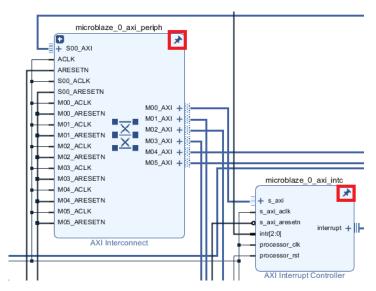

#### *Figure 9:* Concat IP Driving Interrupt Input to AXI Interrupt Controller

The inputs of the Concat IP are driven by different interrupt sources. Accordingly, you must configure the Concat IP to support the appropriate number of input ports. Set the Number of Ports field to the number of interrupt sources in the design, as shown in the following figure.

| 🍌 Re-customize IP              |                                                                                                                                                          |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Concat (2.1)                   | 4                                                                                                                                                        |

| Documentation IP Location      |                                                                                                                                                          |

| Show disabled ports            | Component Name xlconcat_0                                                                                                                                |

|                                | Number of Ports 2 (1 - 32)                                                                                                                               |

|                                | Auto In0 Width 1 [1 - 4096]                                                                                                                              |

|                                | Auto In1 Width 1 [1 - 4096]                                                                                                                              |

| In0[0:0]<br>In1[0:0] dout[1:0] |                                                                                                                                                          |

|                                | Dout Width (Auto)                                                                                                                                        |

|                                | NOTE: The In0 port is connected to the LSB bits of the output, and<br>the In[Number of Ports - 1] input port is connected to the MSB bits of the output. |

|                                | OK Cancel                                                                                                                                                |

Figure 10: Concat Re-Customize IP Dialog Box

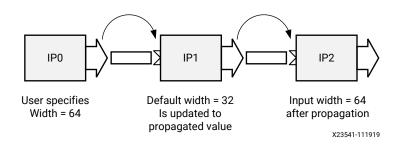

**TIP:** The width of the output (dout) is set automatically during parameter propagation.

You can configure several of the parameters for the AXI Interrupt Controller. The following figure shows the parameters available from the Basic tab of the AXI Interrupt Controller, of which several are configurable.

| 🍌 Re-customize IP                           | × 1                                                             |

|---------------------------------------------|-----------------------------------------------------------------|

| AXI Interrupt Controller (4.1)              | 4                                                               |

| 1 Documentation 📄 IP Location               |                                                                 |

| Show disabled ports                         | Component Name axi_intc_0                                       |

|                                             | Basic Advanced Clocks                                           |

|                                             | Interrupt Usage                                                 |

|                                             | Number of Peripheral Interrupts (Auto)                          |

|                                             | Fast Interrupt Mode                                             |

|                                             | Enable Fast Interrupt Logic                                     |

| + s_axi                                     | Interrupt Vector Address Register reset value (Auto) 0x00000010 |

| - s_axi_aclk<br>• s_axi_aresetn interrupt + | Peripheral Interrupts Type                                      |

| intr[0:0]                                   | Auto Interrupts type - Edge or Level 0xFFFFFFF 0                |

|                                             | Auto Level type - High or Low 0xFFFFFFF 0                       |

|                                             | Auto Edge type - Rising or Falling 0xFFFFFFF 0                  |

|                                             | Processor Interrupt Type and Connection                         |

|                                             | Interrupt type Level Interrupt ~                                |

|                                             | Level type Active High ~                                        |

|                                             | Interrupt Output Connection Bus ~                               |

|                                             |                                                                 |

|                                             | OK Cancel                                                       |

Figure 11: AXI Interrupt Controller Basic Tab Parameters

- The Number of Peripheral Interrupts is set automatically during parameter propagation and cannot be set by a user. The value is determined by the number of interrupt sources that are driving the inputs of the Concat IP.

- The Fast Interrupt Mode can be set by the user if low latency interrupt is desired.

- The Peripheral Interrupts Type is set to Auto, which can be overridden by the user by toggling the Auto setting to Manual. In manual mode, you can specify the custom values in these fields.

- The Processor Interrupt Type field offers two choices:

- 。 Interrupt Type

• Level Type or Edge Type, depending on the Interrupt Type setting.

If the Interrupt Type is Edge Interrupt, the other choice is Edge Type. If the Interrupt Type is Level Interrupt, the other choice is Level Type.

You can select if the interrupt source is either Edge-triggered or Level-triggered. Accordingly, you can then also select whether the interrupt is rising or falling edge and, in case of a Level triggered interrupt, the interrupt is active-High or active-Low.

In IP integrator, this value is normally automatically determined from the connected interrupt signals, but can be set manually.

The following figure shows parameters on the Advanced tab of the AXI Interrupt Controller. See the AXI Interrupt Controller (INTC) LogiCORE IP Product Guide (PG099) for details of these parameters.

| 🔥 Re-customize IP               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ×  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| AXI Interrupt Controller (4.1)  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4  |

| 🚯 Documentation 🛛 📄 IP Location |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Show disabled ports             | Component Name       axi_intc_0         Basic       Advanced       Clocks         Register Usage <ul> <li>Enable Set Interrupt Enable Register</li> <li>Enable Clear Interrupt Enable Register</li> <li>Enable Interrupt Vector Register</li> <li>Enable Interrupt Pending Register</li> <li>Enable Interrupt Level Register</li> <li>Enable Interrupt Level Register</li> <li>Cascade Mode</li> <li>Enable Cascade Interrupt Mode</li> <li>Cascade Mode Master</li> <li>Auto</li> <li>Enable Asynchronous Clock operation</li> </ul> |    |

|                                 | Software Interrupts     Number of Software Interrupts   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -  |

|                                 | OK Canc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | el |

#### Figure 12: Interrupt Controller Advanced Tab

One option of note is the Asynchronous Clocks option. The AXI Interrupt Controller determines whether the interrupt sources in a design are from the same clock domain or different clock domains.

In the case of interrupts being driven from different clock domains, the Vivado IDE uses the Enable Asynchronous Clock operation automatically. In this case, cascading synchronizing registers are added to the interrupt sources.

**TIP:** You can also override the automatic behavior by toggling the Auto button to Manual and setting this option manually.

The Clocks tab lets you specify the Clock Frequencies so constraints can be generated for the Out-of-context (OOC) synthesis flow.

| 🔥 Re-customize IP               | ×                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AXI Interrupt Controller (4.1)  | 4                                                                                                                                                                                                                                                                                                                                                        |

| 🚯 Documentation 🛛 📄 IP Location |                                                                                                                                                                                                                                                                                                                                                          |

| Show disabled ports             | Basic       Advanced       Clocks         Enter the target frequency for the input clock(s) for the IP.       These frequencies will be used during the default out-of-context synthesis flow         s_axi_aclk frequency (MHz)       100.0       Image: Clock synthesis         processor_clk frequency (MHz)       100.0       Image: Clock synthesis |

|                                 | OK Cancel                                                                                                                                                                                                                                                                                                                                                |

#### Figure 13: Interrupt Controller Clocks Tab

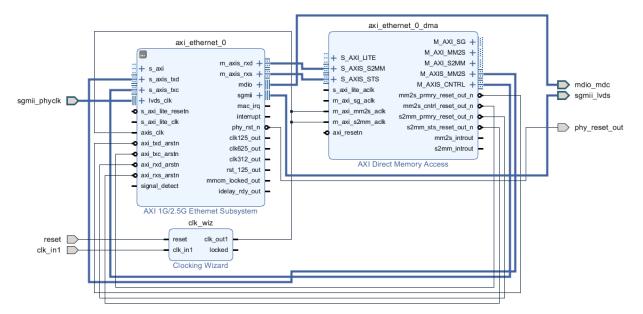

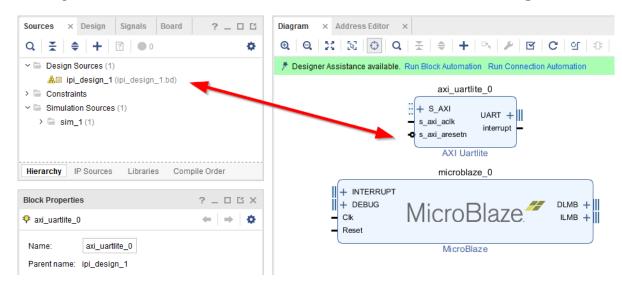

### Using the Designer Assistance Feature

IP integrator offers a feature called Designer Assistance, which includes *Block Automation* and *Connection Automation*, to assist you in putting together a basic IP sub-system by making internal connections between different blocks and making connections to external interfaces. The Block Automation Feature is provided when an embedded processor such as the Zynq-7000 Processor System 7 (ZYNQPS7), a Zynq MPSoC (Zynq\_ultra\_ps\_e\_0), a MicroBlaze processor, or some other hierarchical IP such as an Ethernet is instantiated in the IP integrator BD.

#### **Using Block Automation**

🙏 Run Block Automation

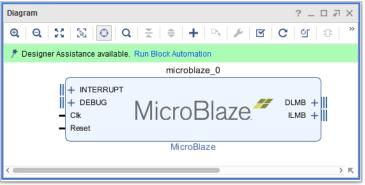

Designer assistance can help you put together a simple MicroBlaze system. To use this feature:

1. Click the **Run Block Automation** link in the banner of the design canvas, as shown in the following figure.

The Run Block Automation dialog box opens, as shown in the following figure.

2. Provide input about basic features that the microprocessor system needs.

| <b>₹</b>   <b>♦</b>                                       | Description                                         |                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ✓ ✓ All Automation (1 out of 1 selected) ✓ ▼ microblaze_0 | caches can be configur<br>Interrupt Controller, a c | automation generates local memory of selected size, and<br>red. MicroBlaze Debug Module, Peripheral AXI interconnect,<br>lock source, Processor System Reset are also added and<br>A preset MicroBlaze configuration can also be selected.<br>0 |

|                                                           | Preset                                              | None 🗸                                                                                                                                                                                                                                          |

|                                                           | Local Memory:                                       | 8KB ~                                                                                                                                                                                                                                           |

|                                                           | Local Memory ECC:                                   | None 🗸                                                                                                                                                                                                                                          |

|                                                           | Cache Configuration:                                | None 🗸                                                                                                                                                                                                                                          |

|                                                           | Debug Module:                                       | Debug O 🗸                                                                                                                                                                                                                                       |

|                                                           | Peripher <u>a</u> l AXI Port                        | Enabled ~                                                                                                                                                                                                                                       |

|                                                           | Interrupt Controller:                               |                                                                                                                                                                                                                                                 |

|                                                           | Clock Connection:                                   | New Clocking Wizard (100 M V                                                                                                                                                                                                                    |

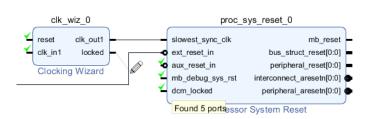

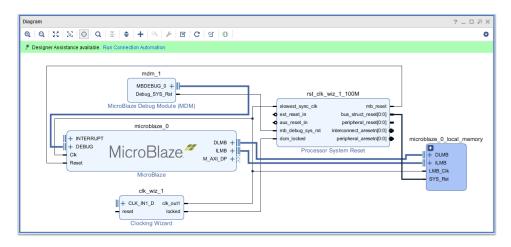

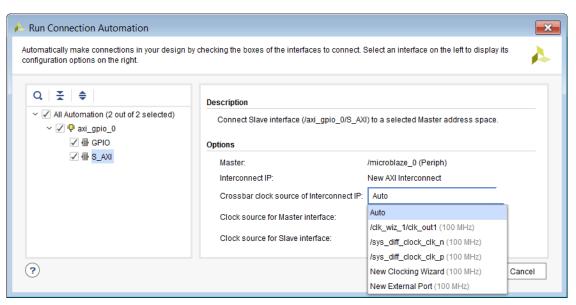

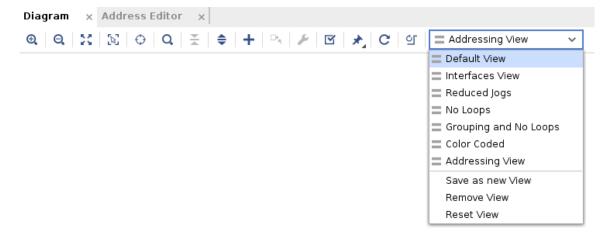

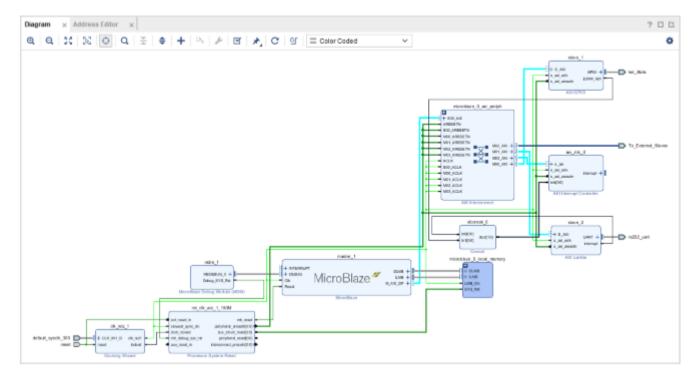

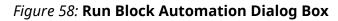

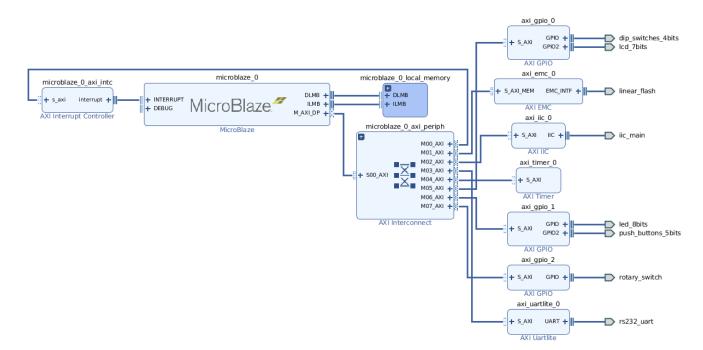

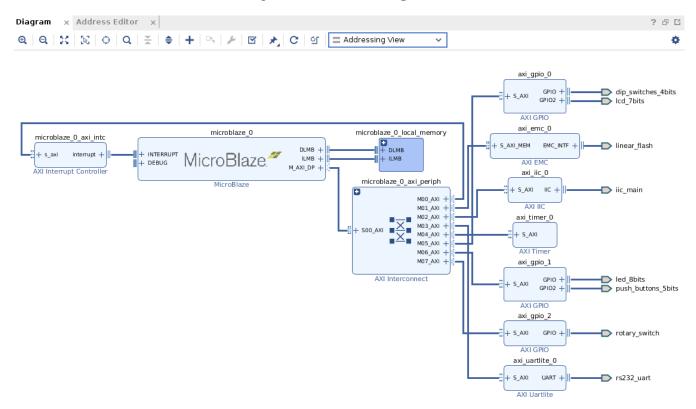

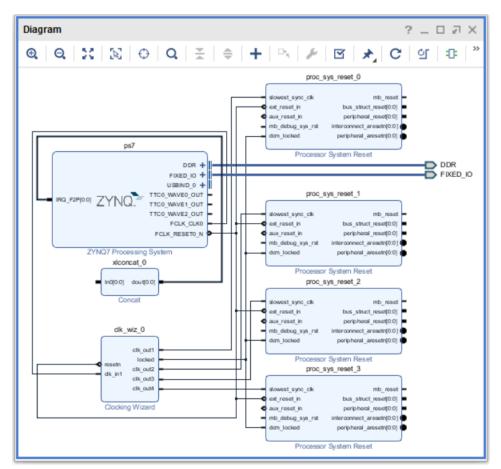

After you specify the necessary options, the Block Automation feature automatically creates a basic system, as shown in the following figure.

For example, the MicroBlaze System shown in the following figure consists of the following:

- A MicroBlaze Debug Module

- A hierarchical block called the microblaze\_1\_local\_memory that has the Local Memory Bus, the Local Memory Bus Controller and the Block Memory Generator

- A Clocking Wizard

- An AXI Interconnect

- An AXI Interrupt Controller

#### **Using Connection Automation**

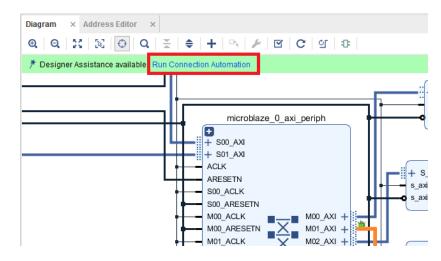

Because the design is not connected to any external I/O at this point, IP integrator offers the Connection Automation feature as shown in the light green banner of the design canvas in the preceding figure. When you click Run Connection Automation, IP integrator provides assistance in connecting interfaces and/or ports to external I/O ports.

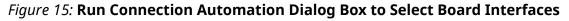

The Run Connection Automation dialog box, shown in the following figure, lists the ports and interfaces that the Connection Automation feature supports, along with a brief description of the available automation, and available options for each automation.

Figure 14: Ports and Interfaces That Can Use Connection Automation

| Aun Connection Automation                                                                                                  |                                                                                        | ×  |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----|

| Automatically make connections in your design<br>display its configuration options on the right.                           | by checking the boxes of the interfaces to connect. Select an interface on the left to | 4  |

| Q   素   ≑                                                                                                                  | Description                                                                            |    |

| <ul> <li>✓ All Automation (3 out of 3 selected)</li> <li>✓ ♥ ¢k_wiz_1</li> <li>✓ ⊕ CLK_IN1_D</li> <li>✓ ☞ reset</li> </ul> | Connect Board Part Interface to IP interface.<br>Interface: /clk_wiz_1/CLK_IN1_D       |    |

| <ul> <li>✓ Preset</li> <li>✓ ✓ Prst_dk_wiz_1_100M</li> <li>✓ ≫ ext_reset_in</li> </ul>                                     | Options Select Board Part Interface: sys_diff_clock (System differential clock)        |    |

| •                                                                                                                          | OK                                                                                     | el |

For Xilinx Target Reference Platforms or evaluation boards, IP integrator has knowledge of the FPGA pins that are used on the target boards; this is called *Board Awareness*. Based on that information, the IP integrator connection automation feature can assist you in tying the ports in the design to external ports on the board. IP integrator then creates the appropriate physical constraints and other I/O constraints required for the I/O port in question.

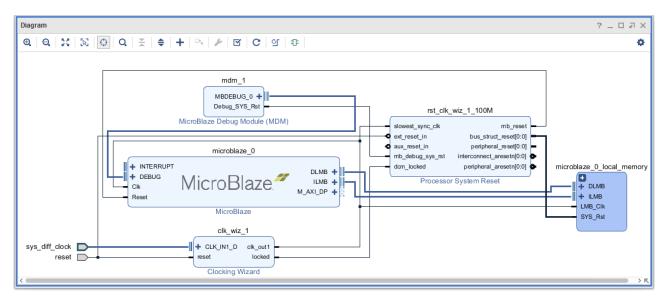

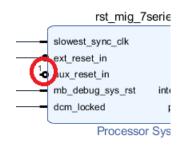

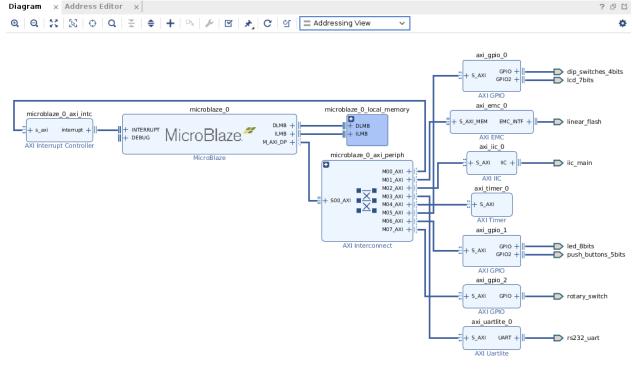

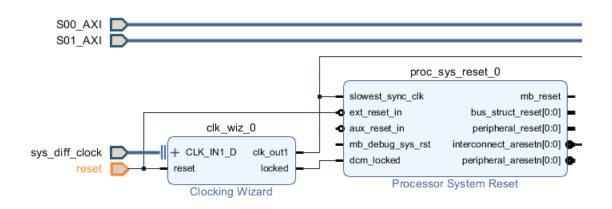

In the MicroBlaze system design shown above, the following connections need to be made:

- Processor System Reset IP needs to be connected to an external reset port.

- Clocking Wizard needs to be connected to an external clock source as well as an external reset.

By selecting the appropriate options, as shown in the following figure, you can tie the clock and the reset ports to the appropriate sources on the target board.

| Run Connection Automation<br>Automatically make connections in your design<br>display its configuration options on the right.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | by checking the boxes of the interfaces to connect. Select an interface on the left to                                                                                                                                        | ×      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Q       ★       ♦         ~        All Automation (3 out of 3 selected)         ~        ✓       ♦         O       ●       CLK_IN1_D         Ø       ●       CLK_IN1_D         Ø       ●       reset         >       Ø       ●         ext_reset_in       Ø       ●         3       ●       •         Image: Second Sec | Description         Connect Board Part Interface to IP interface.         Interface: /rst_clk_wiz_1_100M/ext_reset_in         Options         Select Board Part Interface:         reset (FPGA Reset)         Custom    OK Ca | ↓<br>↓ |

You can select the reset pin that already exists on the KC705 target board in this case, or you can specify a custom reset pin for your design. After the reset is specified, the reset pin is tied to the <code>ext\_reset\_in</code> pin of the <code>Proc\_Sys\_Rst</code> IP and the clock is connected to the on-board 200 MHz clock source called <code>sys\_diff\_clock</code>.

Figure 16: Connecting the Reset Pin to the Board Reset Pin

The Designer Assistance feature is constantly monitoring your design development in IP integrator.

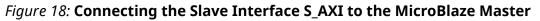

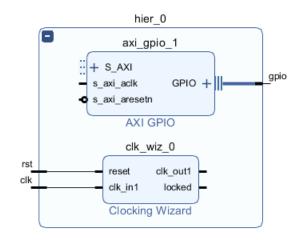

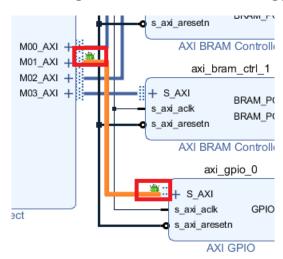

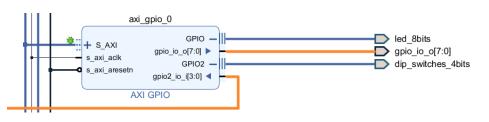

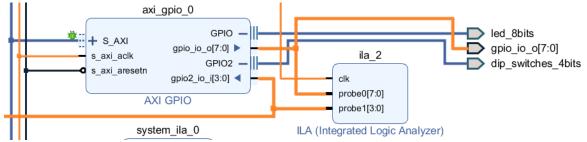

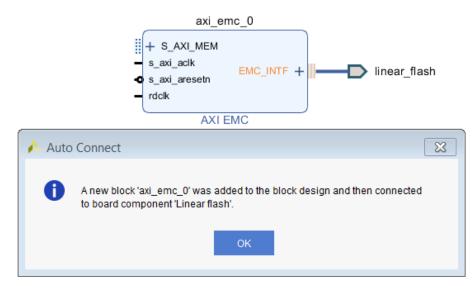

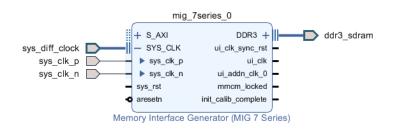

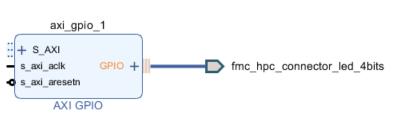

For example, assume that you instantiate the  $AXI_GPIO$  IP into the design. The Run Connection Automation link reappears in the banner on top of the design canvas. You can then click Run Connection Automation and the  $S_AXI$  port of the newly added AXI GPIO can be connected to the MicroBlaze processor using the AXI Interconnect.

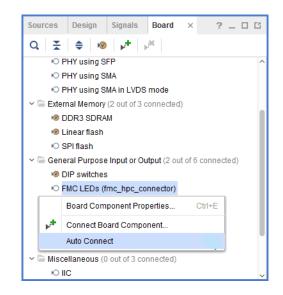

Likewise, the GPIO interface can be tied to one of the several interfaces present on the target board as in the following figure.

| Run Connection Automation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                       |                                                                                                                                                   | ×        |

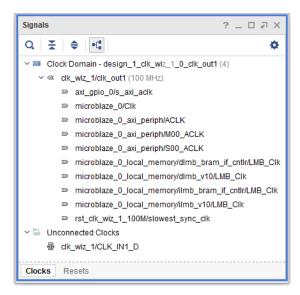

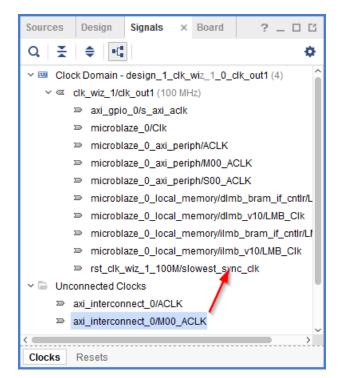

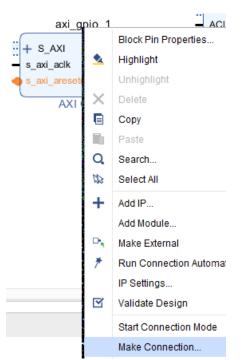

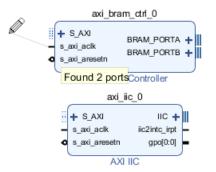

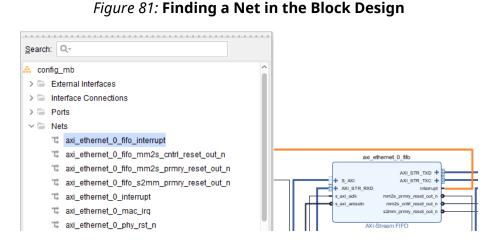

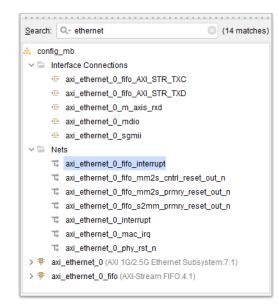

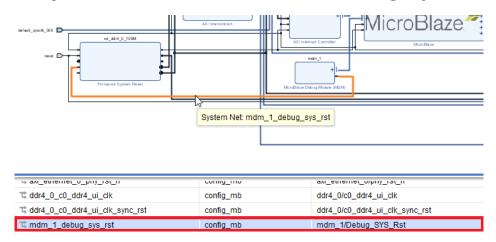

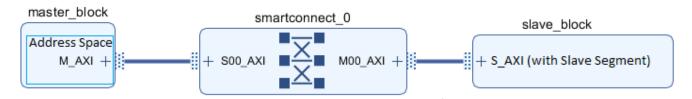

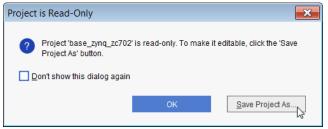

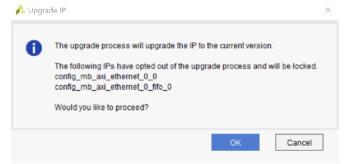

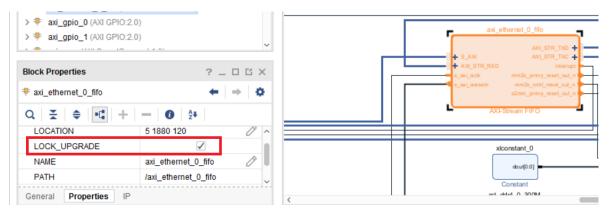

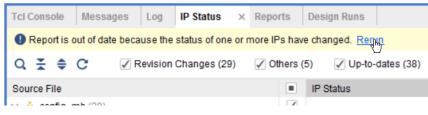

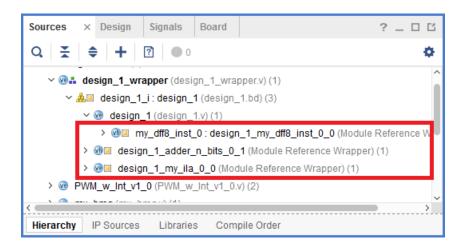

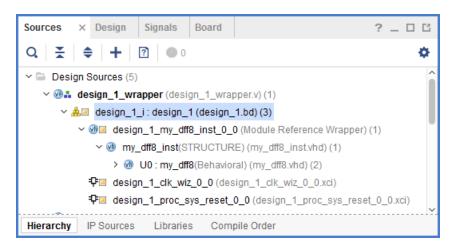

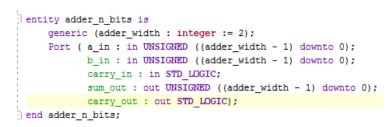

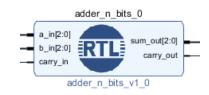

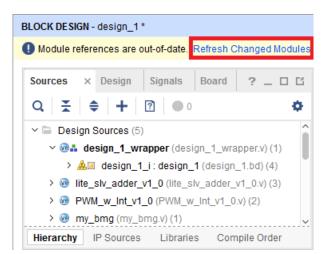

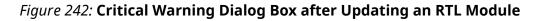

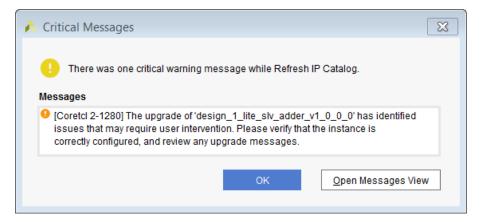

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|