# Vivado Design Suite Tutorial

### Design Analysis and Closure Techniques

vivado-design-suite

UG938 (v2022.2) November 2, 2022

## **Table of Contents**

| Tutorial Overview                                                   | 4  |

|---------------------------------------------------------------------|----|

| Navigating Content by Design Process                                | ∠  |

| Introduction                                                        | ∠  |

| Tutorial Description                                                | ∠  |

| Software Requirements                                               | 5  |

| Locating Tutorial Design Files                                      | 5  |

|                                                                     |    |

| Lab 1: Setting Waivers with the Vivado IDE                          |    |

| Introduction                                                        |    |

| Step 1: Starting the Vivado IDE                                     |    |

| Step 2: Generating the CDC Report                                   |    |

| Step 3: Waiving a Single CDC Violation                              | 8  |

| Step 4: Generating a Report for Waived Violations                   | 12 |

| Step 5: Generating a Text Report with Details for Waived Violations | 13 |

| Step 6: Waiving Multiple CDC Violations                             | 14 |

| Step 7: Exporting Waivers                                           | 17 |

| Step 8: Using the create_waiver Command                             | 18 |

| Step 9: Waiving Multiple CDC Violations                             | 19 |

| Step 10: Waiving Multiple DRC Violations                            | 21 |

| Step 11: Generating a Summary Report for Waived Violations          | 26 |

| Step 12: Using Waiver Commands                                      | 29 |

| Summary                                                             | 30 |

| ·                                                                   |    |

| Lab 2: Using Report QoR Suggestions and Report QoR                  |    |

| Assessment for Timing Closure                                       | 31 |

| Introduction                                                        |    |

| Step 1: Understanding the Design                                    | 32 |

| Step 2: Running Report QoR Assessment                               | 34 |

| Step 3: Running Report QoR Suggestions                              |    |

| Step 4: Understanding the Report                                    |    |

| Step 5: Run with Suggestions                                        |    |

| Step 6: Accumulating Suggestions                                    |    |

| Step 7: Automatically Running QoR Suggestions      | 49 |

|----------------------------------------------------|----|

| Summary                                            | 51 |

| Lab 3: Running ML Strategies                       | 53 |

| Introduction                                       |    |

| Step 1: Generating an ML Strategy RQS File         |    |

| Step 2: Creating ML Strategy Runs                  |    |

| Summary                                            |    |

| Lab 4: Intelligent Design Runs                     | 58 |

| Introduction                                       |    |

| Step 1: Creating Intelligent Design Runs           |    |

| Step 2: Navigating Intelligent Design Runs         | 61 |

| Step 3: Analyzing the Reports and Log File         | 64 |

| Step 4: Final Analysis                             | 67 |

| Summary                                            |    |

| Appendix A: Additional Resources and Legal Notices | 70 |

| Revision History                                   |    |

| Please Read: Important Legal Notices               |    |

### **Tutorial Overview**

### **Navigating Content by Design Process**

Xilinx® documentation is organized around a set of standard design processes to help you find relevant content for your current development task. All Versal® ACAP design process Design Hubs and the Design Flow Assistant materials can be found on the Xilinx.com website. This document covers the following design processes:

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, functional simulation, and evaluating the Vivado® timing, resource use, and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Lab 2: Using Report QoR Suggestions and Report QoR Assessment for Timing Closure

- Lab 3: Running ML Strategies

- Lab 4: Intelligent Design Runs

### Introduction

This tutorial uses the Vivado® design rules checker (report\_drc), clock domain crossing checker (report\_cdc), and quality of results enhancer (report\_qor\_suggestions) to analyze example designs for issues, and shows you how to take corrective actions. It also outlines how to run ML strategies and Intelligent Design Runs (IDRs).

### **Tutorial Description**

Lab 1 walks you through creating waivers for CDC, methodology, and DRC violations.

Lab 2 is a guide to using the report\_qor\_suggestions (RQS) command.

**Note:** The designs used in this tutorial are intended to exhibit issues for demonstration purposes, and should not be used as a reference for designs outside this tutorial.

### **Software Requirements**

This tutorial requires that the 2021.1 Vivado® Design Suite software release or later is installed.

For a complete list of system and software requirements, see the Vivado Design Suite User Guide: Release Notes, Installation, and Licensing (UG973).

### **Locating Tutorial Design Files**

- 1. Download the reference design files from the Xilinx® website.

- 2. Extract the ZIP file contents into any write-accessible location.

This tutorial refers to the location of the extracted ZIP file contents as <Extract\_Dir>.

Lab 1

## Setting Waivers with the Vivado IDE

#### Introduction

In the Vivado® Design Suite, you can use the waiver mechanism to waive clock domain crossing (CDC), design rule check (DRC), or methodology check violations. After a violation is waived, it is no longer reported by the report\_cdc, report\_drc, or report\_methodology commands. Waived checks are also filtered out from the mandatory DRCs run at the start of the implementation commands, such as opt\_design, place\_design, and route\_design. For more information, see this link in the Vivado Design Suite User Guide: Design Analysis and Closure Techniques (UG906).

**IMPORTANT!** The content of the waiver is built with the objects that exist when the waiver is created. However, if an instance referenced inside a waiver is replicated by Vivado<sup>®</sup>, the replicated instance is automatically added to the waiver and saved in subsequent checkpoints and XDC.

This lab shows how to set waivers with the Vivado integrated design environment (IDE) using both menu commands and the Tcl Console. The lab focuses on CDC waivers, but the methods for waiving DRC and methodology violations are similar.

### **Step 1: Starting the Vivado IDE**

This lab uses a Vivado design checkpoint ( .dep file), which is a snapshot of a design. When you launch the Vivado IDE using a design checkpoint, a subset of the Vivado IDE functionality is available.

TIP: To launch the Vivado Tcl Shell on Windows, select Start  $\rightarrow$  All Programs  $\rightarrow$  Xilinx Design Tools  $\rightarrow$  Vivado <version>  $\rightarrow$  Vivado <version> Tcl Shell.

1. From the command line or the Vivado Tcl Shell, change to the directory where the lab materials are stored:

```

cd <Extract_Dir>/Lab1

```

2. To start the Vivado IDE with the design checkpoint loaded, enter the following:

```

vivado my_ip_example_design_placed.dcp

```

**TIP:** You can disregard the critical warnings about the unbounded GT locations.

### **Step 2: Generating the CDC Report**

In this step, you generate the CDC report to view the associated CDC violations.

- 1. Select Reports → Timing → Report CDC.

- 2. In the Report CDC dialog box, leave the default settings as-is, and click **OK**.

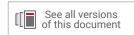

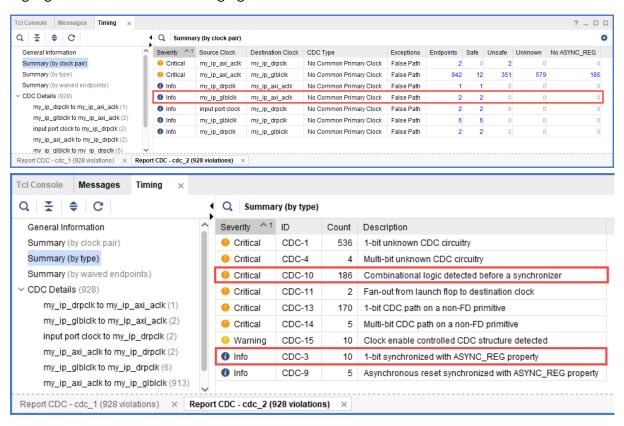

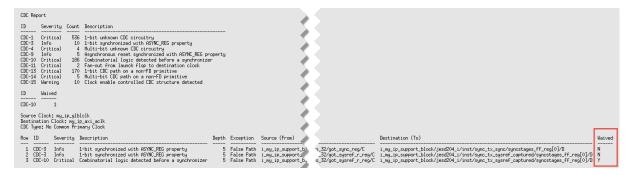

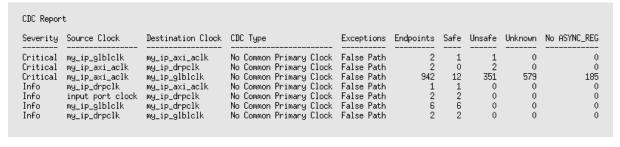

The Summary (by clock pair) section of the CDC Report appears as follows.

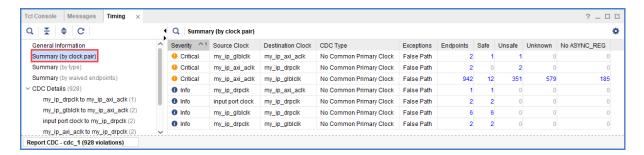

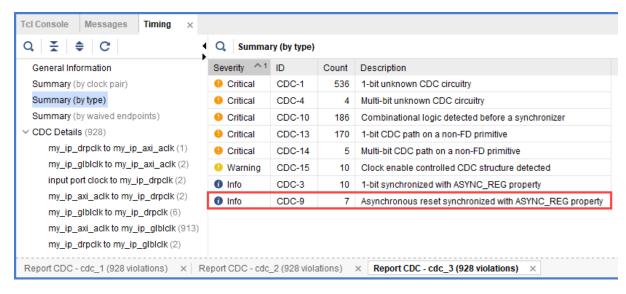

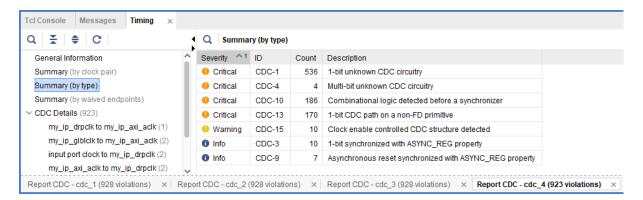

The Summary (by CDC type) section appears as follows.

### Step 3: Waiving a Single CDC Violation

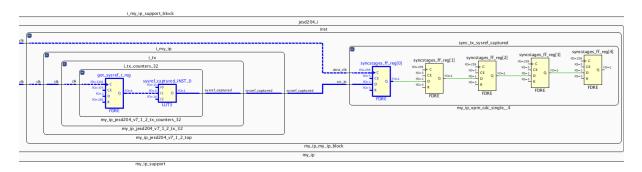

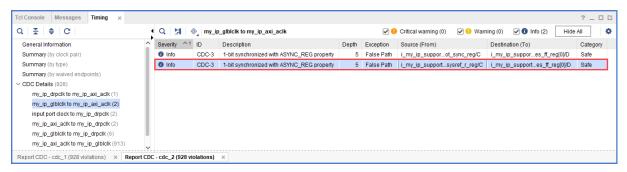

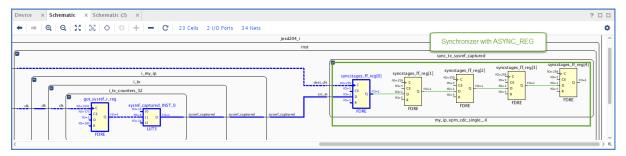

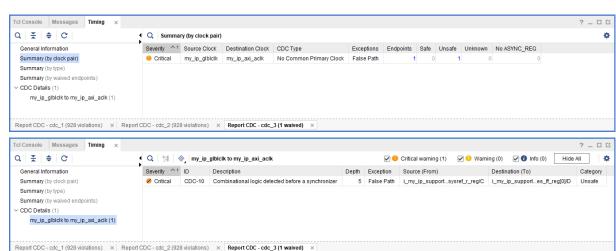

The  $my_{ip_glblclk}$  to  $my_{ip_axi_aclk}$  clock pair includes one Critical CDC-10 violation due to combinational logic on the CDC path. This step covers how to waive the CDC-10 violation.

To view a schematic of the violation, select the CDC-10 row in the CDC Report, and click the Schematic toolbar button .

**Note:** Alternatively, you can press **F4** to generate the schematic. However, using the toolbar button provides a more detailed schematic that includes all the levels of the downstream synchronizer.

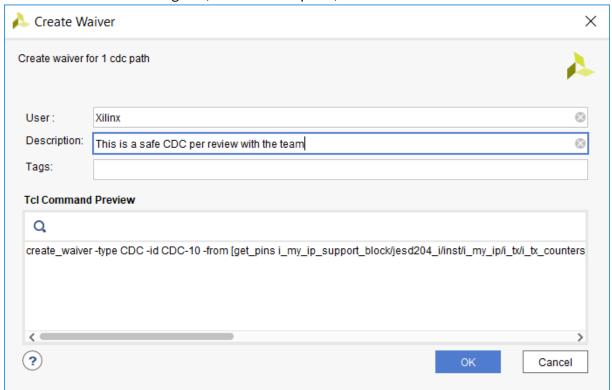

- 2. To waive the violation, select the **CDC-10** row in the CDC Report, right-click, and select **Create Waiver**.

- 3. In the Create Waiver dialog box, enter a description, and click **OK**.

**IMPORTANT!** A waiver tracks the date the waiver was added, the user that added the waiver, and a description of why the violation was waived. The date is automatically added by the system. The Tags field is an optional description or list of keywords that can be used for documentation purposes.

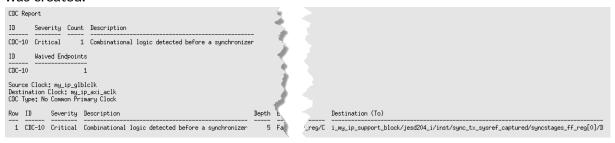

4. After the waiver is created, check the CDC Report.

To indicate that a waiver was created, the CDC-10 row is gray and disabled.

Note: Rows are only disabled in the Report CDC result window from which the waivers were created.

To see the impact of the CDC-10 waiver, select Reports → Timing → Report CDC to rerun Report CDC.

**Note:** When a waiver is created or deleted, you must rerun Report CDC, Report DRC, or Report Methodology to see the updated results.

6. See the CDC Report to view the updated information.

The differences from the previous Summary by clock pair and Summary by type sections are highlighted in red in the following figures.

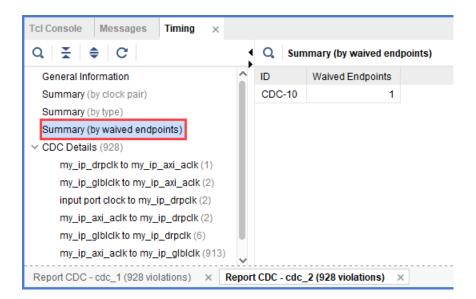

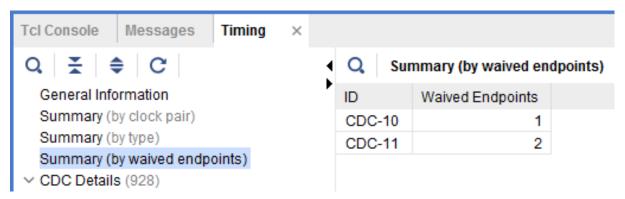

You can also view a summary with the list of waived endpoints.

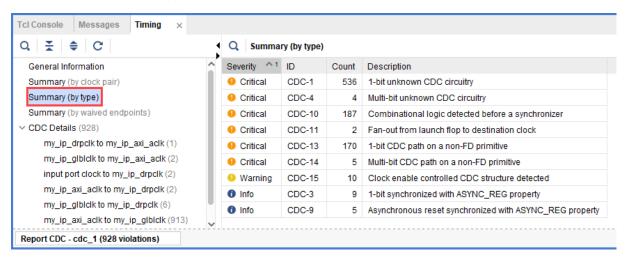

The detailed section for the  $my_{ip_glblclk}$  to  $my_{ip_axi_aclk}$  CDC shows that the Critical CDC-10 was replaced with an Info CDC-3.

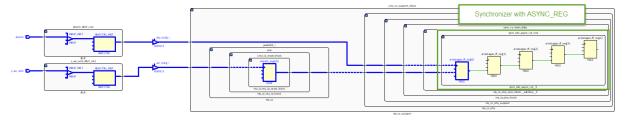

7. Select the new CDC-3 row, and click the Schematic toolbar button <sup>1</sup> . If F4 is used to open the schematic, double-click the Q pin of the output register to expand the schematic to match what is shown in the following figure.

The CDC path includes a 5-level synchronizer on the output of the selected destination register. This is the reason the CDC-10 was replaced with CDC-3 for this topology, as shown in the following figure.

**IMPORTANT!** By default, Report CDC only reports a single violation per endpoint and per clock pair. When multiple violations apply to the same endpoint, only the violation with the highest precedence is reported. Because CDC-10 has a higher precedence than CDC-3, only CDC-10 is reported when both CDC-10 and CDC-3 apply to the same endpoint. For more information on CDC rules precedence, see this link in the Vivado Design Suite User Guide: Design Analysis and Closure Techniques (UG906).

**TIP:** To report all of the CDC violations for each endpoint regardless of the precedence rules, use the command line option  $-all\_checks\_per\_endpoint$ . However, unsafe rules are not reported on a register if at least one safe rule on the same register is detected.

# Step 4: Generating a Report for Waived Violations

You can generate a report for the CDC, DRC, or methodology check violations that were waived. This step shows how to generate a report for waived CDC violations using the Tcl Console as well as the Vivado IDE menu commands.

#### **Generating a Text Report for Waived Violations**

1. In the Tcl Console, enter:

report\_cdc -waived

2. In the CDC report, verify that a single CDC-10 violation is listed, because only one waiver was created.

# Generating a Vivado IDE CDC Report for Waived Violations

- 1. Select Reports → Timing → Report CDC.

- 2. In the Report CDC dialog box, enable **Report only waived paths**, and click **OK**.

- 3. In the CDC Report, check the Summary (by clock pair) and CDC Details to verify that a single CDC-10 violation is listed.

**Note:** The icon next to the violation shows that the violation was waived **8**.

# Step 5: Generating a Text Report with Details for Waived Violations

In this step, you generate text reports with additional details, including a list of all of the rules and all of the violations regardless of the waivers.

### Generating a List of Rules with Waived Violations

1. In the Tcl Console, enter:

```

report_cdc -details -show_waiver

```

2. Verify that the my\_ip\_glblclk to my\_ip\_axi\_aclk CDC-10 violation is waived and the two CDC-3 violations are not waived.

**Note:** In the text report, all of the rules are reported, whether they were waived or not. The Waived column indicates the status of the rule.

# Generating a List of All Violations Regardless of the Waivers

1. In the Tcl Console, enter:

report\_cdc -no\_waiver

2. In the text report, verify that the table matches the original report from Report CDC before the CDC-10 waiver was created.

**TIP:** You can also generate a list of all violations regardless of the waivers from the Vivado IDE. Select **Reports**  $\rightarrow$  **Timing**  $\rightarrow$  **Report CDC**. In the Report CDC dialog box, enable **Ignore all waivers**, and click **OK**.

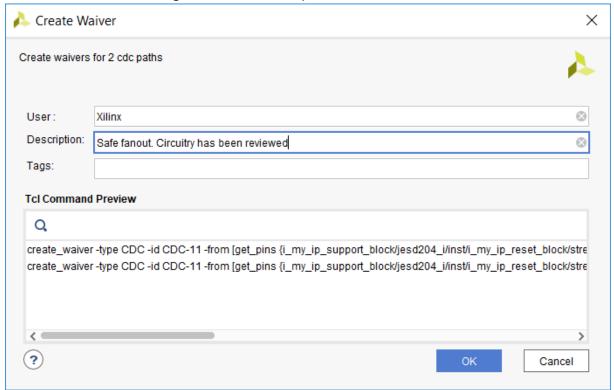

### **Step 6: Waiving Multiple CDC Violations**

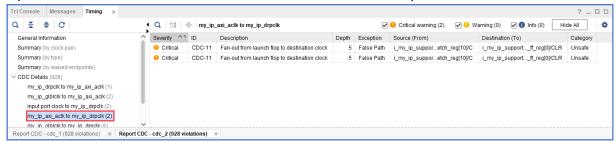

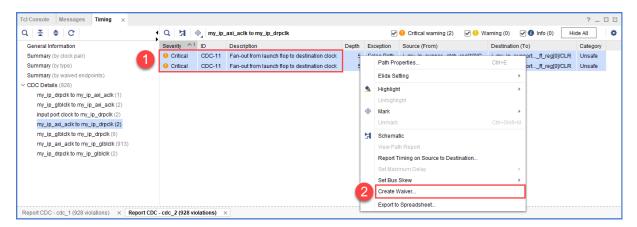

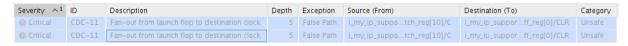

The my\_ip\_axi\_aclk to my\_ip\_drpclk CDC includes two Critical CDC-11 violations. This step covers how to waive both CDC-11 violations simultaneously.

1. To waive the violations, select the **CDC-11** rows in the CDC Report, right-click, and select **Create Waiver**.

2. In the Create Waiver dialog box, enter a description, and click **OK**.

In the Timing Report, the two selected rows are disabled when the waivers are created.

Note: One waiver is created for each selected row. In this example, two waivers are created.

- 3. Select Reports → Timing → Report CDC to rerun Report CDC. In the Report CDC dialog box, make sure that Report only waived paths is unchecked, and click OK.

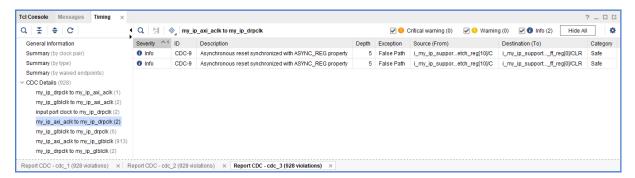

- 4. In the CDC Report, look at the my\_ip\_axi\_aclk to my\_ip\_drpclk CDC.

The two Critical CDC-11 violations were replaced with two Info CDC-9 violations. Based on the CDC precedence rules, waiving CDC-11 unmasks CDC-9 for this circuit.

- 5. To view a schematic of the violation, select the CDC-9 row in the CDC Report, and click the Schematic toolbar button

- 6. Verify that there is a 5-level synchronizer on the destination clock domain.

7. Compare the new Summary (by type) information with the information from the previous CDC Report.

In the updated CDC Report, the two CDC-11 violations are no longer listed. Instead, there are two new CDC-9 violations.

8. Look at the Summary (by waived endpoints) information.

In the updated CDC Report, there are three waived endpoints. This number is different from the number of waived violations (2), because CDC-11 is a multi-bit violation.

9. Generate different text reports and compare the results with previous reports.

For example, you can run the following Tcl commands:

```

report_cdc -details

report_cdc -details -waived

report_cdc -details -show_waiver

report_cdc -details -no_waiver

```

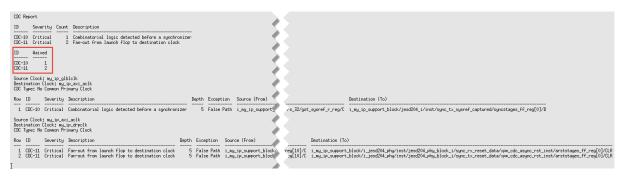

The following report was generated using the report\_cdc -details -waived Tcl command and shows that three violations were waived.

### **Step 7: Exporting Waivers**

In this step, you export waivers with the write\_waivers Tcl command.

Note: The XDC output file can be imported using the read\_xdc or source Tcl commands.

1. To export the CDC waivers, enter: write\_waivers -type cdc waivers.xdc.

**TIP:** Alternatively, because there are no DRC or methodology waivers, you can enter:

write\_waivers waivers.xdcorwrite\_xdc -type waiver waivers.xdc.

2. Open the waivers.xdc file to view the three waivers.

**Note:** The following example is reformatted to better show the different command line options.

```

create_waiver -type CDC -id {CDC-10} -user "Xilinx" \

-desc "This is a safe CDC per review with the team"

-from [get_pins i_my_ip_support_block/jesd204_i/inst/i_my_ip/i_tx/

i_tx_counters_32/got_sysref_r_reg/C] \

-to [get_pins {i_my_ip_support_block/jesd204_i/inst/

sync\_tx\_sysref\_captured/syncstages\_ff\_reg[0]/D\}] \  \  \, \backslash

-timestamp "<timestamp>" ;#1

create_waiver -type CDC -id {CDC-11} -user "Xilinx" \

-desc "Safe fanout. Circuitry has been released"

-from [get_pins {i_my_ip_support_block/jesd204_i/inst/

i_my_ip_reset_block/stretch_reg[10]/C}] \

-to [get_pins {i_my_ip_support_block/i_jesd204_phy/inst/

jesd204_phy_block_i/sync_rx_reset_data/xpm_cdc_async_rst_inst/

arststages_ff_reg[0]/CLR}] \

-timestamp "<timestamp>" ;#1

create_waiver -type CDC -id {CDC-11} -user "Xilinx" \

-desc "Safe fanout. Circuitry has been released" \

-from [get_pins {i_my_ip_support_block/jesd204_i/inst/

i_my_ip_reset_block/stretch_reg[10]/C}] \

-to [get_pins {i_my_ip_support_block/i_jesd204_phy/inst/

jesd204_phy_block_i/sync_tx_reset_data/xpm_cdc_async_rst_inst/

arststages_ff_reg[0]/CLR}] \

-timestamp "<timestamp>" ;#2

```

### Step 8: Using the create\_waiver Command

Waivers added from the Report CDC dialog box are created using the create\_waiver command. You can view these commands as follows.

**Note:** You can use the <code>create\_waiver</code> command line command for CDC, DRC, and methodology waivers. The options differ slightly depending on whether you are creating a CDC, DRC, or methodology waiver. For more information, including information on the different options, see the <code>create\_waiver</code> command in the <code>Vivado Design Suite Tcl Command Reference Guide</code> (UG835).

- 1. Open the Vivado journal file (vivado.jou) to see the three distinct create\_waiver commands issued by the Vivado IDE.

- 2. Scroll through the history of the Tcl Console to see the same three <code>create\_waiver</code> commands.

**TIP:** The  $-f_{TOM}$  and  $-t_O$  options are used to specify the startpoints and endpoints. When a waiver is set from the Report CDC dialog box, both  $-f_{TOM}$  and  $-t_O$  are specified to match the exact violation. However, you can specify a CDC waiver using only the  $-f_{TOM}$  option or only the  $-t_O$  option, but more paths might be waived than expected.

### Step 9: Waiving Multiple CDC Violations

In this step, you waive multiple CDC violations simultaneously.

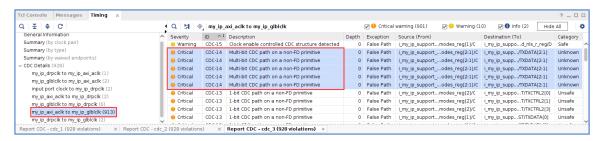

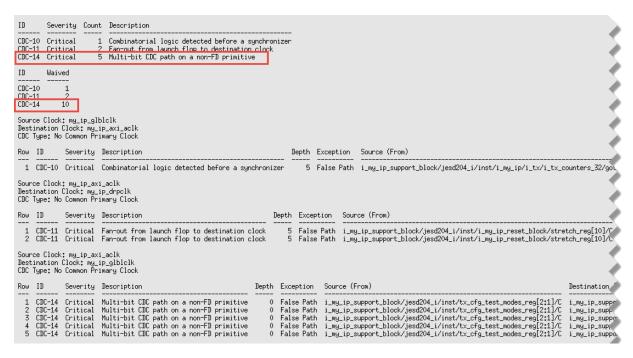

1. In the CDC Report, view the my\_ip\_axi\_aclk to my\_ip\_glblclk CDC under CDC Details.

This crossing has five CDC-14 violations, which are multi-bit violations. The five CDC-14 violations all start from the same two register clock pins:

i\_my\_ip\_support\_block/jesd204\_i/inst/tx\_cfg\_test\_modes\_reg[2:1]/C

**TIP:** You can sort the table by the column ID to more easily see the five CDC-14 violations.

2. Because i\_my\_ip\_support\_block/jesd204\_i/inst/

tx\_cfg\_test\_modes\_reg[\*]/C matches five pins and you only need to target two of those five pins, construct the list of startpoints as follows:

```

set startpoints [list \

[get_pins i_my_ip_support_block/jesd204_i/inst/

tx_cfg_test_modes_reg[1]/C] \

[get_pins i_my_ip_support_block/jesd204_i/inst/

tx_cfg_test_modes_reg[2]/C] \

]

```

To waive the five CDC-14 violations, use the create\_waiver Tcl command with the -from option:

```

\label{local-condition} $$\operatorname{create\_waiver}$ -type $$\{CDC\}$ -id $$\{CDC-14\}$ -user $\{Xilinx\}$ -desc $$\{No$ more $CDC$$ 14!\}$ -from $$\operatorname{startpoints}$$

```

- 4. From the Vivado IDE, select Reports → Timing → Report CDC to rerun Report CDC.

- 5. In the CDC Report, verify that the CDC-14 violations are no longer reported in the Summary section.

6. To report only the waived violations, enter:

```

report_cdc -details -waived

```

The following figure shows the waived CDC violations in two different tables. The first table shows the 5 CDC-14 violations waived as multi-bit violations. The second table shows the 10 single-bit violations, calculated by multiplying the 5 multi-bit violations by 2 bits per multi-bit violation.

7. To export all the waivers inside a script and verify that a total of four waivers were added, enter:

```

write_waivers -type cdc waivers.xdc -force

```

**Note:** Because the waivers.xdc file already exists, the -force option must be specified to override the file.

**TIP:** Alternatively, because there are no DRC or methodology waivers, you can enter:

```

write_waivers waivers.xdc -force

or

write_xdc -type waiver waivers.xdc -force

```

The list of waivers inside waivers.xdc appears as follows.

```

* WRITE CDC Waivers

* UndITE CDC Waivers

* UndITE CDC Waivers

* Cond; write_waivers -type cdc -file waivers.xdc -force

* Current_instance -quiet

* Condition of CDC-10 - Loser "Xilinx" -desc "This is a safe CDC per review with the team" -from [get_pins i_mw_ip_support_block/jesd204_i/inst/i_mw_ip_it_tx/i_tx_counters_32/got_create_waiver -type CDC -id (CDC-11) - user "Xilinx" -desc "Safe fanout, Circuitry has been released" -from [get_pins i_mw_ip_support_block/jesd204_i/inst/i_mw_ip_reset_block/stretch_reg[10]/"

* Create_waiver -type CDC -id (CDC-14) - user "Xilinx" -desc "No more CDC-14!" -from [list [get_pins i_mw_ip_support_block/jesd204_i/inst/tx_cfg_test_modes_reg[1]/") [get_pins_ip_support_block/jesd204_i/inst/tx_cfg_test_modes_reg[1]/"] [get_pins_ip

```

8. To import the waivers.xdc file, enter:

```

read_xdc waivers.xdc

```

The following warnings show that duplicate waivers were not added to the existing waivers. Only waivers that are exact duplicates of existing waivers are rejected.

```

WARNING: [Vivado_Tcl 4-935] Waiver ID 'CDC-10' is a duplicate and will not be added again.

WARNING: [Vivado_Tcl 4-935] Waiver ID 'CDC-11' is a duplicate and will not be added again.

WARNING: [Vivado_Tcl 4-935] Waiver ID 'CDC-11' is a duplicate and will not be added again.

WARNING: [Vivado_Tcl 4-935] Waiver ID 'CDC-14' is a duplicate and will not be added again.

```

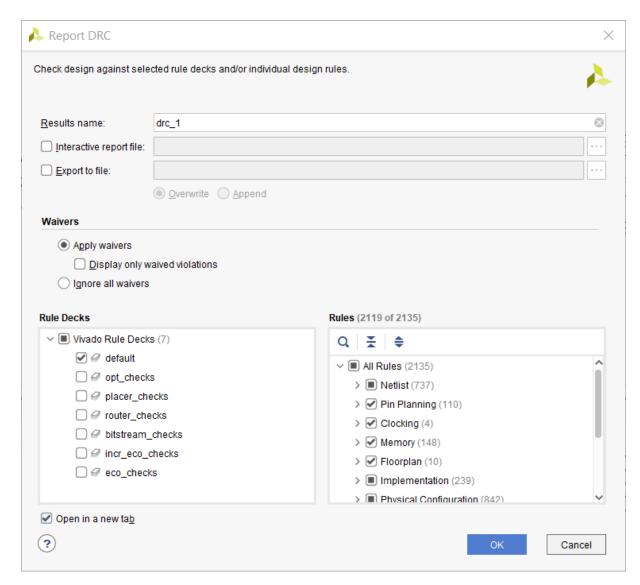

### Step 10: Waiving Multiple DRC Violations

In this step, you waive multiple DRC violations simultaneously.

- 1. Select Reports → Report DRC.

- 2. In the Report DRC dialog box, leave all settings at their default, and click **OK**.

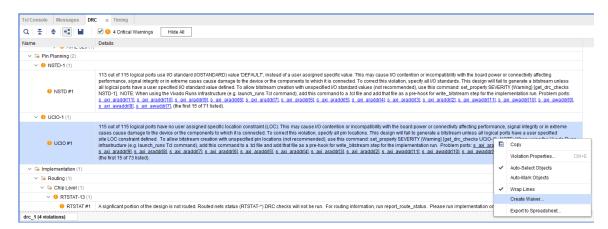

3. In the DRC Report, right-click **UCIO#1**, and select **Create Waiver** to create a waiver for the UCIO-1 violations.

**Note:** The UCIO#1 violation combines 115 individual violations into a single violation. Similarly, the NSTD#1 violation covers 113 ports.

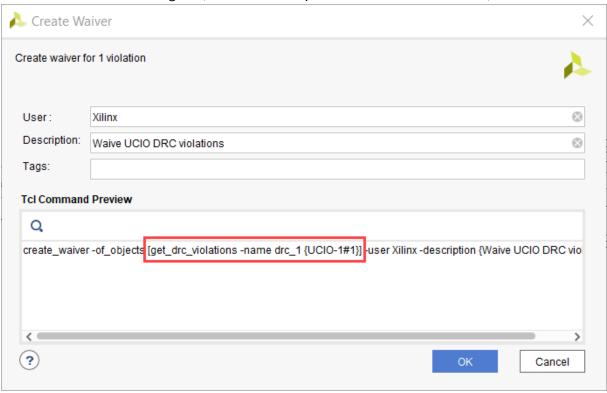

4. In the Create Waiver dialog box, look at the output in Tcl Command Preview, and click OK.

5. To generate the drc\_waivers.xdc file and verify that the waiver is waiving all 115 objects, enter:

```

write_waivers -type DRC drc_waivers.xdc

```

6. In the XDC file, look at the expanded port list, and notice that some of the strings from the violations message were converted to wildcards (\*).

Strings are automatically converted to wildcards for UCIO-1, NSTD-1, TIMING-15, and TIMING-16 type violations. For UCIO-1, the numbers of objects in the violations are replaced with wildcards, because the numbers of elements are not meaningful.

```

# WRITE IRC WAIVERS

**codd write_waivers -type IRC drc_waivers.xdc

**current_instance -quiet

**create_waiver -type IRC id (UCIO-1) -user "Xilinx" -desc "Waive UCIO IRC violations" -objects [get_ports { refclkOp glblclkp refclkOn tx_start_of_frame[3] tx_start_of_multiframe[3] glblclkn

tx_reset drpclk tx_start_of_multiframe[2] txp[3] tx_start_of_multiframe[0] tx_start_of_frame[2] tx_start_of_frame[1] s_axi_rreads[0] s_axi_rr

```

7. To delete the DRC waiver and rewrite the waiver using wildcards to target a subset of the ports objects, enter:

```

delete_waivers [get_waivers -type drc]

create_waiver -type DRC -id {UCIO-1} -user "Xilinx" -desc "Waive

selected UCIO violations" -objects [get_ports { s_axi_rdata[*] }

s_axi_wdata[*] s_axi_araddr[*] } ] -strings { "*" } -strings { "*" }

```

**Note:** This command only covers a subset of the original 115 objects.

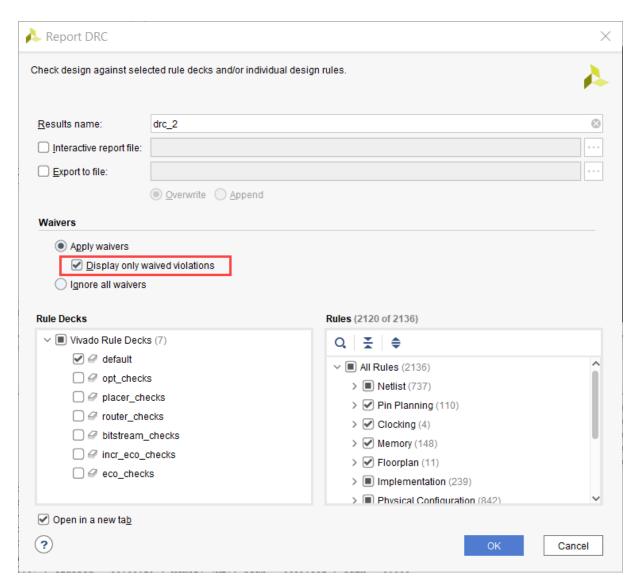

- 8. Select **Reports** → **Report DRC** to rerun Report DRC.

- 9. In the Report DRC dialog box, select **Display only waived violations** to report only waived violations, and click **OK**.

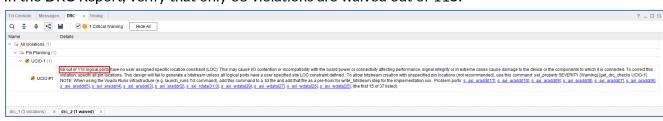

In the DRC Report, verify that only 68 violations are waived out of 115.

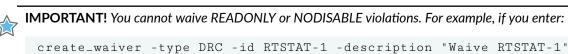

The Vivado tools issue the following error:

ERROR: [Vivado\_Tcl 4-934] Waiver ID 'RTSTAT-1' is READONLY or NODISABLE and cannot be waived. These Factory designations specify that a check is required and may not be overridden by user action.

### Step 11: Generating a Summary Report for **Waived Violations**

This step covers how to use the report\_waivers Tcl command to generate a summary report for CDC, DRC, and methodology waivers.

**IMPORTANT!** Before running the report\_waivers command, you must rerun Report CDC, Report DRC, or Report Methodology to ensure that added or removed waivers are included in the statistics reported by report\_waivers.

1. To rerun Report CDC, enter:

report\_cdc

2. To rerun Report DRC, enter:

report\_drc

Note: You do not need to rerun Report Methodology, because no methodology waivers were set.

3. To create a summary report, enter:

report\_waivers

By default, report\_waivers reports only waived violations. The following figure shows the UCIO-1, CDC-10, CDC-11, and CDC-14 rules, which have defined waivers.

```

Table Of Contents

REPORT SUMMARY

2. REPORT DETAILS (DRC)

3. REPORT DETAILS (METHODOLOGY: no waivers)

4. REPORT DETAILS (CDC)

1. REPORT SUMMARY

Waiver Type Total Vios Remaining Vios Waived Vios Used Waivers Set Waivers

230

162

68

METHODOLOGY 0 0 0 0 CDC 957 944 13

Note: This report is based on the most recent report_drc/report_methodology/report_cdc runs.

2. REPORT DETAILS (DRC)

Rule Severity Description Total Vios Remaining Vios Waived Vios Used Waivers Set Waivers

UCIO-1* Critical Warning Unconstrained Logical Port 115 47 68 1

4. REPORT DETAILS (CDC)

Total Vios Remaining Vios Waived Vios Used Waivers Set Waivers

Rule Severity Description

CDC-10

Critical

Combinational logic detected before a synchronizer

187

186

1

1

CDC-11

Critical

Fan-out from launch flop to destination clock

2

0

2

2

CDC-14

Critical

Multi-bit CDC path on a non-FD primitive

10

0

10

1

Note: Any 'Rule' which is flagged by '*' is an aggregating message and its counts are based on the number of objects represented,

rather than the number of messages.

```

Note the number of waived objects and total violations:

- The aggregating DRCs are reported as 1 violation per object inside the violation. Because there are 113 objects in NSTD-1, 115 objects in UCIO-1, 1 in RTDAT-13, and 1 in AVAL-326, a total number of 240 DRC violations are reported in the Summary table.

- The Report Summary table reports all of the violations.

- The Report Details tables only report the check IDs that have one or more waivers.

- 4. To generate detailed tables with all of the rules, including rules with no waivers, enter:

```

report_waivers -show_msgs_with_no_waivers

```

The following figure shows the report with all DRC and CDC rules reported in the Report Details.

Table Of Contents 1. REPORT SUMMARY 2. REPORT DETAILS (DRC) 3. REPORT DETAILS (METHODOLOGY: no waivers) 4. REPORT DETAILS (CDC) 1. REPORT SUMMARY Waiver Type Total Vios Remaining Vios Waived Vios Used Waivers Set Waivers 162 68 0 0 944 DRC 230 162 METHODOLOGY 0 0 CDC 957 944 Note: This report is based on the most recent report\_drc/report\_methodology/report\_cdc runs. 2. REPORT DETAILS (DRC) Severity Description Total Vios Remaining Vios Waived Vios Used Waivers Set Waivers 0 4. REPORT DETAILS (CDC) Rule Severity Description Total Vios Remaining Vios Waived Vios Used Waivers Set Waivers CDC-10 Critical Combinational logic detected before a synchronizer 187 186 2 0 10 0 536 536 9 9 28 CDC-9 Info Asynchronous reset synchronized with ASYNC\_REG property 5 CDC-15 Warning Clock enable controlled CDC structure detected 10 10 Note: Any 'Rule' which is flagged by '\*' is an aggregating message and its counts are based on the number of objects represented,

5. To run Report Methodology, enter:

report\_methodology

6. To generate detailed tables with all of the rules, including rules with no waivers, enter:

```

report_waivers -show_msgs_with_no_waivers

```

The exact statistics are reported, as shown in the following figure.

Note: This figure does not include the Report Details (CDC) section.

|                                             | e Total Vios R     | -                                      |                           |                    | ers Set Wa         | aivers   |   |             |   |               |             |

|---------------------------------------------|--------------------|----------------------------------------|---------------------------|--------------------|--------------------|----------|---|-------------|---|---------------|-------------|

|                                             | 230 1              |                                        |                           |                    | 1                  |          |   |             |   |               |             |

| METHODOLOG                                  | Y 158 1            | 58                                     | 0                         | 0                  | 0                  |          |   |             |   |               |             |

| CDC                                         | 957 9              | 14                                     | 13                        | 4                  | 4                  |          |   |             |   |               |             |

|                                             | DETAILS (DRC)      |                                        |                           |                    |                    |          |   |             |   |               |             |

| Rule                                        | Severity           | Description                            |                           |                    |                    | -        |   |             |   |               | aivers      |

|                                             | Critical Warnin    |                                        |                           |                    |                    |          |   |             |   | 1             |             |

| RTSTAT-13                                   | Critical Warnin    | g Insufficien                          | t Routing                 | 1                  | 1                  |          | 0 |             | 0 | 0             |             |

| AVAL-326                                    | Critical Warnin    | g Hard_block_                          | must_have_LOC             | 1                  | 1                  |          | 0 |             | 0 | 0             |             |

| NSTD-1*                                     | Critical Warnin    | g Unspecified                          | I/O Standard              | 113                | 113                |          | 0 |             | 0 | 0             |             |

|                                             | DETAILS (METHODO   | LOGY)                                  |                           |                    |                    |          |   |             |   |               |             |

| 3. REPORT                                   |                    |                                        |                           |                    |                    |          |   |             |   | Head Daireans | Sat Wairran |

| Rule                                        | Severity           | -                                      |                           |                    |                    | Remainin |   |             |   |               | Jet walvers |

| Rule<br>TIMING-9                            |                    | Unknown CD                             | C Logic                   |                    | 1                  | 1        |   | 0           |   | 0             | 0           |

| Rule<br>TIMING-9                            |                    | Unknown CD                             | C Logic                   |                    | 1                  | 1        |   | 0           |   | 0             |             |

| Rule<br>TIMING-9                            |                    | Unknown CD<br>Missing pr               | C Logic                   | chronizer          | 1<br>1             | 1 1      |   | 0<br>0      |   | 0             | 0           |

| Rule<br>TIMING-9<br>TIMING-10<br>TIMING-18* | Warning<br>Warning | Unknown CD<br>Missing pr<br>Missing in | C Logic<br>operty on sync | chronizer<br>delay | 1<br>1<br>1<br>115 | 1 1      |   | 0<br>0<br>0 |   | 0<br>0        | 0           |

### **Step 12: Using Waiver Commands**

In this step, you run additional commands related to the waivers.

1. To return a collection of CDC waiver objects, enter:

```

get_waivers -type cdc

```

The following CDC waivers are returned:

```

CDC-10#1 CDC-11#1 CDC-11#2 CDC-14#1

```

2. To filter the list of waivers to only return CDC-14 waivers, enter:

```

get_waivers -filter {ID == CDC-14}

CDC-14#1

```

3. To report all of the properties on a CDC waiver object, enter:

```

report_property [lindex [get_waivers -type cdc] end]

```

The following properties are returned:

| D             | Ш      | D 1 1     | 17 - 7          |

|---------------|--------|-----------|-----------------|

| Property      | Type   | Read-only | Value           |

| CLASS         | string | true      | cdc_waiver      |

| DESCRIPTION   | string | false     | No more CDC-14! |

| ID            | string | true      | CDC-14          |

| INDEX         | string | true      | 1               |

| IS_SCOPED     | bool   | true      | 0               |

| NAME          | string | true      | CDC-14#1        |

| OBJECT_COUNTS | string | true      | pins:2          |

| SCOPE    | string |       |                         |

|----------|--------|-------|-------------------------|

| TAGS     | string | false |                         |

| TIME     | string | true  | <timestamp></timestamp> |

| TYPE     | string | true  | CDC                     |

| USED_CNT | string | true  | 10                      |

| USER     | string | true  | Xilinx                  |

**Note:** You cannot retrieve the design objects attached to a waiver object.

4. To delete all of the previously created CDC-14 waivers, enter:

```

delete_waivers [get_waivers -filter {ID == CDC-14}]

```

**Note:** After a waiver object is deleted, the waiver no longer applies and the violations that it waived are reported again.

5. To delete all of the remaining CDC waivers, enter:

```

delete_waivers [get_waivers -type cdc]

```

### Summary

In this lab, you accomplished the following:

- Waived CDC and DRC violations

- Generated reports for waived violations

- Exported waivers

- Used waiver commands

Lab 2

# Using Report QoR Suggestions and Report QoR Assessment for Timing Closure

### Introduction

The report\_qor\_suggestions (RQS) command enables the Vivado® Design Suite tools to analyze a design and provide automated solutions for enhancing quality of results (QoR). The command can be run on an open design after synthesis or after any stage in the implementation flow. The RQS command evaluates the design and suggests fixes or improvements. Recommendations from RQS can take the following forms:

- RQS objects. These objects can add switches to a given command, or properties to a given design object. They also allow you to add implementation strategies customized for the design using machine learning algorithms.

- Text recommendations that require user intervention.

Using the same analysis techniques, the  $report_qor_{assessment}$  (RQA) command assesses the likelihood that a design will meet its timing requirements and provides a quick summary of design metrics.

This lab covers how to do the following:

- Analyze the QoR assessment report.

- Analyze the QoR suggestion report.

- Export suggestions to an RQS file.

- Add an RQS file to synthesis and implementation runs.

- Accumulate suggestions in an RQS file by generating suggestions at different implementation stages or on different runs.

- Add the AUTO\_RQS property to a project-based design run and automatically accrue suggestions.

### **Step 1: Understanding the Design**

This lab uses an architected design to demonstrate some of the features of RQS. Suggestions are triggered by the design of the RTL and the placement of blocks using floorplanning. The design contains the following modules:

• Clocking Module: The main clocking circuit for the design resides in clocking\_module.vhd. For simplicity, RST is tied to GND. LOCKED is registered and tied to an output port. The structure of this block is shown in the following figure.

- Reg CLKA to CLKB Module: This module contains a synchronous CDC for a large bus. It

registers input data using CLKA and then passes it to a register on the CLKB domain to be

passed to the output. Registering large buses on different related clock domains can impact

hold slack (WHS/THS) and setup slack (WNS/TNS).

- **Bit Expander and Bit Reducer Modules:** These modules enable the expansion and contraction of internal data widths so that the design does not run out of I/Os. The modules take an arbitrary data width and expand or contract it to or from a desired size. The contraction logic creates many logic levels.

The following steps cover opening the project and examining the placement of the floor-planned modules.

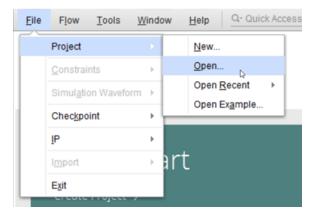

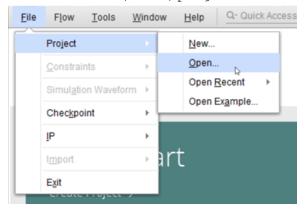

1. In the Vivado Design Suite, go to File  $\rightarrow$  Project  $\rightarrow$  Open and select the project located in <extract\_Dir>/Lab2/project\_2.

- 2. In the Flow Navigator, click Run Synthesis and wait for synthesis to complete.

- 3. In the Flow Navigator, click Open Synthesized Design.

- 4. In the Netlist view, look at the hierarchy.

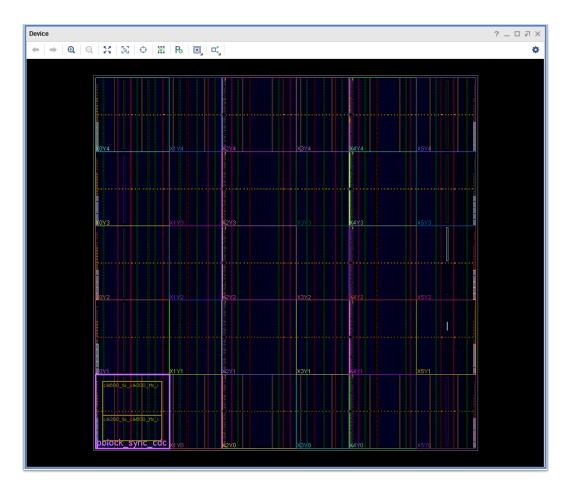

5. In Device view, look at the pblock. This has been added to control placement of the reg\_clka\_to\_clkb modules and force a poor clock skew.

### **Step 2: Running Report QoR Assessment**

In this step, you will run the report\_qor\_assessment command on the open design. This step can be run after any stage of the implementation process: synth\_design, opt\_design, place\_design, phys\_opt\_design, and route\_design. It provides an assessment score that details the likelihood of the design closing timing, as well as a quick first analysis returning items that need to be further investigated.

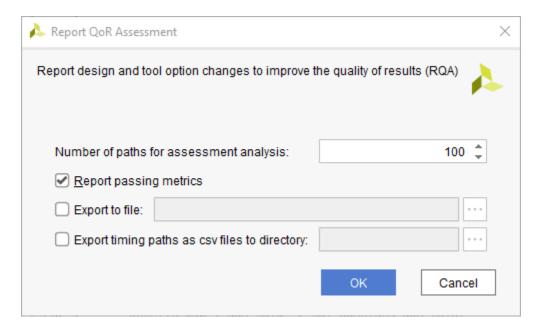

- 1. With the design open, click Reports → Report QoR Assessment....

- 2. In the Report QoR Assessment dialog box, select Report Passing Metrics and click OK.

The equivalent Tcl command is as follows:

```

\tt report\_qor\_assessment - exclude\_methodology\_checks - name \ qor\_assessments - max\_paths \ 100 \ - full\_assessment\_details

```

This opens up the assessment report, with three main sections providing the following:

- Assessment summary

- Difficult timing paths requiring investigation

- Objects with DONT\_TOUCH properties that prevent tool optimizations

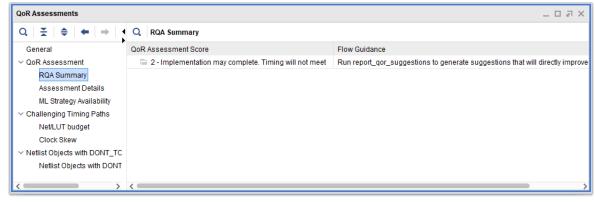

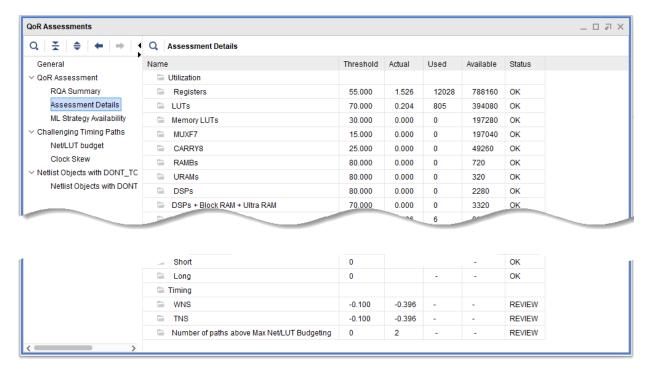

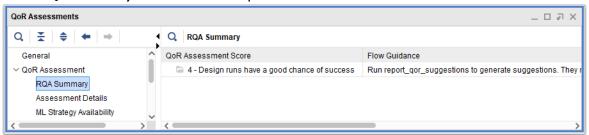

- 3. In the first section of the report, select **RQA Summary**.

This section has the score marked as "2 - Implementation may complete. Timing will not meet". It also recommends running report\_qor\_suggestions. The RQA command understands when suggestions are available and can offer the guidance to check them.

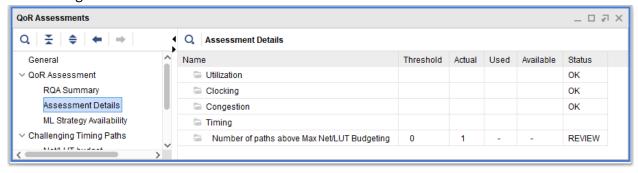

4. Select Assessment Details.

This section lists the items that have led to the assessment score of 2. Because the option to **Report passing metrics** was selected, items marked as OK are shown. Typically, only items marked REVIEW are shown. In this example, you can see WNS and TNS metrics marked for review, as well as paths above their net/LUT budget.

Timing paths usually offer the values that are achievable in the best case scenarios. Not all paths can achieve these values. Net and LUT budget checks substitute net or LUT values with more typical values, and also penalize paths that are more challenging due to a netlist profile or a resource being less sparse. The result is two checks performed under this item. Look at all of these paths before continuing.

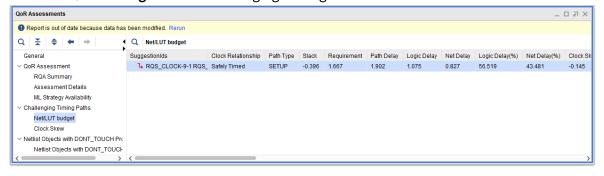

5. Select Net/LUT budget under Challenging Timing Paths.

Scroll across the screen to see all the path characteristics reported. The following items are of particular interest:

• SuggestionIds: These IDs correspond to suggestions that, if triggered, impact this path.

- **Net Check Slack:** This is the slack when the path is substituted with higher net delay values.

- LUT Check Slack: This is the slack when LUTs are substituted with higher LUT delay values.

- 6. Double-click on the path to bring up the Timing Path report. You can also press **F4** to show a schematic. All of these items use standard Vivado cross probing. At this stage, you can also explore other items in the report.

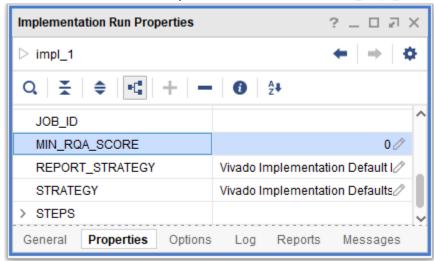

- 7. In the Design Runs window, select **impl\_1**, expand the **Implementation Run Properties** window, and select the **Properties** tab. Locate the MIN\_RQA\_SCORE property.

The MIN\_RQA\_SCORE property can terminate the project implementation run when it is greater than the RQA score. This property defaults to zero, and does not impact unless it is set to another value that is ≥2. The RQA report must also be run. This can done by performing the following steps:

- a. Select Timing Closure Report Strategy.

- b. Add report gor assessment to custom report strategies.

- c. Add report\_qor\_assessment to a Tcl hook. This must execute the command in the run directory to be effective.

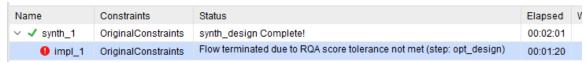

- 8. Edit the MIN\_RQA\_SCORE value to 3. Select the Reports tab and update the Report Strategy to Timing Closure Reports.

- 9. Launch the impl\_1 run.

After opt\_design is complete, the report\_qor\_assessment command is run and the run should terminate. You should see the following in the Design Runs status column:

The log file should have the following message:

```

INFO: [runtcl 7-1] RQA Score (opt_design): 2 (RQA score tolerance: 3)

ERROR: [runtcl 8-1] Flow terminated - RQA score threshold not met after

'opt_design' step

```

The following message appears when the flow successfully passes the check:

```

INFO: [runtcl 7-1] RQA Score (opt_design): 2 (RQA score tolerance: 2)

INFO: [runtcl 9-1] Flow continues - RQA score threshold met after

'opt_design' step

```

10. Update the MIN\_RQA\_VALUE to 1. Revert the reports back to Vivado Implementation Default Reports and reset the run.

# **Step 3: Running Report QoR Suggestions**

This step covers running the report\_qor\_suggestions command to generate a report. The command can be run on an open design at any stage of the implementation flow after synthesis. In project mode, this is typically after synthesis or implementation. In non-project mode, this can be after synth\_design, link\_design, opt\_design, place\_design, phys\_opt\_design, or route\_design.

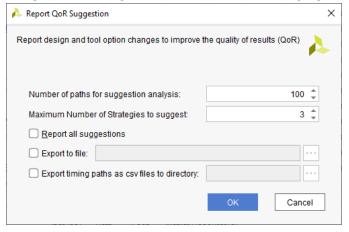

1. In the Vivado IDE, from the pull-down menus, click Reports → Report QoR Suggestions... to bring up the dialog box shown in the following figure.

2. Click **OK** to run the command. The report opens automatically in the integrated design environment (IDE). Due to the interactive nature of the report, only one instance of the report can be open at any time. The equivalent Tcl command is as follows:

```

report_qor_suggestions -max_paths 100 -file rqs.rpt

```

**Note:** By default, the RQS command reports on the 100 worst failing paths per clock group. You can change the number of paths that RQS uses for the analysis of timing-critical paths by modifying the  $-\max_{\texttt{max-paths}}$  switch. Increasing this number generates more suggestions, but on paths that are reducing in criticality.

# **Step 4: Understanding the Report**

This step explains the different sections of the generated QoR Suggestions report. On the left of the report window, you can navigate to the different sections of the report; on the right, more information is provided.

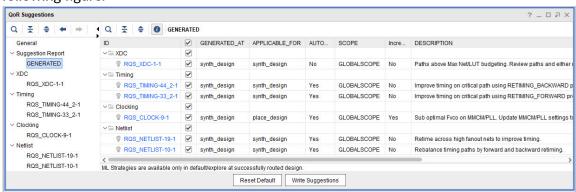

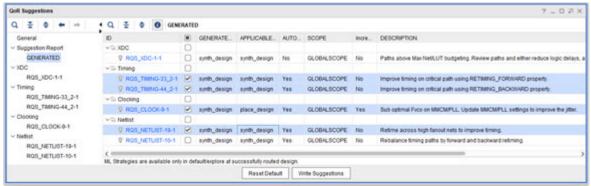

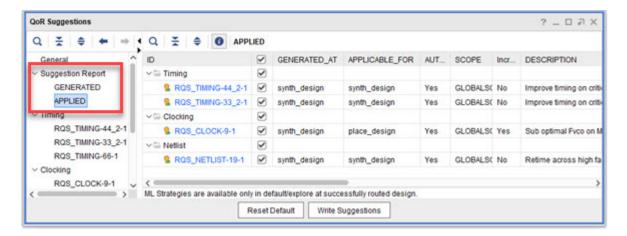

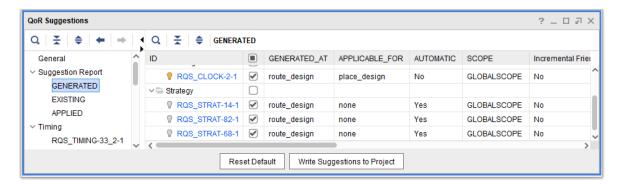

1. In the Suggestion Report, select **GENERATED**. This brings up the report section shown in the following figure.

The GENERATED section provides a list of all the suggestions that have been generated at this stage of the current run. Each suggestion has a description that details the reason for the suggestion. For each suggestion, the following information is also provided.

Table 1: RQS Summary Column Description

| Item                    | Description                                                                                                            | Comment                                                                                                                                                                                                  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GENERATED_AT            | This shows what stage of the design the suggestion was generated at.  Typical values are place_design or route_design. | As you progress through the design stages, the decisions that the tool makes are based on the information available at the time. Information accuracy increases after placement and again after routing. |

| APPLICABLE_FOR          | This stage must be rerun for the suggestion to take effect.                                                            | Most suggestions are executed at either synth_design or place_design.                                                                                                                                    |

| AUTOMATIC               | Indicates if the suggestion is executed automatically or if manual intervention is required.                           | Automatic suggestions either recommend a switch to the tool or a property to be added to a cell or net.                                                                                                  |

| INCREMENTAL<br>FRIENDLY | Indicates if the suggestion is optimized for the incremental flow.                                                     | Non-incremental friendly suggestions must be already present in the reference checkpoint. If you want to add non-incremental friendly suggestions, an updated reference checkpoint must be used.         |

| SCOPE                   | Indicates the target synthesis run level. GLOBALSCOPE is top level. Otherwise, a sub-module is targeted.               | Allows a single RQS file to be used on top-level and sub-<br>module out of context (OOC) synthesis runs. Only<br>applicable to synthesis suggestions.                                                    |

The other sections of the report usually provide details about the individual suggestions that have been generated.

2. Click the RQS\_XDC\_1\_1 hyperlink. This takes you to the details section for this suggestion.

The suggestion description says that the timing constraint is too tight for the given path(s). The path has a large negative slack, which stands out in a timing report. Timing paths use net delays that are optimal. This gives the tools the correct order to place and route them. Close analysis shows this is a 600 MHz path with high logic levels. This path needs to be fixed.

- 3. Click the back arrow button ( \* ) to go back to the GENERATED view.

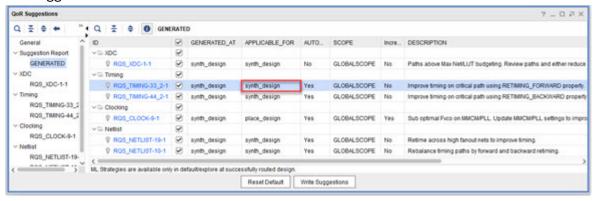

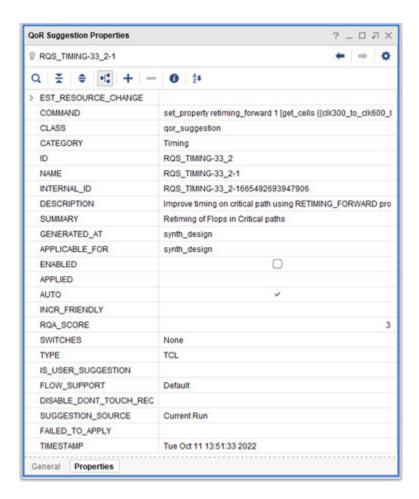

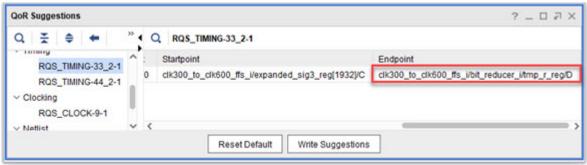

- 4. In the GENERATED view, click the **RQS\_TIMING-33\_2-1** row. You can see this is an AUTOMATIC suggestion that is applicable for <code>synth\_design</code> (see the APPLICABLE\_FOR column). This indicates that you must rerun the <code>synth\_design</code> command to make use of this suggestion.

When you select the row in the GENERATED view, the suggestion object is selected and the properties can be seen in the QoR Suggestion Properties window. If you examine the command property, you can confirm that it generates a retiming forward property for synth\_design.

5. In the GENERATED view, click the **RQS\_TIMING-33\_2-1** ID to go to the details table for that suggestion. Careful examination of the Endpoint column confirms that this is the same path that was mentioned for RQS\_XDC-1-1.

6. In the GENERATED view, you can see the remaining suggestions. The RQS\_CLOCK-9 suggestion is applicable for place\_design. The other RQS\_TIMING-44 suggestion is similar to the existing one.

7. Only select the four suggestions highlighted in the following image to written to the RQS suggestion object file:

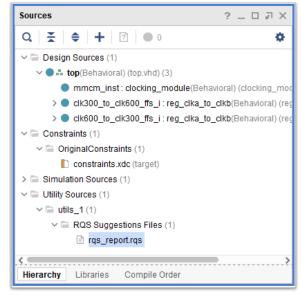

8. Click Write Suggestions to Project. When the Write Suggestions to Project dialog box opens, ensure it is set to write to the rqs\_report.rqs file in the utils\_1 directory, as shown in the following figure. Select Copy sources to project.

9. Examine the Sources window. The RQS file has been added to the utils\_1 fileset. This ensures that the file is captured using the get\_files command and recognized in the next step when you add the file to a run.

# **Step 5: Run with Suggestions**

In this step, you will add a suggestion to a run and examine what happens when a suggestion is applied and how it is reported.

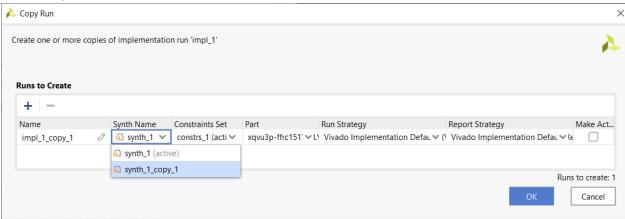

In the Design Runs window, right-click on the synthesis run, select Copy Run, and click OK.

Do the same for the implementation run, but update the synthesis run name to the new one

you have just created, and click OK.

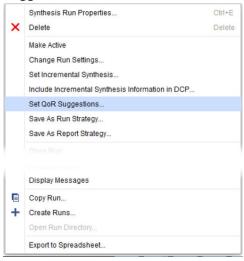

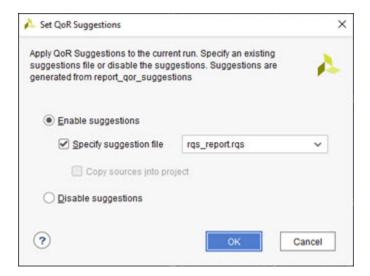

2. In the Design Runs window, right-click the new **synth\_1\_copy\_1** run and select **Set QoR Suggestions**.

3. Specify the suggestion file as the RQS file added to the project from the previous step and click **OK**.

4. Repeat steps 2 and 3 for the implementation run, making sure to specify the new synthesis run as the parent run. Specify the same RQS file for each run. There is a slightly different dialog box for implementation.

- 5. In the Design Runs window, right-click synth\_1\_copy and select Make Active.

- 6. In the Flow Navigator, click Run Synthesis.

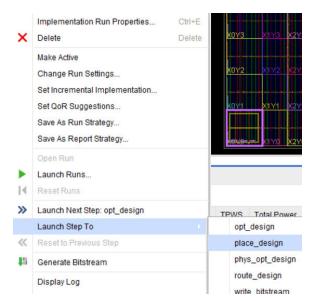

- 7. Because this design takes a long time to route, you will only run to place\_design and analyze at this stage. When synthesis is complete, in the Design Runs window, right-click on the new implementation run and select Launch Step To → place\_design.

- 8. With the implementation running, select the Design Runs window. Right-click the **synth\_1\_copy** synthesis run and click **Open Run**.

- 9. When the run has opened, select Reports → QoR Assessment... and click OK.

- 10. Click RQA Summary. The score has improved from 2 to 4.

11. Click **Assessment Details**. The Net and LUT budget score has been reduced but not eliminated. This is a consequence of the high frequency that paths are being forced to run at in this design.

12. Close the synthesized design.

13. When place\_design is finished, examine the very top of the implementation log file for the new implementation run. It provides a table summary of the suggestions that have been read in. This summary helps you confirm that what has been read in is what you expect.

| 1. Read QOR Suggestions Summary         |               |       |

|-----------------------------------------|---------------|-------|

| Read QOR Suggestions Summary            |               |       |

| Suggestion Summary                      | Incr Friendly | Total |

| Total Number of Enabled Suggestions     | •             | 4     |

| Automatic                               |               | 4     |

| Manual                                  | 0             | 0     |

| APPLICABLE_FOR<br>  synth_design        |               | 1 3 1 |

| opt_design                              |               | !     |

| That overlap with synthesis suggestions | i             | i 0 i |

| place_design                            | 1             | 1 1   |

| postplace_phys_opt_design               | 1 0           | 0     |

| route_design                            | 0             | 0     |

| postroute_phys_opt_design               | 0             | 0 1   |

| ML Strategy                             | 0             | 0 1   |

| Total Number of Disabled Suggestions    | 0             | 0 1   |

- 14. Right-click on the implementation run and select **Open Run Directory**. Open the checkpoint file by double-clicking **top\_placed.dcp**. This step is necessary because you are examining an intermediate run step in the interests of saving time.

- 15. In the new instance of the Vivado tools, select **Reports** → **Report QoR Suggestions** ... and click **OK**.

- 16. In the new report, there are more sections under Suggestion Report:

- **GENERATED:** New suggestions are listed in this section.

- **EXISTING:** Suggestions that existed previously but have not been applied are listed in this section (not shown).

- APPLIED: Suggestions that have been applied are listed in this section.

- **FAILED TO APPLY:** Suggestions that apply to design objects that no longer exist are listed in this section (not shown).

17. Click **APPLIED** and select the details table for one of the items. For APPLIED suggestions, the timing path summary is still available but it is not possible to cross probe to other views in Vivado because some items might have changed.

## **Step 6: Accumulating Suggestions**

You can now review the newly generated suggestions and add them to the RQS file.

- 1. Click **GENERATED**. The RQS\_CLOCK-15 message reports high THS paths but does not provide an automatic suggestion.

- 2. Examine RQS\_CLOCK-2-1. This suggestion recommends changing the clock buffers to BUFGCE\_DIV to improve the timing path uncertainty. It is highly recommended to implement this. Because this suggestion is not automated, however, it requires an RTL edit. If you wish, you can make the recommendation and see the improvement, but this step can be skipped. The next steps focus on the automated suggestions.

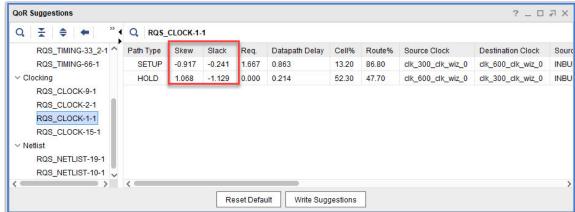

- Click on RQS\_CLOCK-1-1 to view the detailed report. This suggestion applies CLOCK\_DELAY\_GROUP to related clocks. In this report, you can see that there is a high clock skew and failing slack.

Clock skew is difficult to identify before place\_design because the skew estimate depends heavily on placement. As a consequence, RQS does not offer this suggestion unless a design is placed. Whenever there is a change in information level, it might be advisable to run report\_qor\_suggestions. The following summarizes the changes as you progress through the tool flow:

- Clocking estimates are accurate after place\_design.

- Congestion is available after placement and improves further after routing.

- Timing estimates improve throughout the flow and are impacted by the number of paths analyzed.

- 4. Click **Write Suggestions**. When suggestions are written, the APPLIED status is reset. All the previous suggestions and the new RQS\_CLOCK-1-1 suggestion are combined into one file. You can overwrite the previous file and reuse the runs, or create a new file and new runs.

- 5. Select the file location to overwrite the existing file. You can find out the location of this by selecting it in the sources window. Alternatively, it should be at the following location if you have followed the steps carefully: <extract\_dir>/Lab2/project\_2/project\_2.srcs/utils\_1/imports/project\_2.

You are now at the point where you know the fundamentals in handling RQS files and accumulating suggestions. If you have time, rerun implementation through to route\_design and examine the impact of the latest suggestion. Alternatively, generate alternative suggestions by running report\_qor\_suggestions on your own design.

- 6. Close the run.

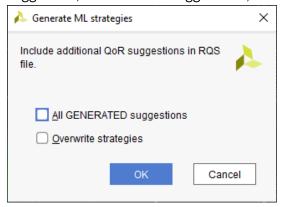

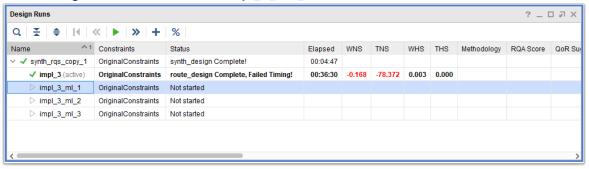

- 7. In the Design Runs window, right-click the implementation run impl\_1\_copy\_1 and select Launch to → Route Design. When routing is complete, right-click and select Generate ML Strategies. Doing this generates three RQS files that each contain one ML strategy suggestion, the APPLIED suggestions, and optionally any GENERATED suggestions.

8. After the generation is complete, in the Design Runs window, right-click the implementation run **impl\_1\_copy\_1** and select **Create ML Strategy Runs**. This creates three implementation runs, each targeting a different ML-based implementation strategy.

# Step 7: Automatically Running QoR Suggestions

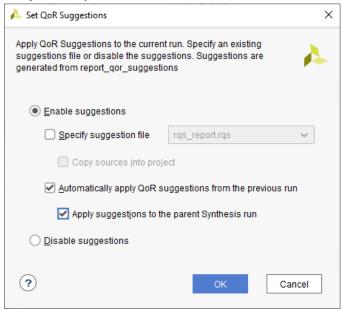

In this section you will run the AUTO\_RQS flow, where suggestions are generated at the end of an implementation run and automatically added to the run when it is reset.

- 1. In the Design Runs window, copy the original synthesis and implementation run again using the right-click menu.

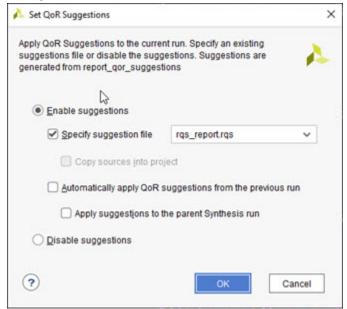

- In the Design Runs window, right-click impl\_2 → Set QoR Suggestions.

- Select Automatically apply QoR suggestions from the previous run and Apply suggestions to the parent Synthesis run.

- 4. You can now launch the runs. Suggestions are only generated at the end of route\_design using this method. The picture the flow sees can be different to the previous steps, so you can expect different results. In addition, all AUTO suggestions generated or regenerated at route\_design will be applied.

- 5. Launch the runs. This step takes some time because it launches the full implementation flow.

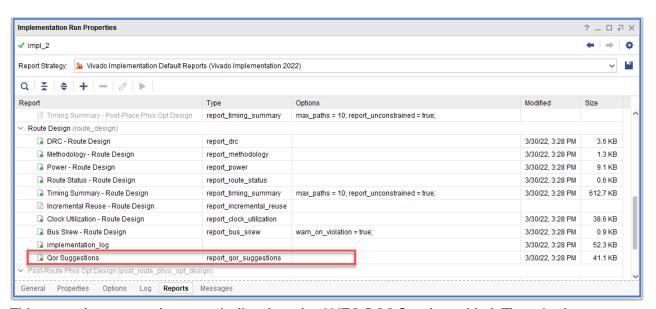

- 6. When the run is complete, go to the **Reports** tab and select the **QoR Suggestions** report.

This report is generated automatically when the AUTO RQS flow is enabled. There is also automatic writing of QoR suggestions. The suggestions written to the RQS file have one of the following properties:

- GENERATED\_AT or REGENERATED\_AT equal to the final flow step, which can be route\_design or postroute\_phys\_opt

- AUTOMATIC

- APPLIED

- 7. Reset the implementation run. This makes the synthesis run out of date at the same time. Because the option to apply suggestions to the parent synthesis run is selected, the RQS file will also be read in this run.

- 8. Right-click **impl\_1\_copy\_2** and launch the implementation run, also selecting the option to restart the synthesis run.

- 9. With the run launched, select <code>impl\_1\_copy\_2</code> in the Design Runs window. E`xamine the RQS\_FILES property on the Implementation Run Properties window. During the reset run process in step 7, the RQS file is copied from the run directory to the <code>utils\_1</code> fileset. The RQS\_FILES property is updated if required at the same time. RQS files in the implementation run directory will be deleted when the run is reset.

- If the RQS\_FILES property previously pointed to a different file, all the APPLIED suggestions from this file are copied to the new RQS file and subsequently, this RQS file is no longer required and is dropped.

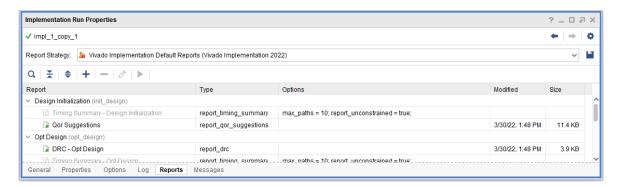

- 10. Select **Implementation Run Properties** and then the **Reports** tab. After the design initialization step is run, a report is made available that contains the QoR suggestions that have been read into the run from the RQS file. Select this report.

11. In the report, you can see that ML strategies have been generated. In the case of the AUTO\_RQS flow, the required RQS files are generated for you automatically. These files are combined with all the suggestions that are currently APPLIED, as well as the suggestions that meet the criteria outlined above to be added when the run is reset.

- 12. In the Design Runs window, right-click  $impl_1 copy_2 \rightarrow Open Run Directory$ . Locate the MLStrategy directory and confirm that there are three RQS files inside it. Close the folder.

- 13. In the Design Runs window, right-click impl\_1\_copy\_2 → Create ML Strategy Runs. Doing this creates three runs and automatically sets the RQS file and directives for you. ML strategies are covered in more detail in the following lab.

- 14. When the implementation run completes, new suggestions are generated. Using only impl\_1\_copy\_2, repeat steps 6 to 10 for a clearer understanding of how the RQS file is updated with the new suggestions.

#### Summary

In this lab, you achieved the following:

• Using RQA, you conducted an assessment before and after improvements were implemented, examining an improvement in the score.

Using RQS, you conducted a complex analysis of a demonstration design. You first examined

the reports that showed RQS recommendations to solve implementation problems, then you

generated an RQS file and added it to a project implementation run. The Vivado

implementation tools executed the suggestions automatically for you. You subsequently

performed further analysis and generated further suggestions, accumulating them in the RQS

file.

Lab 3

# Running ML Strategies

#### Introduction

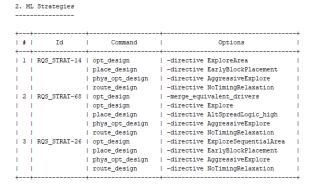

The report\_qor\_suggestions command can generate an implementation design strategy that is predicted to be optimal for the design using machine learning algorithms. In this tutorial, you will look at:

- How to generate ML strategy suggestions.

- How to setup the implementation run to use ML strategy suggestions.

- Reporting specifics related to ML strategies.

# Step 1: Generating an ML Strategy RQS File

This step shows the process of opening a routed design with QoR suggestions and generating a new RQS file with strategies. For details on the design, refer to Step 1: Understanding the Design.

1. In the Vivado Design Suite, go to File  $\rightarrow$  Project  $\rightarrow$  Open and select the project located in <extract\_Dir>/Lab3/project\_2.

- 2. In the Flow Navigator, click Open Implemented Design.

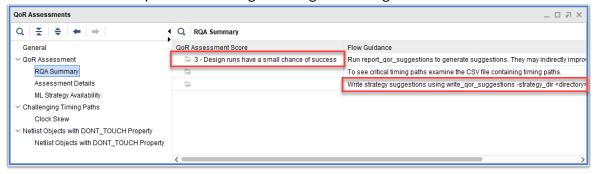

- 3. From the pull-down menus, select Reports → Report QoR Assessment, and click OK.

4. In the RQA Summary table, you will see the QoR Assessment Score and Flow Guidance. This table helps identify good candidate designs on which to use ML strategy suggestions. QoR assessment scores of 3 and above have a chance to meet timing. Designs with an RQA score of less than 3 are not prevented from generating ML strategies.

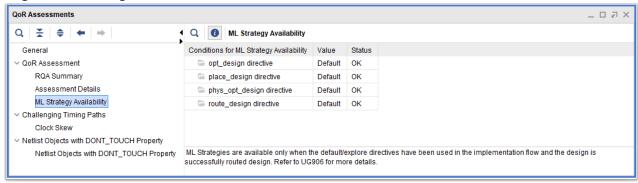

5. Click **ML Strategy Availability**. This table details the required directives for the reference run to generate strategies.

The status for all directives must be listed as OK to generate strategies. The requirements are as follows:

- The opt\_design directive value must be either Default or Explore.

- The place\_design, phys\_opt\_design, and route\_design conditions must be the same as each other and must be set to either Default or Explore.

- 6. In the Design Runs window, confirm the strategy is Vivado Implementation Defaults. This requirement is met when a design has been run with either the Vivado implementation defaults or the performance\_explore strategy.

- 7. From the pull-down menus, select Reports → Report QoR Suggestions, and click OK.

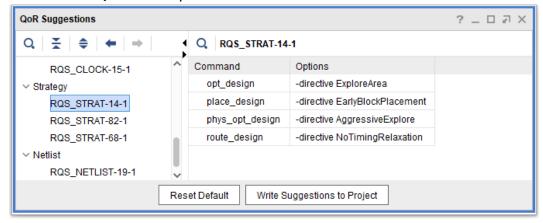

- 8. In the QoR suggestion report, select **GENERATED**. Three new strategies have been generated.

9. In the Strategy section, select the topmost strategy. Here, you can see the details of the strategy being suggested. It is possible to set these up manually, but to automate the process more easily, the recommended flow is to read an RQS file containing strategies and set the directive to RQS on the implementation commands.

- 10. Select Write Suggestions to Project to write the following files:

- A top-level RQS file that does not contain strategies (this file can be ignored)

- An RQS file for each strategy as well as any other QoR suggestions (written to the MLStrategy directory).

Generating the strategy RQS files is the first part of a two-step process. This way of generating the suggestions gives complete control over what other suggestions are in the RQS file. Other ways to generate these files are as follows:

- Automatic generation using AUTO\_RQS flow (as seen in Lab 2: Using Report QoR Suggestions and Report QoR Assessment for Timing Closure)

- Clicking Generate ML Strategies from the right-click menu in the Design Runs window

- Automatic generation at the end of Stage 1: Design Optimization of Intelligent Design Runs

- A post-route Tcl hook script

### **Step 2: Creating ML Strategy Runs**

In this step, you will create the ML strategy implementation runs using the files created in Step 1: Generating an ML Strategy RQS File.

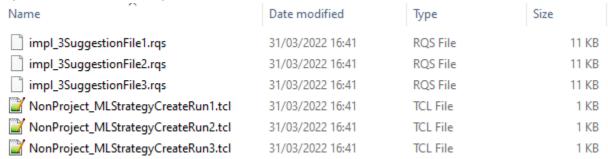

- 1. In the Design Runs window, select impl\_3, then right-click and select Open Run Directory.

- Search for the MLStrategy directory and examine the contents. You will see three RQS files

and three non-project-based Tcl scripts. The RQS files are common for both project and nonproject flows. The non-project scripts are examples of how to use the RQS file.

- 3. The next step is to generate the ML strategy runs. As long as the files reside in the <run\_directory>/MLStrategy directory, this process can be automated. In the Design Runs window, right-click the implementation run and select Create ML Strategy runs. Doing this creates three runs, one for each ML strategy file. Configure the runs to use the RQS directive and the RQS file to be read into each of them.

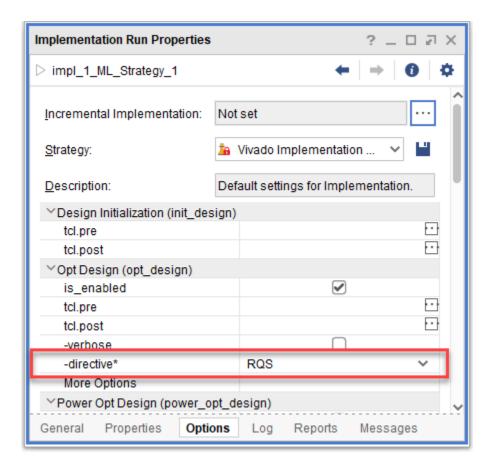

- 4. In the Design Runs window, select impl\_3\_ML\_1.

- 5. In the Implementation Run Properties window, select the **Properties** tab and confirm that RQS\_FILES is set.

- 6. In the Implementation Run Properties window, select the **Options** and confirm the directive is set to RQS for the <code>opt\_design</code>, <code>place\_design</code>, <code>phys\_opt\_design</code>, and <code>route\_design</code> commands.

You are now set up to run with ML strategies. By the time you have an ML strategy file, you cannot generate new strategies after design changes, but you can add other suggestions.

7. You are now ready to launch the runs. Select all the ML strategy runs, right-click, and select **Launch Runs...**. The runs will now proceed in parallel, and complete like a standard run.

#### **Summary**

In this lab, you achieved the following:

- Used report\_qor\_suggestions to generate ML strategies.

- Created the RQS and Tcl files using write\_qor\_suggestions.

- Sourced the Tcl to set up the ML strategy runs and confirmed the key aspects of setting up an ML strategy run.

Iab 4

# Intelligent Design Runs

#### Introduction

In this tutorial, you will work with intelligent design runs (IDRs). An IDR is a simple-to-use implementation run that extends the performance of your design by automating QoR suggestions and ML strategies. These features are applied in a way that maximizes the improvement in performance.

This lab covers how to:

- Create an IDR.

- Add Tcl hooks to the IDR.

- Examine the log file for an IDR.

- Examine reports for an IDR.

- Create a single pass run from an IDR.

# **Step 1: Creating Intelligent Design Runs**

In this section, you will create an example design and an Intelligent Design Run (IDR).

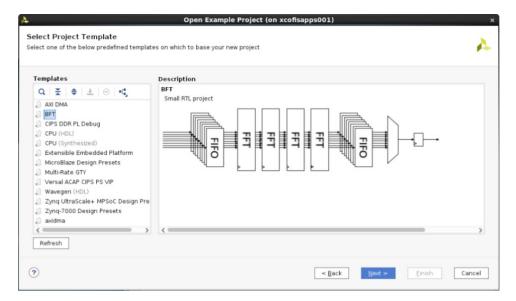

1. First, you need a project. Select Open Example Project.

2. Click **Next**→ **BFT** and then select **Next** again.

- 3. In the next screen, ensure you are working on in a suitable writable directory, and select **Next**.

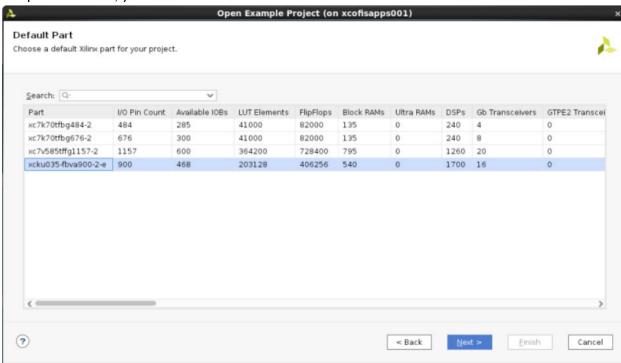

- 4. For part selection, you must select xcku035-fbva900-2-e and then select Next → Finish.

You should now have an open project that is waiting to be synthesized.

**Note:** IDRs are not supported for 7 series devices. Selecting the incorrect family requires you to regenerate the project.

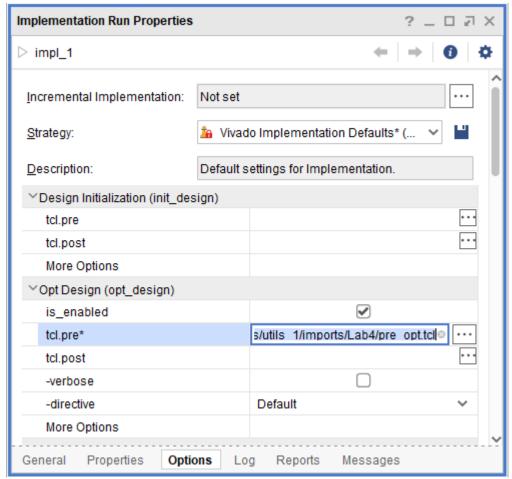

5. This lab aims to demonstrate how to add a Tcl file to an IDR. To do this, add a file to impl\_1. In the Design Runs window, select impl\_1.

- 6. In the Implementation Run Properties window, select the **Options** tab.

- 7. Scroll to the opt\_design tcl.pre option and add the Tcl script <extract\_dir>/Lab4/pre\_opt.tcl to the option.

Alternatively, use the following Tcl syntax:

```

add_files -fileset utils_1 -norecurse <extract_dir>/Lab4/pre_opt.tcl

set_property STEPS.OPT_DESIGN.TCL.PRE [ get_files <extract_dir>/Lab4/

pre_opt.tcl -of [get_fileset utils_1] ] [get_runs impl_1]

```

- 8. In the Flow Navigator, click Run Synthesis.

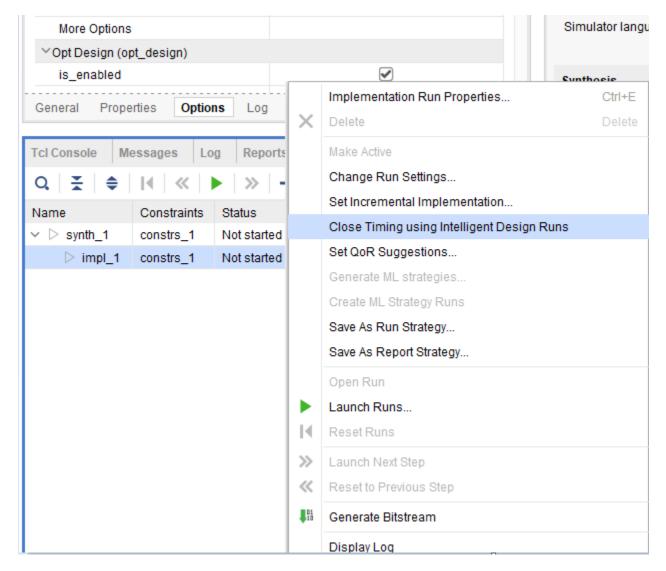

- 9. The next step is to create the Intelligent Design Run. In the **Design Runs** window, right-click on **impl\_1**→ **Close Timing using Intelligent Design Runs**.

If you try this step again to create an additional run, you will find that the option is disabled. This is to prevent the creation of runs that would produce the same results. Runs created from the same netlist with different directives produce the same results because the IDR controls the directive, meaning that they are effectively the same.

If you have a different floorplan or speed grade, create different implementation runs. You can create one IDR from each implementation run.

### **Step 2: Navigating Intelligent Design Runs**

In this step, you will learn how to control intelligent design runs and navigate options and reports.

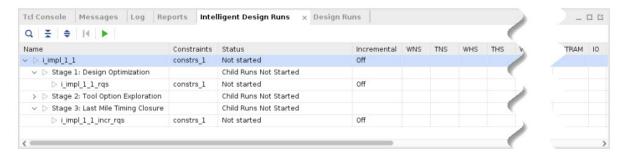

1. Select the Intelligent Design Runs tab at the bottom of the Vivado® IDE.

This window is opened when an IDR is created. If closed, it can be reopened by selecting **Window** → **Intelligent Design Runs**. From this window you can see that there is a hierarchical nature to Intelligent Design Runs. The top-level run is split into three stages:

- Stage 1: Design Optimization

- Stage 2: Tool Option Exploration

- Stage 3: Last Mile Timing Closure

In this lab, only stage 1 is demonstrated. This is the most complex stage, but can be completed quickly because you are working with a simple design.

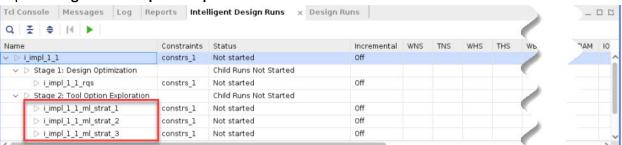

2. Expand Stage 2: Tool Option Exploration.

There are three runs underneath this stage. These runs can be run in parallel if your compute resources allow.

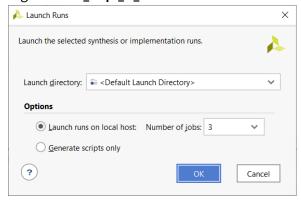

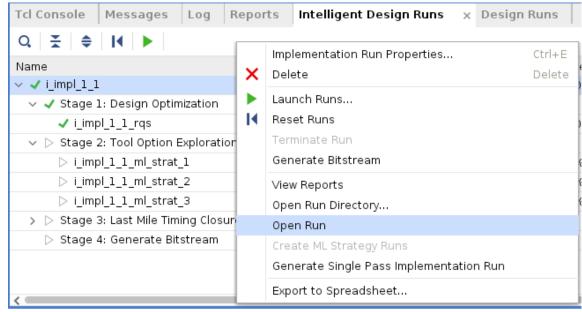

3. Right-click  $i_impl_1_1 \rightarrow Launch Runs$  and select how you normally run jobs. Click **OK**.

- 4. Select **impl\_1\_1** and view the Properties in the Implementation Run Properties window. A PARENT property is set to synth\_1. As is the case with a normal implementation run, there is a dependency on the synthesis run to complete when this is set. If the RTL code is modified, the run will go out of date.

- 5. Click the **Design Runs** tab and confirm that the synth\_1 run is running or finished.

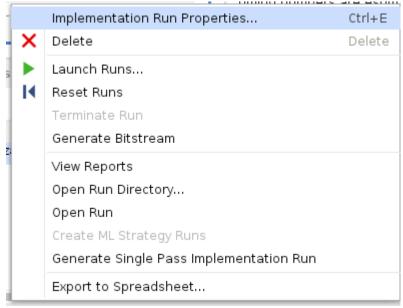

- 6. Click back to Intelligent Design Runs and right-click on the impl\_1\_1 top-level run.

The right-click menu from the top-level run is the main way to control the Intelligent Design Runs. Some options only become available at specific times:

- Reset Runs is only available after a run is launched.

- View Reports is only available after reports are generated.

- Open Run is only available after a run is successfully completed.

- Generate Single Pass Run is only available after a run is successfully completed.

- 7. Select the lower-level run, i\_impl\_1\_1\_rqs, and right-click on it.

When the lower-level run is selected, you can see that there is a reduced set of options. The Open Run Directory and Open Run options are scoped to the lower-level run. If Open Run is selected, the best completed routed run is opened.

### Step 3: Analyzing the Reports and Log File

In this task, you will see where to find reports and analyze runs and intermediate checkpoints from an intelligent design run.

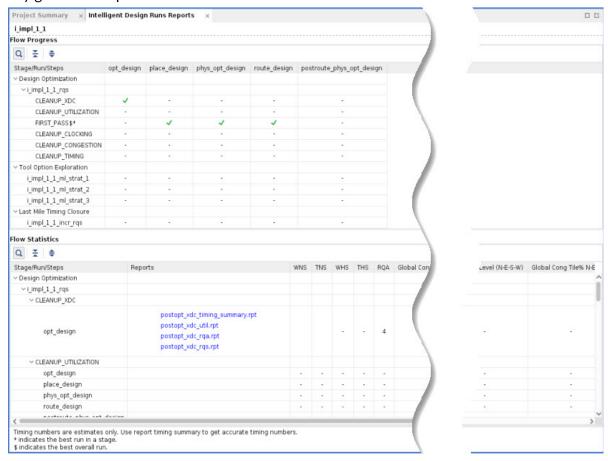

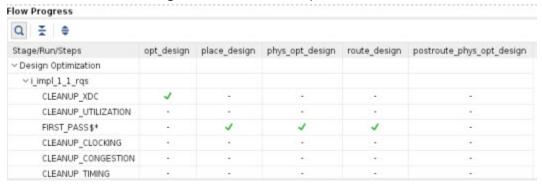

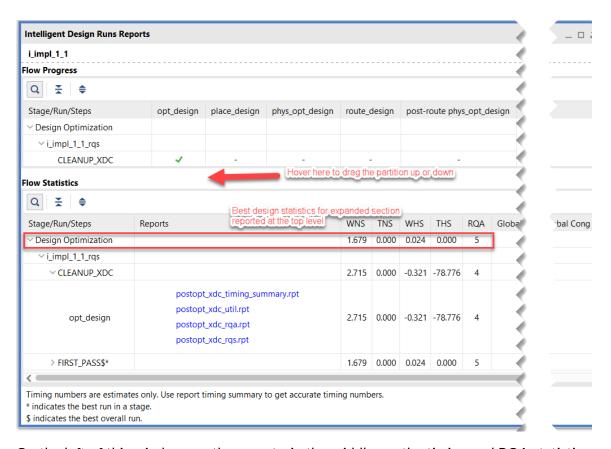

1. If the window is not already open, select **Reports** → **Intelligent Design Run Reports**. This window captures all the metrics that are captured throughout the IDR and provides links to any generated reports.

The report is broken into two windows. The Flow Progress section is in the top half. This details which steps have been run and which steps are running currently. This is more important for an IDR as opposed to a standard implementation run for the following reasons:

- The IDR is a dynamic run, and not all stages are run for every design.

- The steps might be run repeatedly as the run is reset to apply QoR suggestions.

The Flow Statistics section is in the bottom half, and provides the following:

- Hyperlinks to any available reports

- Timing metrics such as WNS/TNS/WHS/THS

- RQA score

- Congestion level and tile % metrics for post-place and post-route designs

- 2. Focus in on the **Flow Progress** section of the report.

- Green ticks indicate a completed stage.

- Hyphens indicate the stage is not run.

- Circles indicate the stage is running.

Because there are no circle icons, you can infer that the run has completed successfully. Note also the FIRST\_PASS step, which is generated for reporting purposes. This special step occurs when there are no utilization or clock suggestions. Only designs without these suggestions have this step.

At the bottom, there is a table footer that describes the meaning of the the \$ and \* notations. These notations help you identify which runs you are opening when you select **Open Run**.

3. Look at the **Flow Statistics** section of the report. This report can be larger, and you can make more space by reducing the divider between the section above and clicking on the arrows to reduce sections of the report.

On the left of this window are the reports, in the middle are the timing and RQA statistics, and on the right are the congestion metrics. Statistics are only available if the flow stage has been run, or if the flow stage generates the statistics. For example, during place, hold statistics are not generated.

- 4. Expand **FIRST\_PASS** and click **postplace\_physopt\_first\_pass\_util.rpt**. Pay attention to the name of this report: postplace\_phys\_opt indicates the implementation step and first\_pass indicates the flow step. When you are ready, close the report.

- 5. In the Intelligent Design Runs window, right-click **impl\_1\_1** and select **Open Run Directory**. In this directory, open the **idr\_flow\_summary.rpt** file. This is the text equivalent to the IDE report. It contains the same information except the links to the report. When you are ready, close the file.

- 6. In the directory explorer, go up one level to the project\_1.runs folder. There is a directory for the main IDR and each of the sub-runs. Click into **impl\_1\_1\_rqs**. Here, you can see all the reports and intermediate checkpoints. When you are ready, close the directory explorer.

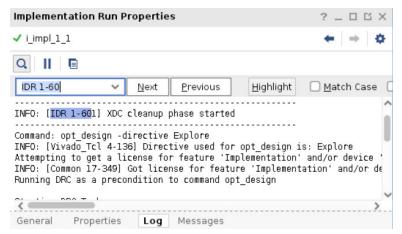

- 7. In the Intelligent Design Runs window, select the top-level run impl\_1\_1.

- 8. In the Implementation Run Properties window, select the **Log** tab and maximize the window.

- 9. Select the search icon and enter "IDR 1-60". Click **Next** multiple times to navigate through the log file. This ID highlights the start and end banners that have been added when you enter and exit a step within Stage 1: Design Optimization.

As the implementation process goes back and forth, it can be difficult to identify which step you are in. These messages can help clarify this.

10. Search for "INFO-TUTORIAL4". This has been inserted by the Tcl script you added in Step 1. This Tcl script is executed every time <code>opt\_design</code> is called. In this case, <code>opt\_design</code> is called only once, so it is similar to a normal flow.

### **Step 4: Final Analysis**

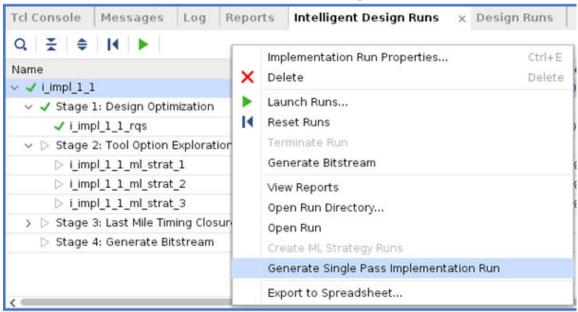

In this task, you will see how to analyze the design and create a single pass run.

1. In the Intelligent Design Runs window, right-click on the top-level run, impl\_1\_1, and then click Open Run. Doing this opens the best overall run from the three stages. This is also the best run from stage 1. Stage 2 and stage 3 were not run with this design. The best run and best stage run are indicated by the \$ and \* notations.

- A device view opens where you can generate reports and analyze the design as you would with a normal implementation run. When you are ready, close the design.

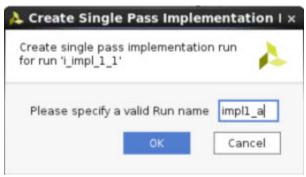

- 2. In the Intelligent Design Runs window, right-click on the top-level **impl\_1\_1\_rqs** and click **Open Run Directory**. This directory has all the intermediate checkpoints from the stage. You can open a new instance of Vivado and open the checkpoints for further analysis. If the DCP is associated with Vivado, you can open the checkpoints by double-clicking on them.