## **Vivado Design Suite Tutorial**

### **Power Analysis and Optimization**

UG997 (v2021.1) June 30, 2021

### **Revision History**

The following table shows the revision history for this document.

| Section Revision Summary                                              |  |  |  |

|-----------------------------------------------------------------------|--|--|--|

| 06/30/2021 Version 2021.1                                             |  |  |  |

| General updates Editorial updates only. No technical content updates. |  |  |  |

### Table of Contents

| Revision History2                                                                 |

|-----------------------------------------------------------------------------------|

| Lab 1: Power Analysis and Optimization Tutorial                                   |

| Software Requirements                                                             |

| Hardware Requirements                                                             |

| Locating Tutorial Design Files                                                    |

| Lab 2: Running Power Analysis in the Vivado Tools                                 |

| Introduction9                                                                     |

| Step 1: Creating a New Project9                                                   |

| Step 2: Synthesizing the Design14                                                 |

| Step 3: Setting Up the Report Power15                                             |

| Step 4: Running Report Power 19                                                   |

| Step 5: Viewing the Power Properties 20                                           |

| Step 6: Editing Power Properties and Refining the Power Analysis                  |

| Step 7: Running Functional Simulation with SAIF Output23                          |

| Step 8: Incorporating SAIF Data into Power Analysis                               |

| Step 9: Implementing the Design                                                   |

| Conclusion                                                                        |

| Lab 3: Running Timing Simulation and Estimating Power                             |

| Introduction                                                                      |

| Step 1: Configuring and Running the Timing Simulation using Vivado Simulator31    |

| Step 2: Running Report Power in Vectorless Mode                                   |

| Step 3: Running Report Power with Vivado Simulator SAIF Data                      |

| Generating a SAIF File using Questa Advanced Simulator                            |

| Step 1: Configuring and Running Timing Simulation in Questa Advanced Simulator 37 |

| Step 2: Running Report Power in Vectorless Mode                                   |

| Step 3: Running Report Power with Questa Advanced Simulator SAIF Data40           |

| Conclusion41                                                                      |

#### Lab 4: Measuring Hardware Power Using the KC705 Evaluation

| Board                                                                | 43 |

|----------------------------------------------------------------------|----|

| Introduction                                                         |    |

| Step 1: Generating a Bit File from the Implemented Design (Non-Power |    |

| Optimization)                                                        | 43 |

| Step 2: Setting Up the KC705 Evaluation Board                        | 44 |

| Step 3: Setting Up the Fusion Digital Power Designer Software        | 45 |

| Step 4: Programming the Bitstream                                    | 46 |

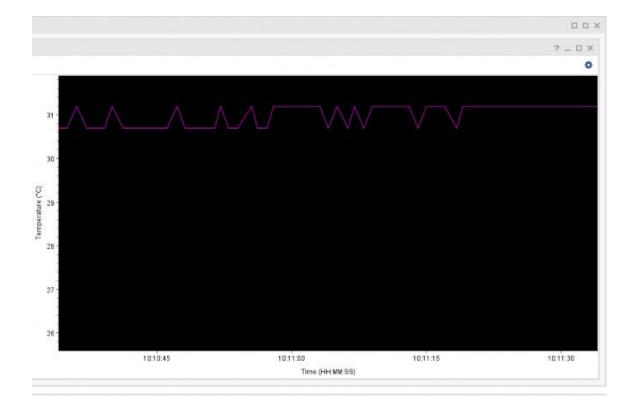

| Step 5: Measuring the Hardware Power Rails                           |    |

| Step 6: Estimating Vectorless Power with Junction Temperature        | 51 |

| Conclusion                                                           | 53 |

#### Lab 5: Measuring Hardware Power Using the KCU105 Evaluation

| Board                                                                   | 54 |

|-------------------------------------------------------------------------|----|

| Introduction                                                            | 54 |

| Step 1: Generating a Bit File from the Implemented Design               | 54 |

| Step 2: Setting up the KCU105 Evaluation Board                          |    |

| Step 3: Configuring the Maxim Digital Power Tool Software               | 56 |

| Step 4: Programming the Bitstream                                       | 57 |

| Step 5: Measuring the Hardware Power Rails                              | 61 |

| Step 6: Estimating the Vectorless Power with Junction Temperature       | 63 |

| Conclusion                                                              | 65 |

|                                                                         |    |

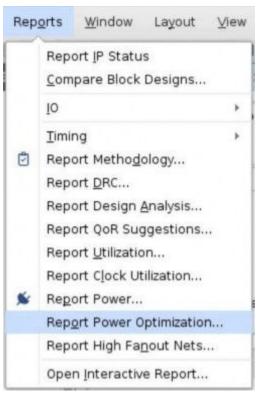

| Lab 6: Performing Power Optimization                                    |    |

| Introduction                                                            |    |

| Step 1: Setting Up Options to Run Power Optimization                    | 66 |

| Step 2: Running report_power_opt to Examine User/Design Specific Power  |    |

| Optimizations                                                           | 68 |

| Step 3: Running report_power to Examine Power Savings                   | 70 |

| Step 4: Turning Off Optimizations on Specific Signals and Rerunning the |    |

| Implementation                                                          | 71 |

| Step 5: Running report_power_opt to Examine Tool Optimizations Again    | 72 |

| Step 6: Saving Power using UltraScale Block RAM in Cascaded Mode        | 73 |

| Conclusion                                                              | 74 |

| Appendix A: Additional Resources and Legal Notices                      | 76 |

|                                                                         |    |

| Xilinx Resources                                                        |    |

| Documentation Navigator and Design Hubs                                 | /6 |

| References76                           |  |

|----------------------------------------|--|

| Please Read: Important Legal Notices77 |  |

I ab 1

### Power Analysis and Optimization **Tutorial**

This tutorial introduces the power analysis and optimization use model recommended for use with the Xilinx<sup>®</sup> Vivado<sup>®</sup> Integrated Design Environment (IDE). The tutorial describes the basic steps involved in taking a small example design from RTL to implementation, estimating power through the different stages, and using simulation data to enhance the accuracy of the power analysis. It also describes the steps involved in using the power optimization tools in the design.

VIDEO: The Vivado Design Suite Quick Take Video: Power Estimation and Analysis Using Vivado shows bow the Vivado Design Suite can help you to estimate power consumption in your design and reviews best practices for getting the most accurate estimation.

VIDEO: The Vivado Design Suite QuickTake Video: Power Optimization Using Vivado describes the factors 0 that affect power consumption in an FPGA, shows how the Vivado Design Suite helps to minimize power consumption in your design, and looks at some advanced control and best practices for getting the most out of Vivado power optimization.

#### Software Requirements

This tutorial requires the latest Vivado Design Suite software is installed. For installation instructions and information, see the Vivado Design Suite User Guide: Release Notes, Installation, and Licensing (UG973).

For hardware power measurement of 7 series devices, the tutorial requires Texas Instruments Fusion Design Power Designer software, which can be downloaded from the following location: http://www.ti.com/tool/fusion\_digital\_power\_designer

For hardware power measurement of UltraScale<sup>™</sup> devices, the tutorial requires Maxim Digital Power Tool software, which can be downloaded from the following location:

https://www.maximintegrated.com/en/products/power/switching-regulators/ MAXPOWERTOOL002.html

#### **Hardware Requirements**

Supported operating systems to run the Vivado Design Suite, and memory recommendations when using the Vivado tools, are described in the Vivado Design Suite User Guide: Release Notes, Installation, and Licensing (UG973).

#### Hardware Requirements for 7 Series Devices

- The hardware power measurements for 7 series devices (needed in Lab 4: Measuring Hardware Power Using the KC705 Evaluation Board), require a Xilinx Kintex®-7 FPGA KC705 Evaluation Kit. You can find information on the Evaluation Kit at this location: Xilinx Kintex®-7 FPGA KC705 Evaluation Kit

- For power measurements through TI Power Regulators (needed in Lab 4: Measuring Hardware Power Using the KC705 Evaluation Board), use the Texas Instruments USB Interface Adapter. You can find information on the USB Interface Adapter at this location:

www.ti.com/lit/ml/sllu093/sllu093.pdf

#### Hardware Requirements for UltraScale Devices

- The hardware power measurements in UltraScale devices (needed in Lab 5: Measuring Hardware Power Using the KCU105 Evaluation Board), requires a Xilinx Kintex<sup>®</sup> UltraScale<sup>™</sup> FPGA KCU105 Evaluation Kit. You can find information on the Evaluation Kit at the following location: Xilinx Kintex UltraScale FPGA KCU105 Evaluation Kit

- For power measurements through Maxim Digital Power Tool (needed in Lab 5: Measuring Hardware Power Using the KCU105 Evaluation Board), use the Maxim Power interface adapter. You can find information on the interface adapter at the following location: https:// www.maximintegrated.com/en/products/power/switching-regulators/ MAXPOWERTOOL002.html

#### **Locating Tutorial Design Files**

1. Download the reference design files from the Xilinx website:

ug997-vivado-power-analysis-optimization-tutorial.zip

2. Extract the zip file contents into any write-accessible location.

This tutorial refers to the location of the extracted ug997-vivado-power-analysisoptimization-tutorial.zip file contents as <Extract\_Dir>.

**IMPORTANT!** You will modify the tutorial design data while working through this tutorial. Use a new copy of the original data each time you start this tutorial.

The ug997-vivado-power-analysis-optimization-tutorial.zip file includes a readme file which contains the details and version history of the design files along with the folders of 7 series and UltraScale design files.

#### 7 Series Tutorial Design Files

You can find a separate 7 series folder containing the 7 series tutorial design files in the contents of the zip file.

The following table describes the contents of the 7 series tutorial design files:

| Directories/Files             | Description                                                          |

|-------------------------------|----------------------------------------------------------------------|

| /src                          | Contains the design HDL and testbench for the functional simulation. |

| /src/dut_fpga.v               | Top module for the design.                                           |

| /src/bram_tdp.v               | Other design blocks - synthesized module.                            |

| /src/bram_top.v<br>/src/dut.v |                                                                      |

| dut_fpga_kc705.xdc            | Contains clocking and timing constraints for the design.             |

| /src/testbench.v              | Testbench for simulating the design.                                 |

#### **UltraScale Device Tutorial Design Files**

You can find a separate UltraScale<sup>™</sup> folder containing the UltraScale device tutorial design files in the contents of the zip file.

The following table describes the contents of the UltraScale device tutorial design files:

| Directories/Files          | Description                                               |  |

|----------------------------|-----------------------------------------------------------|--|

| /src                       | Contains the design HDL and testbench for the simulation. |  |

| /src/dut_fpga.v            | Top module for the design.                                |  |

| /src/dut.v                 | Other design blocks.                                      |  |

| /src/Cascade_bram.v        |                                                           |  |

| /src/Noncascade_bram.v     |                                                           |  |

| /src/bram_top_cascade.v    |                                                           |  |

| /src/bram_top_noncascade.v |                                                           |  |

| /src/bram_tdp_cas.v        |                                                           |  |

| /src/bram_tdp_noncas.v     |                                                           |  |

| dut_fpga_kcu105.xdc        | Contains clocking and timing constraints for the design.  |  |

| /src/testbench.v           | Testbench for simulating the design.                      |  |

#### Table 1: Example table

Lab 2

# Running Power Analysis in the Vivado Tools

#### Introduction

In this lab, you will learn about the Power Analysis and Optimization features in the Vivado<sup>®</sup> IDE. The lab will take you through the steps of project creation and power analysis at the synthesis stage, using the Vivado Report Power feature in vectorless mode. It will also demonstrate using the SAIF file generated from behavioral simulation for Vivado report power analysis.

You will analyze power in the Vivado IDE. Then you will examine some of the major features in the Power window and closely examine some power specific Tcl commands. You will also learn to create a Switching Activity Interchange Format (SAIF) file by simulating the design in the timing simulation stage using both the Vivado simulator and Questa Advanced Simulator.

You will also learn how to achieve Power Optimization after <code>opt\_design</code> in the Vivado IDE. You will examine the power optimization report and selectively turn power optimizations ON or OFF on specific signals, nets, modules, or hierarchy.

#### **Step 1: Creating a New Project**

To create a project, use the New Project wizard to name the project, to add RTL source files and constraints, and to specify the target device.

**Note:** Throughout this tutorial, Xilinx<sup>®</sup> 7 series example design is used to explain the process of configuring, implementing, estimating the power through different stages, and using simulation data to enhance the accuracy of the power analysis. For UltraScale<sup>™</sup> device design, most of the steps are similar to 7 series. Additional information, wherever necessary, is provided for UltraScale devices.

On Linux, do the following.

- 1. Go to the directory where the lab materials are stored:

- cd <Extract\_Dir>/7\_series (for 7 series devices) or

- cd <Extract\_Dir>/UltraScale (for UltraScale devices)

- 2. Launch the Vivado IDE: vivado

| A                                                                           | Vivado 2021.1                                                    | + _ 3 ×   |

|-----------------------------------------------------------------------------|------------------------------------------------------------------|-----------|

| Eile Flow Tools Window Help Q- Quick Access                                 |                                                                  |           |

|                                                                             |                                                                  | £ XILINX. |

| Quick Start<br>Create Project ><br>Open Project ><br>Open Example Project > | Recent Projects Project_1 Project_1 Promovular/Desktopsproject_1 |           |

| Tasks<br>Manage IP ><br>Open Hardware Manager ><br>Vivado Store >           |                                                                  |           |

| Learning Center                                                             | ·                                                                |           |

| Tcl Console                                                                 |                                                                  | ? _ 🗆 🖒 X |

|                                                                             |                                                                  | )°        |

On Windows, do the following.

3. Launch the Vivado IDE by selecting Start → All Programs → Xilinx Design Tools → Vivado 2021.x → Vivado 2021.x (x denotes the latest version of Vivado 2021 IDE).

As an alternative, click the Vivado 2021.x Desktop icon to start the Vivado IDE.

The Vivado IDE Getting Started page contains links to open or create projects and to view documentation.

- 4. In the Getting Started page, click **Create New Project** to start the New Project wizard.

- 5. Click **Next** to continue to the next screen.

| A-New Project                       |                                                                                  |        | <b></b> |

|-------------------------------------|----------------------------------------------------------------------------------|--------|---------|

| Project Name<br>Enter a name for yo | our project and specify a directory where the project data files will be stored. |        | A       |

| Project name:                       | power_tutorial1                                                                  |        | 0       |

| Project location:                   | C:Nivado_power_tutorial                                                          |        | 0       |

| Create project                      | ct subdirectory                                                                  |        |         |

| Project will be cre                 | reated at: C:/vivado_power_tutorial/power_tutorial1                              |        |         |

|                                     |                                                                                  |        |         |

|                                     |                                                                                  |        |         |

|                                     |                                                                                  |        |         |

|                                     |                                                                                  |        |         |

|                                     |                                                                                  |        |         |

|                                     |                                                                                  |        |         |

|                                     |                                                                                  |        |         |

| •                                   | < Back Next >                                                                    | Elnish | Cancel  |

- 6. In the Project Name page, name the new project power\_tutorial1 and enter the project location (C:\Vivado\_Power\_Tutorial). Make sure to check the Create project subdirectory option and click Next.

- 7. In the Project Type page, specify the type of project to create as **RTL Project**, make sure to uncheck the **Do not specify sources at this time** option, and click **Next**.

- 8. In the Add Sources page:

- a. Set Target Language to Verilog and Simulator language to Mixed.

- b. Click the Add Files button.

- c. In the Add Source Files dialog box, navigate to the <Extract\_Dir>/7\_series/src directory for 7 series devices or <Extract\_Dir>/UltraScale/src for UltraScale devices.

- d. Select all of the Verilog (.v) source files, and click OK.

- e. In the Add Sources page, change the HDL Source For the  ${\tt testbench.v}$  file to Simulation only.

| +. | [::]             | +   +                                                 |                |                        |    |                                       |  |

|----|------------------|-------------------------------------------------------|----------------|------------------------|----|---------------------------------------|--|

|    | Index            | Name                                                  | Library        | HDL Source For         |    | Location                              |  |

| 0  | 1                | bram_tdp.v                                            | xil_defaultlib | Synthesis & Simulation | ٠  | C:/vivado_power_tutorial/7_series/src |  |

|    | 2                | bram_top.v                                            | xil_defaultlib | Synthesis & Simulation |    | C:/vivado_power_tutorial/7_series/src |  |

| 0  | 3                | dut.v                                                 | xil_defaultlib | Synthesis & Simulation | *  | C:Nivado_power_tutorial/7_series/src  |  |

|    | 4                | dut_fpga.v                                            | xil_defaultlib | Synthesis & Simulation | ٠  | C:/vivado_power_tutorial/7_series/src |  |

|    | 5                | testbench.v                                           | xil_defaultlib | Simulation only        | ٠  | C:/vivado_power_tutorial/7_series/src |  |

|    | opy <u>s</u> our | add RTL includ<br>ces into project<br>es from subdiri |                |                        | IS | <u>C</u> reate File                   |  |

- f. Verify that the files are added and **Copy sources into project** is checked. Click **Next**.

- 9. In the Add Constraints (optional) page, click Add Files and select dut\_fpga\_kc705.xdc in the file browser. In the directory structure, you will find the dut\_fpga\_kc705.xdc file below the /src folder.

For UltraScale devices, select dut\_fpga\_kcu105.xdc in the file browser. In the directory structure, you will find the dut\_fpga\_kcu105.xdc file below the /src folder.

- 10. Click Next to continue.

- 11. In the Default Part page, click **Boards** and select Kintex-7 KC705 Evaluation Platform for 7 series or Kintex UltraScale KCU105 Evaluation Platform for UltraScale devices. Then click **Next**.

**TIP:** When you specify a board, you are also specifying the part you are targeting for your design, in this case an xc7k325tffg900-2 FPGA for 7 series or xcku040-ffva156-2-e FPGA for UltraScale devices.

12. Review the New Project Summary page. Verify that the data appears as expected, per the steps above, and click **Finish**.

Note: It might take a moment for the project to initialize in the Vivado IDE.

| power submit [Chinedo power                                                                                            | storisk'power_tutoriall/power_tutorialLogs] - Vivodo 2017.3                                                                                                                                         |                                                                                                                                                                   | 0.0                                                                |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| The Eq. Lion Tools R                                                                                                   | indose Lagaul gaw galp Qr Datch Access                                                                                                                                                              |                                                                                                                                                                   | Ready                                                              |

| ■, + + 0 0 X                                                                                                           | ▶, # 0 Σ % # #                                                                                                                                                                                      |                                                                                                                                                                   | E Oetault Laeaul                                                   |

| Now Navagelos 🗧 8 🤉                                                                                                    | PROJECT BARACER - power_information                                                                                                                                                                 |                                                                                                                                                                   | ?                                                                  |

| Y PROJECT NANAGER                                                                                                      | Sources 2 - D D X                                                                                                                                                                                   | Project Summary                                                                                                                                                   | 7.0 S X                                                            |

| O Swittings<br>Add Bources                                                                                             | Q 2 0 + 0 0                                                                                                                                                                                         | Settings 1.4                                                                                                                                                      |                                                                    |

| Canguage Temptales<br>Ø IP Catalog                                                                                     | Concentration (1)     Out of the second (1)                                                 | Projectioner power Microsoft<br>Projectiocater Criterios Jacobspower Microsoft<br>Productionaly: Kiteso 7                                                         |                                                                    |

| <ul> <li>PINTEGRATOR</li> <li>Greate Block Design</li> <li>Open Block Design</li> <li>Germania Block Design</li> </ul> | Benecky Lizzeisz Campis Order                                                                                                                                                                       | Propertia ant kineter 2022/00 E-assuation Platform bioCh325/thg900-02<br>Top models name: date topa<br>Target language: liveling<br>Simulation language: liveling |                                                                    |

| Y SARLATION<br>Nan Simalakin                                                                                           | Properties 7                                                                                                                                                                                        | Boald Part Display name - Kintee-7 KG726 Busication Platform                                                                                                      | 5557676777                                                         |

| <ul> <li>RTL ANALYSIS</li> <li>Open Distorated Design</li> </ul>                                                       | Sarked are object to see programme                                                                                                                                                                  | Board anthrane alline.com Is/73/5part/1.5<br>Connections<br>Researchere anth<br>Researchere anth<br>URL several for comite/103                                    |                                                                    |

| <ul> <li>SYNTHESE</li> <li>Ratification</li> </ul>                                                                     |                                                                                                                                                                                                     | Ecard oveniew: Kinte 7 KC715 Exclusion Platform                                                                                                                   | #1.1777                                                            |

| > Open Sutherbed Design                                                                                                | Tol Console Mexicages Log Reports Design Russ. ×                                                                                                                                                    |                                                                                                                                                                   | ? _ 0 0                                                            |

| MPLEMENTATION     Run Implementation     Open implementation                                                           | Q. Ξ. ÷     14     ≪     >>     +     %       Name     Constraints     Status     Whit     THS     WHS       ~ D syntl_1     constraint     Not stated       D imp[_1     constraint     Not stated | THS THAT THAT WAY Fare Routes LUT IF BRUES UNAN USY Stat Elegand                                                                                                  | Shalegy<br>Veado Synthesis Debadle (W<br>Veado Implementation Debu |

| PROCRAW AND DEBUG     If Convrats Bitstream                                                                            |                                                                                                                                                                                                     |                                                                                                                                                                   |                                                                    |

| > Open Hardesare Manager                                                                                               | 8                                                                                                                                                                                                   |                                                                                                                                                                   |                                                                    |

13. In the Settings dialog box (**Tools** → **Settings** → **Tool Settings** → **Project**), enter the tutorial project directory in the Specify project directory field, so that all reports are saved in the tutorial project directory. Then click **OK**.

| 2-                                                              | Project                                     |      | 2 |

|-----------------------------------------------------------------|---------------------------------------------|------|---|

| Project Settings<br>General                                     | Specify various settings related to project | ts.  | , |

| Simulation                                                      | Default Project Directory                   |      |   |

| Elaboration<br>Synthesis<br>Implementation<br>Bitstream         | Start in directory (C:/Users/venkal)        | as)  |   |

| Fool Settings                                                   | Specify project directory: C:/pro           |      |   |

| Project                                                         | Target Language                             |      |   |

| IP Defaults<br>Source File<br>Display<br>WebTalk                | Verilog VHDL                                |      |   |

| Help                                                            | Reopen last project on startup              |      |   |

| <ul> <li>Text Editor</li> <li>3rd Party Simulators</li> </ul>   | Number of recent projects to list:          | 10 🗘 |   |

| > Colors                                                        | Number of recent directories to list        | 15 🗘 |   |

| Selection Rules<br>Shortcuts<br>Strategies<br>> Window Behavior | Number of recent files to list              | 10 ‡ |   |

| _                                                               |                                             |      |   |

Now, the design is ready for synthesis.

#### **Step 2: Synthesizing the Design**

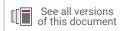

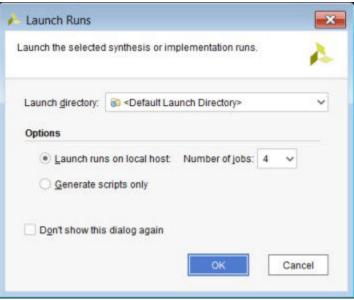

1. Click **Run Synthesis** in the Flow Navigator. In the Launch Runs dialog box that appears, click **OK**.

2. The Synthesis Completed dialog box appears after synthesis has completed on the design.

3. Open the synthesized design by selecting **Open Synthesized Design** in the Synthesis Completed dialog box and clicking **OK**.

#### **Step 3: Setting Up the Report Power**

The Vivado IDE allows you to specify input data to the Report Power tool to enhance the accuracy of the power analysis.

In the Vivado IDE, you can configure thermal, environmental, and power supply options to mimic the board level settings as closely as possible. For information on setting these options, see the *Vivado Design Suite User Guide: Power Analysis and Optimization* (UG907).

- 1. In the main menu bar, select **Reports**  $\rightarrow$  **Report Power**.

- 2. Examine the Environment tab in the Report Power dialog box.

| Res <u>u</u> lts name: | power_1            |                  |           |           |             | C |

|------------------------|--------------------|------------------|-----------|-----------|-------------|---|

| Environment            | Power Supply       | Switching 9      | Output    |           |             |   |

| Device Setting         | S                  |                  |           |           |             | î |

| Temp grad              | le:                | extended         | ~         | ]         |             |   |

| Pro <u>c</u> ess:      |                    | maximum          | ~         |           |             |   |

| Environment S          | ettings            |                  |           |           |             |   |

| Output Loa             | d:                 |                  | 0 ‡       | pF        | [0 - 10000] |   |

| Unctio                 | n temperature:     |                  | 25.679    | °C        |             |   |

| Ambient te             | mperature:         | -                | 25 🌲      | °C        |             |   |

| Effectiv               | e ƏJ <u>A</u> :    |                  | 1.42      | 2 °C/W    | [0 - 100]   |   |

| Airflow:               |                    | 250              | ~         | LFM       |             |   |

| <u>H</u> eat sink:     | <u>H</u> eat sink: |                  | um Prof 🗸 |           |             |   |

| ϑSA:                   |                    |                  | °C/W      | [0 - 100] |             |   |

| <u>B</u> oard sele     | ction:             | medium (10"x"    | 10") 🗸    |           |             |   |

| Number of              | board layers:      | 12to 15 (12 to 1 | 5 Layer 🗸 |           |             |   |

| JB:                    |                    | 1                | 2.5 🌲     | °C/W      | [0 - 100]   |   |

| C Board tom            | o o roturo:        |                  | nc 🔺      |           | 1 55 4001   | ~ |

| Legend                 |                    |                  |           |           |             |   |

3. In the Environment tab, set Process to **maximum** for a worst case power analysis. Examine the Power Supply tab.

**IMPORTANT!** By default, Vivado Report Power uses nominal values for voltage supply sources. Voltage is a large factor contributing to both static and dynamic power. For the most accurate analysis, ensure that actual voltage values are entered for each supply. Similarly, ensure temperature and other environmental factors match actual operating conditions.

| lesylts name:     | power_1      |   |            |        |   |

|-------------------|--------------|---|------------|--------|---|

| Environment       | Power Supply |   | Switching  | Output |   |

| Settings          |              |   |            |        |   |

| Vccint:           | 1.000 ‡      | v | [0.970 -   | 1.030} | î |

| Vccaux            | 1.800 \$     | v | [1.710 -   | MICHT. |   |

| Vcco <u>3</u> 3:  | 3.300 \$     | v | [3.000 - 3 |        |   |

| Vcco25:           | 2.500 🗘      | v | (2.380 - ) | 2.630] |   |

| Vcco <u>1</u> 8:  | 1.800 🌲      | v | [1.710 -   | 1.900] |   |

| Vcco1 <u>5</u> :  | 1.500 ‡      | v | [1.430 -   | 1.580] |   |

| Vcco135:          | 1.350 🗘      | v | [1.300 -   | 1.400] |   |

| Vcco12            | 1.200 🌻      | v | [1.140 -   | 1.260J |   |

| Vccaux_io:        | 1.800 ‡      | v | [1.710 -   | 1.890} |   |

| Vccbra <u>m</u> : | 1.000 ‡      | v | [0.970 -   | 1.030] |   |

| MGTAVcc:          | 1.000 🌲      | ۷ | [0.950 -   | 1.050] |   |

| MGTAVII:          | 1.200 🗘      | v | [1.140 -   | 1.260] |   |

| MGTVccaux         | 1.800 🌻      | ۷ | [1.710 -   | 1.890] |   |

| MGTZVccl:         | 1.075 ‡      | v | [1.050 -   | 1.100) |   |

| Legend            | +            |   |            |        | ~ |

4. In the Switching tab, expand **Constrained Clocks** and examine the constrained clocks in the design.

, **IMPORTANT!** Make sure all the relevant clocks in the design are constrained. All the design clocks must be defined using *create\_clock* or *create\_generated\_clock* XDC constraints, so that Report Power recognizes the clocks.

Default toggle rate is set to 12.5% and Default Static Probability is set to 0.5. This will be applied to primary input ports (non-clock) and block box outputs.

| stimate power c                 | onsumption based       | d on the netli | st design and | 1 part xc7k325t | tg900-2.  |   |

|---------------------------------|------------------------|----------------|---------------|-----------------|-----------|---|

| Results name:                   | power_1                |                |               |                 |           |   |

| Environment                     | Power Supply           | Switching      | Output        |                 |           |   |

| Simulation Se                   | ttings                 |                |               |                 |           |   |

| Simulation                      | activity file (.saif): | 1              |               |                 |           | ] |

| Default Activit                 | y Settings             |                |               |                 |           |   |

| Default tog                     | gle rate:              | 12.5           | [0 - 100]     |                 |           |   |

| Default Sta                     | tic Probability:       | 0.5            | [0.0 - 1.0]   |                 |           |   |

| Enable Rate S                   | ettings                |                |               |                 |           |   |

|                                 |                        | Static Proba   | bility        | Toggle Rate     |           |   |

| BRAM Port                       | Enable:                |                | [0.0 - 1.0]   |                 | [0 - 100] |   |

| BRAM Writ                       | e Enable:              |                | [0.0 - 1.0]   |                 | [0 - 100] |   |

| Bidi Outpu                      | Port Enable:           |                | [0.0 - 1.0]   |                 | [0 - 100] |   |

| Toggle Rate S                   | ettings                |                |               |                 |           |   |

|                                 |                        | Static Proba   | bility        | Toggle Rate     |           |   |

| Primary Ou                      | itputs:                |                | [0.0 - 1.0]   |                 | [0 - 100] |   |

| Logic                           |                        |                |               |                 |           |   |

| Register                        | s:                     |                | [0.0 - 1.0]   |                 | [0 - 100] |   |

| Shift Reg                       | gisters:               |                | [0.0 - 1.0]   |                 | [0 - 100] |   |

| Distribut                       | ed RAMs:               |                | [0.0 - 1.0]   |                 | [0 - 100] |   |

| LUTs:                           |                        |                | [0.0 - 1.0]   |                 | [0 - 100] |   |

| DSPs:                           |                        |                | [0.0 - 1.0]   |                 | [0 - 100] |   |

| Block R/                        | Ws:                    |                | [0.0 - 1.0]   |                 | [0 - 100] |   |

| GTs                             |                        |                |               |                 |           |   |

| RX Data                         |                        |                | [0.0 - 1.0]   |                 | [0 - 100] |   |

| TX Data:                        |                        |                | [0.0 - 1.0]   |                 | [0 - 100] |   |

| <ul> <li>Constrained</li> </ul> | Clocks                 |                |               |                 |           |   |

| Clock                           |                        |                | Period        |                 |           |   |

| sys_clk_in_p                    |                        |                | 5 ns          |                 |           |   |

| clk_0                           |                        |                | 5 ns          |                 |           |   |

| clkout0                         |                        |                | 10 ns         |                 |           |   |

- 5. In the Output tab of the Report Power dialog box, specify the **Output text file** as power\_1.pwr.

- Specify the Output XPE file as power\_1.xpe. After creating this file when Report Power runs, you can import the file and results into the Xilinx Power Estimator. For information on importing the file in to the Xilinx Power Estimator, see the Xilinx Power Estimator User Guide (UG440).

- Specify the RPX file to write the results of the Report Power command. The saved RPX file

can be reloaded using the Reports → Open Interactive Report command to provide

interaction/cross-probing with the open design.

| Report Power     | onsum   | ption base | d on the netlis | t design and | part xc7k325 | tfg900-2. | × |

|------------------|---------|------------|-----------------|--------------|--------------|-----------|---|

| Results name:    | powe    | er_1       |                 |              |              |           | 0 |

| Environment      | Powe    | er Supply  | Switching       | Output       |              |           |   |

| Output text file | 0       | power_1    | pwr             |              |              | ¢         |   |

| Output XPE file  | e:      | power_1    | xpe             |              |              | C         |   |

| J Output RP      | X file: | C:/proj/p  | ower_1.rpx      |              |              | C         |   |

|                  |         |            |                 |              |              |           |   |

|                  |         |            |                 |              |              |           |   |

|                  |         |            |                 |              |              |           |   |

|                  |         |            |                 |              |              |           |   |

|                  |         |            |                 |              |              |           |   |

#### **Legends in Report Power Tool**

The following legends appear consistently in the Report Power tool:

- **Constraint:** Displays when the nets are defined as clock with timer constraints. The defined frequency of a clock determines the switching activity.

- Stimulation: Displays when the nets with switching activities are derived from simulation's .saif file.

- User Defined: Displays when the nets with user set switching activities are derived from set\_switching\_activity power Tcl command.

- Estimated: Displays when the nets with switching activities are generated by report\_power vectorless propagation engine.

- **Default:** Displays when the nets include default switching activities. If you use set\_switching\_activity on input port nets or on internal nets before running report\_power (vectorless propagation), the report tool displays the default.

#### **Step 4: Running Report Power**

1. Click **OK** on the Report Power dialog box.

This runs the report\_power command.

2. Examine the power report, power\_1, generated in the Power window in the Vivado IDE.

*Note*: Due to continuous accuracy improvements in the Vivado tools, the actual power numbers you see might be slightly different than the ones that appear in the following figures.

| Power                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7 _ 0 2 3 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| a ¥ ≑ c ∎"                                                                                                                                                                                                                                                                                      | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

| Setings<br>Summary (1.379 W)<br>Power Supply<br>V Ulication Details<br>Hierarchical (0.918 W)<br>Clocks (0.011 W)<br>State (0.051 W)<br>Date (0.051 W)<br>Clock Reate (0 W)<br>SetReate (0 W)<br>SetReate (0 W)<br>Logic (0.011 W)<br>ERVM (0.714 W)<br>Clock Manager (0.117 W)<br>KD (0.004 W) | Power estimation from Synthesized netlist Adduly<br>derived form constraints files, simulation files or<br>vectories analysis. Note: these early estimates can<br>change after implementation.<br>Total On Chip Power: 1.379 W<br>Junction Temperature: 27.4 °C,<br>Thermail Margin: 57.6 °C (30.3 W)<br>Effective 2UA: 1.3 °C.W<br>Power supplied to off-chip devices: 0.W<br>Confidence level: 8654 um<br>Launch Power Constraint Addiagr to find and fix<br>invalid switching activity |           |

- 3. Examine the power breakdown in the power report by block type (Logic, BRAM, I/O, etc.).

- 4. Examine the power supply breakdown in the Power Supply view.

| Power                                   |               |             |           |             |            |  | ? _ D 2               |

|-----------------------------------------|---------------|-------------|-----------|-------------|------------|--|-----------------------|

| Q 😤 单 C 🕍 "                             | Power Supply  |             |           |             |            |  | 🔂 Getault 🛛 Calculate |

| Sellings                                | Supply Source | Voltage (v) | Total (A) | Dynamic (A) | Static (A) |  |                       |

| Summary (5.379 W)                       | Vecint        | 1.000       | 1.041     | 0.745       | 0.295      |  |                       |

| Power Supply                            | Voceux        | 1.800       | 0.152     | 0.067       | 0.085      |  |                       |

| <ul> <li>Utilization Details</li> </ul> | V00033        | 3 300       | 0.042     | 0.000       | 0.042      |  |                       |

| Herarchical (0.918 W)                   | Voco25        | 2.500       | 0.000     | 0.000       | 0.000      |  |                       |

| Clocks (0.011 W)                        | Vcco18        | 1.800       | 0.000     | 0.000       | 0.000      |  |                       |

| <ul> <li>Signala (0.061 W)</li> </ul>   | Vcco15        | 1500        | 0.000     | 0.000       | 0.000      |  |                       |

| Date (0.061 V/)                         | Veco135       | 1350        | 0.000     | 0.000       | 0.000      |  |                       |

| Clock Enable (0 W)                      | Voco 12       | 1.200       | 0.000     | 0.000       | 0.000      |  |                       |

| SeoReaet (0 W)                          | Vocaux_io     | 1.800       | 0.000     | 0.000       | 0.000      |  |                       |

| Logic (0.011 W)                         | Vocbram       | 1.000       | 0.065     | 0.054       | 0.013      |  |                       |

| BRAM (0.714 W)                          | MGTAVec       | 1.000       | 0.000     | 0.000       | 0.000      |  |                       |

| Clock Manager (0.157 W)                 | MGTAVI        | 1.200       | 0.000     | 0.000       | 0.000      |  |                       |

| <b>VO</b> (0.004 W)                     | MGTVccaux     | 1.800       | 0.000     | 0.000       | 0.000      |  |                       |

|                                         | Vocado        | 1.800       | 0.030     | 0.000       | 0.030      |  |                       |

5. Examine the hierarchical breakdown of the power in the **Utilization Details** → **Hierarchical** view.

| a 🛛 e c 📕 "                                                                               | Q 📱 Hierarchical                                    |                   |            |             |          |           |          |                   |          |        |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------|------------|-------------|----------|-----------|----------|-------------------|----------|--------|

| Setings                                                                                   | Utilization                                         | Name              | Clocks (W) | Signals (W) | Data (W) | Logic (W) | BRAM (W) | Clock Manager (W) | MICH (W) | NO (W) |

| Summary (1.370 W)                                                                         | <ul> <li>E 0.918 W (67% of total)</li> </ul>        | agat_tub 🎉        |            |             |          |           |          |                   |          |        |

| Power Supply                                                                              | <ul> <li>Compared 0.795 W (58% of total)</li> </ul> | (tut) tub 📳       | 0.009      | 0.061       | 0.061    | 0.011     | 0.714    | <0.001            | <0.001   | <0.001 |

| Utilization Details                                                                       | > 🔲 0.079 W (6% of total)                           | 🗐 gen_dutj0] br   | 0.001      | 0.005       | 0.006    | 0.001     | 0.071    | =0.001            | <0.001   | -0.001 |

| Hierarchical (0.918 W)                                                                    | > 0.079 W (0% of total)                             | 🗿 gen_dut(1).br   | 0.001      | 0.005       | 0.006    | 0.001     | 0.071    | <0.001            | <0.001   | -0.001 |

| Clocks (0.011 W)                                                                          | > 0.079 W (0% of total)                             | gen_dut(2).br     | 0.001      | 0.005       | 0.006    | 0.001     | 0.071    | <0.001            | <0.001   | <0.001 |

| <ul> <li>Signals (0.051 W)</li> <li>Dats (0.051 W)</li> <li>Clock Enable (0 W)</li> </ul> | > 0.079 W (5% of total)                             | gen_dut(3).br     | 0.001      | 0.005       | 0.006    | 0.001     | 0.071    | +0.001            | <0.001   | -0.001 |

|                                                                                           | > 0.079 W (0% of total)                             | I gen_dut[4].br   | 0.001      | 0.006       | 0.006    | 0.001     | 0.071    | <0.001            | <0.001   | +0.001 |

|                                                                                           | > 0.079 W (5% of total)                             | al gen_dut(6).br  | 0.001      | 0.006       | 0.006    | 0.001     | 0.071    | +0.001            | +0.001   | +0.001 |

| SebReset (0 W)                                                                            | > 0.079 W (6% of total)                             | 📓 gen_dul(8) br.  | 0.001      | 0.006       | 0.006    | 0.001     | 0.071    | *0.001            | +0.001   | -0.001 |

| Logic (0.041 W)                                                                           | > 0.079 W (5% of local)                             | gen_dul(?).br     | 0.001      | 0.006       | 0,006    | 0.001     | 0.071    | +0.001            | +0,001   | -0.001 |

| BRAW (0.714 W)<br>Clock Manager (0.117 W)                                                 | > 0.078 W (8% of total)                             | 🧾 gen_dut(ii) br  | 0.001      | 0.006       | 0.006    | 0.001     | 0.071    | *0.001            | +0.001   | -0.001 |

|                                                                                           | > @ 0.079 W (8% of total)                           | 📓 gen_dul(9) br   | 0.001      | 0,006       | 0.006    | 0.001     | 0.071    | +0.001            | +0.001   | +0.001 |

| UC (0.004 W)                                                                              | \$ <0.001 W (<1% of fotal)                          | Lesf Cells (8)    |            |             |          |           |          |                   |          |        |

|                                                                                           | 0.124 W (9% of total)                               | E Leaf Cells (18) |            |             |          |           |          |                   |          |        |

6. Examine the Clocks view and the various Signals views (Data, Clock Enable, and Set/Reset).

| Q 🔮 🖨 C 📕 "                             | Q 🔮 Clocks                                  |               |                 |        |                         |               |            |       | Constr      | aint 🗄 | Calculated |

|-----------------------------------------|---------------------------------------------|---------------|-----------------|--------|-------------------------|---------------|------------|-------|-------------|--------|------------|

| Settings                                | Utilization                                 | Name          | Frequency (MHz) | Buffer | Clock Buffer Enable (%) | Enable Signal | Bel Fanout | Sites | FanoutiSite | Type   |            |

| Summary (1.379 W)                       | <ul> <li>E 0.011 W (1% of total)</li> </ul> | 🙀 dut_fpga    |                 |        |                         |               |            |       |             |        |            |

| Power Supply                            | > 0.009 W (1% of Islar)                     | J cikoutó     | 100.000         | NA     | NA                      | NAVA          | 842        | 611   | 1.378       | NIA    |            |

| <ul> <li>Utilization Details</li> </ul> | > 10.002 W (<1% of lotal)                   | ∫ dk_0        | 200.000         | NIA    | NIA                     | NA            | 2          | 2     | 1.000       | NØ.    |            |

| Hierarchical (0.918-W)                  | > 1<0.001 W (<1% of total)                  | _ sys_dk_in_p | 200.000         | NIA    | N/4                     | NA            | 2          | 2     | 1.000       | NiA    |            |

| Clocks (0.011 W)                        |                                             |               |                 |        |                         |               |            |       |             |        |            |

| Signals (0.061 W)                       |                                             |               |                 |        |                         |               |            |       |             |        |            |

| Data (0.061 W)                          |                                             |               |                 |        |                         |               |            |       |             |        |            |

| Clock Enable (0.W)                      |                                             |               |                 |        |                         |               |            |       |             |        |            |

| SetReset (0 W)                          |                                             |               |                 |        |                         |               |            |       |             |        |            |

| Logic (0.011 W)                         |                                             |               |                 |        |                         |               |            |       |             |        |            |

| BRAM (0.714 W)                          |                                             |               |                 |        |                         |               |            |       |             |        |            |

| Clear Manager () 417740                 |                                             |               |                 |        |                         |               |            |       |             |        |            |

| Clock Manager (0.117 W)                 |                                             |               |                 |        |                         |               |            |       |             |        |            |

| UD (8 004 W)                            |                                             |               |                 |        |                         |               |            |       |             |        |            |

|                                         |                                             |               |                 |        |                         |               |            |       |             |        |            |

|                                         |                                             |               |                 |        |                         |               |            |       |             |        |            |

#### **Step 5: Viewing the Power Properties**

This step shows how you can get the display of static probability and toggle rate for a signal in property window.

- 1. Note the total power (Total On-Chip Power) in the Power Report Summary view.

- 2. Click the Set/Reset item in the Power Report.

- 3. Click on the dut/dut\_reset signal.

| wer                                       |             |                  |                     |         |        |              |         |            |           |           | ?          |

|-------------------------------------------|-------------|------------------|---------------------|---------|--------|--------------|---------|------------|-----------|-----------|------------|

| 2 ₹ ♦ C 📕 "                               | QI          | SetReset         |                     |         |        |              |         |            | Attribute | Estimated | Calculated |

| Settings                                  | Utilization | Name             | Signal Rate (Mtr/s) | % High  | Fanout | Slice Fanout | Clock   | Logic Type |           |           |            |

| Summary (1.370 W)                         | ~ DW        | Gil dut_fpga     |                     |         |        |              |         |            |           |           |            |

| Power Supply                              | 0.W         | _f_dut/dut_reset | 0.000               | 0.000   | 530    | 0            | clkout0 | FFLUT      |           |           |            |

| Utilization Details                       | 0 W O       | J led_OBUF       | 0.000               | 100,000 | 3      | 0            | clkout0 | FEIIOLUT   |           |           |            |

| Hierarchical (0.918 W)                    |             |                  |                     |         |        |              |         |            |           |           |            |

| Clocks (0.011 W)                          |             |                  |                     |         |        |              |         |            |           |           |            |

| ✓ Signals (0.061 W)                       |             |                  |                     |         |        |              |         |            |           |           |            |

| Data (0.061 W)                            |             |                  |                     |         |        |              |         |            |           |           |            |

| Clock Enable (0.W)                        |             |                  |                     |         |        |              |         |            |           |           |            |

| Set/Reset (0 W)                           |             |                  |                     |         |        |              |         |            |           |           |            |

| Logic (0.011 W)                           |             |                  |                     |         |        |              |         |            |           |           |            |

| BRAM (0.714 W)<br>Clock Manager (0.117 W) |             |                  |                     |         |        |              |         |            |           |           |            |

|                                           |             |                  |                     |         |        |              |         |            |           |           |            |

| UD (8 004 W)                              |             |                  |                     |         |        |              |         |            |           |           |            |

|                                           |             |                  |                     |         |        |              |         |            |           |           |            |

|                                           |             |                  |                     |         |        |              |         |            |           |           |            |

4. Note that there is a Power view in the Net Properties window that displays net properties for the dut/dut\_reset signal. Click on Load Power Properties to get the power information the first time.

| Legend: Estimated                             | ⇔   ⇒   <b>0</b> |

|-----------------------------------------------|------------------|

| Toggle rate: 0.0 %<br>Static probability: 0.0 |                  |

| Static probability: 0.0                       |                  |

|                                               |                  |

| Legend: 📃 Estimated                           |                  |

|                                               |                  |

| Edit Properties                               |                  |

5. Note the Toggle rate is 0% and the Static probability is 0 for the dut/dut\_reset signal, which indicates that reset is always deasserted in the design.

# Step 6: Editing Power Properties and Refining the Power Analysis

Assume the reset is asserted for 10% of the cycles in this design. Switching activity can be set accordingly to re-estimate the power.

- 1. In the Net Properties window, click the **Edit Properties** button.

- 2. In the **Edit Power Properties** dialog box, change the Toggle rate to 4% and the Static probability to 0.1.

| et power properties for du | t_reset. |            |

|----------------------------|----------|------------|

| Output                     |          |            |

| Toggle rate:               | 4.000 🗘  | %          |

|                            |          | 0.0 - 1.0] |

| Static probability:        | 0.1 🌲 [  | 0.0 - 1.0] |

- 3. Click OK.

- 4. In the Net Properties window, observe that the Toggle Rate and Static Probability values turn a different color to indicate that they are user defined.

| Net Properties                                | ? _ D .7 ×                               |

|-----------------------------------------------|------------------------------------------|

| .F dut_reset                                  | + - O                                    |

| Output                                        |                                          |

| Toggle rate: 4.0 %<br>Static probability: 0.1 |                                          |

|                                               | Edit Properties                          |

| General Properties Connectivi                 | Power Aliases Cell Pins Nodes Tiles Pips |

You can also observe the equivalent Tcl command executed in the Tcl Console.

| cl Console x Micessajos Log Reports Design Runs Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5 – D D |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Q. 茶 ゆ 川 田 麗 首                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

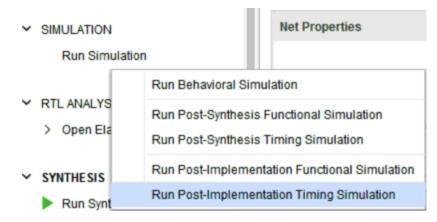

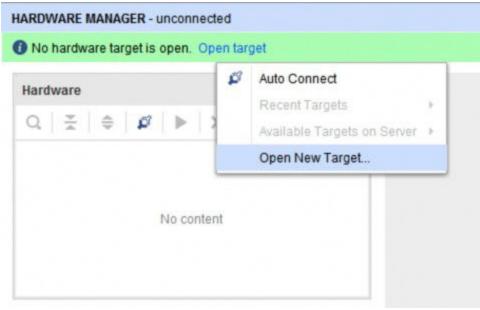

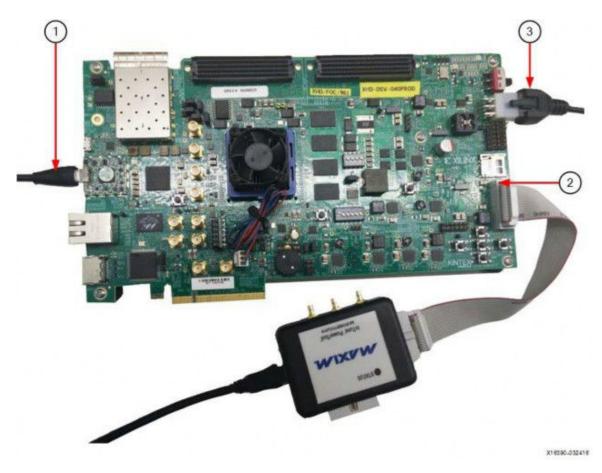

| Command: report power -file Cr/DorshNMm/power 1.pwr -xpc Cr/DorshNMm/power 1.apc -rpm Cr/peo//power 1.rpm -mame power 1<br>Running Vector-Leas Activity Propagation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ^       |