# **Vivado Design Suite Tutorial**

### Designing with IP

UG939 (v2021.1) July 19, 2021

## **Revision History**

The following table shows the revision history for this document.

| Section         | Revision Summary                     |

|-----------------|--------------------------------------|

| 07/19/2021 V    | ersion 2021.1                        |

| General updates | Validated for Xilinx release 2021.1. |

## Table of Contents

| Revision History                                    | 2  |

|-----------------------------------------------------|----|

| Chapter 1: Designing with IP Overview               | 5  |

| Introduction                                        |    |

| Tutorial Description                                | 5  |

| Hardware and Software Requirements                  |    |

| Locating and Preparing the Tutorial Design Files    |    |

| Chapter 2: Lab 1: Customizing the FIFO Generator    | 7  |

| Introduction                                        | 7  |

| Step 1: Open the Project                            | 7  |

| Step 2: Customize the FIFO Generator                | 10 |

| Step 3: Instantiate IP into the Design              | 16 |

| Step 4: Synthesize the Design                       | 19 |

| Conclusion                                          | 21 |

| Chapter 3: Lab 2: Creating and Managing Reusable IP | 23 |

| Introduction                                        |    |

| Step 1: Start a Manage IP session                   |    |

| Step 2: Customize the FIFO Generator                |    |

| Step 3: Customize the Clocking Wizard               |    |

| Step 4: Use Third-Party Simulators                  |    |

| Step 5: Add Additional IP                           |    |

| step 6: Use Third-Party Synthesis Tools             |    |

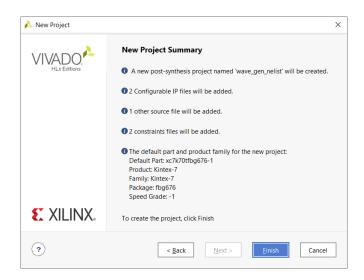

| Step 7: Create a Netlist Project                    |    |

| Conclusion                                          |    |

| Chapter 4: Lab 3: Scripting the Project Mode        | 42 |

| Introduction                                        |    |

| Step 1: Create a Project                            |    |

| Step 2: Add RTL Source Files                        |    |

| Step 3: Add XDC Constraints                         |    |

Step 4: Add Existing IP......45

| Step 5: Disable the IP XDC Files                   |    |

|----------------------------------------------------|----|

| Step 6: Upgrade an IP                              | 47 |

| Step 7: Setup Design Runs for IP                   | 49 |

| Step 8: Launch Synthesis and Implementation        | 50 |

| Step 9: Run the Script                             | 51 |

| Conclusion                                         | 53 |

| Chapter 5: Lab 4: Scripting the Non-Project Mode   | 54 |

| Introduction                                       | 54 |

| Step 1: Read the Design Source Files               | 54 |

| Step 2: Add Existing IP                            | 55 |

| Step 3: Disable XDC Files                          | 57 |

| Step 4: Upgrade IP                                 | 58 |

| Step 5: Create DCP for IP                          | 60 |

| Step 6: Run Synthesis                              | 60 |

| Step 7: Run Implementation                         | 61 |

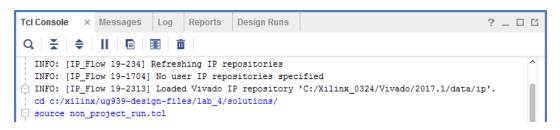

| Step 8: Run the Script                             | 63 |

| Conclusion                                         | 65 |

| Appendix A: Additional Resources and Legal Notices | 66 |

| Xilinx Resources                                   | 66 |

| Documentation Navigator and Design Hubs            | 66 |

| References                           | 66 |

|--------------------------------------|----|

| Please Read: Important Legal Notices | 67 |

|                                      |    |

## Designing with IP Overview

#### Introduction

**XILINX**

MPORTANT! This tutorial requires the use of the Kintex<sup>®</sup>-7 family of devices. You must update your Vivado<sup>®</sup> tools installation if you do not have this device family installed. See Vivado Design Suite User Guide: Release Notes, Installation, and Licensing (UG973) for more information on Adding Design Tools or Devices.

The Vivado Design Suite provides multiple ways to use IP in a design. You can customize and add it from the IP catalog into a project. You can also create and reference a repository of customized IP in either a project or non-project based flow, with full scripting capabilities as well.

The Vivado Design Suite provides an IP-centric design flow that helps you quickly turn designs and algorithms into reusable IP.

The Vivado IP catalog is a unified IP repository that provides the framework for the IP-centric design flow. This catalog consolidates IP from all sources including: Xilinx<sup>®</sup> IP, IP obtained from third parties, and end-user designs targeted for reuse as IP into a single environment.

The Vivado IP packager is a unique design reuse feature based on the IP-XACT standard. The IP packager provides any Vivado user the ability to package a design at any stage of the design flow and deploy the core as system-level IP.

VIDEO: You can also learn more about the creating and using IP cores in the Vivado Design Suite QuickTake videos: Configuring and Managing Custom IP and Customizing and Instantiating IP.

#### **Tutorial Description**

This tutorial contains several labs as described in the following:

- Lab 1: Open a modified version of the Xilinx wave\_gen example design that is missing a FIFO; locate and customize the IP in the catalog; and instantiate the IP into the design.

- Lab 2: Create and customize IP using the Manage IP flow. Create a project, include an IP from the IP catalog as the top-level source; customize and verify the IP. Optionally, use the customized IP as a black box in a third-party synthesis flow.

- Lab 3: Write and run a Tcl script using the Vivado<sup>®</sup> Design Suite to create a project, add IP, upgrade IP, disable IP sources, and generate output products including synthesized design checkpoints (DCP).

- Lab 4: Write and run a Non-Project Tcl script using the Vivado Design Suite to read in IP sources, upgrade IP, disable IP sources, and generate output products including a design checkpoint (DCP) file.

#### Hardware and Software Requirements

This tutorial requires that the 2021.1 Vivado Design Suite software release or later is installed.

See the Vivado Design Suite User Guide: Release Notes, Installation, and Licensing (UG973) for a complete list and description of the system and software requirements.

#### Locating and Preparing the Tutorial Design Files

There are separate project files and sources for each of the labs in this tutorial. You can find the design files for this tutorial on the Xilinx website: Reference Design Files.

- 1. Download the zipped reference file from the Xilinx website.

- 2. Extract the zip file contents into any write-accessible location on your hard drive, or network location.

The extracted source directory is referred to as <Extract\_Dir> throughout this tutorial.

**RECOMMENDED:** You will modify the tutorial design data while working through this tutorial. Use a new copy of the  $< Extract_Dir>$  directory each time you start this tutorial.

### Chapter 2

## Lab 1: Customizing the FIFO Generator

#### Introduction

In this lab, you open a Vivado<sup>®</sup> project and customize the FIFO Generator IP core. You will generate the output products for the IP and instantiate it in the design RTL source. Finally, you will synthesize the project.

### **Step 1: Open the Project**

- From the Getting Started page, select Open Project and browse to: <extract\_dir>/ lab\_1/project\_wave\_gen\_ip.

- On Windows, select Start → All Programs → Xilinx Design Tools → Vivado 2021.1 → Vivado 2021.1 → Vivado 8 Design Suite.

- 3. As an alternative, click the Vivado 2021.1 Desktop icon to start the Vivado IDE.

The Vivado IDE Getting Started page, shown in the following figure, contains links to open or create projects and to view documentation.

| Quick Start<br>Create Project ><br>Open Project ><br>Open Example Project >             |

|-----------------------------------------------------------------------------------------|

| Tasks<br>Manage IP ><br>Open Hardware Manager ><br>Xilinx Tcl Store >                   |

| Learning Center Documentation and Tutorials > Quick Take Videos > Release Notes Guide > |

4. From the Open Project window, shown in the following figure, select **project\_wave\_gen\_ip.xpr**, and click **OK**.

|                                                 |                       | Open Project              |                 | ×      |

|-------------------------------------------------|-----------------------|---------------------------|-----------------|--------|

| Look in: 📄 project_wave_                        | _gen_ip               | ~                         | 1 🗠 🖵 🖵 🍐 📾 🗙 C |        |

| project_wave_gen_ip.ca                          |                       | Recent Directories        |                 |        |

| project_wave_gen_ip.hw                          |                       |                           |                 | ~      |

| project_wave_gen_ip.ip_ project_wave_gen_ip.sim | _                     | File Preview              |                 |        |

| project_wave_gen_ip.src                         |                       | Select a file to preview. |                 |        |

| project_wave_gen_ip.xpr                         |                       |                           |                 |        |

| File <u>n</u> ame:                              |                       |                           |                 |        |

| Files of type: Vivado and F                     | PlanAhead Project Fil | es (.xpr, ppr)            |                 | ~      |

|                                                 |                       |                           | ОК              | Cancel |

The design loads and you see the Vivado IDE in the default layout view, with the Project Summary information as shown in the following figure.

| Sources                                                                                                                                                        |                                                          | ? _ 🗆 🗆 ×    | Proje                           | ect Summa                                                                                                        | ary                                  |                                                                                           |                    |          |           |                    |                                                                 |        |           |                                                                                                                                 | ? 🗆 🖸 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------|---------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------|--------------------|----------|-----------|--------------------|-----------------------------------------------------------------|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------|-------|

| Q   ¥   <b>≑   +</b>                                                                                                                                           | 2 0                                                      | •            | Ove                             | rview   D                                                                                                        | ashboard                             |                                                                                           |                    |          |           |                    |                                                                 |        |           |                                                                                                                                 |       |

| <ul> <li>Design Sources (</li> <li>Verlog Heade</li> <li>Verlog Heade</li> <li>Constraints (2)</li> <li>Simulation Sources</li> <li>Utility Sources</li> </ul> | r (1)<br>(wave_gen.v) (13)                               |              | Pro<br>Pro<br>Pro<br>Top<br>Tan | tings Ed<br>ject name:<br>ject locatio<br>duct family<br>ject part:<br>o module na<br>get langua<br>julator lang | P<br>n: //<br>: K<br>ame: w<br>ge: V | oroject_wave_<br>ug939-design<br>Gntex-7<br>ic7k70tfbg67<br>vave_gen<br>/erilog<br>4lixed | n-files/lab_       | _1/proje | ct_wave_ç | gen_ip             |                                                                 |        |           |                                                                                                                                 |       |

|                                                                                                                                                                |                                                          |              | Syn                             | thesis                                                                                                           |                                      |                                                                                           |                    |          |           | Im                 | plemen                                                          | tation |           |                                                                                                                                 |       |

|                                                                                                                                                                |                                                          |              | Par<br>Stra<br>Rep              | ssages:                                                                                                          | 3V:                                  | Not started<br>No errors of<br>xc7k70tfbg6<br>Vivado Synt<br>Vivado Synt<br>None          | 76-1<br>nesis Defa | aults    | orts      | M<br>Pi<br>St<br>R | tatus:<br>lessages<br>art:<br>trategy:<br>eport Str<br>icrement | ategy: | mentation | Not started<br>No errors or warnings<br>xc7k70tfbg676-1<br>Vivado Implementation Defaults<br>Vivado Implementation Default Repo | rts   |

| Hierarchy IP Source                                                                                                                                            | es Libraries C                                           | ompile Order |                                 |                                                                                                                  |                                      |                                                                                           |                    |          |           |                    |                                                                 |        |           |                                                                                                                                 |       |

| Tcl Console Mess                                                                                                                                               | ages Log Repo                                            | rts Design R | uns ×                           |                                                                                                                  |                                      |                                                                                           |                    |          |           |                    |                                                                 |        |           |                                                                                                                                 | ? _ 🗆 |

| Q 素 ≑ !∢                                                                                                                                                       | «                                                        | %            |                                 |                                                                                                                  |                                      |                                                                                           |                    |          |           |                    |                                                                 |        |           |                                                                                                                                 |       |

| Name Cons<br>∨ ⊳ synth_1 cons                                                                                                                                  | traints Status<br>trs_1 Not started<br>trs_1 Not started | WNS TNS      | WHS TH                          | HS TPWS                                                                                                          | Total Pow                            | er Failed F                                                                               | toutes L           | UT FF    | BRAM      | URAM               | DSP                                                             | Start  | Elapsed   | Run Strategy<br>Vivado Synthesis Defaults (Vivado Synth<br>Vivado Implementation Defaults (Vivado                               |       |

Because this is an RTL project, you can run behavioral simulation, elaborate the design, launch synthesis and implementation, and generate a bitstream for the device. The Vivado IDE also offers a one-button flow to generate a bitstream, which will automatically launch synthesis and implementation. For more information, see the *Vivado Design Suite User Guide: Using the Vivado IDE* (UG893).

#### **Step 2: Customize the FIFO Generator**

1. From the Flow Navigator, select IP Catalog.

The Xilinx IP catalog displays in a new tab.

- 2. You can work with the IP catalog in a variety of ways. You can search using keywords in the search box or browse through the catalog in the various categories.

- 3. Type fifo in the search box.

The search results narrow the list of IP definitions displayed in the catalog.

4. From the **Memories & Storage Elements** → **FIFOs** group select **FIFO Generator**, as shown in the following figure.

| IP Catalog                                 |                   |            | ? _ 🗆 🔊  | ×        |

|--------------------------------------------|-------------------|------------|----------|----------|

| Cores   Interfaces                         |                   |            |          |          |

| Q   ¥   ♦  ₮   •G   ♪   ♪   @   ■          |                   |            |          | ¢        |

| Search: Q-                                 |                   |            |          |          |

| Name ^ 1                                   | AXI4              | Status     | License  |          |

| > 🗁 Debug & Verification                   |                   |            |          | ^        |

| > 🗁 Digital Signal Processing              |                   |            |          |          |

| > 🗁 Embedded Processing                    |                   |            |          |          |

| > 🗁 FPGA Features and Design               |                   |            |          |          |

| > 🕞 Kernels                                |                   |            |          |          |

| > 🗁 Math Functions                         |                   |            |          |          |

| 🗸 🗁 Memories & Storage Elements            |                   |            |          |          |

| ₱ ECC                                      |                   | Production | Included |          |

| 🗸 🗁 FIFOs                                  |                   |            |          |          |

| FIFO Generator                             | AXI4, AXI4-Stream | Production | Included | 1        |

| > 🗁 Memory Interface Generators            |                   |            |          |          |

|                                            |                   |            |          | <u> </u> |

| Details                                    |                   |            |          |          |

| Select an IP or Interface or Repository to | o see details     |            |          |          |

5. Right-click and select Customize IP, or double-click the selected IP.

The FIFO Generator customization window opens, as shown in the following figure. There is a schematic symbol for the selected core displayed on the left. The schematic symbol changes as you customize the IP.

*Note:* This is not the original setting; it shows the change that you make to the customization.

| Show disabled ports              | Component Name char_fif                |                                                     |               |                               |          |          |     |        |       |  |  |  |  |

|----------------------------------|----------------------------------------|-----------------------------------------------------|---------------|-------------------------------|----------|----------|-----|--------|-------|--|--|--|--|

|                                  | Basic Native Ports                     | Basic Native Ports Status Flags Data Counts Summary |               |                               |          |          |     |        |       |  |  |  |  |

|                                  | Interface Type                         |                                                     |               |                               |          |          |     |        |       |  |  |  |  |

|                                  | Native      AXI                        | Memory Mapped                                       | O AXI Stream  | n                             |          |          |     |        |       |  |  |  |  |

|                                  |                                        |                                                     |               |                               |          |          |     |        |       |  |  |  |  |

|                                  | Fifo Implementation                    | Independent Clock                                   | ks Block RAM  | ~                             |          |          |     |        |       |  |  |  |  |

|                                  | Synchronization Stages                 |                                                     |               |                               |          |          |     |        |       |  |  |  |  |

|                                  | -,                                     |                                                     |               |                               |          |          |     |        |       |  |  |  |  |

|                                  | FIFO Implementation O                  | ptions                                              |               |                               |          |          |     |        |       |  |  |  |  |

| + FIFO_WRITE                     | Supported Features                     |                                                     |               |                               |          |          |     |        |       |  |  |  |  |

| + FIFO_READ<br>rst wr_rst_busy - |                                        |                                                     |               | Memory                        |          |          | (-) |        |       |  |  |  |  |

| - wr_clk                         |                                        |                                                     |               | Туре                          | (1)<br>√ | (2)<br>√ | (3) | (4)    | (5)   |  |  |  |  |

| - rd_clk                         |                                        | Common Clock (CLK) Block                            |               |                               |          |          |     | 1      | √     |  |  |  |  |

|                                  | Common Clock (CLK                      |                                                     | -             | istributed RAM                | _        | √        |     |        |       |  |  |  |  |

|                                  | Common Clock (CLK<br>Common Clock (CLK |                                                     |               | hift Register<br>uilt-in FIFO |          | 1        | 4   | 4      | √     |  |  |  |  |

|                                  | Independent Clock                      |                                                     |               | Block RAM                     | ~        | <br>✓    | Y   | ·<br>· | <br>✓ |  |  |  |  |

|                                  | Independent Clocks                     |                                                     |               | istributed RAM                |          | •<br>√   |     | •      | Y     |  |  |  |  |

|                                  |                                        |                                                     | Built-in FIFO |                               | 1        | 1        | 1   | 4      |       |  |  |  |  |

|                                  | (1) Non-symmetric as                   |                                                     |               |                               |          | ,        | ,   | ,      | ,     |  |  |  |  |

|                                  | (2) First-Word Fall-Th                 |                                                     |               | nite data widths)             |          |          |     |        |       |  |  |  |  |

|                                  |                                        | -                                                   |               |                               |          |          |     |        |       |  |  |  |  |

|                                  | (3) Uses Built-in FIFO                 | primitives                                          |               |                               |          |          |     |        |       |  |  |  |  |

|                                  | (4) ECC support                        |                                                     |               |                               |          |          |     |        |       |  |  |  |  |

- 6. Zoom into the schematic symbol using mouse strokes with the left mouse button, just like in the Device window.

- 7. If checked, disable the **Show Disabled Ports** checkbox to hide unused ports on the symbol.

- 8. Above the symbol, click the **Documentation** menu to examine the options for viewing available information.

The Documentation menu lets you open the PDF file datasheet for the IP, open the change log to review the revision history of the core, or open an Internet browser to navigate to the IP webpage, or view any Answer Records related to the IP.

The IP Location specifies the location to which to save the IP customization (XCI) file and any generated output products. By default, these are saved inside the project directory structure in the project\_wave\_gen\_ip/project\_wave\_gen.gen/ip directory.

The Switch to Defaults option resets the configuration options back to the default settings.

- 9. In the Customize IP dialog box, change the following:

- a. **Component Name** to **char\_fifo** from the default name.

The Basic tab defines the interface type, memory type, and other implementation IP options.

- b. Default Interface Type of Native.

- c. Change Fifo Implementation to Independent Clocks Block RAM.

The customization window should now look like the preceding figure.

- 10. Select the **Native Ports** tab to set the Read Mode, Data Port Parameters, ECC and Output Register Options, and configure Initialization.

- a. Set Read Mode to First Word Fall Through.

- b. Set the Write Width to 8 bits.

Setting the Write Width automatically changes the Read Width to match when you click in the Read Width field.

- c. Click the Read Width field to automatically change it to 8 bits.

- 11. Leave everything else with the default settings on this tab.

- 12. Examine the fields of the Status Flags and Data Counts tabs.

These fields configure other options for the FIFO Generator. For this design, leave everything with the default settings.

13. Click OK.

The Generate Output Products dialog box opens for you to generate required files, as shown in the following figure.

| À Generate Output Products                       | ×                  |

|--------------------------------------------------|--------------------|

| The following output products will be generated. | $\mathbf{\lambda}$ |

|                                                  |                    |

| Preview                                          |                    |

| Q 素 ♠                                            |                    |

| ∽ ♀ ∎ char_fifo.xci (OOC per IP)                 | ^                  |

| Instantiation Template                           |                    |

| Synthesized Checkpoint (.dcp)                    |                    |

| Behavioral Simulation                            |                    |

| Change Log                                       | ~                  |

| Synthesis Options                                |                    |

| O <u>G</u> lobal                                 |                    |

| Out of context per IP                            |                    |

|                                                  |                    |

| Run Settings                                     |                    |

| Number of jobs: 4                                |                    |

| ? Apply Ggnerate Can                             | cel                |

14. Leave Out of context per IP selected, and click the **Generate** button.

#### 15. Click **OK**.

By default, the Vivado IDE generates the Synthesized Checkpoint (DCP) file.

To create this DCP, You see that the Vivado tools have added an OOC module run for the  $char_fifo$  IP to the Design Runs window, and launched the run to synthesize the IP, as shown in the following figure.

| Design Runs                  |             |                        |     |     |     |     |      |             |               |     |    |       |      |     |       |          | ?_D』×         |

|------------------------------|-------------|------------------------|-----|-----|-----|-----|------|-------------|---------------|-----|----|-------|------|-----|-------|----------|---------------|

| Q                            | >   >   +   | %                      |     |     |     |     |      |             |               |     |    |       |      |     |       |          |               |

| Name                         | Constraints | Status                 | WNS | TNS | WHS | THS | TPWS | Total Power | Failed Routes | LUT | FF | BRAMs | URAM | DSP | Start | Elapsed  | Run Strategy  |

| synth_1 (active)             | constrs_1   | Not started            |     |     |     |     |      |             |               |     |    |       |      |     |       |          | Vivado Synth  |

| ▷ impl_1                     | constrs_1   | Not started            |     |     |     |     |      |             |               |     |    |       |      |     |       |          | Vivado Imple  |

| 🗸 📄 Out-of-Context Module Ru | ıs          |                        |     |     |     |     |      |             |               |     |    |       |      |     |       |          |               |

| char_fifo_synth_1            | char_fifo   | synth_design Complete! |     |     |     |     |      |             |               | 82  | 1  | 0.50  | 0    | 0   | 10/   | 00:02:09 | Vivado Synthe |

The out-of-context (OOC) run creates the DCP for the specified IP customization, which does the following:

- Allows the IP to be complete with regard to synthesis.

- Ensures that the integrity of the core is preserved in the current design.

- Reduces synthesis time for the top-level design in future iterations of the design flow.

For more information on OOC runs, and the use of DCP files, see the Vivado Design Suite User Guide: Designing with IP (UG896)

**IMPORTANT!** Generate the DCP file to reduce synthesis time for the top-level design. Do not change the default synthesis setting for the IP Design Runs.

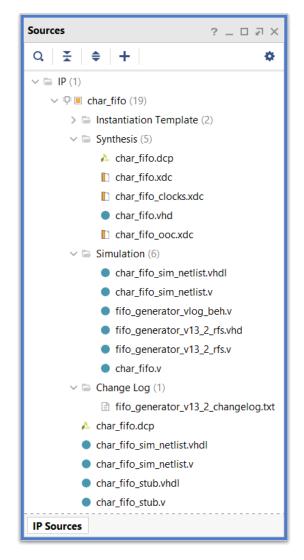

The FIFO now appears in the Sources > IP Sources view, as shown in the following figure.

16. In the Sources window > IP Sources tab, examine the output products produced for the FIFO Generator customization. If you had not generated the output products, they would generate automatically when you launch the top-level synthesis run.

The FIFO IP is added to the design sources, but is not yet instantiated into your design. It is added at the same level as the top-level wave\_gen module in the Hierarchy tab, and appears in the Block Sources folder in the Libraries and Compile Order tabs.

The FIFO Generator customization includes instantiation templates (this tutorial uses char\_fifo.veo), synthesis constraints, VHDL entity and architecture definition, Verilog simulation files, and the synthesized design checkpoint (DCP).

*Note*: A char\_fifo.vho template also exists, but will not be used in this design.

**Note:** Because the FIFO IP was originally defined in VHDL, the entity and architecture are added as VHDL source files. However, because Verilog is the target language for the current project, the instantiation template is a VEO file for instantiating the VHDL FIFO entity into the Verilog design. You can also customize and add IP to your design using Tcl commands.

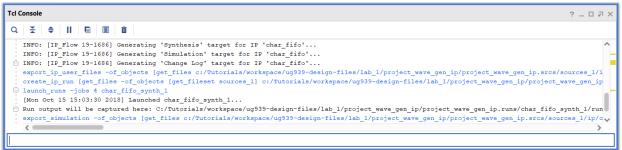

17. Examine the Tcl Console in the Vivado IDE, as shown in the following figure and review the Tcl commands used to add the FIFO Generator core to your project.

The following commands are related to the creation, customization, generation, and launch of the IP run:

- The create\_ip command adds the IP into the current project.

- The set\_property command sets the various configuration options selected in the Customize IP dialog box. Scroll up in the screen to see this command.

- The generate\_target command creates the specified output products for the customized IP. Scroll up in the screen to see this command.

- The create\_ip\_run command creates the Out-of-Context synthesis run for the customized IP.

- The launch\_runs command runs synthesis on the IP customization to produce the synthesis DCP file, functional simulation netlists, and stub files for third-party synthesis tools to infer a black box for the IP.

See the Vivado Design Suite Tcl Command Reference Guide (UG835) for specific information on the different Tcl commands used in this tutorial.

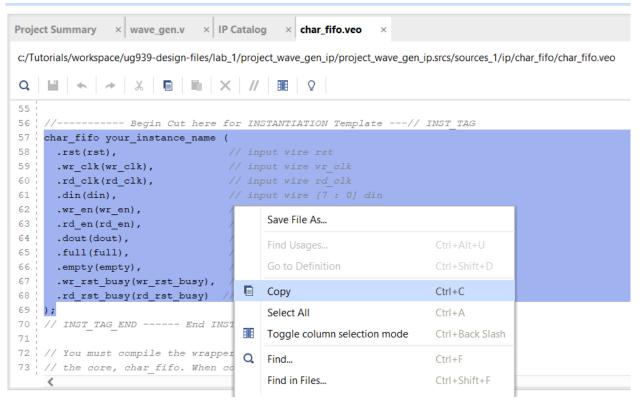

#### Step 3: Instantiate IP into the Design

You will now instantiate the IP customization into the design by copying and pasting the Verilog Instantiation Template into the appropriate Verilog source file in your project and modifying the signals.

- 1. In the IP Sources tab of the Sources window, click the **Instantiation Template** to expand it and then double-click the **char\_fifo.veo** file to open the template in the Vivado<sup>®</sup> Text Editor.

- 2. Scroll down to line 57 of the template file, and select and copy the module instantiation text, as shown in the following figure.

Next, you paste the instantiation template into the appropriate RTL source file. In this case, you paste the module into the top-level of the design, in the  $wave_gen.v$  source file.

3. Open this file for editing from the Hierarchy tab of the Sources view, by double-clicking wave\_gen.v. The following figure shows the file.

- 4. Go to line 337, which contains a comment stating the Character FIFO should be instanced at this point.

- 5. Paste the template code into the file as shown in the following figure.

Because it is only a template for the module, you need to do some local editing to make the module work in your design.

| Project    | Summary × char_fifo                      | .veo    | × wave_gen.v * ×                    |                       |                                       |

|------------|------------------------------------------|---------|-------------------------------------|-----------------------|---------------------------------------|

| C:/Tuto    | orials/workspace/ug939-des               | sign-fi | iles/lab_1/project_wave_gen_ip/proj | ect_wave_gen_ip.srcs/ | /sources_1/imports/verilog/wave_gen.v |

| Q.         | ₩ 🛧 🕕 🗶 🗉                                |         | h 🗙 // 🎟 🔉                          |                       |                                       |

| 334        | );                                       | •       | Save File                           | Ctrl+S                |                                       |

| 335        |                                          |         | Save File As                        |                       |                                       |

| 336        |                                          |         | Save All Files                      |                       |                                       |

| 337<br>338 | // Instantiate th<br>char fifo your inst |         |                                     |                       |                                       |

| 339 ¦      | .rst(rst),                               |         | Find Usages                         | Ctrl+Alt+U            |                                       |

| 340        | .wr_clk(wr_clk),                         |         | Go to Definition                    | Ctrl+Shift+D          |                                       |

| 341        | .rd_clk(rd_clk),                         | •       | Undo                                | Ctrl+Z                |                                       |

| 342<br>343 | .din(din),                               |         |                                     |                       |                                       |

| 343        | .wr_en(wr_en),<br>.rd en(rd en),         | 1       | Redo                                | Ctrl+Shift+Z          |                                       |

| 345        | .dout(dout),                             | x       | Cut                                 | Ctrl+X                |                                       |

| 346        | .full(full),                             |         | Сору                                | Ctrl+C                |                                       |

| 347        | .empty(empty),                           |         | Paste                               | Ctrl+V                |                                       |

| 348<br>349 | .wr_rst_busy(wr_r<br>.rd rst busy(rd r   |         | Duplicate Selection                 | Ctrl+D                |                                       |

| 350        | );                                       |         | Select All                          | Ctrl+A                |                                       |

| 351        |                                          | _       |                                     |                       |                                       |

| 352        |                                          |         | Toggle column selection mode        | Ctrl+Back Slash       |                                       |

|            | <                                        | Q       | Find                                | Ctrl+F                |                                       |

a. In line 338 (approximately) above where you pasted the instantiation, change the module name from <code>your\_instance\_name</code> to <code>char\_fifo\_i0</code>.

b. Change the wire names as follows, to connect the ports of the module into the design:

```

char_fifo char_fifo_i0 (

.rst(rst_i), // input wire rst

.wr_clk(clk_rx), // input wire wr_clk

.rd_clk(clk_tx), // input wire rd_clk

.din(char_fifo_din), // input wire [7 : 0] din

.wr_en(char_fifo_wr_en), // input wire wr_en

.rd_en(char_fifo_rd_en), // input wire rd_en

.dout(char_fifo_dout), // output wire [7 : 0] dout

.full(char_fifo_full), // output wire full

.empty(char_fifo_empty), // output wire empty

.wr_rst_busy(), // output wire wr_rst_busy

.rd_rst_busy() // output wire rd_rst_busy

);

```

6. In the Text Editor menu, click the Save File button (➡) to save the changes to the wave\_gen.v file.

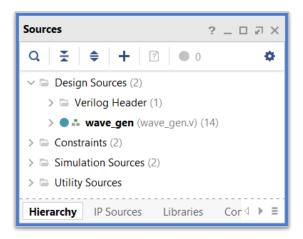

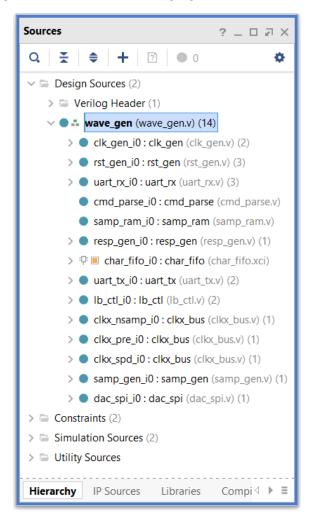

Notice that the Hierarchy, Libraries, and Compile Order tabs update to indicate that the IP is instanced into the design, as seen in the following figure.

#### Step 4: Synthesize the Design

With the customized IP integrated into your design, you can now synthesize the design.

Xilinx IP in the IP catalog are delivered as RTL source. This provides the benefit of being able to perform behavioral simulation, which is faster than netlist-based simulation. However, synthesizing each IP along with the overall design, with every design iteration, can add significant synthesis time to the project development.

The design checkpoint (DCP) file delivered with the IP core output products, and generated by the out-of-context (OOC) synthesis run, eliminates the need to re-synthesize the core over multiple iterations.

The default behavior of the Vivado Design Suite is to generate the necessary output products, including the DCP file, when you create an IP customization.

You can disable generation of the DCP file, as well as defer generating output products until later.

1. In the Hierarchy tab of the Sources window, look at the clk\_core IP customization instantiated under the top-level of the design, wave\_gen/clk\_gen\_i0.

Notice that the clk\_core IP cannot be expanded with the '>' icon like you can expand the char\_fifo IP. This indicates that no output products exist for the clk\_core when it was instanced in the project.

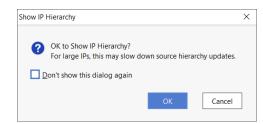

2. In the Sources window > IP Sources view, click the Plus (>) icon next to the char\_fifo IP.

The Vivado tool displays the Show IP Hierarchy dialog box, (following figure), warning you that expanding the hierarchy of very large IP cores can add significant delay to updating the hierarchy in the Sources window.

*Note*: If you do not get the same results, ensure that you are in the Source Window > IP Sources view.

3. Click Cancel to close the Show IP Hierarchy dialog box.

If you skip generation of output products when the IP is customized, the Vivado<sup>®</sup> Design Suite automatically generates the required output products at the point in the design flow they become necessary, such as during synthesis or simulation.

By default, a DCP file for an IP core is created unless you disable this in the Generate Output Products dialog box. See the *Vivado Design Suite User Guide: Designing with IP* (UG896) for more information. If DCP file generation is disabled, the IP RTL synthesizes along with the top-level design.

4. In the Flow Navigator, click the **Run Synthesis •** Run Synthesis button.

The Vivado tool automatically creates a new OOC module synthesis run for the  $clk_core$ , and launches that synthesis run as seen in the following figure.

| Design Runs ? _ ㅁ ㅋ ×                |             |                        |     |     |     |     |      |             |               |     |     |       |      |     |                   |         |

|--------------------------------------|-------------|------------------------|-----|-----|-----|-----|------|-------------|---------------|-----|-----|-------|------|-----|-------------------|---------|

| Q   素   ♦    ∢   ≪   )               | >   >   +   | %                      |     |     |     |     |      |             |               |     |     |       |      |     |                   |         |

| Name                                 | Constraints | Status                 | WNS | TNS | WHS | THS | TPWS | Total Power | Failed Routes | LUT | FF  | BRAMs | URAM | DSP | Start             | Elapsed |

| <ul> <li>Synth_1 (active)</li> </ul> | constrs_1   | Running synth_design   |     |     |     |     |      |             |               |     |     |       |      |     | 10/19/18, 3:30    | 00:00:2 |

| ▷ impl_1                             | constrs_1   | Not started            |     |     |     |     |      |             |               |     |     |       |      |     |                   |         |

| 🗸 🗁 Out-of-Context Module Ru         | ns          |                        |     |     |     |     |      |             |               |     |     |       |      |     |                   |         |

| char_fifo_synth_1                    | char_fifo   | synth_design Complete! |     |     |     |     |      |             |               | 82  | 192 | 0.50  | 0    | 0   | 10/19/18, 3:11 PM | 00:02:0 |

| clk_core_synth_1                     | clk_core    | synth_design Complete! |     |     |     |     |      |             |               | 0   | 0   | 0.00  | 0    | 0   | 10/19/18, 3:29 PM | 00:01:0 |

This synthesis run creates the DCP file for the IP customization.

5. When the  $clk_core$  synthesis run is finished, click OK.

You can examine the contents of the IP Sources tab of the Sources window. You will see the output products generated by the Vivado tools for the IP, (following figure).

With the required output products for the clk\_core created, the Vivado synthesis tool runs on the top-level of the design, (see the following figure).

When the top-level of the design is synthesizing, Vivado synthesis infers a black box for the FIFO generator IP ( $char_fifo$ ) and the Clock generator IP ( $clk_core$ ) in the design.

| Design Runs ? _           |             |                        |     |     |     |     |      |             |               |     |     |       |      |     |                   |         |

|---------------------------|-------------|------------------------|-----|-----|-----|-----|------|-------------|---------------|-----|-----|-------|------|-----|-------------------|---------|

| Q   ≚   ♦   II   ≪   ▶    | -   »   +   | %                      |     |     |     |     |      |             |               |     |     |       |      |     |                   |         |

| Name                      | Constraints | Status                 | WNS | TNS | WHS | THS | TPWS | Total Power | Failed Routes | LUT | FF  | BRAMs | URAM | DSP | Start             | Elapsed |

| 🗸 🖌 synth_1 (active)      | constrs_1   | synth_design Complete! |     |     |     |     |      |             |               | 650 | 4   | 0.50  | 0    | 0   | 10/19/18, 3:30    | 00:02:0 |

| ▷ impl_1                  | constrs_1   | Not started            |     |     |     |     |      |             |               |     |     |       |      |     |                   |         |

| Out-of-Context Module Run | IS          |                        |     |     |     |     |      |             |               |     |     |       |      |     |                   |         |

| char_fifo_synth_1         | char_fifo   | synth_design Complete! |     |     |     |     |      |             |               | 82  | 192 | 0.50  | 0    | 0   | 10/19/18, 3:11 PM | 00:02:  |

| clk_core_synth_1          | clk_core    | synth_design Complete! |     |     |     |     |      |             |               | 0   | 0   | 0.00  | 0    | 0   | 10/19/18, 3:29 PM | 00:01:  |

6. When the Synthesis Completed dialog box opens, select the **View Reports** option, and click **OK**.

This opens the Reports window at the bottom of the Vivado IDE.

- 7. Switch to the Reports window, and select Synthesis → Synth Design → synth\_1\_synthesis\_report\_0.

- 8. In the Log window, click the **Find** button  $\mathbf{Q}$  to search for "blackbox."

- Click Find Next until you come to the following section, which summarizes the black boxes found in the current design, then click Next. The following figure is a snippet of the "Report BlackBoxes" report.

| -+  | +          | +      | +-        |

|-----|------------|--------|-----------|

| Bla | ckBox name | Instan | ices      |

| -+  | +          | ·+     | +-        |

| 1   | char_fifo  | I      | 1         |

| 2   | clk_fifo   | I      | 1         |

| -+  | +          | +      |           |

|     |            | X231   | 29-081919 |

10. Review the report.

You can also review the project IP runs folder for the results of the out-of-context synthesis runs:

<Extract\_Dir>/lab\_1/project\_wave\_gen\_ip/project\_wave\_gen\_ip.runs

You can use the IP customizations created in other projects by adding the XCI file as a source. All the output products for the IP, including the DCP, are used automatically. If you change the part, you must update the IP and regenerate the output products.

#### Conclusion

This concludes Lab 1. You have successfully created a FIFO Generator IP customization, and instanced it in a design. Close the project and exit the Vivado<sup>®</sup> tool, or continue and implement the design to explore further. In this Lab, you learned how to:

• Open the Vivado IDE.

- Select and customize an IP from the IP catalog.

- Instantiate the customized IP into an HDL design.

- Use some details of the output products required to support the IP in the design flow.

You can add and manage IP in a design interactively within the Vivado IDE, or using Tcl scripting.

Chapter 3

### Lab 2: Creating and Managing Reusable IP

#### Introduction

To simplify revision control, and to support the use of customized IP across multiple projects and designs, you can manage and store the customized IP in a repository, separate from any design projects in which they are used. The IP customization file (XCI), and the output products for synthesis, simulation, and other outputs, are contained together in a unique directory.

You can reference these IP customizations in new projects and designs, to simulate, synthesize, and implement the IP as part of the design. Having all the generated output products available also preserves that customized version of the IP for use in a future release of the Vivado<sup>®</sup> Design Suite, even if the IP is updated in the Xilinx<sup>®</sup> IP catalog. See the *Vivado Design Suite User Guide: Designing with IP* (UG896) for more information on managing IP.

In this lab, you create and verify an IP customization in an IP repository using the Manage IP flow in the Vivado Design Suite. This flow lets you browse the IP catalog to create and manage IP customizations for use in either a Project or a Non-Project design flow.

You can create a repository of the customized IP for use in your design(s), managed and maintained outside of a Vivado Project. A special IP project is created at the location specified for the Manage IP flow. This special project facilitates the creation of a synthesis design checkpoint (DCP) and structural simulation models for the IP.

When using an IP customization, in a project or non-project flow, all output products, including a DCP if present, are used in the design flow. The use of IP synthesis DCP file speeds synthesis of the top-level design because the IP have been pre-synthesized. In addition, a stub file is produced for use in third party synthesis tools to infer a black box for IP.

#### Step 1: Start a Manage IP session

1. Change to the directory where the lab materials are stored:

cd <extract\_dir>/lab\_2

- 2. Launch the Vivado<sup>®</sup> IDE:

- a. On Linux, by typing vivado.

- b. On Windows, launch the Vivado Design Suite IDE by pressing **Start → All Programs → Xilinx Design Tools → Vivado 2021.1**.

As an alternative, click the Vivado 2021.1 Desktop icon to start the Vivado IDE.

The Vivado IDE Getting Started page displays with links to open or create projects, and to view documentation.

3. On the Getting Started page, click the Manage IP link, as shown in the following figure.

In the menu that displays, you can click one of the following:

- Click **New IP Location** to specify a New IP location for a new Manage IP project and generated output products.

- Click **Open IP Location** to open an existing IP location for prior Manage IP projects.

- 4. Select New IP Location.

- 5. Click **Next** to move to the Manage IP Settings dialog box shown in the following figure (this shows to what you change the default setting).

|                                                  | New IP Location                                             |        |  |  |  |  |  |  |

|--------------------------------------------------|-------------------------------------------------------------|--------|--|--|--|--|--|--|

| Manage IP Settings<br>Set options for creating a | nage IP Settings<br>options for creating and generating IP. |        |  |  |  |  |  |  |

| Part:                                            | @xc7k70tfbg676-1                                            | •••    |  |  |  |  |  |  |

| Target language:                                 | Verilog                                                     | ~      |  |  |  |  |  |  |

| Target simulator:                                | Vivado Simulator                                            | ~      |  |  |  |  |  |  |

| Simulator language:                              | Mixed                                                       | ~      |  |  |  |  |  |  |

| IP location:                                     | C:/Tutorials/workspace/ug939-design-files/lab_2/my_ip       |        |  |  |  |  |  |  |

| ?                                                | < <u>B</u> ack <u>N</u> ext > <u>Einish</u>                 | Cancel |  |  |  |  |  |  |

|                                                  |                                                             |        |  |  |  |  |  |  |

- 6. Configure the dialog box settings as follows:

- **Part:** xc7k70tfbg676-1

Note: Use the browse button to select the specified target part.

- Target Language: Verilog

- Target Simulator: Vivado Simulator

- Simulator Language: Mixed

- **IP location:** <Extract\_Dir>/lab\_2/my\_ip

- 7. Press Finish.

The IP catalog displays in an IP Project, which is a simple interface for the creation and management of IP customizations.

#### **Step 2: Customize the FIFO Generator**

You can work with the IP catalog by searching with a keyword or browsing through the categories.

**TIP:** For a complete description of the Customize IP dialog box, and its use, see Chapter 2: Lab 1: Customizing the FIFO Generator. This Lab assumes that you have previously completed Lab 1, and are familiar with the concepts covered in that lab.

- 1. In the IP catalog search bar, type: fifo.

- 2. Double-click the FIFO Generator from the Memories & Storage Elements group.

The Customize IP dialog box opens, as shown in the following figure (this is not the original setting; it shows the change that you make to the customization).

| ocumentation 🕒 IP Location 😋 Switch to              | Defaults                                                                                                                                                                                      |                                                     |     |                                                      |     |     |     |  |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|------------------------------------------------------|-----|-----|-----|--|--|--|--|--|

| Show disabled ports                                 | Component Name char_fifo                                                                                                                                                                      |                                                     |     |                                                      |     |     |     |  |  |  |  |  |

|                                                     | Basic Native Ports Status Flags Data                                                                                                                                                          | Basic Native Ports Status Flags Data Counts Summary |     |                                                      |     |     |     |  |  |  |  |  |

|                                                     | Interface Type                                                                                                                                                                                | Interface Type                                      |     |                                                      |     |     |     |  |  |  |  |  |

|                                                     | Fifo Implementation Independent Clocks Block RAM v<br>Synchronization Stages 2 v                                                                                                              |                                                     |     |                                                      |     |     |     |  |  |  |  |  |

|                                                     | FIFO Implementation Options Supported Features                                                                                                                                                |                                                     |     |                                                      |     |     |     |  |  |  |  |  |

| + FIFO_READ<br>- rst vr_rst_busy -<br>rd_rst_busy - |                                                                                                                                                                                               | Memory<br>Type                                      | (1) | (2)                                                  | (3) | (4) | (5) |  |  |  |  |  |

| - vr_clk                                            | Common Clock (CLK)                                                                                                                                                                            | Block RAM                                           | 1   | 1                                                    |     | 1   | √   |  |  |  |  |  |

|                                                     | Common Clock (CLK)                                                                                                                                                                            | ) Distributed RAM                                   |     |                                                      |     |     |     |  |  |  |  |  |

|                                                     | Common Clock (CLK)                                                                                                                                                                            | Shift Register                                      |     |                                                      |     |     |     |  |  |  |  |  |

|                                                     | Common Clock (CLK)                                                                                                                                                                            | Built-in FIFO                                       |     | $\checkmark$                                         | ×   | ×   | ×   |  |  |  |  |  |

|                                                     | Independent Clocks (RD_CLK, WR_CLK)                                                                                                                                                           | Block RAM                                           | ✓   | ✓                                                    |     | ✓   | ✓   |  |  |  |  |  |

|                                                     | Independent Clocks (RD_CLK, WR_CLK)                                                                                                                                                           | Distributed RAM                                     |     | 1                                                    |     |     |     |  |  |  |  |  |

|                                                     | Independent Clocks (RD_CLK, WR_CLK)                                                                                                                                                           | Built-in FIFO                                       |     | 1                                                    | ×   | √   | √   |  |  |  |  |  |

|                                                     | <ol> <li>Non-symmetric aspect ratios (different r</li> <li>First-Word Fall-Through</li> <li>Uses Bull-In FIFO primitives</li> <li>Uses CC support</li> <li>Dynamic Error Injection</li> </ol> | ead and write data widths)                          |     | (3) Uses Built-in FIFO primitives<br>(4) ECC support |     |     |     |  |  |  |  |  |

- 3. At the top of the Customize IP dialog box, change the Component Name to char\_fifo.

- 4. In the Basic tab:

- Select the default Interface Type of Native.

- From the Fifo Implementation menu, set Independent Clocks Block RAM.

- 5. In the Native Ports tab:

- Set the Read Mode to First Word Fall Through.

- Set the Write Width to be 8 bits.

- Click the Read Width field to adjust it automatically to 8 bits as well.

- 6. Select the **Summary** tab.

The Summary page displays a summary of all the options selected as well as listing resources used for this configuration. The summary for the FIFO Generator core should look like the following figure. For this configuration you will see you are using one 18K BRAM.

| Basic   | Native Ports       | Status Flags     | Data Counts         | Summary                                                                 |

|---------|--------------------|------------------|---------------------|-------------------------------------------------------------------------|

| WARN    | NING : The use of  | Asynchronous Re  | eset can lead to Bi | AM data corruption(AR 42571). It is recommended to Enable Safety Circui |

| Block F | RAM resource(s) (  | 18K BRAMs): 1    |                     |                                                                         |

| Block F | RAM resource(s) (  | 36K BRAMs): 0    |                     |                                                                         |

| Clocki  | ing Scheme         |                  |                     | Independent Clocks                                                      |

| Memo    | ory Type           |                  |                     | Block RAM                                                               |

| Mode    | l Generated        |                  |                     | Behavioral Model                                                        |

| Write   | Width              |                  |                     | 8                                                                       |

| Write   | Depth              |                  |                     | 1025                                                                    |

| Read    | Width              |                  |                     | 8                                                                       |

| Read    | Depth              |                  |                     | 1025                                                                    |

| Almos   | st Full/Empty Flag | S                |                     | Not Selected/Not Selected                                               |

| Progra  | ammable Full/Em    | pty Flags        |                     | Not Selected/Not Selected                                               |

| Data (  | Count Outputs      |                  |                     | Not Selected                                                            |

| Hands   | shaking            |                  |                     | Not Selected                                                            |

| Read    | Mode / Reset       |                  |                     | First-word Fall-through / Asynchronous                                  |

| Read    | Latency (From Ris  | ing Edge of Read | d Clock)            | 0                                                                       |

7. Verify that the information is correct as shown, and click **OK** to generate the customized IP core for use in your design.

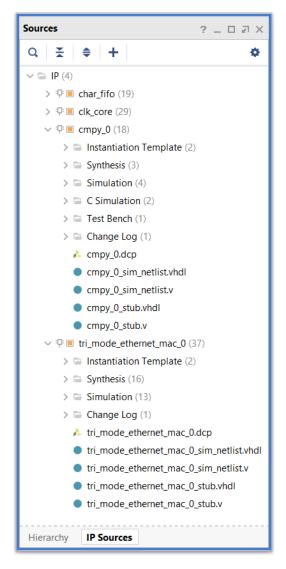

The Generate Output Products popup appears, as seen in the following figure. When creating a repository of customized IP using the Managed IP flow, generate all output products, including the design checkpoint (DCP), for each IP. A specific release of the Vivado tools only supports a single version of an IP core. You cannot re-customize or generate outputs for a prior version of IP in the Vivado Design Suite. Instead, you would need to update the IP to the latest version if you have not preserved the needed output products.

**IMPORTANT!** Only one version of an IP is supported in a given release of the Vivado tool. To use older versions of an IP, ALL output products must be available in your custom IP repository.

8. Click the Generate button to create the output products, as shown in the following figure.

| 🍌 Generate Output Products                       | × |

|--------------------------------------------------|---|

| The following output products will be generated. |   |

|                                                  |   |

| Preview                                          |   |

| Q X \$                                           |   |

| v 中 ■ char_fifo.xci (OOC per IP)                 | ^ |

| Instantiation Template                           |   |

| Synthesized Checkpoint (.dcp)                    |   |

| Structural Simulation                            |   |

| Change Log                                       | ~ |

|                                                  |   |

| Synthesis Options                                |   |

| O <u>G</u> lobal                                 |   |

| Out of context per IP                            |   |

| <b>B</b> . 6                                     |   |

| Run Settings                                     |   |

| Number of jobs: 4                                |   |

| Apply         Generate         Skip              |   |

|                                                  |   |

9. When prompted, click **OK**.

To reduce synthesis runtime for a design using one or more customized IP cores, the IP are pre-synthesized as a standalone module by default, with the netlist saved in a synthesized checkpoint file (DCP).

During synthesis of the overall design, the Vivado synthesis infers a black box for the IP.

During implementation, the netlists from the DCP files are linked into the design. This flow is scriptable in Tcl for both Project and Non-Project Mode.

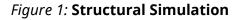

To create the synthesized checkpoint file, the Vivado IDE creates and launches a corresponding out-of-context module run, as seen in the following figure.

This run automatically launches, and when synthesis completes, the  $char_fifo$  directory contains the following additional files:

- char\_fifo.dcp: The synthesis design checkpoint, which contains a netlist for the IP.

- char\_fifo\_stub.v: A Verilog port module for use with third-party synthesis tools to infer a black box for the IP. The stub contains directives for Synplify Pro to not insert IO buffers, this may require editing for other third-party synthesis tools.

- char\_fifo netlist files, sim\_netlist.v, and sim\_netlist.vhd: A Verilog and VHDL netlist for functional simulation of the IP core.

If you are using a third-party synthesis tool for the design, a Verilog stub file with the port declarations, or a VHDL component declaration, is required to infer the black box.

The Vivado Design Suite automatically creates this file along with the synthesis design checkpoint (DCP) when generating the output products.

Customized IPs can be referenced using the XCI file from both Project and Non-Project Mode.

In a project-based design, Xilinx recommends that you do not copy sources into the local project structure, but rather reference them from your custom IP repository. For more information on Project Mode and Non-Project Mode, see the *Vivado Design Suite User Guide*: *Design Flows Overview* (UG892).

10. Examine the <extract\_dir>/lab\_2/my\_ip location.

Notice that three directories are created, as shown in the following figure:

- The IP customization (char\_fifo) containing the XCI file, which has all the customization information for the IP, and all the output products generated.

- The IP Project (managed\_ip\_project) which you created in this lab to customize the char\_fifo IP and manage the output products, including the post synthesis DCP.

- The support files for IP (ip\_user\_files) which contains simulation scripts for all supported simulators, copies of the instantiation templates, stub files for use with third party synthesis tools, and static RTL files used for simulation. All these files with the exception of the simulation scripts are copied from the IP customization directory (in this case char\_fifo). See the Vivado Design Suite User Guide: Designing with IP (UG896) for more details on the ip\_user\_files directory.

| ▶ OSDisk (C:)    ▶ ug939-design-files    ▶ lab_2 | ▶ my_ip ▶          |             |

|--------------------------------------------------|--------------------|-------------|

| Help                                             |                    |             |

| ibrary 🔻 Share with 👻 New folder                 |                    |             |

| Name                                             | Date modified      | Туре        |

| 🐌 char_fifo                                      | 9/30/2016 10:18 AM | File folder |

| 🎉 ip_user_files                                  | 9/30/2016 10:16 AM | File folder |

| 鷆 managed_ip_project                             | 9/30/2016 10:16 AM | File folder |

11. Examine the Sources window as shown in the following figure, to see the generated output products in the Manage IP project.

The generated output products for the char\_fifo core include the instantiation template, synthesis files, simulation files, synthesized design checkpoint, functional simulation netlists as well as stub files for use with third-party synthesis tools.

**Note:** The FIFO customization created in this lab is the same as the one from Lab 1: Customizing the FIFO Generator. If you want to add existing IP into a Managed IP project, select **File**  $\rightarrow$  **Add Existing IP**.

#### **Related Information**

Step 2: Customize the FIFO Generator

### Step 3: Customize the Clocking Wizard

Now, you create a customization for the Clocking Wizard IP.

- 1. Follow the same processes you used for finding the FIFO Generator IP in the IP catalog to find and launch a Clocking Wizard IP customization.

- 2. Change the Component Name to clk\_core.

- 3. In the Clocking Options tab, leave all the settings on the default, except for the Input Clock Information as shown in following figure.

- Primary Clock Input Frequency: 200

- Source: Differential clock capable pin

| Input Clock | Port Name | Input Frequency(MHz) |                   | Jitter Options | Input Jitter | Source                         |   |

|-------------|-----------|----------------------|-------------------|----------------|--------------|--------------------------------|---|

| Primary     | clk_in1   | 200.000 📀            | 10.000 - 800.000  | UI 👻           | 0.010        | Differential clock capable pin | ۳ |

| Secondary   | clk_in2   | 100.000              | 120.000 - 240.000 |                | 0.010        | Single ended clock capabl      | Ŧ |

- 4. In the Output Clocks tab, change the Port Name, as well as Output Freq Requested as follows:

- **clk\_out1:** clk\_rx, 200

- **clk\_out2:** clk\_tx, 166.667

You should end up with the configuration shown in the following figure.

| Clocking Options   | Output Clocks        | Port Renaming         | MMCM Settings St | Immary          |        |                |        |        |         |

|--------------------|----------------------|-----------------------|------------------|-----------------|--------|----------------|--------|--------|---------|

| The phase is calcu | lated relative to th | e active input clock. |                  |                 |        |                |        |        |         |

| Output Clock       | Port Name            | Output Freq (MHz)     |                  | Phase (degrees) |        | Duty Cycle (%) |        | Drives | Use     |

| Оцтрит Сюск        |                      | Requested             | Actual           | Requested       | Actual | Requested      | Actual | Drives | Fine PS |

| ✓ clk_out1         | clk_n                | 200.000 💿             | 200.000          | 0.000 💿         | 0.000  | 50.000         | 50.0   | BUFG   | •       |

| ✓ clk_out2         | clk_tx               | 166.667 💿             | 166.667          | 0.000 💿         | 0.000  | 50.000         | 50.0   | BUFG   | •       |

- 5. Click **OK** to bring up the Generate Output Product window.

- 6. Click Generate, and then click OK.

- 7. Vivado<sup>®</sup> creates and launches a design run for the Clocking Wizard IP as shown in the following figure.

8. Verify the output products and directory created for the Clocking Wizard IP customization (clk\_core) you just created, just as you did with the customized FIFO Generator IP.

#### **Step 4: Use Third-Party Simulators**

The purpose of the Managed IP project is to create and manage IP customizations; there is no support for directly simulating IP in a Managed IP project. Customized IP can be instanced into a standard design project for simulation, in either Project or Non-Project Mode.

Xilinx<sup>®</sup> IP delivered in the Vivado<sup>®</sup> Design Suite are encrypted using industry standard IEEE P1735 encryption. Supported simulator use this encryption standard, and can run behavioral simulation.

The Vivado Design Suite includes the Vivado simulator, for mixed language simulation, as well as direct support for Mentor Graphics<sup>®</sup> Questa Advanced Simulator, ModelSim Simulator, Cadence<sup>®</sup> Incisive Enterprise Simulator (IES), Synopsys<sup>®</sup> Verilog Compiler Simulator (VCS), and Aldec<sup>®</sup>.

By default, Vivado creates a directory called *ip\_user\_files* in the same directory as the IP and Managed IP directories. This directory contains scripts for simulation with all supported simulators for all the IP created. You can use these scripts as a starting point for simulating with the IP. The scripts will reference all the files needed for simulating the IP.

You can use the following Tcl command to generate a Tcl script for the target simulator: export\_simulation -simulator <simulator>

See the Vivado Design Suite User Guide: Logic Simulation (UG900) for more information on using third-party simulators, including creating scripts for running simulations outside of the Vivado Design Suite.

#### **Get the Required Simulation Files**

As an alternative to the export\_simulation command, you can manually gather the required files to support third-party simulation.

**Note:** If there is a need to use the VIP (Verification IP) on IP, use the Tcl command: set\_property

CONFIG.<AXI interface> [get\_ips <ip>] and additional simulation files will be generated. See

Vivado Design Suite User Guide: Designing with IP (UG896) for more information.

1. To get all files that an IP delivers for simulation, use the get\_files Tcl command. In the Tcl Console, type the following command:

```

get_files -compile_order sources -used_in simulation -of_objects

[get_ips char_fifo]

```

Where:

- -used\_in: Lets you specify files that are marked for use in simulation, or marked for use in synthesis.