# Vivado Design Suite User Guide

# **Design Analysis and Closure Techniques**

UG906 (v2021.1) June 30, 2021

# **Revision History**

The following table shows the revision history for this document.

| Section                                                                    | Revision Summary                                                                        |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 06/30/2021 Version 2021.1                                                  |                                                                                         |  |  |  |  |  |  |  |

| General updates                                                            | Updated for Vivado <sup>®</sup> 2021.1 release.                                         |  |  |  |  |  |  |  |

| Intelligent Design Runs                                                    | IDR feature documented.                                                                 |  |  |  |  |  |  |  |

| Report QoR Suggestions                                                     | Edited section for clarity.                                                             |  |  |  |  |  |  |  |

| Report Timing Summary                                                      | Add note about running <pre>report_timing_summary</pre> in the IDE and the Tcl Console. |  |  |  |  |  |  |  |

| Reporting the Scoped Timing Exceptions Being Overridden                    | Added new information.                                                                  |  |  |  |  |  |  |  |

| Report Summary Section                                                     | Added note about WBSS.                                                                  |  |  |  |  |  |  |  |

| Chapter 9: Performing NoC Quality of Service Analysis in<br>Versal Devices | New section.                                                                            |  |  |  |  |  |  |  |

# Table of Contents

| Revision History                                    | 2  |

|-----------------------------------------------------|----|

| Chapter 1: Overview                                 | 7  |

| Navigating Content by Design Process                |    |

| Chapter 2: Implementation Results Analysis Features |    |

| Using the Design Runs Window                        |    |

| Placement Analysis                                  | 10 |

| Routing Analysis                                    | 16 |

| Report Design Analysis                              | 21 |

| Report QoR Assessment                               | 45 |

| Report QoR Suggestions                              | 49 |

| Chapter 3: Logic Analysis Within the IDE            |    |

| Design Analysis Within the IDE                      |    |

| Logic Analysis Features                             |    |

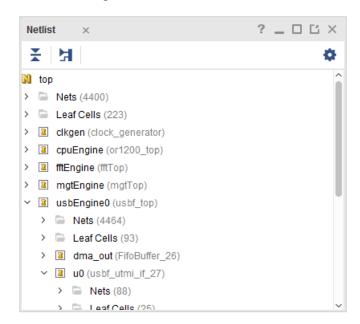

| Using the Netlist Window                            |    |

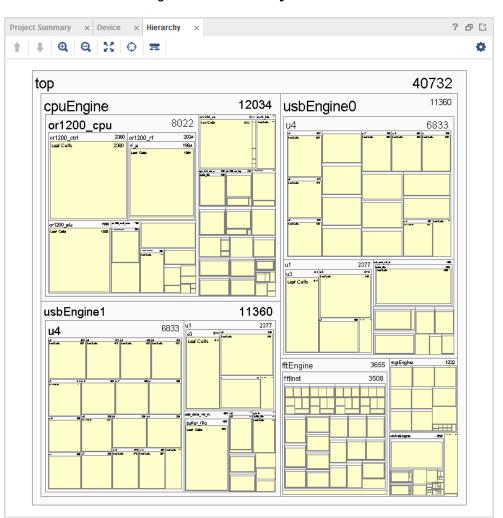

| Using the Hierarchy Window                          |    |

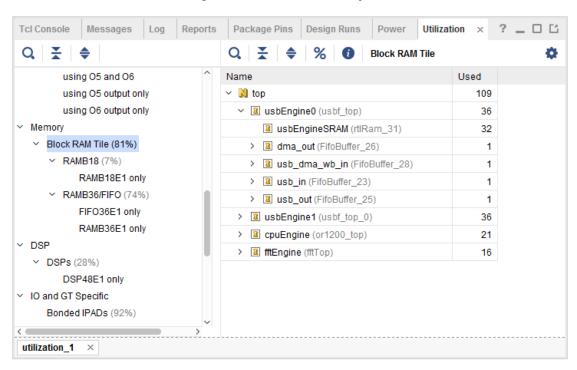

| Using the Utilization Report                        |    |

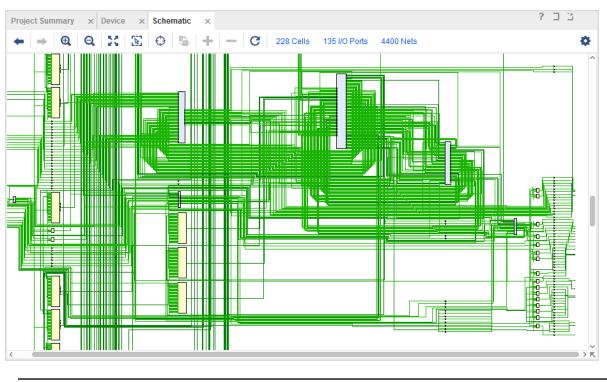

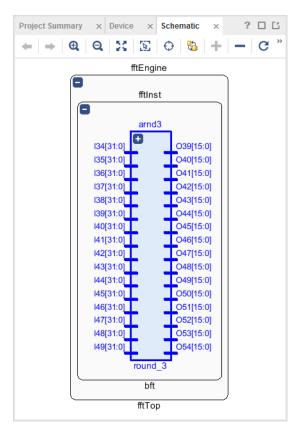

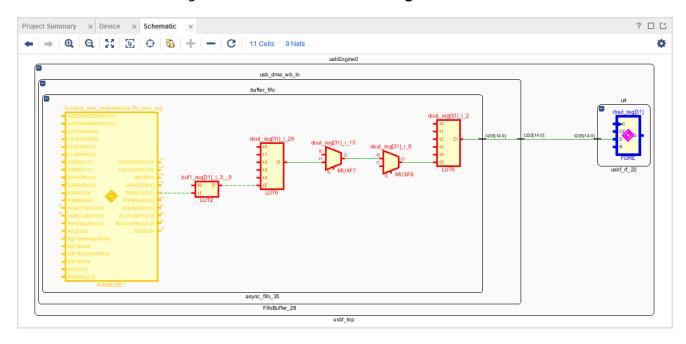

| Using the Schematic Window                          |    |

| Searching for Objects Using the Find Dialog Box     |    |

| Analyzing Device Utilization Statistics             |    |

| Using Report DRC                                    | 74 |

| Validating Design Methodology DRCs                  |    |

| Chapter 4: Timing Analysis Features                 | 70 |

| Report Timing Summary                               |    |

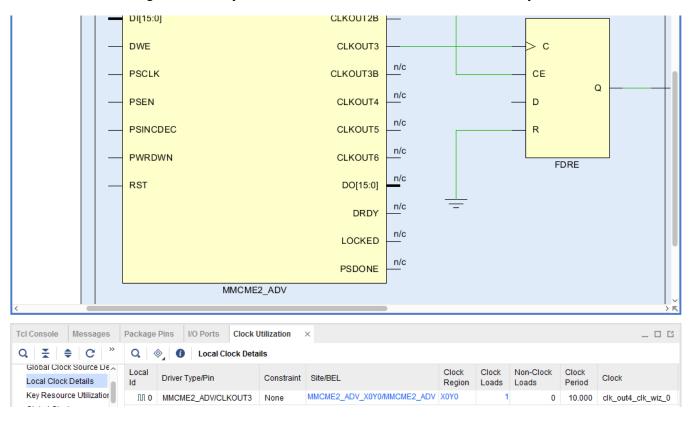

| Report Clock Networks                               |    |

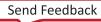

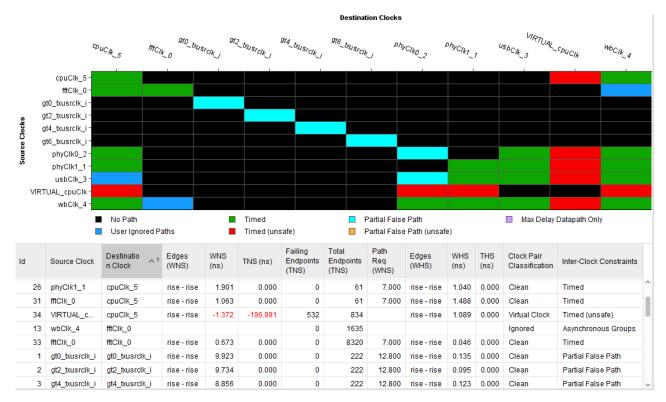

| Report Clock Interaction                            |    |

| Report Pulse Width                                  |    |

| Report Timing                                       |    |

| Report Datasheet                                    |    |

| Report Exceptions                                   |    |

|                                                     |    |

| Report Exceptions in the Vivado IDE                                   |              |

|-----------------------------------------------------------------------|--------------|

| Report Clock Domain Crossings                                         |              |

| Report Bus Skew                                                       | 157          |

| Chapter 5: Viewing Reports and Messages                               |              |

| Introduction to Reports and Messages                                  |              |

| Viewing and Managing Messages in the IDE                              | 168          |

| Vivado Generated Messages                                             | 171          |

| Generating and Waiving Design Checks                                  | 172          |

| Configurable Report Strategies                                        |              |

| Creating Design Related Reports                                       |              |

| Chapter 6: Performing Timing Analysis                                 |              |

| Introduction to Timing Analysis                                       |              |

| Understanding the Basics of Timing Analysis                           | 228          |

| Reading a Timing Path Report                                          | 239          |

| Verifying Timing Signoff                                              |              |

| Chapter 7: Synthesis Analysis and Closure Techniques                  | 249          |

| Using the Elaborated View to Optimize the RTL                         |              |

| Decomposing Deep Memory Configurations for Balanced Power and Perform |              |

| Optimizing RAMB Utilization when Memory Depth is not a Power of 2     |              |

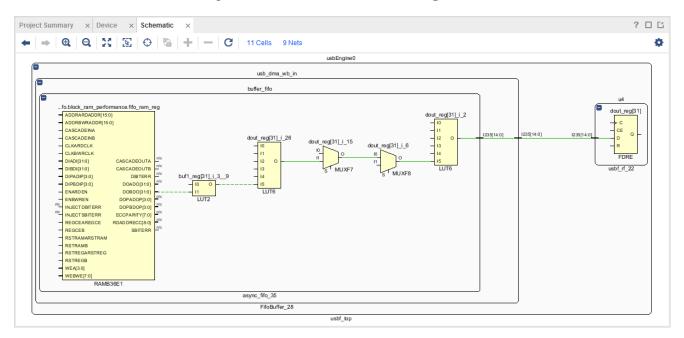

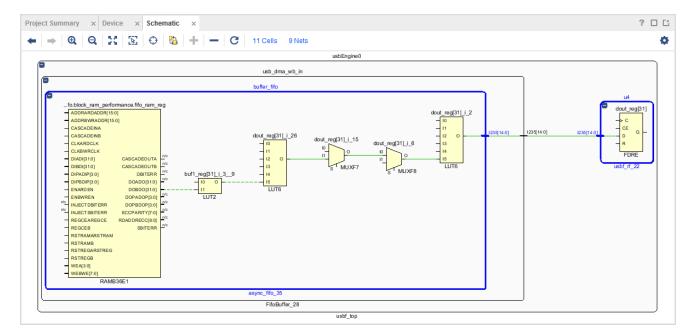

| Optimizing RAMB Input Logic to Allow Output Register Inference        |              |

| Improving Critical Logic on RAMB Outputs                              |              |

|                                                                       |              |

| <b>Chapter 8: Implementation Analysis and Closure Technique</b>       | <b>S</b> 266 |

| Intelligent Design Runs                                               |              |

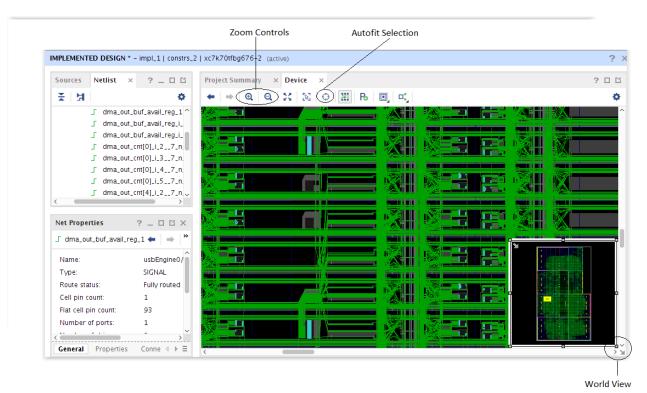

| Using the report_design_analysis Command                              |              |

| Identifying the Longest Logic Delay Paths in the Design               | 279          |

| Identifying High Fanout Net Drivers                                   | 281          |

| Determining if Hold-Fixing is Negatively Impacting the Design         |              |

| Quickly Analyzing All Failing Paths                                   | 284          |

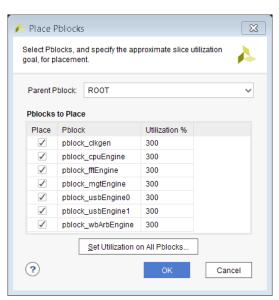

| Floorplanning                                                         | 285          |

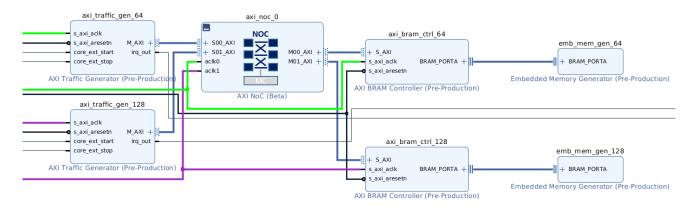

| Chapter 9: Performing NoC Quality of Service Analysis in Ve           | ersal        |

| Devices                                                               |              |

| Introduction to QoS Analysis using the QoS Report in Vivado           |              |

| Vivado NoC QoS Reporting Examples                                     |              |

| opendix A: Timing Methodology Checks                                   |     |

|------------------------------------------------------------------------|-----|

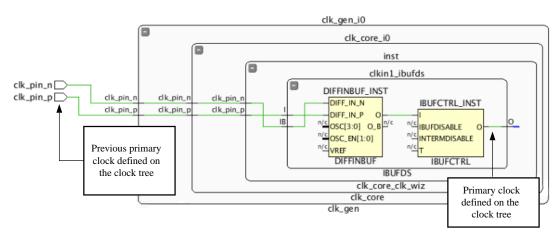

| TIMING-1: Invalid Clock Waveform on Clock Modifying Block              |     |

| TIMING-2: Invalid Primary Clock Source Pin                             |     |

| TIMING-3: Invalid Primary Clock on Clock Modifying Block               | 307 |

| TIMING-4: Invalid Primary Clock Redefinition on a Clock Tree           |     |

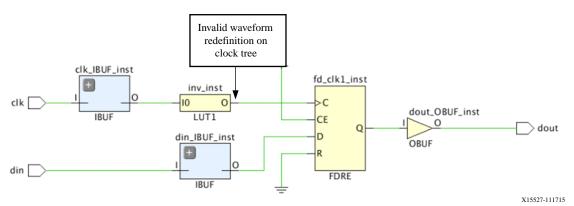

| TIMING-5: Invalid Waveform Redefinition on a Clock Tree                | 310 |

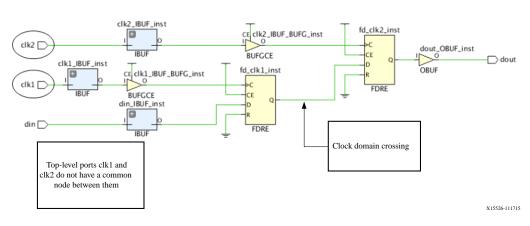

| IMING-6: No Common Primary Clock Between Related Clocks                |     |

| IMING-7: No Common Node Between Related Clocks                         |     |

| IMING-8: No Common Period Between Related Clocks                       |     |

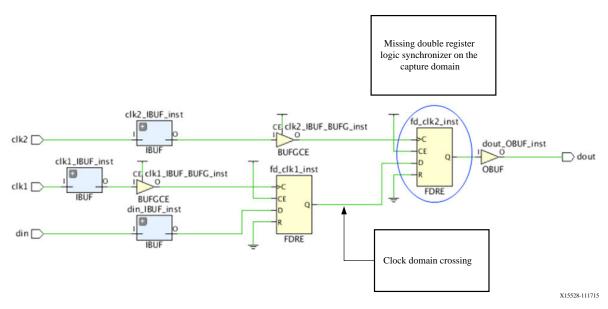

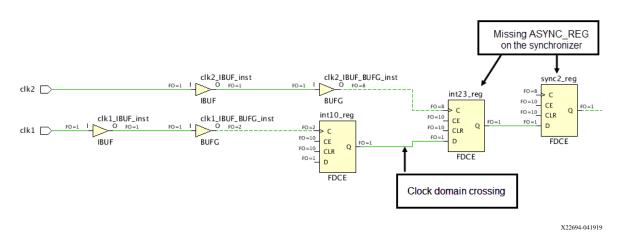

| IMING-9: Unknown CDC Logic                                             | 314 |

| IMING-10: Missing Property on Synchronizer                             |     |

| IMING-11: Inappropriate Max Delay with Datapath Only Option            | 316 |

| IMING-12: Clock Reconvergence Pessimism Removal Disabled               |     |

| IMING-13: Timing Paths Ignored Due to Path Segmentation                |     |

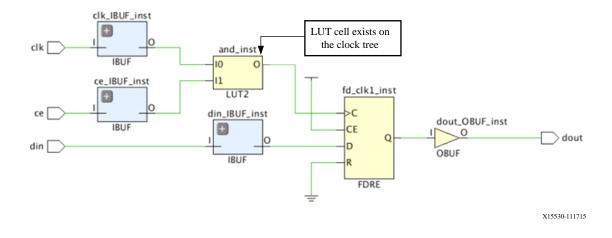

| IMING-14: LUT on the Clock Tree                                        |     |

| IMING-15: Large Hold Violation on Inter-Clock Path                     |     |

| MING-16: Large Setup Violation                                         | 320 |

| IMING-17: Non-Clocked Sequential Cell                                  |     |

| IMING-18: Missing Input or Output Delay                                |     |

| IMING-19: Inverted Generated Clock Waveform on ODDR                    |     |

| TIMING-20: Non-Clocked Latch                                           |     |

| IMING-21: Invalid COMPENSATION Property on MMCM                        |     |

| IMING-22: Missing External Delay on MMCM                               | 323 |

| IMING-23: Combinatorial Loop Found                                     | 323 |

| IMING-24: Overridden Max Delay Datapath Only                           | 324 |

| IMING-25: Invalid Clock Waveform on Gigabit Transceiver (GT)           | 325 |

| IMING-26: Missing Clock on Gigabit Transceiver (GT)                    | 325 |

| TIMING-27: Invalid Primary Clock on Hierarchical Pin                   | 326 |

| IIMING-28: Auto-Derived Clock Referenced by a Timing Constraint        |     |

| IMING-29: Inconsistent Pair of Multicycle Paths                        |     |

| TIMING-30: Sub-Optimal Master Source Pin Selection for Generated Clock | 328 |

| TIMING-201: Add an Output Register to RAM                  |     |

|------------------------------------------------------------|-----|

| TIMING-202: Add Extra Pipelining to Wide Multipliers       |     |

| UTIL-10: Incomplete Case Statement Increasing Control Sets |     |

| UTIL-203: Large ROM Inferred using Distributed RAM         |     |

| Reference Design Files                                     | 343 |

| Appendix C: Additional Resources and Legal Notices |     |

|----------------------------------------------------|-----|

| Xilinx Resources                                   |     |

| Solution Centers                                   |     |

| Documentation Navigator and Design Hubs            | 344 |

| References                                         | 345 |

| Training Resources                                 | 345 |

| Please Read: Important Legal Notices               |     |

Chapter 1

# Overview

# **Navigating Content by Design Process**

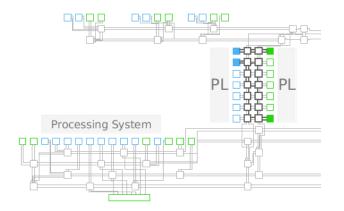

Xilinx<sup>®</sup> documentation is organized around a set of standard design processes to help you find relevant content for your current development task. All Versal<sup>™</sup> ACAP design process Design Hubs can be found on the Xilinx.com website. This document covers the following design processes:

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, functional simulation, and evaluating the Vivado<sup>®</sup> timing, resource use, and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Chapter 4: Timing Analysis Features

- Chapter 6: Performing Timing Analysis

- Chapter 8: Implementation Analysis and Closure Techniques

Chapter 2

# Implementation Results Analysis Features

# **Using the Design Runs Window**

The Design Runs window displays the state of the current runs.

For more information, see this link in the Vivado Design Suite User Guide: Using the Vivado IDE (UG893).

If the run is running, finished cleanly, or finished with errors, the Design Runs window appears when a run is done.

Т

TIP: If the run is not up to date, you can select Force Up-to-Date from the pop-up menu.

| Tcl Console Messages Log                             | Reports      | Design Runs × Power D   | RC Met | hodology | Timing |       |        |       | ? _ 🗆       | Ľ |

|------------------------------------------------------|--------------|-------------------------|--------|----------|--------|-------|--------|-------|-------------|---|

| Q   ¥   ♦   I   ≪   ▶                                | <b>» +</b> % | 6                       |        |          |        |       |        |       |             |   |

| Name                                                 | Constraints  | Status                  | WNS    | TNS      | WHS    | THS   | WBSS   | TPWS  | Total Power |   |

| <ul> <li>✓ synth_1 (active)</li> </ul>               | constrs_1    | synth_design Complete!  |        |          |        |       |        |       |             | ^ |

| ✓ impl_1                                             | constrs_1    | route_design Complete!  | 0.111  | 0.000    | 0.024  | 0.000 | 12.535 | 0.000 | 2.690       |   |

| 🗸 📄 Out-of-Context Module Runs                       |              |                         |        |          |        |       |        |       |             |   |

| ✓ ✓ config_mb                                        |              | Submodule Runs Complete |        |          |        |       |        |       |             |   |

| 🗸 config_mb_axi_gpio                                 | config_m     | synth_design Complete!  |        |          |        |       |        |       |             |   |

| ✓ config_mb_ilmb_v10 config_m synth_design Complete! |              |                         |        |          |        |       |        |       |             |   |

| ✓ config_mb_rst_ddr4                                 | config_m     | synth_design Complete!  |        |          |        |       |        |       |             | ~ |

| <                                                    |              |                         |        |          |        |       |        |       |             | > |

#### Figure 1: Design Runs Window

The Design Runs Window columns show:

- The name of the run

- The target part

- The constraints set associated with a run

- The run strategy

- The status of the last completed step of a run

- The progress of a run

- The start time of a run

- The elapsed time of a run during execution or the final runtime of a completed run

- The timing score of a run: WNS, TNS, WHS, THS, WBSS, and TPWS (see Report Timing Summary for more information on these numbers). This is where you can quickly verify that a run meets timing. If it does not meet timing, you must start the analysis with the Timing Summary Report.

*Note*: WBSS represents the Worst Bus Skew Slack report\_bus\_skew.

- The number of nets that were not successfully routed

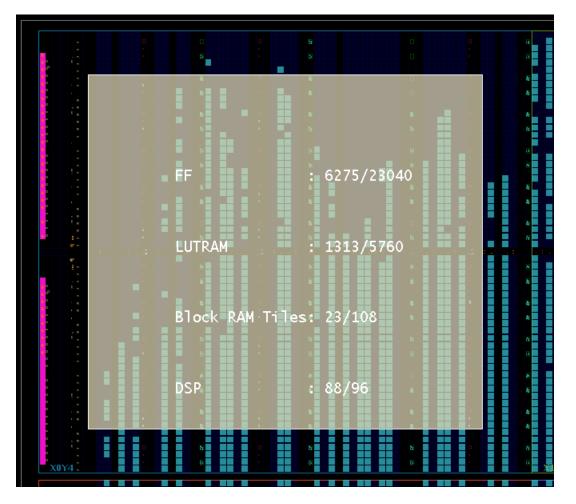

- The utilization of the design LUT, FF, block RAMs, DSP, and if applicable, UltraRAMs.

- The total power estimate

- A brief description of the run strategy

- The incremental mode of the design run

If you are using the Vivado<sup>®</sup> IDE project flow, review the Messages tab for your active synthesis and implementation runs. Messages are grouped by run steps in the flow. All the information saved in the run log files, and the main Vivado session log file, appear in this consolidated and filtered view.

## Figure 2: Messages Grouped by Step

Some messages crossprobe back to a source file that can always be opened by clicking on the file name, or in some cases to a design object related to the message. Depending on which step of the flow you are analyzing, you must open either the synthesized design or the implemented design in order to be able use the object crossprobing from the message.

# **Placement Analysis**

This section discusses Placement Analysis and includes:

- Highlighting Placement

- Showing Connectivity

- Viewing Metrics

# **Highlighting Placement**

Another way to review design placement is to analyze cell placement. The Highlight Leaf Cells command helps in this analysis.

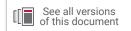

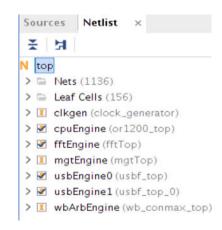

- 1. In the Netlist Window, select the levels of hierarchy to analyze.

- 2. From the popup menu, select **Highlight Leaf Cells**  $\rightarrow$  **Select a color**.

- 3. If you select multiple levels of hierarchy, select Cycle Colors.

The leaf cells that make up the hierarchical cells are color coded in the Device window.

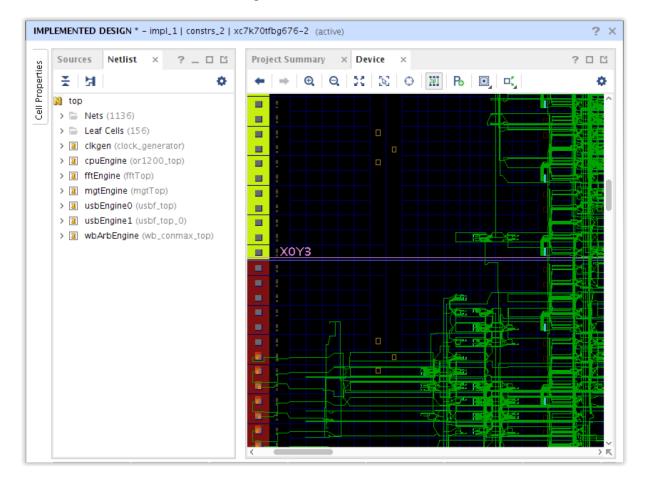

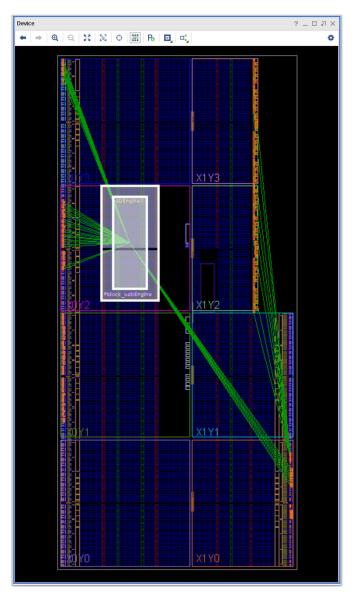

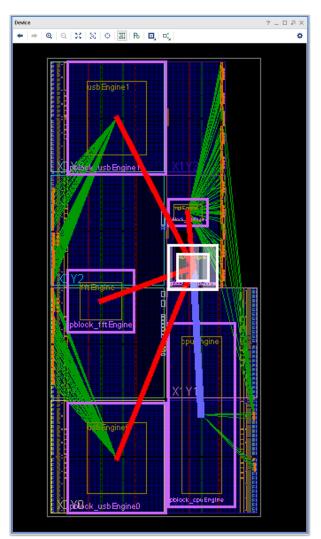

## Figure 3: Highlight Hierarchy

The color coding shows the placement of the key hierarchical blocks in the device. The usbEngine0 (in blue):

- Uses a number of Block RAM and DSP48 cells.

- Is in the middle clock regions of the chip.

- Is intermingled with other logic (fftEngine) in the design.

It is easy to see that the fftEngine (in green) and the cpuEngine (in yellow) are intermingled. The two blocks primarily use different resources (DSP48 as opposed to slices). Intermingling makes best use of the device.

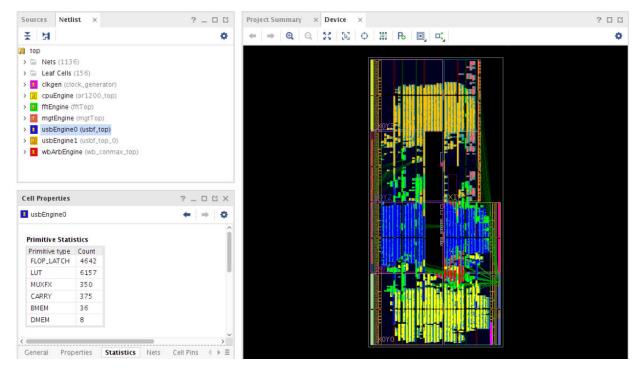

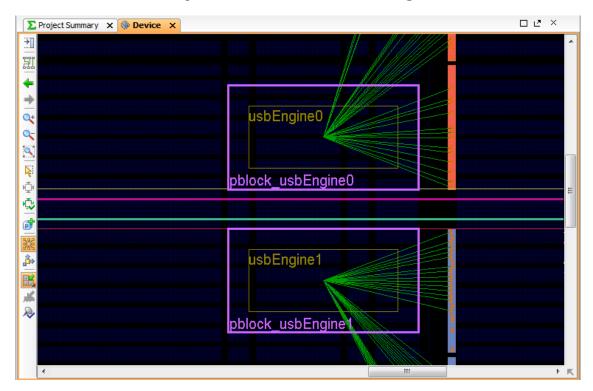

# **Showing Connectivity**

It can be useful to analyze a design based on connectivity. Run **Show Connectivity** to review the placement of all logic driven by an input, a Block RAM, or a bank of DSPs. Show Connectivity takes a set of cells or nets as a seed, and selects objects of the other type.

$\bigcirc$

**TIP:** Use this technique to build up and see cones of logic inside the design.

The following figure shows a Block RAM driving logic inside the device including OBUFs. A synthesis pragma stops synthesis from placing the output flop in the Block RAM during memory inferencing.

## Figure 4: Show Connectivity

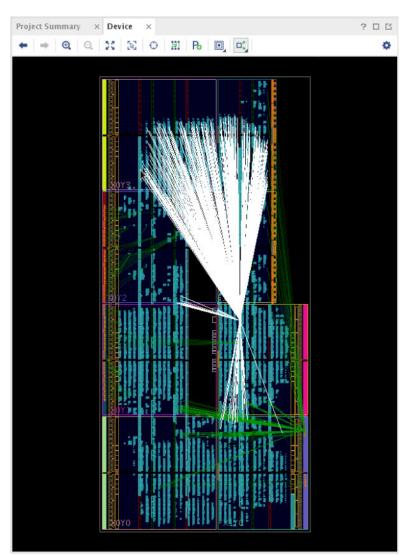

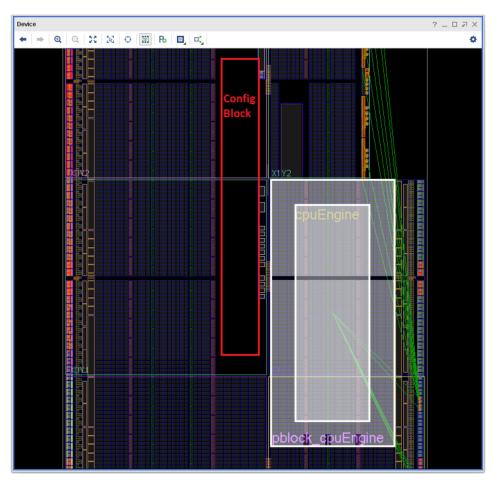

# **Fixed and Unfixed Logic**

The Vivado tools track two different types of placement:

- Elements placed by the user (shown in orange) are Fixed.

- Fixed logic is stored in the XDC.

- Fixed logic normally has a LOC constraint and might have a BEL constraint.

- Elements placed by the tool (shown in blue) are Unfixed.

In the following figure, the I/O and Block RAM placement is Fixed. The slice logic is Unfixed.

## Figure 5: Fixed and Unfixed Placement

# **Cross Probing**

For designs synthesized with Vivado Synthesis, it is possible to cross probe back to the source files once the netlist design is in memory.

To cross probe:

- 1. Select the gate.

- 2. Select **Go to Source** from the popup menu, shown in the following figure.

| urces Netl                                                                                                                                      | ist ×                                                                                                                            | ? _ 🗆 🖸                                                                                                                   | Project | t Summa     | ry × D | vice         | × rtlRam.v                                                                                                                                                            | ×         |                   |               | ? 🗆        |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------|-------------|--------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------|---------------|------------|

| E H                                                                                                                                             |                                                                                                                                  | •                                                                                                                         | +       | ⇒ ©,        | Q 23   | $\mathbb{M}$ | 🕀 🛛 🕅 🛛 R                                                                                                                                                             |           |                   |               |            |

| shoopyrtam,                                                                                                                                     | _ieg_0_10                                                                                                                        | (POAMIDSOET) ~                                                                                                            |         |             |        | -            |                                                                                                                                                                       | ***       |                   |               | ***        |

|                                                                                                                                                 | -                                                                                                                                | (RAMB36E1)                                                                                                                |         |             |        | 开            |                                                                                                                                                                       |           |                   |               | - 33 24    |

|                                                                                                                                                 | -                                                                                                                                | (RAMB36E1)                                                                                                                |         |             |        | 田            |                                                                                                                                                                       | 88        |                   |               | 田田         |

|                                                                                                                                                 | -                                                                                                                                | (RAMB36E1)                                                                                                                |         |             |        | 囲            |                                                                                                                                                                       |           |                   |               | 123        |

|                                                                                                                                                 | -                                                                                                                                | (RAMB36E1)                                                                                                                |         |             |        | ##           |                                                                                                                                                                       |           |                   |               | 111        |

|                                                                                                                                                 |                                                                                                                                  | (RAMB36E1)                                                                                                                |         |             |        |              |                                                                                                                                                                       |           | 님                 |               |            |

|                                                                                                                                                 | -                                                                                                                                | (RAMB36E1)                                                                                                                |         |             |        | 田田           |                                                                                                                                                                       |           |                   |               | <b>HH</b>  |

|                                                                                                                                                 | -                                                                                                                                | (RAMB36E1)                                                                                                                |         |             |        |              |                                                                                                                                                                       |           |                   |               | <b>#</b> # |

|                                                                                                                                                 | -                                                                                                                                | (RAMB36E1)                                                                                                                |         |             |        |              |                                                                                                                                                                       |           |                   |               |            |

|                                                                                                                                                 | -                                                                                                                                | (RAMB36E1)                                                                                                                |         |             |        | ##           |                                                                                                                                                                       |           |                   |               | ###        |

|                                                                                                                                                 | -                                                                                                                                | (RAMB36E1)                                                                                                                |         |             |        |              | Cell Properties                                                                                                                                                       |           | Ctrl+E            |               |            |

|                                                                                                                                                 | -                                                                                                                                | (RAMB36E1)                                                                                                                |         |             |        |              | Unplace                                                                                                                                                               |           | Ctrl+U            |               |            |

|                                                                                                                                                 | _                                                                                                                                | (RAMB36E1)                                                                                                                |         |             |        | Į.           | Delete Cells                                                                                                                                                          |           |                   |               |            |

| snoopvRam                                                                                                                                       | _red_0_28                                                                                                                        | (RAMB36E1) ~                                                                                                              |         |             |        |              |                                                                                                                                                                       |           |                   |               |            |

|                                                                                                                                                 |                                                                                                                                  | · · · · ·                                                                                                                 |         |             |        |              | Figure 1 and 1 and                                                                                                                                                    |           |                   |               |            |

|                                                                                                                                                 |                                                                                                                                  |                                                                                                                           |         |             |        |              | Floorplanning                                                                                                                                                         |           | •                 |               |            |

| ell Properties                                                                                                                                  | 3                                                                                                                                | , – – , ×                                                                                                                 |         |             |        |              | Floorplanning<br>Select Leaf Cel                                                                                                                                      | l Parents | Þ                 |               |            |

|                                                                                                                                                 |                                                                                                                                  |                                                                                                                           |         |             |        |              |                                                                                                                                                                       | l Parents | Þ                 |               |            |

| snoopyRam_r                                                                                                                                     | eg_0_25                                                                                                                          | ←   ⇒   ✿                                                                                                                 |         | ×o¥         | 1      |              | Select Leaf Cel                                                                                                                                                       | l Parents | Þ                 | <u>et y t</u> |            |

| snoopyRam_r                                                                                                                                     | eg_0_25                                                                                                                          | ←   →   �<br>Engine0/usbl                                                                                                 |         | XoY         | 1      |              | Select Leaf Cel                                                                                                                                                       | l Parents | •                 | <u>et y t</u> |            |

| snoopyRam_r                                                                                                                                     | eg_0_25                                                                                                                          | ←   ⇒   ✿                                                                                                                 |         | жо <u>ү</u> | 1      | •            | Select Leaf Cell<br>Fix Cells<br>Unfix Cells<br>Highlight                                                                                                             | l Parents | •                 | <u>(171</u>   |            |

| snoopyRam_r<br>ame:<br>arent:                                                                                                                   | eg_0_25<br>ust                                                                                                                   | ←   →   �<br>Engine0/usbl                                                                                                 |         | жо <u>т</u> | 1      | •            | Select Leaf Cell<br>Fix Cells<br>Unfix Cells<br>Highlight<br>Unhighlight                                                                                              | I Parents | •                 |               |            |

| snoopyRam_n<br>ame:<br>arent:<br>eference nam                                                                                                   | eg_0_25<br>ust<br>e: RA                                                                                                          | ←   →   ✿<br>Engine0/usbl<br>usbEngine0/                                                                                  |         |             |        |              | Select Leaf Cell<br>Fix Cells<br>Unfix Cells<br>Highlight<br>Unhighlight<br>Mark                                                                                      | I Parents | )<br>(trl=Shift=M | <u>CT YI</u>  |            |

| snoopyRam_n<br>lame:<br>arent:<br>eference name<br>ype:                                                                                         | eg_0_25<br>ust<br>e: RAI<br>Blo                                                                                                  | ←   →   ✿<br>Engine0/usbl<br>usbEngine0/<br>MB36E1                                                                        |         | <u>×ογ</u>  |        | \$           | Select Leaf Cell<br>Fix Cells<br>Unfix Cells<br>Highlight<br>Unhighlight<br>Mark<br>Unmark                                                                            | l Parents | )<br>Ctrl+Shift+M | 41 71 2       |            |

| snoopyRam_r<br>ame:<br>arent:<br>eference name<br>ype:<br>EL:                                                                                   | eg_0_25<br>usk<br>e: RAI<br>Blo                                                                                                  | ←   →   ◆<br>Engine0/usbE<br>usbEngine0/<br>MB36E1<br>ck Memory<br>RAMB36E1                                               |         | жоү<br>жоү  |        |              | Select Leaf Cell<br>Fix Cells<br>Unfix Cells<br>Highlight<br>Unhighlight<br>Mark<br>Unmark.<br>Schematic                                                              |           | F4                |               |            |

| snoopyRam_n<br>lame:<br>arent:<br>eference name<br>ype:<br>EL:<br>te:                                                                           | eg_0_25<br>usk<br>e: RAJ<br>Blo<br>@                                                                                             | ← → ↓ ↔<br>Engine0/usbt<br>usbEngine0/<br>MB36E1<br>ck Memory<br>RAMB36E1<br>RAMB36_X0                                    |         |             |        | \$           | Select Leaf Cell<br>Fix Cells<br>Unfix Cells<br>Highlight<br>Unhighlight<br>Mark<br>Unmark                                                                            |           |                   | <u>¢tyr</u> t |            |

| snoopyRam_r<br>lame:<br>arent:<br>leference name<br>ype:<br>EL:<br>ite:<br>ile:                                                                 | eg_0_25 -<br>ust<br>e: RAI<br>Blo<br>III<br>IIII<br>IIII                                                                         | ← → ↓ ↔<br>Engine0/usbE<br>usbEngine0/<br>MB36E1<br>ck Memory<br>RAMB36E1<br>RAMB36_X0<br>BRAM_L_X6Y                      |         |             |        | \$           | Select Leaf Cell<br>Fix Cells<br>Unfix Cells<br>Highlight<br>Unhighlight<br>Mark<br>Unmark.<br>Schematic                                                              |           | F4                |               |            |

| snoopyRam_r<br>lame:<br>arent:<br>teference name<br>ype:<br>EL:<br>EL:<br>ite:<br>ite:<br>ilock region:                                         | eg_0_25 -<br>ust<br>e: RAJ<br>Blo<br>@<br>@                                                                                      | ← → ↓ ↓<br>Engine0/usbE<br>usbEngine0/<br>MB36E1<br>ck Memory<br>RAMB36E1<br>RAMB36_X0 <sup>•</sup><br>BRAM_L_X6Y<br>X0Y1 |         |             |        | \$           | Select Leaf Cell<br>Fix Cells<br>Unfix Cells<br>Highlight<br>Unhighlight<br>Mark<br>Unmark<br>Schematic<br>Show Connection                                            |           | F4<br>Ctrl+T      |               |            |

| snoopyRam_n<br>lame:<br>arent:<br>leference name<br>ype:<br>EL:<br>ite:<br>ite:<br>ile:<br>lock region:<br>lumber of cell                       | eg_0_25 •<br>usk<br>e: RAA<br>Blo<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E | ← → ↓ ↓<br>Engine0/usbt<br>usbEngine0/<br>MB36E1<br>ck Memory<br>RAMB36E1<br>RAMB36E1<br>BRAM_L_X6Y<br>X0Y1<br>3          |         |             |        | \$           | Select Leaf Cell<br>Fix Cells<br>Unfix Cells<br>Highlight<br>Unhighlight<br>Mark<br>Unmark<br>Schematic<br>Show Connection<br>Go to Source                            |           | F4<br>Ctrl+T      |               |            |

| snoopyRam_n<br>ame:<br>arent:<br>eference name<br>ype:<br>EL:<br>te:<br>te:<br>ile:<br>lock region:<br>umber of cell                            | eg_0_25 •<br>usk<br>e: RAA<br>Blo<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E | ← → ↓ ↓<br>Engine0/usbt<br>usbEngine0/<br>MB36E1<br>ck Memory<br>RAMB36E1<br>RAMB36E1<br>BRAM_L_X6Y<br>X0Y1<br>3          |         |             |        | \$           | Select Leaf Cell<br>Fix Cells<br>Unfix Cells<br>Highlight<br>Unhighlight<br>Mark<br>Unmark<br>Schematic<br>Show Connection<br>Go to Source<br>Select<br>View          |           | F4<br>Ctrl+T      |               |            |

| snoopyRam_n<br>ame:<br>arent:<br>eference name<br>ype:<br>EL:<br>te:<br>te:<br>ile:<br>lock region:<br>umber of cell<br>umber of nets           | eg_0_25 -<br>usk<br>e: RA4<br>Blo<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D<br>D | ← → ♦<br>Engine0/usbt<br>usbEngine0/<br>MB36E1<br>ck Memory<br>RAMB36E1<br>RAMB36_X0<br>BRAM_L_X6Y<br>X0Y1<br>3           |         |             |        | \$           | Select Leaf Cell<br>Fix Cells<br>Unfix Cells<br>Highlight<br>Unhighlight<br>Mark<br>Unmark<br>Schematic<br>Show Connectiv<br>Go to Source<br>Select<br>View<br>Metric | vity      | F4<br>Ctrl+T      |               |            |

| snoopyRam_r<br>lame:<br>Parent:<br>Reference name<br>Type:<br>IEL:<br>ite:<br>ite:<br>ile:<br>Ilock region:<br>Jumber of cell<br>Jumber of nets | eg_0_25 •<br>usk<br>e: RAA<br>Blo<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E<br>E | ← → ↓ ↓<br>Engine0/usbt<br>usbEngine0/<br>MB36E1<br>ck Memory<br>RAMB36E1<br>RAMB36E1<br>BRAM_L_X6Y<br>X0Y1<br>3          |         |             |        | \$           | Select Leaf Cell<br>Fix Cells<br>Unfix Cells<br>Highlight<br>Unhighlight<br>Mark<br>Unmark<br>Schematic<br>Show Connection<br>Go to Source<br>Select<br>View          | vity      | F4<br>Ctrl+T      |               |            |

Figure 6: Cross Probe Back To Source

Use cross probing to determine which source is involved in netlist gates. Due to the nature of synthesis transforms, it is not possible to cross probe back to source for every gate in the design.

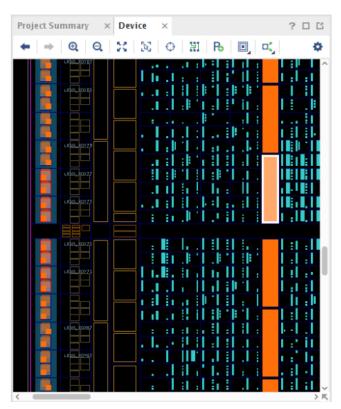

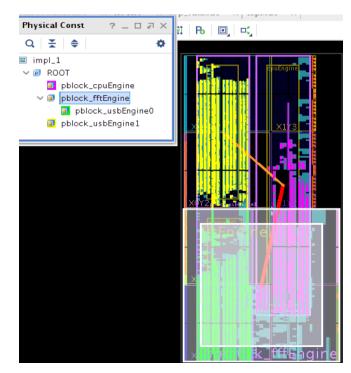

# **Viewing Metrics**

After implementation finishes, you may want to analyze the design to see how it interacts with the device. The Vivado IDE has a number of metrics to help you determine logic and routing usage inside the device. The Metrics color code the device window based on a specified rule. To view a metric, right-click in the Device window, select **Metric**, and then select the metric you would like to view. See the following figure.

| Sources Netlist          | × ?_         |          | Proje | ct Summ     | ary ×        | Device ×      |        | ? 🗆 🖸  |

|--------------------------|--------------|----------|-------|-------------|--------------|---------------|--------|--------|

| X H                      |              | •        | +     | ⇒ ©         |              | XXOI          | 1 Po 💽 | o( ) 🗘 |

| top                      |              |          |       | JT Utilizat | ion ner C    | IB            |        |        |

| > 📄 Nets (1136)          |              |          |       | or other    | ion per e    | 20            |        |        |

| > 🗎 Leaf Cells (156)     |              |          |       |             | 1            |               |        |        |

| > 😰 clkgen (clock_ge     | enerator)    |          |       |             |              |               |        |        |

| > 🔳 cpuEngine (or12      | 200_top)     |          |       |             |              | 1000          |        |        |

| > 😰 fftEngine (fftTop    | ))           |          |       |             |              |               |        |        |

| > 🔳 mgtEngine (mgt       | Top)         |          |       |             |              |               |        |        |

| > 👔 usbEngine0 (usl      | of_top)      |          |       |             | <b>BKO</b> Y | 1. Same 1     |        |        |

| > 🔳 usbEngine1 (us)      | bf_top_0)    |          |       |             |              |               | -      |        |

| > 🔋 wbArbEngine (w       | /b_conmax_to | (q       |       |             | All the      |               |        |        |

| File Properties          | ? _ 0        | ц×       |       |             |              |               | 3      |        |

| CLBLM_L_X12Y77           | + +          | •        |       |             |              |               |        |        |

| Q ≚ ♦ €                  | + -          | >>       |       |             |              |               |        |        |

| CLASS                    | tile         | ^        |       |             |              |               |        |        |

| COLUMN                   |              | 34       |       |             |              | £ 🖬 🔄 🕾 .     |        |        |

| DEVICE_ID                |              | 0        |       |             |              |               |        |        |

| FIRST_SITE_ID            | 11           | 564      |       |             |              | P             |        |        |

| GRID_POINT_X             |              | 34       |       |             |              |               |        |        |

| GRID_POINT_Y             |              | 127      |       |             |              | all an annual |        |        |

| INDEX                    | 14           | 893      |       |             | KOY          |               |        |        |

| General <b>Propertie</b> | s Cell Pit < | 1 ▶ Ξ    |       |             |              |               |        |        |

| Metric Results           |              |          |       |             |              |               | _      |        |

| H 🗃                      |              |          |       |             |              |               |        |        |

| Name                     | Туре         | Row      | Col   | Sites       | Cells        | LUT Util (%)  |        |        |

| CLBLL_L_X20Y2            | CLBLL_L      | 205      | 54    | 2           | 9            | 100.00        |        |        |

| CLBLL_L_X18Y2            | CLBLL_L      | 205      | 50    | 2           | 9            | 100.00        |        |        |

| CLBLM_R_X31Y3            | CLBLM_R      | 204      | 81    | 2           | 9            | 100.00        |        |        |

| CLBLM_R_X29Y3            | CLBLM_R      | 204      | 76    | 2           | 9            | 100.00        |        |        |

|                          | CLBLL_L      | 204      | 58    | 2           | 12           | 100.00        |        |        |

| <pre>ELBLL_L_X22Y3</pre> |              | 100.0004 | 1     | -           | 10000        |               |        |        |

| CLBLL_L_X22Y3            | CLBLL_L      | 204      | 54    | 2           | 8            | 100.00        |        |        |

Figure 7: Metrics

# **Metrics Requiring a Placed Design**

Four metrics require a placed design in order to be accurate. They do not require a fully routed design.

- LUT Utilization per CLB: Color codes slices based on placed LUT utilization.

- FF Utilization per CLB: Color codes slices based on placed FF utilization.

- Vertical Routing Congestion per CLB: Color codes the fabric based on a best case estimate of vertical routing usage.

- Horizontal Routing Congestion per CLB: Color codes the fabric based on a best case estimate of horizontal routing usage.

For UltraScale+ and newer architectures:

• Interconnect Congestion Level: Color codes the Interconnect Congestion Level based on a worst case estimate of routing usage over contiguous regions.

# Metrics in a Netlist Design with No Placement

Two metrics are applicable if there are Pblocks. They do not depend on placement:

- LUT Utilization per Pblock: Color codes the Pblock based on an estimate of how the LUTs will be placed into the slices contained in the Pblock.

- FF Utilization per Pblock: Color codes the Pblock based on an estimate of how the FFs will be packed into the slices contained in the Pblock.

More than one rule can be used at a time as shown in the previous figure. Both LUT Utilization per CLB and FF Utilization per CLB are on.

**TIP:** If there are sections of the design with high utilization or high estimates of routing congestion, consider tweaking the RTL or placement constraints to reduce logic and routing utilization in that area.

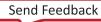

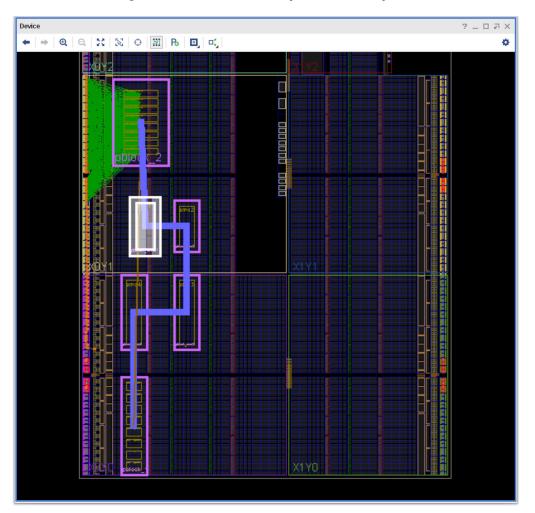

# **Routing Analysis**

Turn on Routing Resources in the Device window to view the exact routing resources.

| Sources Netlist                                                                                                                   | × ?_0Ľ                                                                                                                                                                   | Project Summary × Device ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ? 🗆   |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| ¥ H                                                                                                                               | 0                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| top                                                                                                                               |                                                                                                                                                                          | Routing Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17.58 |

| > 🗁 Nets (1136)                                                                                                                   |                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| > 🚞 Leaf Cells (156                                                                                                               | 6)                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| > 👔 clkgen (clock_g                                                                                                               | generator)                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| > 👔 cpuEngine (or 1                                                                                                               | 1200_top)                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| > 😰 fftEngine (fftTo                                                                                                              | (qo                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| > 🔳 mgtEngine (mg                                                                                                                 |                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| > 🔳 usbEngine0 (u                                                                                                                 | Service Mildleren                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

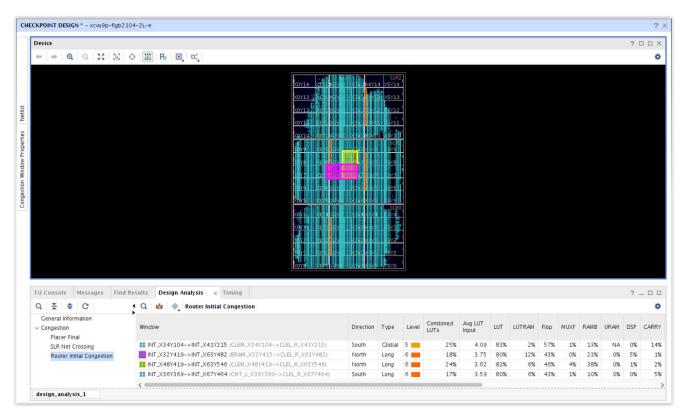

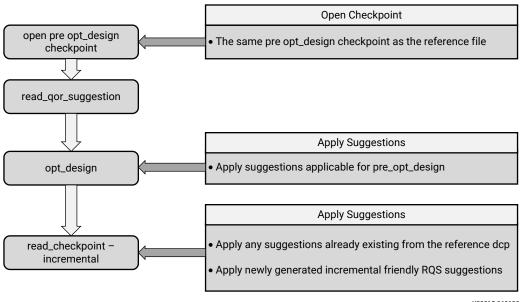

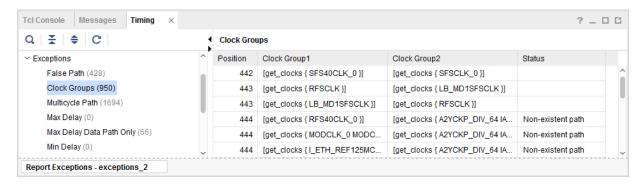

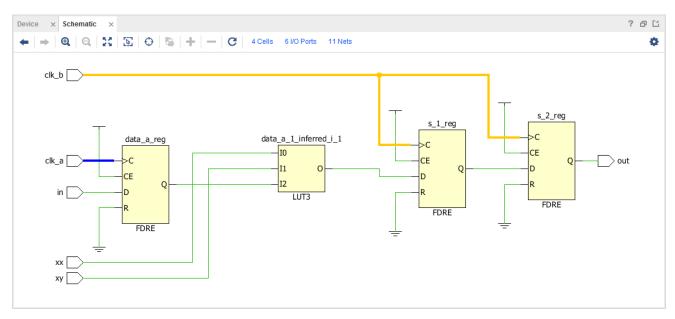

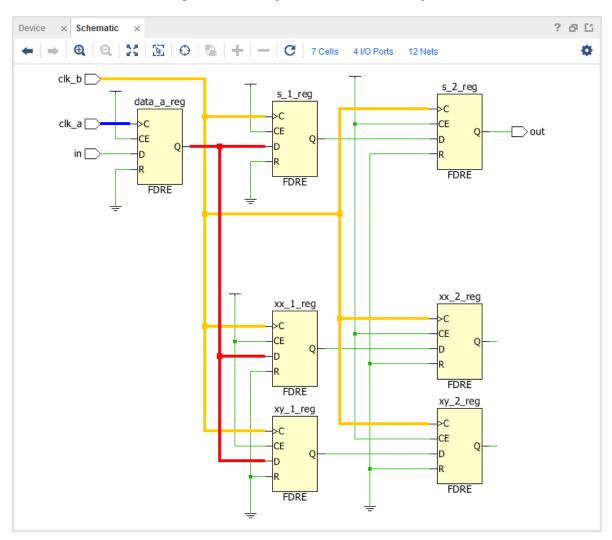

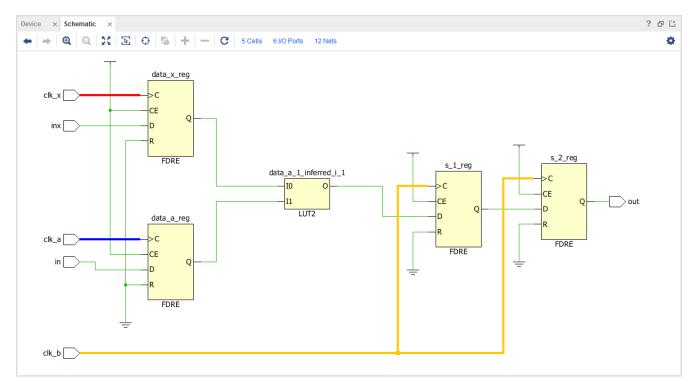

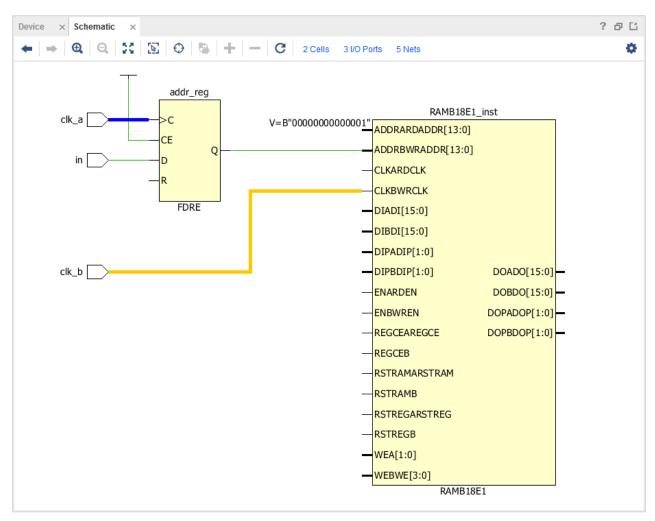

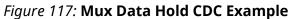

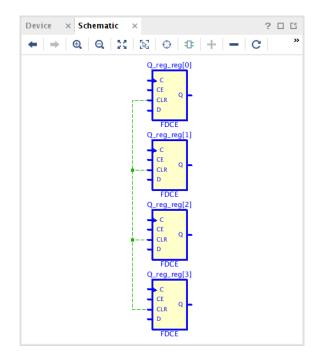

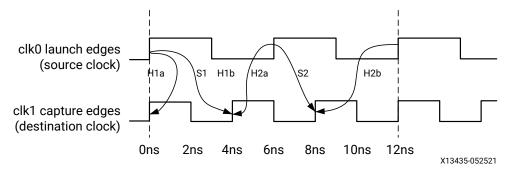

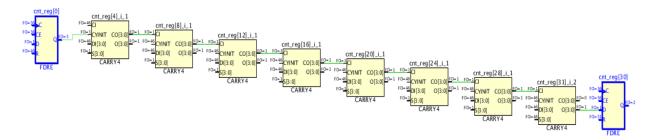

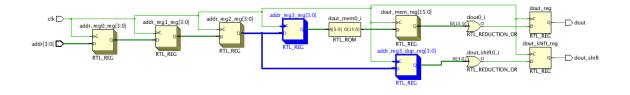

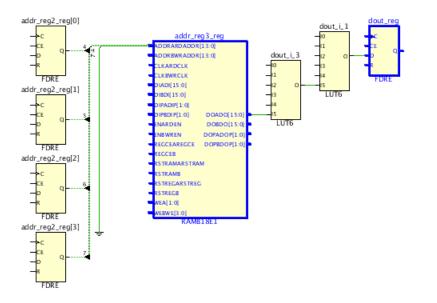

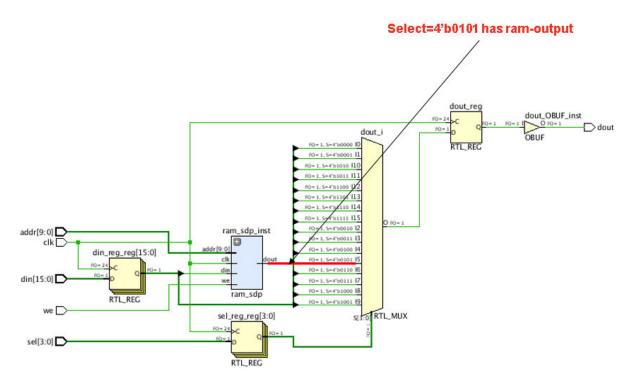

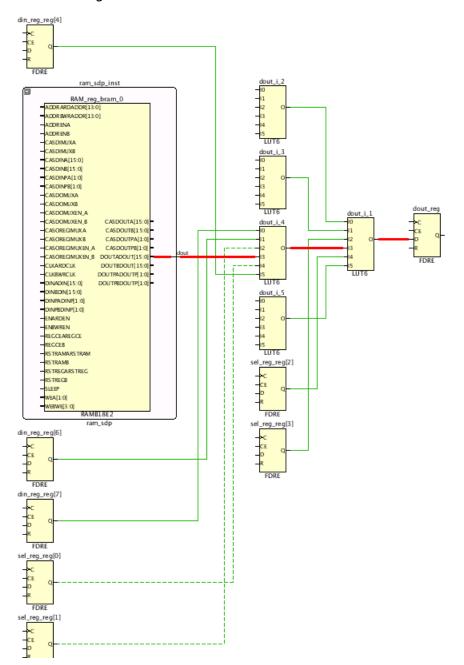

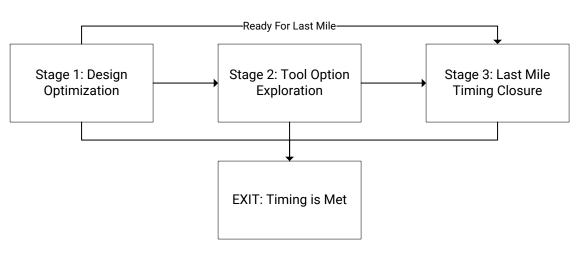

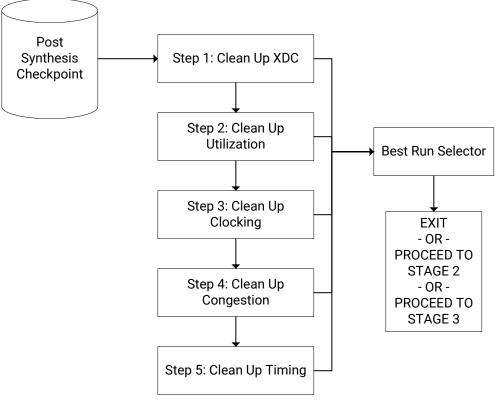

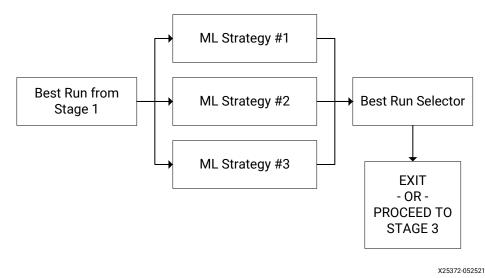

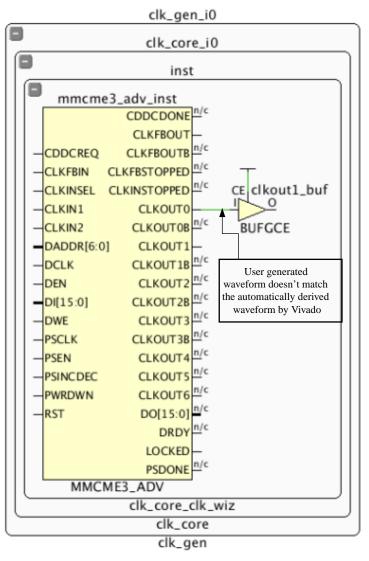

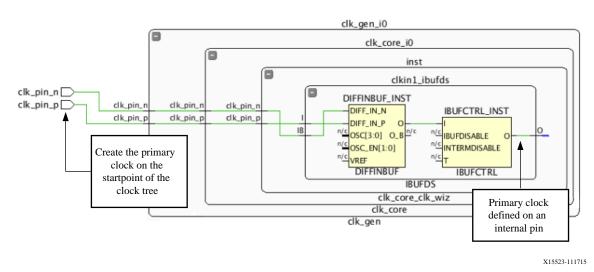

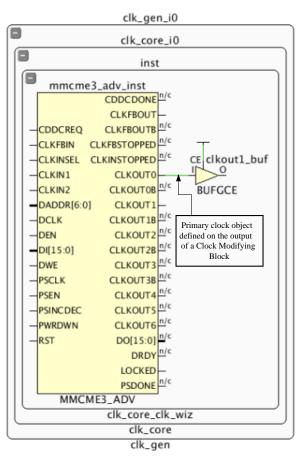

| > 😰 usbEngine1 (u                                                                                                                 |                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |