# Vivado Design Suite User Guide

# Dynamic Function eXchange

UG909 (v2020.2) February 25, 2022

Xilinx is creating an environment where employees, customers, and partners feel welcome and included. To that end, we're removing non-inclusive language from our products and related collateral. We've launched an internal initiative to remove language that could exclude people or reinforce historical biases, including terms embedded in our software and IPs. You may still find examples of non-inclusive language in our older products as we work to make these changes and align with evolving industry standards. Follow this <a href="link">link</a> for more information.

# **Table of Contents**

| Revision History                                                 | 5  |

|------------------------------------------------------------------|----|

| Chapter 1: Introduction                                          | 6  |

| Navigating Content by Design Process                             |    |

| Introduction to Dynamic Function eXchange                        |    |

| Terminology                                                      |    |

| Design Considerations                                            |    |

| Dynamic Function eXchange Licensing                              |    |

| Chapter 2: Common Applications                                   | 17 |

| Networked Multiport Interface                                    | 17 |

| Configuration by Means of Standard Bus Interface                 | 19 |

| Dynamically Reconfigurable Packet Processor                      | 21 |

| Asymmetric Key Encryption                                        | 21 |

| Summary                                                          | 23 |

| Chapter 3: Vivado Software Flow                                  | 24 |

| Dynamic Function eXchange Commands                               |    |

| Dynamic Function eXchange Constraints and Properties             |    |

| Apply Reset After Reconfiguration                                |    |

| Software Flow                                                    |    |

| Tcl Scripts                                                      |    |

| Nested Dynamic Function eXchange                                 |    |

| Abstract Shell for Dynamic Function eXchange                     |    |

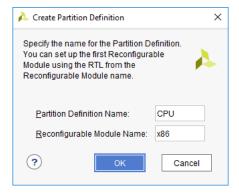

| Chapter 4: Vivado Project Flow                                   | 73 |

| Flow Summary                                                     | 73 |

| Steps for Creating and Using a Dynamic Function eXchange Project | 74 |

| Supported/Unsupported Features                                   |    |

| Chapter 5: Design Considerations and Guidelines for All Xilinx   |    |

| Devices                                                          | 94 |

| Dynamic Function eXchange IP                                     |    |

|                                                                  |    |

| Design Hierarchy                                                 | 95                       |

|------------------------------------------------------------------|--------------------------|

| Partition Pin Placement                                          | 99                       |

| Active-Low Resets and Clock Enables                              | 99                       |

| Decoupling Functionality                                         | 100                      |

| Black Boxes                                                      | 101                      |

| Effective Approaches for Implementation                          | 102                      |

| Configuration Analysis Report                                    | 103                      |

| Managing Constraints for a DFX Design                            | 107                      |

| Defining Reconfigurable Partition Boundaries                     | 109                      |

| Avoiding Deadlock                                                | 110                      |

| Design Revision Checks                                           | 110                      |

| Simulation and Verification                                      | 111                      |

| <b>Chapter 6: Design Considerations and Guidelines</b>           | for 7 Series             |

| and Zynq Devices                                                 | 112                      |

| Design Elements Inside Reconfigurable Modules                    | 112                      |

| Global Clocking Rules                                            | 113                      |

| Creating Pblocks for 7 Series Devices                            | 114                      |

| Using High Speed Transceivers                                    | 122                      |

| Dynamic Function eXchange Design Checklist (7 Series)            | 123                      |

| <b>Chapter 7: Design Considerations and Guidelines</b>           | for UltraScale           |

| and UltraScale+ Devices                                          | 126                      |

| Design Elements Inside Reconfigurable Modules                    |                          |

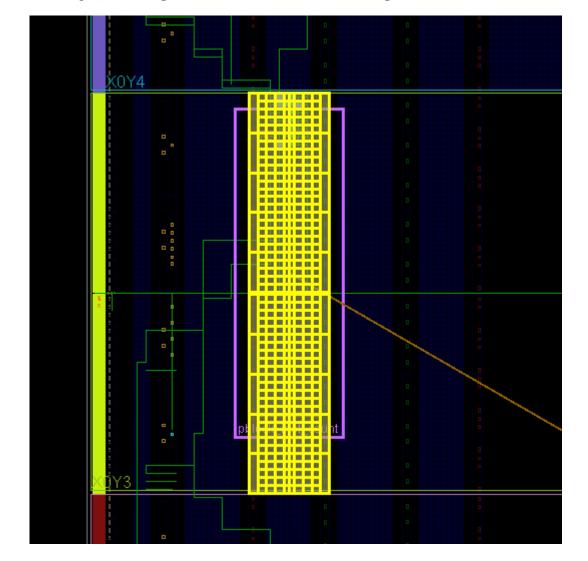

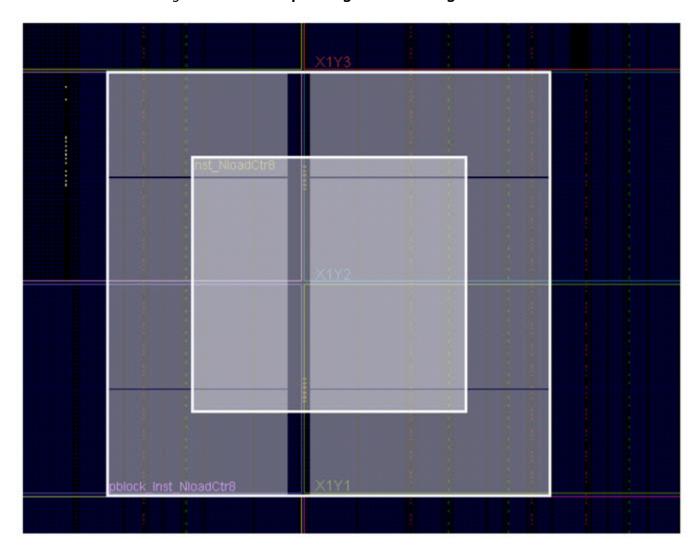

| Creating Pblocks for UltraScale and UltraScale+ Devices          | 127                      |

| Global Clocking Rules                                            | 138                      |

| I/O Rules                                                        | 139                      |

| Using High Speed Transceivers                                    | 141                      |

| Dynamic Function eXchange Checklist for UltraScale and UltraS    | cale+ Device Designs 141 |

| Chapter 8: Configuring the Device                                | 147                      |

| Configuration Modes                                              | 147                      |

| Bitstream Type Definitions                                       | 149                      |

| Dynamic Function eXchange through ICAP for Zynq Devices          | 154                      |

| Tandem Configuration and Dynamic Function eXchange               | 154                      |

| Formatting BIN Files for Delivery to Internal Configuration Port | s159                     |

| Summary of BIT Files for UltraScale Devices                      | 160                      |

| System Design for Configuring an EPGA                            | 161                      |

| Partial BIT File Integrity                                                                                                      | 163               |

|---------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Configuration Frames                                                                                                            | 164               |

| Configuration Time                                                                                                              | 165               |

| Configuration Debugging                                                                                                         | 166               |

| Using Vivado Debug Cores                                                                                                        | 169               |

| Chapter 9: Known Issues and Limitations                                                                                         | 174               |

| Known Limitations                                                                                                               | 174               |

|                                                                                                                                 |                   |

| Chapter 10: Hierarchical Design Flows                                                                                           | 176               |

| Chapter 10: Hierarchical Design FlowsAppendix A: Additional Resources and Legal Notices                                         |                   |

|                                                                                                                                 | 177               |

| Appendix A: Additional Resources and Legal Notices                                                                              | <b>177</b><br>177 |

| Appendix A: Additional Resources and Legal Notices  Xilinx Resources                                                            |                   |

| Appendix A: Additional Resources and Legal Notices  Xilinx Resources  Solution Centers                                          | 177177177177      |

| Appendix A: Additional Resources and Legal Notices  Xilinx Resources  Solution Centers  Documentation Navigator and Design Hubs |                   |

# **Revision History**

The following table shows the revision history for this document.

| Section                                      | Revision Summary                                                                  |  |

|----------------------------------------------|-----------------------------------------------------------------------------------|--|

| 02/25/2022 Version 2020.2                    |                                                                                   |  |

| General                                      | Editorial updates.                                                                |  |

| 02/08/2021 Version 2020.2                    |                                                                                   |  |

| Abstract Shell for Dynamic Function eXchange | Added the Abstract Shell for Dynamic Function eXchange section.                   |  |

| 06/24/2020 Version 2020.1                    |                                                                                   |  |

| General                                      | Replaced all instances of Partial Reconfiguration with Dynamic Function eXchange. |  |

| Chapter 3: Vivado Software Flow              | Added the Nested Dynamic Function eXchange section                                |  |

# Introduction

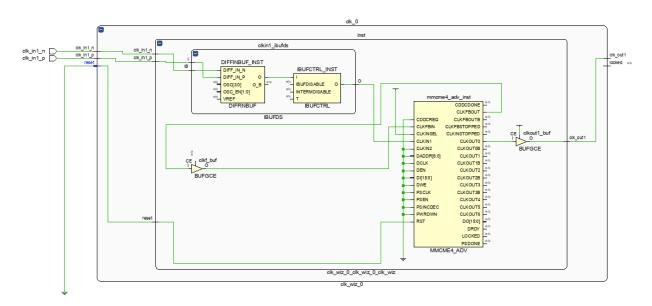

Dynamic Function eXchange (DFX) allows for the reconfiguration of modules within an active design. This flow requires the implementation of multiple configurations, which ultimately results in full bitstreams for each configuration and partial bitstreams for each reconfigurable module (RM). The number of configurations required varies by the number of modules that need to be implemented. However, all configurations use the same top-level, or static, placement and routing results. These static results are exported from the initial configuration and imported by all subsequent configurations using checkpoints.

DFX is a comprehensive solution that is comprised of many parts. These elements include the Xilinx<sup>®</sup> silicon ability to be dynamically reconfigured, the Vivado<sup>®</sup> software flow for compiling designs from RTL to bitstream, and the complementary features such as IP. In this release, you will see a mix of DFX and Partial Reconfiguration (PR) terminology, with DFX representing the overall solution and PR representing a component technology piece of that solution.

Complementary documentation, such as application notes, white papers, and videos, will not be recaptured with DFX terminology, but all new documentation from 2020 on will show the DFX terms.

The content of this guide includes the following:

- Description of Dynamic Function eXchange as implemented in the Vivado® Design Suite

- Assumption of familiarity with FPGA design software, particularly Vivado Design Suite

- Updates specific to the Vivado Design Suite Release 2020.2. This release supports Dynamic Function eXchange for the products listed below:

- . 7 series Devices

- Nearly all Virtex®-7, Kintex®-7, Artix®-7, and Zynq®-7000 SoC devices.

Note: Spartan-7 devices, as well as Artix-7A12T and 7A25T, are not supported.

- UltraScale™ Devices

- Place and route, as well as bitstream generation is enabled for all production devices.

Note: Access to the VU440 is not restricted in this release. However, expect memory usage to be higher for this device than all others (potentially exceeding 64 MB).

- Bitstream generation is disabled by default for ES2 devices, but place and route can still be performed.

- . UltraScale+ Devices

- Place and route, as well as bitstream generation, is enabled for all production devices, including all Zyng UltraScale+ RFSoCs and the Virtex UltraScale+ VU23P.

- Place and route is enabled for all Virtex UltraScale+ VU57P devices, but bitstreams are gated by a parameter as device support is still beta.

- Place and route is enabled for many engineering silicon (ES1, ES2) versions of UltraScale+ devices. Bitstream generation is disabled by default for these devices.

- **Versal Devices**

- DFX support for Versal devices is limited early access in this release. Please contact your local FAE or support provider to request access.

**VIDEO:** For an overview of the Vivado Partial Reconfiguration solution in 7 series devices, see the Vivado Design Suite QuickTake Video: Partial Reconfiguration in Vivado. For an overview of the Vivado Partial Reconfiguration solution in UltraScale devices, see the Vivado Design Suite QuickTake Video: Partial Reconfiguration for UltraScale.

## **Navigating Content by Design Process**

Xilinx® documentation is organized around a set of standard design processes to help you find relevant content for your current development task. All Versal™ ACAP design process Design Hubs can be found on the Xilinx.com website. This document covers the following design processes:

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, subsystem functional simulation, and evaluating the Vivado® timing, resource use, and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Chapter 3: Vivado Software Flow

- Chapter 4: Vivado Project Flow

- Chapter 5: Design Considerations and Guidelines for All Xilinx Devices

- Chapter 6: Design Considerations and Guidelines for 7 Series and Zyng Devices

- Chapter 7: Design Considerations and Guidelines for UltraScale and UltraScale+ Devices

- Board System Design: Designing a PCB through schematics and board layout. Also involves power, thermal, and signal integrity considerations. Topics in this document that apply to this design process include:

- Chapter 8: Configuring the Device

# Introduction to Dynamic Function eXchange

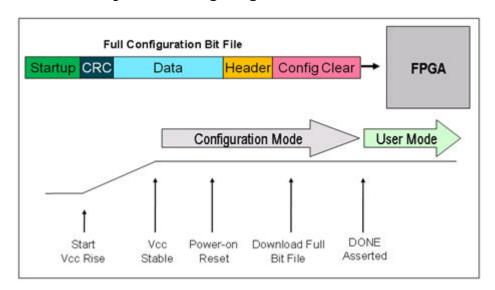

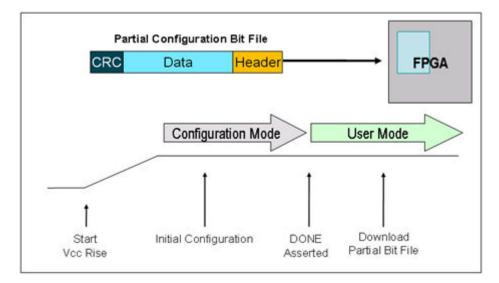

FPGA technology provides the flexibility of on-site programming and re-programming without going through re-fabrication with a modified design. Dynamic Function eXchange (DFX) takes this flexibility one step further, allowing the modification of an operating FPGA design by loading a dynamic configuration file, usually a partial BIT file. After a full BIT file configures the FPGA, partial BIT files can be downloaded to modify reconfigurable regions in the FPGA without compromising the integrity of the applications running on those parts of the device that are not being reconfigured.

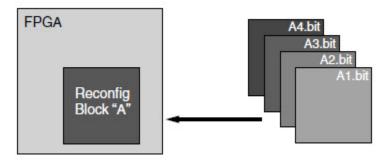

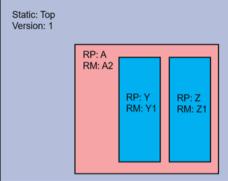

Introduction to Dynamic Function eXchange illustrates the premise behind Dynamic Function eXchange.

Figure 1: Basic Premise of Dynamic Function eXchange

As shown, the function implemented in Reconfig Block A is modified by downloading one of several partial BIT files, A1.bit, A2.bit, A3.bit, or A4.bit. The logic in the FPGA design is divided into two different types, reconfigurable logic and static logic. The gray area of the FPGA block represents static logic and the block portion labeled Reconfig Block "A" represents reconfigurable logic. The static logic remains functioning and is unaffected by the loading of a partial BIT file. The reconfigurable logic is replaced by the contents of the partial BIT file.

There are many reasons why the ability to time multiplex hardware dynamically on a single FPGA is advantageous. These include:

- Reducing the size of the FPGA required to implement a given function, with consequent reductions in cost and power consumption

- Providing flexibility in the choices of algorithms or protocols available to an application

- Enabling new techniques in design security

- Improving FPGA fault tolerance

- Accelerating configurable computing

- Delivering updates (fixes and new features) to deployed systems

In addition to reducing size, weight, power and cost, Dynamic Function eXchange enables new types of FPGA designs that would be otherwise impossible to implement.

# **Terminology**

The following terminology is specific to the Dynamic Function eXchange feature and is used throughout this document.

### **Bottom-Up Synthesis**

Bottom-Up Synthesis is synthesis of the design by modules, whether in one project or multiple projects. InVivado, bottom-up synthesis is referred to as out-of-context (OOC) synthesis. OOC synthesis generates a separate netlist (or DCP) per OOC module, and is required for Dynamic Function eXchange to ensure no optimization occurs across the module boundary. In OOC synthesis, the top-level (or static) logic is synthesized with black\_box module definitions for each OOC module.

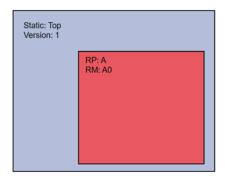

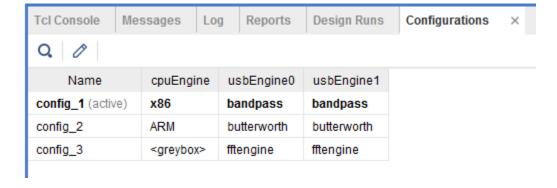

### Configuration

A configuration is a complete design that has one RM for each reconfigurable partition (RP). There might be many configurations in a Dynamic Function eXchange FPGA project. Each configuration generates one full BIT file as well as one partial BIT file for each RM.

### **Configuration Frame**

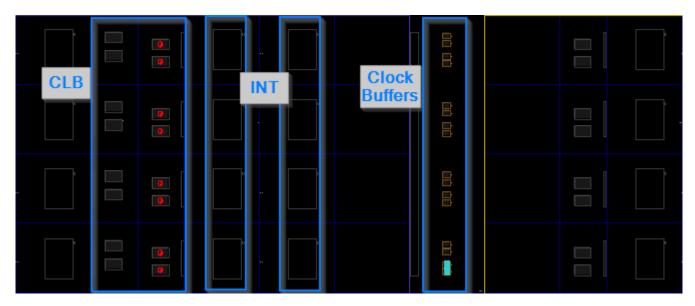

Configuration frames are the smallest addressable segments of the FPGA configuration memory space. Reconfigurable frames are built from discrete numbers of these lowest-level elements. In Xilinx devices, the base reconfigurable frames are one element (CLB, block RAM, DSP) wide by one clock region high. The number of resources in these frames vary by device family.

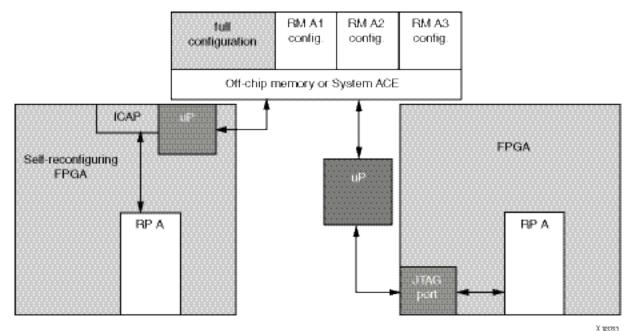

### **Internal Configuration Access Port (ICAP)**

The internal configuration access port (ICAP) is essentially an internal version of the SelectMAP interface. For more information, see the 7 Series FPGAs Configuration User Guide (UG470) References or the UltraScale Architecture Configuration User Guide (UG570) References.

## Media Configuration Access Port (MCAP)

The MCAP is dedicated link to the configuration engine from one specific PCle<sup>®</sup> block per UltraScale<sup>™</sup> device. This entry point can be enabled when configuring the Xilinx PCle IP.

#### **Partition**

A Partition is a logical section of the design, user-defined at a hierarchical boundary, to be considered for design reuse. A Partition is either implemented as new or preserved from a previous implementation. A Partition that is preserved maintains not only identical functionality but also identical implementation.

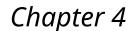

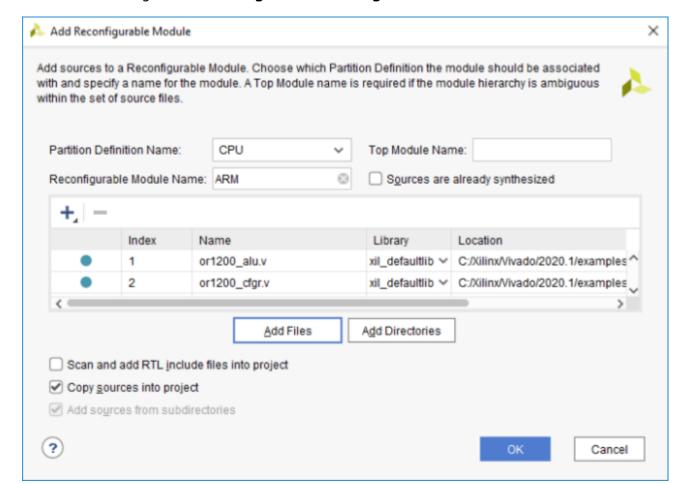

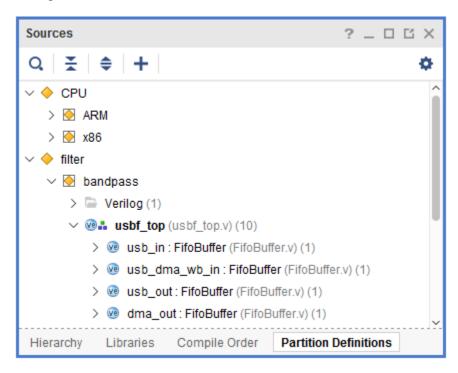

### Partition Definition (PD)

This is a term used within the project flow only. A Partition Definition defines a set of RMs that are associated with the module instance (or RP). A PD is applied to all instances of the module, and cannot be associated with a subset of module instances.

#### **Partition Pin**

Partition pins are the logical and physical connection between static logic and reconfigurable logic. The tools automatically create, place, and manage partition pins.

### Partial Reconfiguration (PR)

Partial reconfiguration (PR) is the Xilinx silicon technology that enables users to modify a subset of logic in an operating FPGA design by downloading a partial bitstream. The overall solution name has changed to Dynamic Function eXchange, but the underlying capability of the silicon remains, so references to PR, especially in fundamental Tcl commands, can still be seen in Vivado.

### **Processor Configuration Access Port (PCAP)**

The processor configuration access port (PCAP) is similar to the internal configuration access port (ICAP) and is the primary port used for configuring a Zynq-7000 SoC device. For more information, see the Zynq-7000 SoC Technical Reference Manual (UG585) References.

### Programmable Unit (PU)

In the UltraScale architecture, this is the minimum required resources for reconfiguration. The size of a PU varies by resource type. Because adjacent sites share a routing resource (or Interconnect tile) in the UltraScale architecture, a PU is defined in terms of pairs.

### **Reconfigurable Frame**

Reconfigurable frames (in all references other than "configuration frames" in this guide) represent the smallest reconfigurable region within an FPGA. Bitstream sizes of reconfigurable frames vary depending on the types of logic contained within the frame.

### **Reconfigurable Logic**

Reconfigurable logic is any logical element that is part of an RM. These logical elements are modified when a partial BIT file is loaded. Many types of logical components can be reconfigured such as LUTs, flip-flops, block RAM, and DSP blocks.

### **Reconfigurable Module**

An RM is the netlist or HDL description that is implemented within an RP. Multiple RMs exist for an RP.

### **Reconfigurable Partition**

RP is an attribute set on an instantiation that defines the instance as reconfigurable. The RP is the level of hierarchy within which different RMs are implemented. Tcl commands such as opt\_design, place\_design and route\_design detect the HD.RECONFIGURABLE property on the instance and process it correctly.

### Static Logic

Static logic is any logical element that is not part of an RP. The logical element is never partially reconfigured and is always active when RPs are being reconfigured. Static logic is also known as top-level logic.

### Static Design

The static design is the part of the design that does not change during partial reconfiguration. The static design includes the top-level and all modules not defined as reconfigurable. The static design is built with static logic and static routing.

## **Design Considerations**

Dynamic Function eXchange is an expert flow within the Vivado Design Suite. The following requirements and expectations need to be understood before embarking on a DFX project.

## **Design Requirements and Guidelines**

- Dynamic Function eXchange requires the use of Vivado 2013.3 or newer.

- Partial reconfiguration is supported in the ISE Design Suite as well. Use the ISE Design Suite for PR only with Virtex-6, Virtex-5 and Virtex-4 devices. See the Partial Reconfiguration User Guide (v14.5) (UG702) for more information.

- Floorplanning is required to define reconfigurable regions, per element type.

- For 7 series, vertically align Pblocks with frame/clock region boundaries. This produces the best results and allows RESET\_AFTER\_RECONFIG to be enabled.

- For UltraScale, the floorplanning is more flexible. Xilinx recommends stopping the Pblock short of frame/clock region boundaries to allow for expanded routing, which can greatly improve routability and quality.

- Horizontal alignment rules also apply. See Create a Floorplan for the Reconfigurable Region for more information.

- Automatic expansion for routing resources is done for all UltraScale and UltraScale+ device targets.

- Bottom-up/OOC synthesis (to create multiple netlist/DCP files) and management of RM netlist files is the responsibility of the user.

- For third party synthesis tools, I/O insertion must be disabled.

- For Vivado OOC synthesis, I/O insertion is automatically disabled in the out\_of\_context mode.

- Standard timing constraints are supported, and additional timing budgeting capabilities are available if needed.

- A unique set of design rule checks (DRCs) has been established to help ensure successful design completion.

- A DFX design must consider the initiation of partial reconfiguration as well as the delivery of partial BIT files, either within the FPGA or as part of the system design.

- The Vivado Design Suite includes support for the Dynamic Function eXchange Controller IP.

This customizable IP manages the core tasks for partial reconfiguring any Xilinx device. The

core receives triggers from hardware or software, manages handshaking and decoupling tasks,

fetches partial bitstreams from memory locations, and delivers them to the ICAP. More

information on the DFX Controller IP is available on the Xilinx website.

- An RP must contain a super set of all pins to be used by the varying reconfigurable modules

(RM) implemented for the partition. If an RM uses different inputs or outputs from another

RM, the resulting RM inputs or outputs might not connect inside of the RM. The tools handle

this by inserting a LUT1 buffer within the RM for all unused inputs and outputs. The output

LUT1 is tied to a constant value and the value of the constant can be controlled by

HD.PARTPIN\_TIEOFF property on the unused output pin. For more information on this

property refer to Black Boxes

- Black boxes are supported for bitstream generation. See Black Boxes for details about how to tie off ports with constant values.

- For user reset signals, determine if the logic inside the RM is level or edge sensitive. If the reset circuit is edge sensitive (as it may be in some IP such as FIFOs), the RM reset should not be applied until after reconfiguration is complete.

DFX designs are compatible with the Xilinx Isolation Design Flow (IDF) for Zynq MPSoC devices. For more information on solution details, please consult XAPP1335, the Isolation Design Flow for UltraScale+ FPGAs and Zynq UltraScale+ MPSoCs application note.

## **Design Performance**

Performance metrics vary from design to design, and the best results are achieved if you follow the Hierarchical Design techniques suggested in Chapter 10: Hierarchical Design Flows. This documents was created for the ISE Design Suite, but the methodologies contained therein apply for the Vivado Design Suite. You can find additional design recommendations in the *UltraFast Design Methodology Guide for Xilinx FPGAs and SoCs* (UG949).

However, the additional restrictions that are required for silicon isolation are expected to have an impact on most designs. The application of partial reconfiguration rules, such as routing containment, exclusive placement, and no optimization across RM boundaries, means that the overall density and performance is lower for a DFX design than for the equivalent flat design. The overall design performance for DFX designs varies from design to design, based on factors such as the number of RPs, the number of interface pins to these partitions, and the size and shape of Pblocks.

Any potential Dynamic Function eXchange design must have extra timing slack and resource overhead before considering this solution. See the <u>Building Up Implementation Requirements</u> section for more information on evaluating a design for DFX.

## **Design Criteria**

Some component types can be reconfigured and some cannot.

- For 7 series devices, the component rules are as follows:

- Reconfigurable resources include CLB, block RAM, and DSP component types as well as routing resources.

- Clocks and clock modifying logic cannot be reconfigured, and therefore must reside in the static region.

- Includes BUFG, BUFR, MMCM, PLL, and similar components

- The following components cannot be reconfigured, and therefore must reside in the static region:

- I/O and I/O related components (ISERDES, OSERDES, IDELAYCTRL)

- Serial transceivers (MGTs) and related components

- Individual architecture feature components (such as BSCAN, STARTUP, ICAP, XADC.)

- For UltraScale and UltraScale+ devices, the list of reconfigurable component types is more extensive:

- CLB, block RAM, and DSP component types as well as routing resources

- Clocks and clock modifying logic, including BUFG, MMCM, PLL, and similar components

- 。 I/O and I/O related components (ISERDES, OSERDES, IDELAYCTRL)

- Note: The types of changes for I/O components is limited. See I/O Rules for more information.

- Serial transceivers (MGTs) and related components

- PCIe, CMAC, Interlaken, and SYSMON blocks

- Bitstream granularity of these new components require that certain rules are followed. For example, partial reconfiguration of I/O require that the entire bank, plus all clocking resources in that frame are reconfigured together.

- Only the configuration components (such as BSCAN, STARTUP, ICAP, and FRAME\_ECC) must remain in the static portion of the design.

- Global clocking resources to RPs are limited, depending on the device and on the clock regions occupied by these RPs.

- IP restrictions may occur due to components used to implement the IP or due to connections required by the IP. Examples include:

- Vivado Debug Cores (See Using Vivado Debug Cores for more information on using debug cores inside of RMs)

- IP modules with embedded global buffers or I/O (7 series only)

- Memory IP controller (MMCM and BSCAN)

- RMs must be initialized to ensure a predictable starting condition after reconfiguration. For all devices other than 7 series, GSR is automatically applied after DFX completes. For 7 series devices, GSR can be turned on, after meeting Pblock requirements, with the RESET\_AFTER\_RECONFIG Pblock property.

- Decoupling logic is highly recommended to disconnect the reconfigurable region from the static portion of the design during the act of partial reconfiguration.

- GSR events hold all logic inside the RM in reset until configuration completes. However, RM outputs can be random and all downstream logic should be decoupled. For 7 series, if RESET\_AFTER\_RECONFIG is not used, additional decoupling of clocks and inputs can be required to prevent unintended capture of erroneous data of during reconfiguration (e.g. spurious write to memory).

- The Vivado Design Suite includes the Partial Reconfiguration Decoupler IP. This IP allows users to easily insert MUXes to efficiently decouple AXI4-Lite, AXI4-Stream, and custom interfaces. More information on the PR Decoupler IP is available on the Xilinx website.

- An RP must be floorplanned with a Pblock, so the module must be a block that can be

physically isolated and meet timing. If the module is complete, it is recommended to run this

design through a non-DFX flow to get an initial evaluation of placement, routing, and timing

results. If the design has issues in a non-DFX flow, these should be resolved before moving on

to the DFX flow.

- Optimize an RP's interface as much as possible. An excessive number of interface pins on an RP can cause timing and routing issues. This is especially true if the partition pins are densely placed. This can happen for two reasons:

- 1. RP Pblock is relatively small compared to the number of partition pins

- 2. All the partition pins are placed in a small area due to static connections.

Consider the RP interface when designing and floorplanning for DFX.

- Virtex-7 SSI devices (7V2000T, 7VX1140T, 7VH870T, 7VH580T) have two fundamental requirements. These requirements are:

- Reconfigurable regions must be fully contained within a single SLR. This ensures that the global reset events are properly synchronized across all elements in the RM, and that all super long lines (SLL) are contained within the static portion of the design. SLL are not partially reconfigurable.

- If the initial configuration of a 7 series SSI device is done through an SPIx1 interface, partial bitstreams must be delivered to the ICAP located on the SLR where the RP exists, or to an external port, such as JTAG. If the initial configuration is done through any other configuration port, the master ICAP can be used as the delivery port for partial bitstreams.

- UltraScale devices have a new requirement related to partial reconfiguration events. Before a

partial bitstream for a new RM is loaded, the current RM must be "cleared" to prepare for

reconfiguration. UltraScale+ devices do not have this limitation. For more information, see

Summary of BIT Files for UltraScale Devices.

- Dedicated encryption support for partial bitstreams is available natively. See Known Limitations for specific unsupported use cases for UltraScale devices.

- Devices can use a per-frame CRC checking mechanism, enabled by write\_bitstream, to ensure each frame is valid before loading.

- Optimization across the DFX boundary is prohibited by the implementation tools. Often the WNS paths in a DFX design are high fanout control/reset signals that cross the RP boundary. Avoid high fanout signals crossing the RP boundary because the drivers cannot be replicated. To allow the tools maximum flexibility of optimization/replication, consider the following:

- For inputs to the RP, make the signal crossing the RP boundary a single fanout net, and register the signal inside the RM before the fanout. This can be replicated as necessary inside the RM (or put on global resources).

- For outputs, again make the signal crossing the DFX boundary a single fanout net. Register the signal in static before the fanout for replication/optimization.

- For design with multiple RPs, Xilinx recommends not having direct connections between two RPs. This includes connections that go through asynchronous static logic (not registered in static). If direct connections exist between two RPs, all possible configurations must be verified in static timing analysis to ensure timing is met across these interfaces. This can be done for closed systems that are fully owned and maintained by a single user, but can be impossible to verify for designs where different RMs are developed by multiple users. Adding a synchronous endpoint in static ensures timing is always met on any configuration, as long as the configuration where the RM was implemented met timing.

Dynamic Function eXchange is a powerful capability within Xilinx devices, and understanding the capabilities of the silicon and software is instrumental to success. While trade-offs must be recognized and considered during the development process, the overall result is a more flexible implementation of your FPGA design.

# **Dynamic Function eXchange Licensing**

Dynamic Function eXchange is available as a feature within the Vivado Design Suite. Starting with Vivado 2019.1, no specific license code is necessary to use this feature for any edition of Vivado.

For older versions of Vivado, a Partial Reconfiguration license is included with every System Edition and Design Edition seat, and is available for purchase for WebPACK Edition seats.

# **Common Applications**

The basic premise of Dynamic Function eXchange (DFX) is that the device hardware resources can be time-multiplexed similar to the ability of a microprocessor to switch tasks. Because the device is switching tasks in hardware, it has the benefit of both flexibility of a software implementation and the performance of a hardware implementation. Several different scenarios are presented here to illustrate the power of this technology.

# **Networked Multiport Interface**

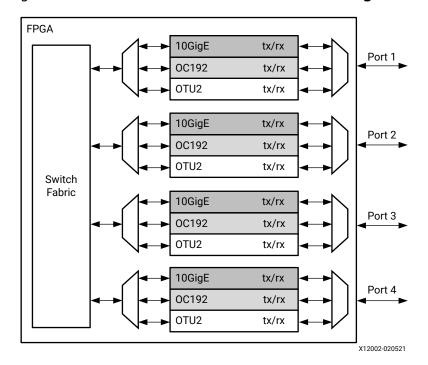

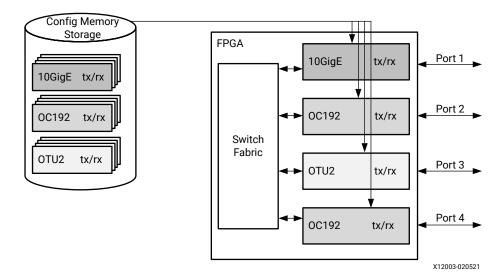

Dynamic Function eXchange optimizes traditional FPGA applications by reducing size, weight, power, and cost. Time-independent functions can be identified, isolated, and implemented as reconfigurable modules (RM) and swapped in and out of a single device as needed. A typical example is a 40G OTN muxponder application. The ports of the client side of the muxponder can support multiple interface protocols. However, it is not possible for the system to predict which protocol will be used before the FPGA is configured. To ensure that the FPGA does not have to be reconfigured and thus disable all ports, every possible interface protocol is implemented for every port, as illustrated in Networked Multiport Interface.

Figure 2: Network Switch Without Partial Reconfiguration

This is an inefficient design because only one of the standards for each port is in use at any point in time. Dynamic Function eXchange enables a more efficient design by making each of the port interfaces an RM, as shown in Networked Multiport Interface. This also eliminates the MUX elements required to connect multiple protocol engines to one port.

Figure 3: Network Switch With Partial Reconfiguration

A wide variety of designs can benefit from this basic premise. Software defined radio (SDR), for example, is one of many applications that has mutually exclusive functionality, and which sees a dramatic improvement in flexibility and resource usage when this functionality is multiplexed.

There are additional advantages with a dynamically reconfigurable design other than efficiency. In the Networked Multiport Interface example, a new protocol can be supported at any time without affecting the static logic, the switch fabric in this example. When a new standard is loaded for any port, the other existing ports are not affected in any way. Additional standards can be created and added to the configuration memory library without requiring a complete redesign. This allows greater flexibility and reliability with less down time for the switch fabric and the ports. A debug module could be created so that if a port was experiencing errors, an unused port could be loaded with analysis/correction logic to handle the problem real-time.

In the Networked Multiport Interface example, a unique partial BIT file must be generated for each unique physical location that could be targeted by each protocol. Partial BIT files are associated with an explicit region on the device. In this example, sixteen unique partial BIT files to accommodate four protocols for four locations.

# Configuration by Means of Standard Bus Interface

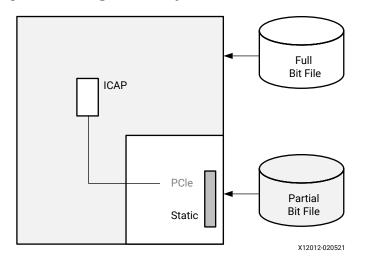

Dynamic Function eXchange can create a new configuration port using an interface standard more compatible with the system architecture. For example, the FPGA could be a peripheral on a PCIe® bus and the system host could configure the FPGA through the PCIe connection. After power-on reset the FPGA must be configured with a full BIT file. However, the full BIT file might only contain the PCIe interface and connection to the internal configuration access port (ICAP).

Bitstream compression can be used to reduce the size and therefore configuration time of this initial device load, helping the FPGA configuration meet PCle enumeration specifications.

The system host could then configure the majority of the FPGA functionality with a partial BIT file downloaded through the PCIe port as shown in Configuration by Means of Standard Bus Interface. An example of fast configuration over PCIe is shown in XAPP1338, with an example targeting UltraScale+™ included.

Figure 4: Configuration by Means of PCIe Interface

The PCIe standard requires the peripheral (the FPGA in this case) to acknowledge any requests even if it cannot service the request. Reconfiguring the entire FPGA would violate this requirement. Because the PCIe interface is part of the static logic, it is always active during the dynamic reconfiguration process, thus ensuring that the FPGA can respond to PCIe commands even during reconfiguration.

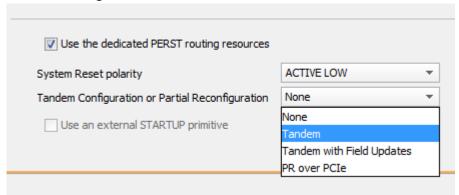

Tandem Configuration is a related solution that at first glance appears to be the same as is shown here. However, the solution using Dynamic Function eXchange differs from Tandem Configuration in two regards:

- The configuration process with DFX is a full device configuration, made smaller and faster through compression, followed by a partial bitstream that overwrites the black box region to complete the overall configuration. Tandem Configuration is a two-stage configuration where each configuration frame is programmed exactly once.

- Tandem Configuration for 7 series devices does not permit dynamic reconfiguration of the

user application. Using DFX, the dynamic region can be reloaded with different user

applications or field updates. Tandem Configuration for UltraScale devices does permit Field

Updates and compatibility with DFX in general. The overall flow is Tandem Configuration for a

two-stage initial load, followed by partial reconfiguration to dynamically modify the user

application.

Tandem Configuration is designed to be a specific solution for a specific goal: fast configuration of a PCIe endpoint to meet enumeration requirements. For more information, see the following manuals:

- 7 Series FPGAs Integrated Block for PCI Express LogiCORE IP Product Guide (PG054)

- Virtex-7 FPGA Integrated Block for PCI Express LogiCORE IP Product Guide (PG023)

- UltraScale Devices Gen3 Integrated Block for PCI Express LogiCORE IP Product Guide (PG156)

- UltraScale+ Devices Integrated Block for PCI Express LogiCORE IP Product Guide (PG213)

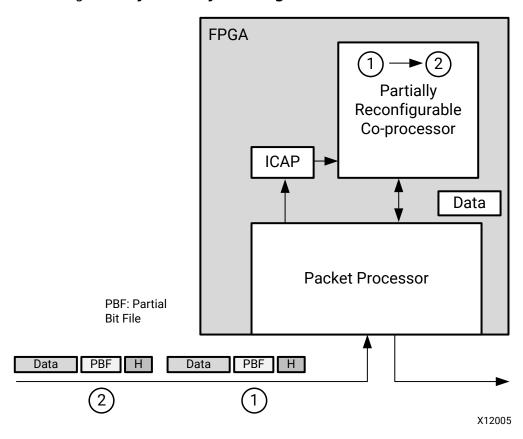

# **Dynamically Reconfigurable Packet Processor**

A packet processor can use Dynamic Function eXchange to change its processing functions quickly, based on the packet types received. In Dynamically Reconfigurable Packet Processor, a packet has a header that contains the partial BIT file, or a special packet contains the partial BIT file. After the partial BIT file is processed, it is used to reconfigure a co-processor in the FPGA. This is an example of the FPGA reconfiguring itself based on the data packet received instead of relying on a predefined library of partial BIT files.

Figure 5: Dynamically Reconfigurable Packet Processor

# **Asymmetric Key Encryption**

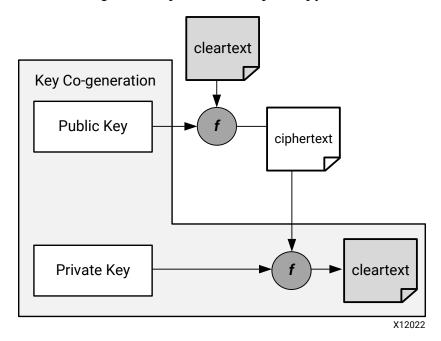

There are some new applications that are not possible without Dynamic Function eXchange. A very secure method for protecting the FPGA configuration file can be architected when Dynamic Function eXchange and asymmetric cryptography are combined. (See Public-key cryptography for asymmetric cryptography details.)

In Asymmetric Key Encryption, the group of functions in the shaded box can be implemented within the physical package of the FPGA. The cleartext information and the private key never leave a well-protected container.

Figure 6: Asymmetric Key Encryption

In a real implementation of this design, the initial BIT file is an unencrypted design that does not contain any proprietary information. The initial design only contains the algorithm to generate the public-private key pair and the interface connections between the host, FPGA and ICAP.

After the initial BIT file is loaded, the FPGA generates the public-private key pair. The public key is sent to the host which uses it to encrypt a partial BIT file. The encrypted partial BIT file is downloaded to the FPGA where it is decrypted and sent to the ICAP to partially reconfigure the FPGA, as shown in Asymmetric Key Encryption.

FPGA Host Generate Key Pair Bit File Library Private **Public** Encrypt Config 1 Algorithm External Decrypt **ICAP** Config 2 Interface Algorithm Public Config 3 X12023-020521

Figure 7: Loading an Encrypted Partial Bit File

The partial BIT file could be the vast majority of the FPGA design with the logic in the static design consuming a very small percentage of the overall FPGA resources.

This scheme has several advantages:

- The public-private key pair can be regenerated at any time. If a new configuration is downloaded from the host it can be encrypted with a different public key. If the FPGA is configured with the same partial BIT file, such as after a power-on reset, a different public key pair is used even though it is the same BIT file.

- The private key is stored in SRAM. If the FPGA ever loses power the private key no longer exists.

- Even if the system is stolen and the FPGA remains powered, it is extremely difficult to find the private key because it is stored in the general purpose FPGA programmable logic. It is not stored in a special register. You could manually locate each register bit that stores the private key in physically remote and unrelated regions.

# **Summary**

In addition to reducing size, weight, power and cost, Dynamic Function eXchange enables new types of FPGA designs that would otherwise be impossible to implement.

# Vivado Software Flow

The Vivado<sup>®</sup> Dynamic Function eXchange (DFX) design flow is similar to a standard design flow, with some notable differences. The implementation software automatically manages the low-level details to meet silicon requirements. You must provide guidance to define the design structure and floorplan. The following steps summarize processing a DFX design:

- 1. Synthesize the static and reconfigurable modules (RM) separately. See Synthesis for more information.

- 2. Create physical constraints (Pblocks) to define the reconfigurable regions. See Create a Floorplan for the Reconfigurable Region for more information.

- 3. Set the HD. RECONFIGURABLE property on each reconfigurable partition (RP). See Define a Module as Reconfigurable for more information.

- 4. Implement a complete design (static and one RM per RP) in context. See Implementation for more information.

- 5. Save a design checkpoint for the full routed design. See Implementation for more information.

- 6. Remove RMs from this design and save a static-only design checkpoint. See Implementation for more information.

- 7. Lock the static placement and routing. See Preserving Implementation Data for more information.

- 8. Add new RMs to the static only design and implement this new configuration, saving a checkpoint for the full routed design.

- 9. Repeat Step 8 until all RMs are implemented.

- 10. Run a verification utility ( $pr_verify$ ) on all configurations. See Verifying Configurations for more information.

- 11. Create bitstreams for each configuration. See Bitstream Generation for more information.

# **Dynamic Function eXchange Commands**

The DFX flows are supported through the non-project batch/Tcl interface (no project based commands), as well as within an RTL-based project flow. Example scripts for the non-project flow are provided in the *Vivado Design Suite Tutorial*: *Dynamic Function eXchange* (UG947), along with step-by-step instructions for setting up the flows. See that Tutorial for more information.

Even with the introduction of the Dynamic Function eXchange terminology, the underlying design flow remains unchanged. Fundamental Tcl commands remain unchanged so that existing projects and scripts will safely migrate forward. Designs and scripts created prior to Vivado 2019.2 require no modification when updating to this release.

The following sections describe a few specialized commands and options needed for the DFX flows. Examples of how to use these commands to run a DFX flow are given. For more information on individual commands, see the *Vivado Design Suite Tcl Command Reference Guide* (UG835).

## **Synthesis**

Synthesizing a partially reconfigurable design does not require any special commands, but does require bottom-up synthesis. There are currently no unsupported commands for synthesis, optimization, or implementation.

These synthesis tools are supported:

- XST (supported for 7 series only)

- Synplify

- Vivado Synthesis

**IMPORTANT!** Bottom-up synthesis refers to a synthesis flow in which each module has its own synthesis project. This generally involves turning off automatic I/O buffer insertion for the lower level modules.

This document only covers the Vivado synthesis flow.

## Synthesizing the Top Level

You must have a top-level netlist with a black box for each reconfigurable partition (RP). This requires the top-level synthesis to have module or entity declarations for the partitioned instances, but no logic; the module is empty.

The top-level synthesis infers or instantiates I/O buffers on all top level ports. For more information on controlling buffer insertion, see this link in the *Vivado Design Suite User Guide: Synthesis* (UG901).

```

synth_design -flatten_hierarchy rebuilt -top <top_module_name> -part <part>

```

## Synthesizing Reconfigurable Modules

Because each RM must be instantiated in the same black box in the static design, the different versions must have identical interfaces. The name of the block must be the same in each instance, and all the properties of the interfaces (names, widths, direction) must also be identical. Each configuration of the design is assembled like a flat design.

To synthesize a RM, turn off all buffer insertions. You can do so in Vivado Synthesis using the synth\_design command in conjunction with the -mode out\_of\_context switch:

```

synth_design -mode out_of_context -flatten_hierarchy rebuilt -top

<reconfig_module_name> -part <part>

```

### Table 1: synth\_design Options

| Command Option             | Description                                                                                                                                  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| -mode out_of_context       | Prevents I/O insertion for synthesis and downstream tools. The out_of_context mode is saved in the checkpoint if write_checkpoint is issued. |

| -flatten_hierarchy rebuilt | There are several values allowed for <code>-flatten_hierarchy</code> , but <code>rebuilt</code> is the recommended setting for DFX flows.    |

| -top                       | This is the module/entity name of the module being synthesized.                                                                              |

| -part                      | This is the Xilinx® part being targeted (for example, xc7k325tffg900-3)                                                                      |

The  $synth_{design}$  command synthesizes the design and stores the results in memory. In order to write the results out to a file, use:

```

write_checkpoint <file_name>.dcp

```

It is recommended to close the design in memory after synthesis, and run implementation separately from synthesis.

## **Reading Design Modules**

If there is currently no design in memory, you must load a design. This can be done in a variety of ways, for either the static design or for RM. After the configurations are implemented, checkpoints are exclusively used to read in placed and routed module databases.

### Method 1: Add and Link Files

This is the recommended method to load and link all design sources in the most explicit and thorough manner. The following steps pull in all necessary design sources and define the RP boundaries.

1. Create a new project in memory. While this allows you to select a target device, the project is not saved.

```

create_project -part <part> -in_memory

```

2. Add all the design sources. This can include multiple checkpoints for static or reconfigurable logic, including lower-level RM sources.

```

add_files <top>.dcp

add_files <rp1_rmA_top>.dcp

add_files <rp1_rmA_lower>.dcp

add_files <rp2_rmA_top>.dcp

```

3. Use the SCOPED\_TO\_CELLS property to define relationships between levels of hierarchy.

```

expanse="page">set_property SCOPED_TO_CELLS {<RP1_module_instance>}

[get_files <rp1_rmA_top>.dcp]

expanse="page">set_property SCOPED_TO_CELLS

{<RP1_lower_module_instance>} [get_files <rp1_rmA_lower>.dcp]

expanse="page">set_property SCOPED_TO_CELLS {<RP2_module_instance>}

[get_files <rp2_rmA_top>.dcp]

```

4. Link the design together, defining all RPs.

```

expanse="page">link_design -top <top> -part <part> -reconfig_partitions

{<RP1_module_instance> <RP2_module_instance>}

```

### Table 2: link\_design Options

| Command Option                     | Description                                                                                                                                                                                          |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -part                              | This is the Xilinx part being targeted (for example, xc7k325tffg900-3)                                                                                                                               |

| -top                               | This is the module/entity name of the module being implemented. This switch can be omitted if set_property top <top_module_name> [current_fileset] is issued prior to link_design.</top_module_name> |

| -reconfig_partitions <args></args> | Specify a list of RPs to load while opening the design. The specified RPs are then marked with the HD.RECONFIGURABLE property for proper handling in the design.                                     |

| -pr_config <arg></arg>             | For the project-based design flow only. This option specifies the PR Configuration to apply while opening the design.                                                                                |

## Method 2: Read Netlist Design

This approach should be used when modules have been synthesized by tools other than Vivado synthesis.

```

read_edif <top>.edf/edn/ngc

read_edif <rp1_a>.edf/edn/ngc

read_edif <rp2_a>.edf/edn/ngc

link_design -top <top_module_name> -part <part>

```

## Method 3: Open/Read Checkpoint

If the static (top-level) design has synthesis or implementation results stored as a checkpoint, it can be loaded using the <code>open\_checkpoint</code> command. This command reads in the static design checkpoint and opens it in active memory:

```

open_checkpoint <file>

```

If the checkpoint is for the complete netlist of a RM (that is, not for static), the instance name can be specified using read\_checkpoint -cell. If the checkpoint is a post-implementation checkpoint, the additional -strict option must be used. This option can also be used with a post-synthesis checkpoint to ensure exact port matching. To read in a checkpoint in a RM, the top-level design must be open and have a black box for the specified cell. Then the following command can be specified:

```

read_checkpoint -cell <cellname> <file> [-strict]

```

Table 3: read\_checkpoint Switches

| Switch Name   | Description                                                                                                                                                              |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -cell         | Specifies the full hierarchical name of the RM.                                                                                                                          |

| -strict       | Requires exact ports match for replacing a cell, and checks that part, package, and speed grade values are identical. Should be used when restoring implementation data. |

| <file></file> | Specifies the full or relative path to the checkpoint (DCP) to be read in.                                                                                               |

**CAUTION!** Do not use this method if the synthesized checkpoint has underlying modules that are not included. The  $read\_checkpoint\_-cell$  approach does not support nesting. Use the  $link\_design$  approach instead in Method 1: Add and Link Files.

**CAUTION!** Any Tcl variable pointing to design objects becomes invalid after subsequent  $read\_checkpoint\_-cell$  commands. The content of those variables needs to be rebuilt prior to a second call to  $read\_checkpoint\_-cell$ . Failure to do so could result to unwanted behavior (or even crashes) due to referencing objects that no longer exist.

## Method 4: Open Checkpoint/Update Design

This is useful when the synthesis results are in the form of a netlist (EDF or EDN), but static has already been implemented. The following example shows the commands for the second configuration in which this is true.

```

open_checkpoint <top>.dcp

lock_design -level routing

update_design -cells <rp1> -from_file <rp1_b>.{edf/edn}

update_design -cells <rp2> -from_file <rp2_b>.{edf/edn}

```

# Adding Reconfigurable Modules with Sub-Module Netlists

If a RM has sub-module netlists, it can be difficult for the Vivado tools to process the sub-module netlists. This is because in the DFX flow the RM netlists are added to a design that is already open in memory. This means the update\_design -cells command must be used, which requires the cell name for every EDIF file, which can be troublesome to get.

There are two ways to make loading RM sub-module netlists easier in the Vivado Design Suite.

### Method 1: Create a Single RM Checkpoint (DCP)

Create an RM checkpoint (DCP) that includes all netlists. Use add\_files to add all of the EDIF (or NGC) files, and use link\_design to resolve the EDIF files to their respective cells. Here is an example of the commands used in this process:

```

add_files [list rm.edf ip_1.edf ip_n.edf]

# Run if RM XDC exists

add_files rm.xdc

link_design -top <rm_module> -part <part>

write_checkpoint rm_v#.dcp

close_project

```

**IMPORTANT!** Using this methodology to combine/convert a netlist into a DCP is the recommended way to handle an RM that has one or more NGC source files as well.

Then this newly-created RM checkpoint can be used in the DFX flow. In the commands below, the single read\_checkpoint -cell command replaces what could be many update\_design -cell commands.

```

add_files static.dcp

link_design -top <top> part <part>

lock_design -level routing

read_checkpoint -cell <rm_inst> rm_v#.dcp

```

# Method 2: Place the Sub-Module Netlists in the Same Directory as the RM's Top-Level Netlist

When the top-level RM netlist is read into the DFX design using update\_design -cell, make sure that all sub-module netlists are in the same directory as the RM top-level netlist. In this case, the lower-level netlists do not need to be specified, but they are picked up automatically by the update\_design -cells command. This is less explicit than Method 1, but requires fewer steps. In this case the commands to load the RM netlist would look like the following:

```

add_files static.dcp

link_design -top <top> part <part>

lock_design -level routing

update_design -cells <rm_inst> -from_file rm_v#.edf

```

In the last (update\_design) command above, the lower-level netlists are picked up automatically if they are in the same directory as rm\_v#.edf.

## **Reading Design Constraints**

New constraints can be applied for each configuration at various points in the flow. If an RM is read in as a DCP, then any constraints stored in the DCP are automatically applied. Additionally, the read\_xdc command can be used to apply constraints scoped to the top-level, or to the specific cell (using -cell switch). If constraint are expected to directly or indirectly affect the RM, then the RM must be resolved (not a black box) prior to reading in the new constraints. Otherwise, the constraints may be dropped or not correctly propagated in the constraint system. Because Static is only placed and routed in the initial configuration, all constraints for subsequent configurations (where Static is locked) should be focused strictly on the RP regions being implemented.

## **Implementation**

Because the DFX flow allows for various configurations in hardware, multiple implementation runs are required. Each implementation of a DFX design is referred to as a *configuration*. Each module of the design (static or RM) can be implemented or imported (if previously implemented). Implementation results for the static design must be consistent for each configuration, so that the design is implemented in one configuration, and then imported in subsequent configurations. Additional configurations can be constructed by importing static, and implementing or importing each RM.

There are no restrictions to the support of implementation commands or options for DFX, but certain optimizations and sub-routines are not done if they oppose the fundamental requirements of partial reconfiguration. The following list of commands can be run after the logical design is loaded (using link\_design or open\_checkpoint):

```

# Run if all constraints are not already loaded

read_xdc

# Optional command

opt_design

place_design

# Optional command

phys_opt_design

route_design

```

## **Preserving Implementation Data**

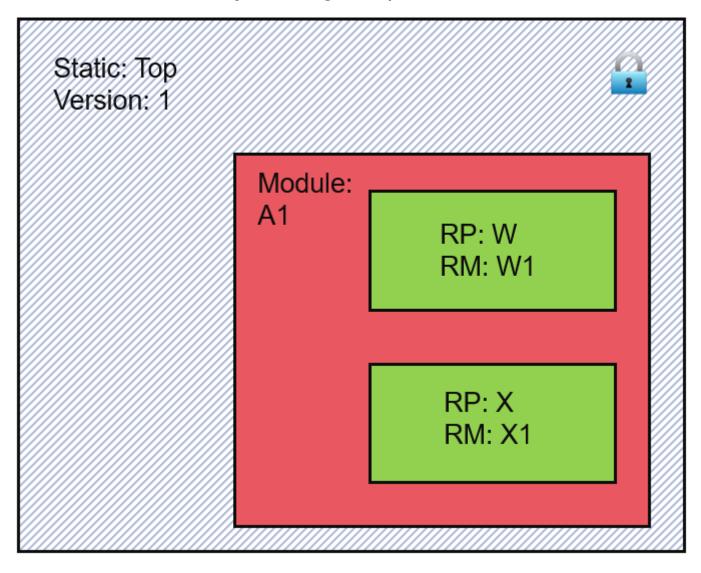

In the DFX flow, it is a requirement to lock down the placement and routing results of the static logic from the first configuration for all subsequent configurations. The static implementation of the first configuration must be saved as a checkpoint. When the checkpoint is read for subsequent configurations, the placement and routing must be locked, to ensure that the static design remains completely identical from configuration to configuration. To lock the placement and routing of an imported checkpoint (static or reconfigurable), the <code>lock\_design</code> command is used.

```

lock_design -level [logical|placement|routing] [cell_name]

```

When locking down the static logic with the above command, the optional [cell\_name] can be omitted.

```

lock_design -level routing

```

To lock the results of an imported RM, the full hierarchical name should be specified within the post-implementation checkpoint:

```

lock_design -level routing u0_RM_instance

```

For Dynamic Function eXchange, the only supported preservation level is routing. Other preservation levels are available for this command, but they must only be used for other Hierarchical Design flows.

# Dynamic Function eXchange Constraints and Properties

There are properties and constraints unique to the Dynamic Function eXchange flow. These initiate DFX-specific implementation processing and apply specific characteristics in the partial bitstreams. The four areas for constraints and properties for DFX are:

**Table 4: Constraints and Properties**

| Constraints and Properties                         | Necessity                        |

|----------------------------------------------------|----------------------------------|

| Defining a module as reconfigurable                | Required                         |

| Creating a floorplan for the reconfigurable region | Required                         |

| Applying reset after reconfiguration               | Optional, but highly recommended |

| Turn on visualization scripts                      | Optional                         |

## **Define a Module as Reconfigurable**

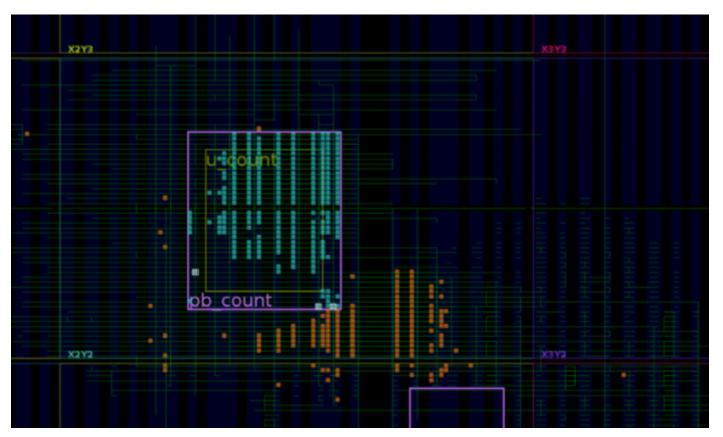

In order to implement a DFX design, it is required to specify each RM as such. To do this you must set a property on the top level of each hierarchical cell that is going to be reconfigurable. For example, take a design where one RP named <code>inst\_count</code> exists, and it has two RMs, <code>count\_up</code> and <code>count\_down</code>. The following command must be issued prior to implementation of the first configuration.

```

set_property HD.RECONFIGURABLE TRUE [get_cells inst_count]

```

This initiates the Dynamic Function eXchange features in the software that are required to successfully implement a DFX design. The  ${\tt HD}$  .  ${\tt RECONFIGURABLE}$  property implies a number of underlying constraints and tasks:

- Sets DONT\_TOUCH on the specified cell and its interface nets. This prevents optimization across the boundary of the module.

- Sets EXCLUDE\_PLACEMENT on the cell's Pblock. This prevents static logic from being placed in the reconfigurable region.

- Sets CONTAIN\_ROUTING on the cell's Pblock. This keeps all the routing for the RM within the bounding box.

- Enables special code for DRCs, clock routing, etc.

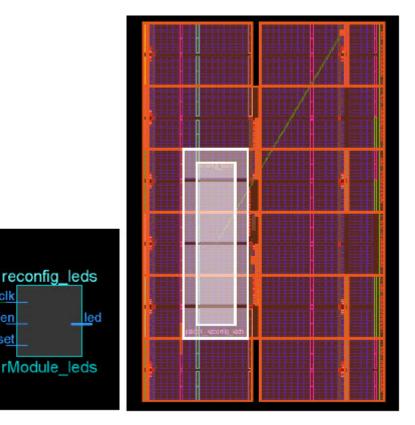

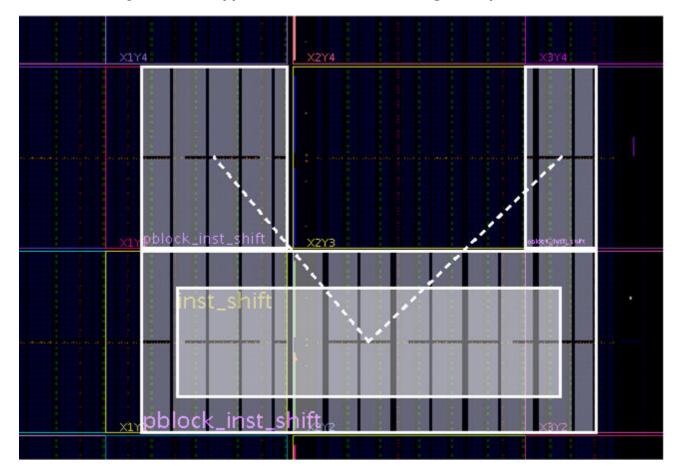

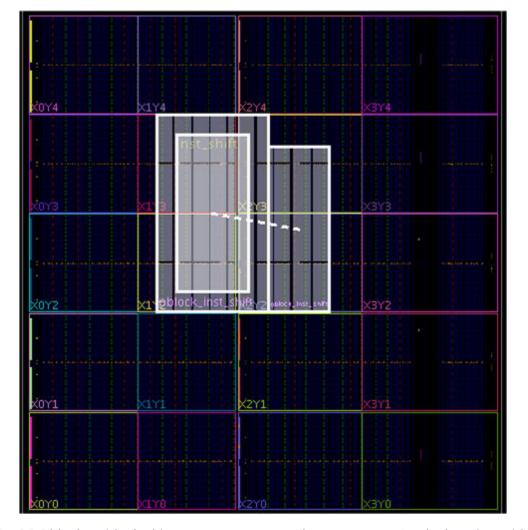

## Create a Floorplan for the Reconfigurable Region

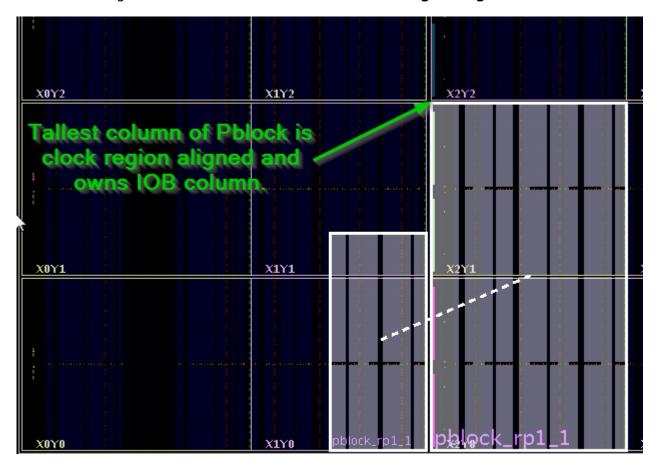

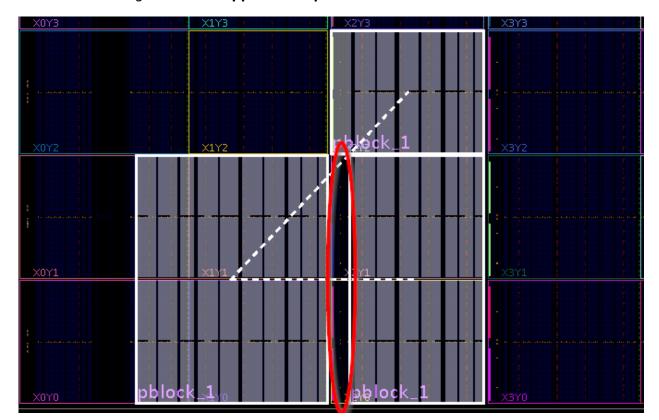

Each RP is required to have a Pblock to define the physical resources available for the RM. Because this Pblock is set on a RP, these restrictions and requirements apply:

- The Pblock must contain only valid reconfigurable element types. The region may overlap other site types, but these other sites must not be included in the resize\_pblock commands.

- Multiple Pblock rectangles for each component type can be used to create the RP region, but

for the greatest routability, they should be contiguous. Gaps to account for non-reconfigurable

resources are permitted, but in general, the simpler the overall shape, the easier the design is

to place and route.

- If using the RESET\_AFTER\_RECONFIG property for 7 series devices, the Pblock height must align to clock region boundaries. See Apply Reset After Reconfiguration for more details.

- The width and composition of the Pblock must not split interconnect columns for 7 series devices. See Creating Pblocks for 7 Series Devices for more details.

- The resource usage of the largest RM needs to be taken into consideration when defining the Pblock in certain parts. If the largest RM exceeds the documented maximum resource counts of the target device, write\_bitstream generates an error.

- The Pblock must not overlap any other Pblock in the design.

- Standard Pblocks for floorplanning logic within a RP are supported, as are nested Pblocks.

- The IS\_SOFT property of a reconfigurable Pblock is automatically set to FALSE, as the Pblock size and boundaries must remain fixed. Setting this property to TRUE results in an error.

- Any nested Pblocks under the reconfigurable Pblock inherit the IS\_SOFT = FALSE property; this cannot be changed.

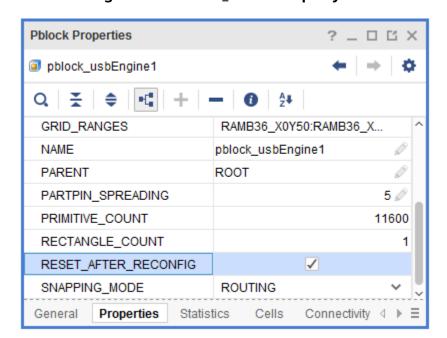

**Table 5: Pblock Commands and Properties**

| Command/Property Name | Description                                                                                                                                                                                                                                                                                                      |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| create_pblock         | Command used to create the initial Pblock for each RP instance.                                                                                                                                                                                                                                                  |

| add_cells_to_pblock   | Command used to specify the instances that belong to the Pblock. This is typically a level of hierarchy as defined by the bottom-up synthesis processing.                                                                                                                                                        |

| resize_pblock         | Command used to define the site types (such as SLICE or RAMB36) and site locations that are owned by the Pblock.                                                                                                                                                                                                 |

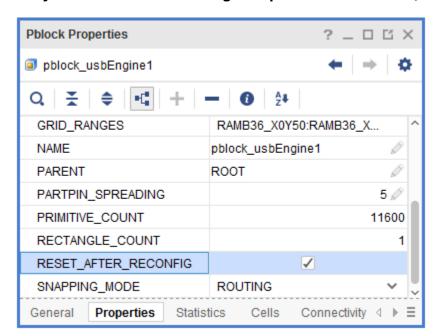

| RESET_AFTER_RECONFIG  | Pblock property used to control the use of the dedicated GSR event on the reconfigurable region. Use of this property is highly recommended and, for 7 series and Zynq devices, requires clock region alignment in the vertical direction.                                                                       |

| CONTAIN_ROUTING       | Pblock property used to control the routing to prevent usage of routing resources not owned by the Pblock. This property is mandatory for PR and is set to True automatically for RPs. Static routing is still allowed to use resources inside of the Pblock.                                                    |

| EXCLUDE_PLACEMENT     | Pblock Property used to prevent the placement of any logic, not belonging to the Pblock, inside the defined Pblock RANGE. This property is mandatory for PR and set to true automatically for RPs. Static logic can be placed inside of the RP with a specific LOC property if RESET_AFTER_RECONFIG is not used. |

*Table 5:* **Pblock Commands and Properties** (cont'd)

| Command/Property Name | Description                                                                                                                                                                                                            |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PARTPIN_SPREADING     | Used to control the maximum number of PartPins per INT tile. Default is 5.                                                                                                                                             |

|                       | Setting a lower value (i.e. 3) increases the spreading between partition pin placements. This typically eases routing congestion in areas with dense PartPin placement, but can negatively affect RP interface timing. |

The following is an example of a set of constraints for a RP:

```

#define a new pblock

create_pblock pblock_count

#add a hierarchical module to the pblock

add_cells_to_pblock [get_pblocks pblock_count] [get_cells [list inst_count]]

#define the size and components within the pblock

resize_pblock [get_pblocks pblock_count] -add {SLICE_X136Y50:SLICE_X145Y99}

resize_pblock [get_pblocks pblock_count] -add {RAMB18_X6Y20:RAMB18_X6Y39}

resize_pblock [get_pblocks pblock_count] -add {RAMB36_X6Y10:RAMB36_X6Y19}

```

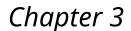

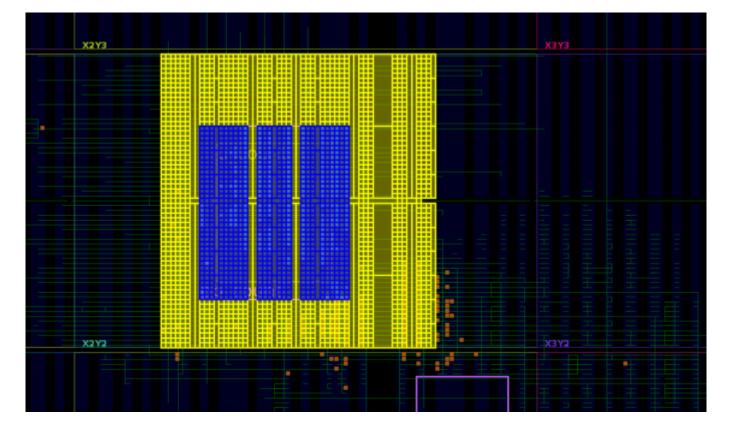

## Floorplan in the Vivado IDE

The Vivado IDE can be used for planning and visualization tasks. The best example of this is using the Device view to create and modify Pblock constraints for floorplanning.

1. Open the synthesized static design and the largest of each RM. Here are the commands, using the tutorial design (found in the Vivado Design Suite Tutorial: Dynamic Function eXchange (UG947)) as an example:

```

open_checkpoint synth/Static/top_synth.dcp

set_property HD.RECONFIGURABLE true [get_cells inst_count]

read_checkpoint -cell [get_cells inst_count] synth/count_up/

count_synth.dcp

set_property HD.RECONFIGURABLE true [get_cells inst_shift]

read_checkpoint -cell [get_cells inst_shift] synth/shift_right/

shift_synth.dcp

```

At this point, a full configuration has been loaded into memory, and the RPs have been defined.

- To create Pblock constraints for the RPs, right-click on an instance in the Netlist window (in this case, inst\_count or inst\_shift) and select **Draw Pblock**. Create a rectangle in the Device view to select resources for this RP.

- 3. With this Pblock selected, note that the Pblock Properties pane shows the number of available and required resources. The number required is based on the currently loaded RM, so keep in mind that other modules may have different requirements. If additional rectangles are required to build the appropriate shape (an "L", for example), right-click the Pblock in the Device view and select **Add Pblock Rectangle**.

4. Design rule checks (DRCs) can be issued to validate the floorplan and other design considerations for the in-memory configuration. To run, select Reports → Report DRC and ensure the Partial Reconfiguration checks are present (see Floorplan in the Vivado IDE). Note that if HD. RECONFIGURABLE has not been set on a Pblock, only a single DRC is available, instead of the full complement shown below.

This set of DRCs can be run from the Tcl Console or within a script, by using the  $report_drc$  command. To limit the checks to the ones shown here for Partial Reconfiguration, use this syntax:

```

report_drc -checks [get_drc_checks HDPR*]

```

To extend the DRCs to those checked during specific phases of design processing the - ruledeck option can be used. For example, the following command can be issued on a placed and routed design:

```

report_drc -ruledeck bitstream_checks

```

To save these floorplanning constraints, enter the following command in the Tcl Console:

```

write_xdc top_fplan.xdc

```

The Pblock constraints stored in this constraints file can be used directly or can be copied to another top-level design constraints file. This XDC file contains all the constraints in the current design in memory not just the constraints recently added.

**CAUTION!** Do NOT save the overall design from the Vivado IDE using  $File \rightarrow Checkpoint \rightarrow Save$  or the equivalent button. If you save the currently loaded design in this way, you will overwrite your synthesized static design checkpoint with a new version that includes RMs and additional constraints.

## **Using Visualization Scripts**

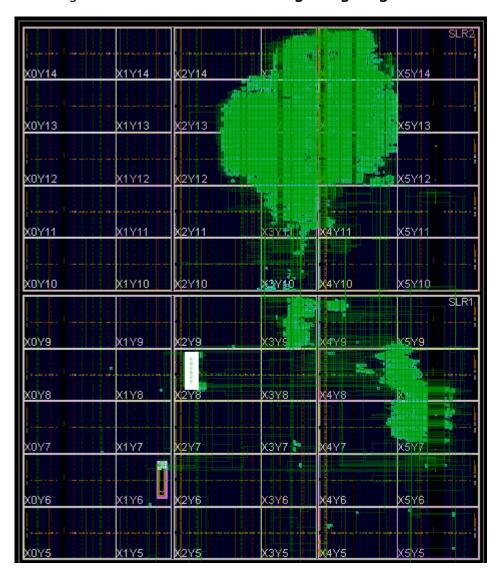

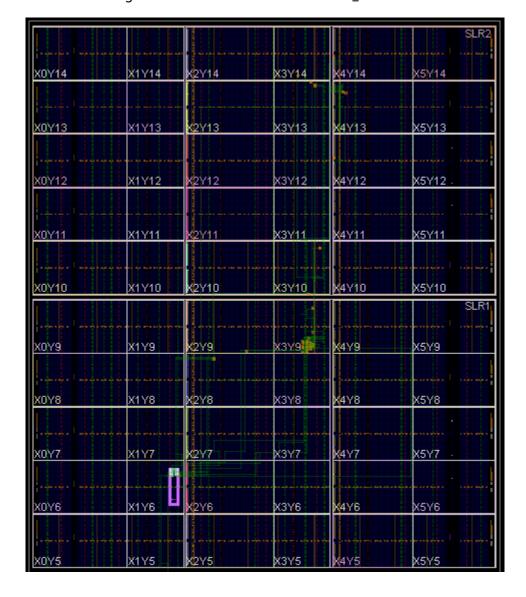

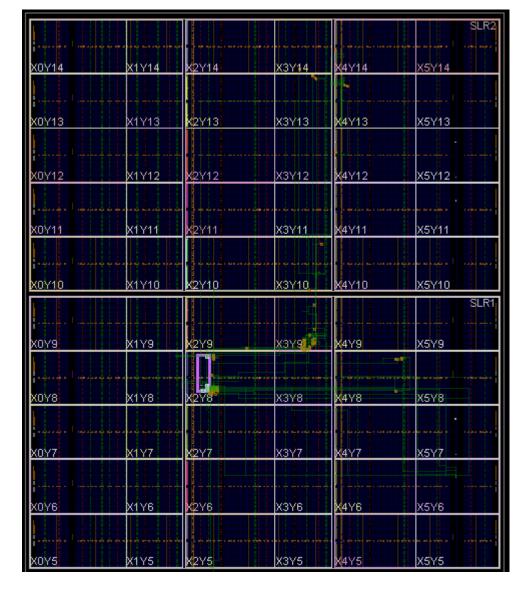

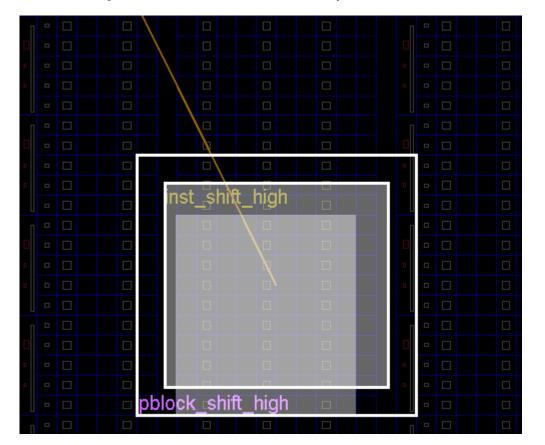

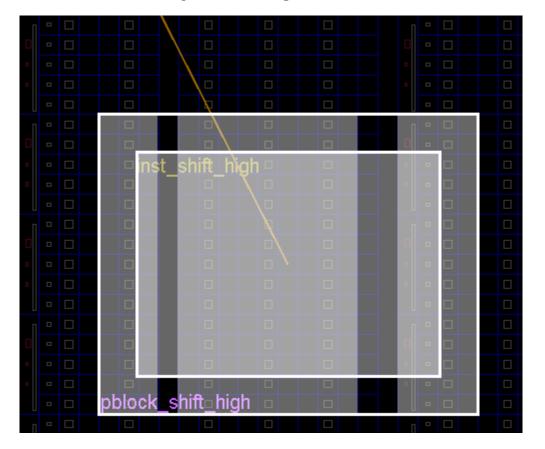

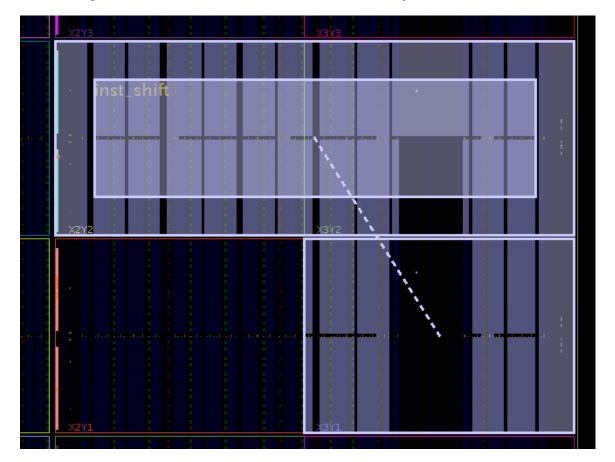

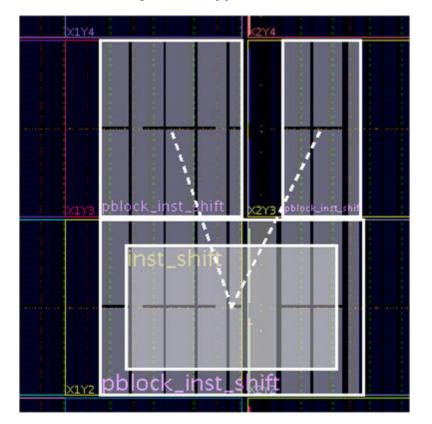

For each RP, scripts are automatically created to confirm the site ownership for each part of a DFX design. The visualization scripts generated can vary based on architecture and need.

Scripts are automatically created for all RP Pblock in an hd\_visual directory, which is created in the directory where the run script is launched. To use these scripts, read a routed design checkpoint into the Vivado IDE, then source one of the scripts. These design-specific scripts highlight configuration tiles as you have defined them, show configuration frames used to create the partial bit file, or show sites excluded by the DFX floorplan. Additional scripts are created for other flows, such as Module Analysis or Tandem Configuration, and are not used for DFX.

For 7 series devices, the main script is named  $<rp_pblock>_AllTiles.tcl$  and shows all the sites owned by the RP, for both placement and routing of any implemented RMs. Other scripts are created for very specific goals and are not needed in most cases.

For all devices, three additional scripts might be created per design when necessary: blockedBelsRouteThrus.tcl, blockedPins.tcl, and blockedSitesInputs.tcl. When designs encounter higher levels of congestion, these scripts are created to show restricted sites. This information can be used to adjust the size and shape of the RP pblock, and can also be shared with support for troubleshooting purposes.

## **Timing Constraints**

Timing constraints for a partially reconfigurable design are similar to timing constraints for a traditional flat design. The primary clocks and I/Os must be constrained with the corresponding constraints. For more information on these constraints, see this link (for defining clocks) and this link (for constraining I/O delays) in the Vivado Design Suite User Guide: Using Constraints (UG903).

After the correct constraints are applied to the design, run static timing analysis to verify the performance of the design. This verification must be run for each RM in the overall static design. For more information on how to analyze the design, see the *Vivado Design Suite User Guide:* Design Analysis and Closure Techniques (UG906).

The Vivado Design Suite includes the capability to run cell level timing reports. Use the <code>-cell</code> option for <code>report\_timing</code> or <code>report\_timing\_summary</code> to focus timing analysis on a specific RM. This is especially useful on configurations where the static design has been imported and locked from a prior configuration.

There is a **Partition** column added to the timing reports generated by report\_timing and report\_timing\_summary. It helps identify if failing paths are within static, an RM, or crosses an RP boundary. Both of these commands have a new -no\_pr\_attribute switch to turn this new functionality off. This can be useful if, for example, scripts are being used to parse the timing reports and are negatively affected by this new column.

### **Partition Pins**

Interface points called partition pins are automatically created within the Pblock ranges defined for the RP. These virtual I/O are established within interconnect tiles as the anchor points that remain consistent from one module to the next. No physical resources such as LUTs or flip-flops are required to establish these anchor points, and no additional delay is incurred at these points.

The placer chooses locations based on source and loads and timing requirements, but you can specify these locations as well. The following constraints can be applied to influence partition pin placement.

**Table 6: Context Properties**

| Command/Property Name | Description                                                                                                                                                                                                                                                                                                                                     |