# Zynq UltraScale+ MPSoC: Embedded Design Tutorial

## A Hands-On Guide to Effective Embedded System Design

UG1209 (v2019.2) October 30, 2019

## **Revision History**

The following table shows the revision history for this document.

| Section                                                  | Revision Summary                                                   |  |  |  |

|----------------------------------------------------------|--------------------------------------------------------------------|--|--|--|

| 10/30/2019 Version 2019.2                                |                                                                    |  |  |  |

| Updated for Vitis <sup>™</sup> unified software platform | Migrated the flow to Vitis <sup>™</sup> unified software platform. |  |  |  |

| General updates                                          | Validated with Vitis IDE and PetaLinux 2019.2.                     |  |  |  |

| 07/03/2019 Version 2019.1                                |                                                                    |  |  |  |

| General updates                                          | Validated with Vivado® Design Suite and PetaLinux 2019.1.          |  |  |  |

## **Table of Contents**

| Revision History                                                                |

|---------------------------------------------------------------------------------|

| Chapter 1: Introduction                                                         |

| About This Guide                                                                |

| How Zynq UltraScale+ Devices Offer a Single Chip Solution                       |

| How the Xilinx Design Tools Expedite the Design Process                         |

| What You Need to Set Up Before Starting    10                                   |

| Chapter 2: Zynq UltraScale+ MPSoC Processing System Configuration               |

| Zynq UltraScale+ System Configuration 13                                        |

| Example Project: Creating a New Embedded Project with Zynq UltraScale+ MPSoC 14 |

| Chapter 3: Build Software for PS Subsystems                                     |

| Processing Units in Zynq UltraScale+ 29                                         |

| Example Project: Running the "Hello World" Application from Arm Cortex-A53      |

| Example Project: Running the "Hello World" Application from Arm Cortex-R5       |

| Additional Information                                                          |

| Example Project: Create a Bare-Metal Application Project in the Vitis IDE       |

| Reviewing Software Projects in the Platform 42                                  |

| Example Project: Create Linux Images using PetaLinux                            |

| Chapter 4: Debugging with the Vitis Debugger                                    |

#### apter 4: Debugging '66

| Xilinx System Debugger                      | 53 |

|---------------------------------------------|----|

| Debugging Software Using the Vitis Debugger | 55 |

| Debugging Using XSCT                        | 58 |

### **Chapter 5: Boot and Configuration**

| System Software                             | 69 |

|---------------------------------------------|----|

| Linux on APU and Bare-Metal on RPU          | 71 |

| Boot Sequence for SD-Boot                   | 71 |

| Boot Sequence for QSPI Boot Mode            | 81 |

| Boot Sequence for QSPI-Boot Mode Using JTAG | 94 |

| Boot Sequence for USB Boot Mode             | 97 |

| Secure Boot Sequence                                                               |

|------------------------------------------------------------------------------------|

| Chapter 6: System Design Examples                                                  |

| Design Example 1: Using GPIOs, Timers, and Interrupts                              |

| Design Example 2: Example Setup for Graphics and Display Port Based Sub-System 158 |

| Appendix A: Debugging Problems with Secure Boot                                    |

| Determine if PUF Registration is Running 165                                       |

| Read the Boot Image    165                                                         |

| Appendix B: Additional Resources and Legal Notices                                 |

| Xilinx Resources                                                                   |

| Solution Centers                                                                   |

| Documentation Navigator and Design Hubs 166                                        |

| Design Files for This Tutorial                                                     |

| Xilinx Resources                                                                   |

| Training Resources                                                                 |

| Please Read: Important Legal Notices 169                                           |

## Introduction

## **About This Guide**

This document provides an introduction to using the Xilinx® Vivado® Design Suite flow for using the Zynq® UltraScale+™ MPSoC device. The examples are targeted for the Xilinx ZCU102 Rev 1.0 and Rev 1.1 evaluation boards. The tool used is the Vitis™ unified software platform.

The examples in this document were created using the Xilinx tools running on Windows 10, 64-bit operating system, and PetaLinux on Linux 64-bit operating system. Other versions of the tools running on other Window installs might provide varied results. These examples focus on introducing you to the following aspects of embedded design.

**Note:** The sequence mentioned in the tutorial steps for booting Linux on the hardware is specific to the PetaLinux tools released for 2019.2, which must be installed on the Linux host machine for exercising the Linux portions of this document.

- Chapter 2, Zynq UltraScale+ MPSoC Processing System Configuration describes the creation of a system with the Zynq UltraScale+ MPSoC Processing System (PS) and the creation of a hardware platform for Zynq Ultrascale+ MPSoC. This chapter is an introduction to the hardware and software tools using a simple design as the example.

- Chapter 3, Build Software for PS Subsystems describes the steps to configure and build software for processing blocks in processing system, including application processing unit (APU), real-time processing unit (RPU). Creation of bare metal applications targeting on application processing unit (APU) and RPU is also included. Review of boot components in hardware platform.

- Chapter 4, Debugging with the Vitis Debugger provides an introduction to debugging software using the debug features of the Vitis IDE. This chapter uses the previous design and runs the software bare metal (without an OS) to show how to debug. This chapter also lists Debug configurations for Zynq UltraScale+ MPSoC.

- Chapter 5, Boot and Configuration shows integration of components to configure and create Boot images for a Zynq UltraScale+ system. The purpose of this chapter is to understand how to integrate and load Boot loaders.

- Chapter 6, System Design Examples highlights how you can use the software blocks you configured in Chapter 3 to create a Zynq UltraScale+ system.

### **Document Audience and Scope**

The purpose of this guide is to familiarize software application developers, system software designers, and system hardware designers by providing the following:

- Tutorials for creating a Zynq UltraScale+ MPSoc System

- Tutorials on building software for the PS subsystem

- Tutorials on debugging using the Vitis IDE

- System design examples

### **Example Project**

The best way to learn a tool is to use it. This guide provides opportunities for you to work with the tools under discussion. Specifications for sample projects are given in the example sections, along with an explanation of what is happening behind the scenes. Each chapter and examples are meant to showcase different aspects of embedded design. The example takes you through the entire flow to complete the learning and then moves on to another topic.

### Additional Documentation

Additional documentation is listed in Appendix B, Additional Resources and Legal Notices.

# How Zynq UltraScale+ Devices Offer a Single Chip Solution

Zynq UltraScale+ MPSoC, the next generation Zynq device, is designed with the idea of using the right engine for the right task. The Zynq UltraScale+ comes with a versatile Processing System (PS) integrated with a highly flexible and high-performance Programmable Logic (PL) section, all on a single System on Chip (SoC). The Zynq UltraScale+ MPSoC PS block includes engines such as the following:

- Quad-core Arm Cortex-A53 based Application Processing Unit (APU)

- Dual-core Arm Cortex-R5 based Real Time Processing Unit (RPU)

- Arm Mali-400 MP2 based Graphics Processing Unit (GPU)

- Dedicated Platform Management Unit (PMU) and Configuration Security Unit (CSU)

- List of High Speed peripherals, including Display port and SATA

The Programmable Logic Section, in addition to the programmable logic cells, also comes integrated with few high performance peripherals, including the following:

- Integrated Block for PCI Express

- Integrated Block for Interlaken

- Integrated Block for 100G Ethernet

- System Monitor

- Video Codec Unit

The PS and the PL in Zynq UltraScale+ can be tightly or loosely coupled with a variety of high performance and high bandwidth PS-PL interfaces.

To simplify the design process for such sophisticated devices, Xilinx offers the Vivado Design Suite, Vitis IDE, and PetaLinux Tools for Linux. This set of tools provides you with everything you need to simplify embedded system design for a device that merges an SoC with an FPGA. This combination of tools enables hardware and software application design, code execution and debug, and transfer of the design onto actual boards for verification and validation.

### Vitis Integrated Design Environment (IDE)

The Vitis<sup>™</sup> unified software platform is an integrated development environment (IDE) for the development of embedded software applications targeted towards Xilinx<sup>®</sup> embedded processors. The Vitis software platform works with hardware designs created with Vivado<sup>®</sup> Design Suite. The Vitis software platform is based on the Eclipse open source standard and the features for software developers include:

- Feature-rich C/C++ code editor and compilation environment.

- Project management.

- Application build configuration and automatic Makefile generation.

- Error navigation.

- Integrated environment for seamless debugging and profiling of embedded targets.

- Source code version control.

- System-level performance analysis.

- Focused special tools to configure FPGAs.

- Bootable image creation.

- Flash programming.

- Script-based command-line tool.

## For more information about the Eclipse development environment, refer to http://www.eclipse.org.

Other components include:

- Drivers and libraries for embedded software development

- Linaro GCC compiler for C/C++ software development targeting the Arm Cortex-A53 and Arm Cortex-R5F MPCore processors in the Zynq UltraScale+ Processing System.

### The Vivado Design Suite

The Vivado Design Suite offers a broad range of development system tools for FPGA implementation. It can be installed as a standalone tool when software programming is not required. It is also a part of the Vitis IDE installation. Various Vivado Design Suite editions can be used for embedded system development. In this guide the System Edition installed with the Vitis IDE is used. The Vivado Design Suite editions are shown in the following figure.

### Vivado Design Suite - HLx Editions

| Vivado Design Suite -<br>HLx Edition Features | Vivado HL<br>Design<br>Edition | Vivado HL<br>System<br>Edition | Vivado<br>Lab<br>Edition | Vivado HL WebPACK<br>Edition (Device Limited) | Free 30-day<br>Evaluation |

|-----------------------------------------------|--------------------------------|--------------------------------|--------------------------|-----------------------------------------------|---------------------------|

| Accelerating Implementat                      | ion                            |                                |                          |                                               |                           |

| Synthesis and Place and Route                 | •                              | •                              |                          | •                                             | •                         |

| Partial Reconfiguration*                      | •                              | •                              |                          | •                                             | •                         |

| Accelerating Verification                     |                                |                                |                          |                                               |                           |

| Vivado Simulator                              | •                              | •                              |                          | •                                             | •                         |

| Vivado Device<br>Programmer                   | •                              | •                              | •                        | •                                             | •                         |

| Vivado Logic Analyzer                         | •                              | •                              | •                        | •                                             | •                         |

| Vivado Serial I/O Analyzer                    | •                              | •                              | •                        | •                                             | •                         |

| Debug IP (ILA/VIO/IBERT)                      | •                              | •                              |                          | •                                             | •                         |

| Accelerating High Level De                    | esign                          |                                |                          |                                               |                           |

| Vivado High-Level<br>Synthesis                | •                              | •                              |                          | •                                             | •                         |

| Vivado IP Integrator                          | •                              | •                              |                          | •                                             | •                         |

| System Generator for<br>DSP                   |                                | •                              |                          |                                               | •                         |

\* Can be purchased as an option.

Figure 1-1: Vivado Design Suite Editions

### **Other Vivado Components**

Other Vivado components include:

- Embedded/Soft IP for the Xilinx embedded processors

- Documentation

- Sample projects

### **PetaLinux Tools**

The PetaLinux tools set is an Embedded Linux System Development Kit. It offers a multi-faceted Linux tool flow, which enables complete configuration, build, and deploy environment for Linux OS for the Xilinx Zynq devices, including Zynq UltraScale+.

For more information, see the *PetaLinux Tools Documentation: Reference Guide* (UG1144) [Ref 7].

The PetaLinux Tools design hub provides information and links to documentation specific to PetaLinux Tools. For more information, see Documentation Navigator and Design Hubs.

## How the Xilinx Design Tools Expedite the Design Process

You can use the Vivado Design Suite tools to add design sources to your hardware. These include the IP integrator, which simplifies the process of adding IP to your existing project and creating connections for ports (such as clock and reset).

You can accomplish all your hardware system development using the Vivado tools along with IP integrator. This includes specification of the Zynq UltraScale+ Processing System, peripherals, and the interconnection of these components, along with their respective detailed configuration.

The Vitis IDE can be used for software development, hardware acceleration, and platform development. It also be used to debug software applications.

The Zynq UltraScale+ Processing System (PS) can be booted and run without programming the FPGA (programmable logic or PL). However, in order to use any soft IP in the fabric, or to bond out PS peripherals using EMIO, programming of the PL is required. You can program the PL using the Vitis IDE or using the Vivado Hardware Manager.

For more information on the embedded design process, refer to the *Vivado Design Suite Tutorial: Embedded Processor Hardware Design* (UG940) [Ref 2].

For more information about the Zynq UltraScale+ Processing System, refer to the Zynq UltraScale+ Processing System Product Guide (PG201) [Ref 8].

## What You Need to Set Up Before Starting

Before discussing the tools in depth, you should make sure they are installed properly and your environments match the requirements mentioned in the "Example Project" section of this guide.

### Hardware Requirements for this Guide

This tutorial targets the Zynq UltraScale+ ZCU102 evaluation board. The examples in this tutorial were tested using the ZCU102 Rev 1 board. To use this guide, you need the following hardware items, which are included with the evaluation board:

- ZCU102 Rev1 evaluation board

- AC power adapter (12 VDC)

- USB Type-A to USB Micro cable (for UART communications)

- USB Micro cable for programming and debugging via USB-Micro JTAG connection

- SD-MMC flash card for Linux booting

- Ethernet cable to connect target board with host machine

- Monitor with Display Port (DP) capability and at least 1080P resolution.

- DP cable to connect the Display output from ZCU102 Board to a DP monitor.

### **Installation Requirements**

### Vitis Integrated Design Environment and Vivado Design Suite

Make sure that you have installed the 2019.2 Vitis IDE. Visit https://www.xilinx.com/support/download.html to confirm that you have the latest tools version.

Ensure that you have the Vitits 2019.2 software development platform installed. The Vitis IDE is a Xilinx unified tool which comes with all the hardware and software as a package. If you install the Vitis IDE, you will automatically get both the Vivado Design Suite and the Vitis IDE. You do not have to make any extra selections in the installer. The installation and selection window is shown below.

| 🗜 Vitis IDE 2019.2 Installer - Vitis Development Environments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | – a ×                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Vitis Development Environments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | € XILINX.            |

| Customize your installation by (de)selecting items in the tree below. Noving the cursor over the selections below provides additional information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |

| Choose the right devices for your target device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      |

| Control of the c |                      |

| Download Star: 1888 08<br>Disk Space Required: 78.54 G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reset to Defaults    |

| Copyright (2) 1986-2019 Xilinx, Inc. All rights                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | < Back Next > Cancel |

Figure 1-2: Vitis IDE Installer with Vivado

For more information on installing the Vivado Design Suite, refer to the Vitis Embedded Software Development Flow Documentation [Ref 13].

### PetaLinux Tools

Install the PetaLinux Tools to run through the Linux portion of this tutorial. PetaLinux tools run under the Linux host system running one of the following:

- Red Hat Enterprise Workstation/Server 7.4, 7.5, 7.6 (64-bit)

- CentOS Workstation/Server 7.4, 7.5, 7.6 (64-bit)

- Ubuntu Linux Workstation/Server 16.04.5, 16.04.6, 18.04.1, 18.04.02 (64-bit)

This can use either a dedicated Linux host system or a virtual machine running one of these Linux operating systems on your Windows development platform.

When you install PetaLinux Tools on your system of choice, you must do the following:

- Download PetaLinux 2019.2 software from the Xilinx Website.

- Download the ZCU102 PetaLinux BSP (ZCU102 BSP (prod-silicon)) from the 2019.2 downloads page.

- Add common system packages and libraries to the workstation or virtual machine. For more information, see the Installation Requirements from the *PetaLinux Tools Documentation: Reference Guide* (UG1144) [Ref 7].

### Prerequisites

- 8 GB RAM (recommended minimum for Xilinx tools)

- 2 GHz CPU clock or equivalent (minimum of 8cores)

- 100 GB free HDD space

#### Extract the PetaLinux Package

PetaLinux tools installation is straight-forward. Without any options, the PetaLinux tools are installed into the current working directory. Alternatively, an installation path may be specified.

For example: To install PetaLinux tools under /opt/pkg/petalinux/2019.2:

```

$ mkdir -p /opt/pkg/petalinux/2019.2

$ ./petalinux-v2019.2-final-installer.run /opt/pkg/petalinux/2019.2

```

For more information, see PetaLinux Tools Documentation: Reference Guide [Ref 7].

### Software Licensing

Xilinx software uses FLEXnet licensing. When the software is first run, it performs a license verification process. If the license verification does not find a valid license, the license wizard guides you through the process of obtaining a license and ensuring that the license can be used with the tools installed. If you do not need the full version of the software, you can use an evaluation license.For installation instructions and information, see the *Vivado Design Suite User Guide: Release Notes, Installation, and Licensing* (UG973) [Ref 3].

### **Tutorial Design Files**

See Design Files for This Tutorial for information about downloading the design files for this tutorial.

## **E** XILINX.

## Zynq UltraScale+ MPSoC Processing System Configuration

Now that you have been introduced to the Xilinx<sup>®</sup> Vivado<sup>®</sup> Design Suite, you will learn how to use it to develop an embedded system using the Zynq<sup>®</sup> UltraScale+<sup>™</sup> MPSoC Processing System (PS).

The Zynq UltraScale+ device consists of Quad-Core Arm® Cortex®-A53 based APU, Dual-Core Arm Cortex-R5 RPU, Mali 400 MP2 GPU, and many hard Intellectual Property components (IPs), and Programmable Logic (PL). This offering can be used in two ways:

- The Zynq UltraScale+ PS can be used in a standalone mode, without attaching any additional fabric IP.

- IP cores can be instantiated in fabric and attached to the Zynq UltraScale+ PS as a PS+PL combination.

## Zynq UltraScale+ System Configuration

Creation of a Zynq UltraScale+ system design involves configuring the PS to select the appropriate boot devices and peripherals. To start with, as long as the PS peripherals and available MIO connections meet the design requirements, no bitstream is required. This chapter guides you through creating a simple PS-based design that does not require a bitstream.

In addition to the basic PS configuration, this chapter will briefly touch upon the concept of Isolation Configuration to create subsystems with protected memory and peripherals. This advanced configuration mode in the PS Block enables you to setup subsystems comprising Masters with dedicated memory and peripherals. The protection is provided by the XMPU and the XPPU in Zynq UltraScale+ PS block. The isolation configuration also allows the TrustZone settings for components to create and configure the systems in Secure and Non-Secure Environments.

## Example Project: Creating a New Embedded Project with Zynq UltraScale+ MPSoC

For this example, you will launch the Vivado Design Suite and create a project with an embedded processor system as the top level.

## **Starting Your Design**

- 1. Start the Vivado Design Suite.

- 2. In the Vivado Quick Start page, click **Create Project** to open the New Project wizard.

- 3. Use the information in the table below to make selections in each of the wizard screens.

**Wizard Screen** System Property Setting or Command to Use **Project Name** Project name edt zcu102 Project Location C:/edt Create Project Subdirectory Leave this checked **Project Type** Specify the type of sources for your **RTL Project** design. You can start with RTL or a synthesized EDIF. Do not specify sources at this time Leave this unchecked. check box Add Sources Do not make any changes to this screen. Add Constraints Do not make any changes to this screen. **Default Part Boards** Select Zynq UltraScale+ ZCU102 Display Name **Evaluation Board** New Project Summary Project Summary Review the project summary

Table 2-1: New Project Wizard Options

4. Click **Finish**. The New Project wizard closes and the project you just created opens in the Vivado design tool.

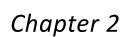

### **Creating a Block Design Project**

You will now use the IP Integrator to create a Block Design project.

1. In the Flow Navigator, under IP Integrator, click Create Block Design.

#### Figure 2-1: Create Block Design Button

The Create Block Design wizard opens.

2. Use the following information to make selections in the Create Block Design wizard.

Table 2-2: Setting in Create Block Design Wizard

| Wizard Screen       | System Property    | Setting or Command to Use        |

|---------------------|--------------------|----------------------------------|

| Create Block Design | Design Name        | edt_zcu102                       |

|                     | Directory          | <local project="" to=""></local> |

|                     | Specify Source Set | Design Sources                   |

3. Click **OK**.

The Diagram window view opens with a message that states that this design is empty. To get started, you will next add some IP from the catalog.

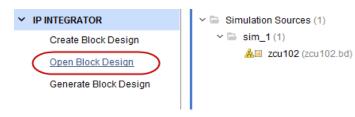

- 4. Click the Add IP button | + .

- 5. In the search box, type **zynq** to find the Zynq device IP.

- 6. Double-click the **ZYNQ UltraScale+ MPSoC** IP to add it to the Block Design.

The Zynq UltraScale+ MPSoC processing system IP block appears in the Diagram view, as shown in the following figure.

Figure 2-2: Zynq UltraScale+ MPSoC Processing System IP Block

### Managing the Zynq UltraScale+ Processing System in Vivado

Now that you have added the processor system for the Zynq MPSoC to the design, you can begin managing the available options.

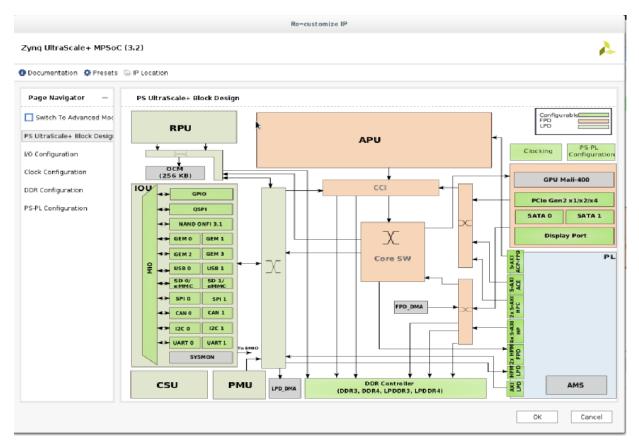

1. Double-click the **ZYNQ UltraScale+ Processing System** block in the Block Diagram window.

The Re-customize IP dialog box opens, as shown in the following figure. Notice that by default, the processor system does not have any peripherals connected

Figure 2-3: Re-customize IP Dialog Box

2. Click **Cancel** to exit the dialog box without making changes to the design.

**TIP:** In the Block Diagram window, notice the message stating that designer assistance is available, as shown in the following figure. When designer assistance is available, you can click the link to have Vivado perform that step in your design.

| Diagram × Address Editor ×               | 2013 |

|------------------------------------------|------|

| ଷ୍ଟ୍ର୍୍୍ର୍୍ର୍୍ର୍ର୍ର୍ର୍ର୍ର୍ର୍ର୍ର୍ର୍ର୍ର୍ର୍ | 0    |

|                                          |      |

Figure 2-4: Designer Assistance Link

3. You will now use a preset template created for the ZCU102 board. Click the **Run Block Automation** Link.

The Run Block Automation dialog box opens.

4. Click **OK** to accept the default processor system options and make default pin connections.

This configuration wizard enables many peripherals in the Processing System with some multiplexed I/O (MIO) pins assigned to them according to the board layout of the ZCU102 board. For example, UART0 and UART1 are enabled. The UART signals are connected to a USB-UART connector through UART to the USB converter chip on the ZCU102 board.

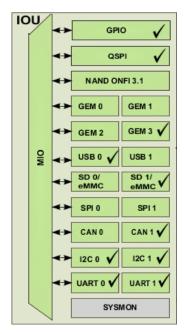

5. To verify, double-click on the **Zynq UltraScale+ Processing System** block in the block diagram window.

Note the check marks that appear next to each peripheral name in the Zynq UltraScale+ device block diagram, signifying the I/O Peripherals that are active.

Figure 2-5: I/O Unit with Active Peripherals Identified

6. In the block diagram, click one of the green I/O Peripherals, as shown in the previous figure. The I/O Configuration dialog box opens for the selected peripheral.

|                              |                     |                   | Re-custor       | nize IP         |          |                      |       |           |

|------------------------------|---------------------|-------------------|-----------------|-----------------|----------|----------------------|-------|-----------|

| Zynq UltraScale+ MPSoC (3.2) |                     |                   |                 |                 |          |                      |       |           |

| Documentation 🔅 Presets      | P Location          |                   |                 |                 |          |                      |       |           |

| Page Navigator –             | I/O Configuration   |                   |                 |                 |          |                      |       |           |

| Switch To Advanced Moc       | ~ MIO Voltage Stan  | dard              |                 |                 |          |                      |       |           |

|                              |                     | Bank1 [MIO 26:51] | Bank2 (MIO 52:7 | 71 Bank3 (Dedic | ated     |                      |       |           |

| PS UltraScale+ Block Desig   | LVCMOS18 V          | LVCM0S18 V        |                 | LVCM0533        | ~        |                      |       |           |

| /0 Configuration             | EVCHOSIS +          | EVENO318 +        | LUCHOSIG        | e Locido333     |          |                      |       |           |

| Clock Configuration          | + Q ± + (           |                   |                 |                 |          |                      |       |           |

|                              | Search: Q-          |                   |                 |                 |          |                      |       |           |

| ODR Configuration            | Peripheral          | VO                | Signa           | -               | I/O Type | Drive Strength(mA)   | Speed | Pull Type |

| S-PL Configuration           | V Low Speed         | 40                | Sign            | 31              | t/o type | Drive Screngcrittia) | sheen | run type  |

|                              | > Memory Interfaces |                   |                 |                 |          |                      |       |           |

|                              | ✓ I/O Peripherals   |                   |                 |                 |          |                      |       |           |

|                              | > CAN               |                   |                 |                 |          |                      |       |           |

|                              | ~ I2C               |                   |                 |                 |          |                      |       |           |

|                              | > 🖌 12C 0           | MIO 14 15         | ~               |                 |          |                      |       |           |

|                              | > 🖉 I2C 1           | MIO 16 17         | ~               |                 |          |                      |       |           |

|                              | PJTAG               |                   |                 |                 |          |                      |       |           |

|                              | > 🗹 PMU             |                   |                 |                 |          |                      |       |           |

|                              | CSU                 |                   |                 |                 |          |                      |       |           |

|                              | > SPI               |                   |                 |                 |          |                      |       |           |

|                              | > UART              |                   |                 |                 |          |                      |       |           |

|                              | > GPIO              |                   |                 |                 |          |                      |       |           |

|                              | > Processing Unit   |                   |                 |                 |          |                      |       |           |

|                              | > High Speed        |                   |                 |                 |          |                      |       |           |

|                              | > Reference Clocks  |                   |                 |                 |          |                      |       |           |

|                              |                     |                   |                 |                 |          |                      |       |           |

|                              |                     |                   |                 |                 |          |                      |       |           |

|                              | 6.0                 |                   |                 |                 |          |                      |       |           |

Figure 2-6: I/O Configuration Page of the Re-customize IP Dialog Box

This page enables you to configure low speed and high speed peripherals. For this example, you will continue with the basic connection enabled using Board preset for ZCU102.

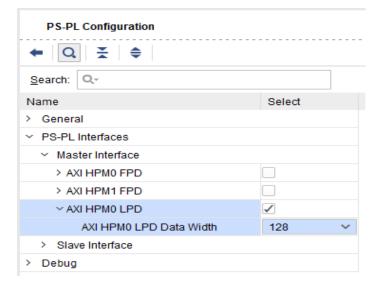

- 7. In the Page Navigator, select **PS-PL Configuration**.

- 8. In PS-PL Configuration, expand **PS-PL Interfaces** and expand the **Master Interface**.

For this example, because there is no design in PL, you can disable the PS-PL interface. In this case, AXI HPM0 FPD and AXI HPM1 FPD Master Interfaces can be disabled.

9. De-select AXI HPM0 FPD and AXI HPM1 FPD.

The PS-PL configuration looks like following figure.

| 🝌 Re-customize IP           |                                      |        |

|-----------------------------|--------------------------------------|--------|

| Zynq UltraScale+ MPSoC (3   |                                      |        |

| Page Navigator —            | PS-PL Configuration                  |        |

| Switch To Advanced Mode     | ←   Q   풒   ≑                        |        |

| PS UltraScale+ Block Design | Search: Q-                           |        |

|                             | Name                                 | Select |

| I/O Configuration           | > General                            |        |

|                             | <ul> <li>PS-PL Interfaces</li> </ul> |        |

| Clock Configuration         | <ul> <li>Master Interface</li> </ul> |        |

| DDR Configuration           | > AXI HPM0 FPD                       |        |

|                             | > AXI HPM1 FPD                       |        |

| PS-PL Configuration         | > AXI HPM0 LPD                       |        |

|                             | > Slave Interface                    |        |

|                             | > Debug                              |        |

Figure 2-7: **PS-PL Configuration**

10. Click **OK** to close the Re-customize IP wizard.

### **Isolation Configuration**

This section is for reference only. It explains the importance of Isolation Configuration settings for different use-cases. Different use-cases may need to establish Isolation Configurations on an as-need basis. Isolation configuration is optional and you can set it as per your system requirement. Safety/Security critical use cases typically require isolation between safe/non-safe or secure/non-secure portions of the design. This requires a safe/secure region that contains a master (such as the RPU) along with its slaves (memory regions and peripherals) to be isolated from non-safe or non-secure portions of the design. In such cases, the TrustZone attribute can be applied to the dedicated peripherals or memory locations. In this way only a valid and trusted master can access the secure slaves. An other use-case requiring Isolation is for Platform and Power management. In this case, independent subsystems can be created with Masters and slaves. This is used to identify dependencies during run-time power management or warm restart for upgrade or recovery. An example of this use-case can be found on the Zyng UltraScale+ Restart solution wiki page. The Xilinx Memory Protection Unit (XMPU) and Xilinx Peripheral Protection Unit (XPPU) in Zyng UltraScale+ provide hardware protection for memory and peripherals. These protection units complement the isolation provided by TrustZone (TZ) and the Zynq UltraScale+ MPSoC SMMU.

The XMPU and XPPU in Zynq UltraScale+ allow Isolation of resources at SoC level. Arm MMU and Trustzone enable Isolation within Arm Cortex-A53 Core APU. Hypervisor and SMMU allows setting Isolation between Cortex-A53 cores. From a tools standpoint, these Protection Units can be configured using Isolation Configuration in Zynq UltraScale+ PS IP wizard. The Isolation settings are exported as an initialization file which is loaded as a part

of the bootloader, in this case the First Stage Boot Loader (FSBL). For more details, see the *Zyng UltraScale+ MPSoC Technical Reference Manual* (UG1085) [Ref 5].

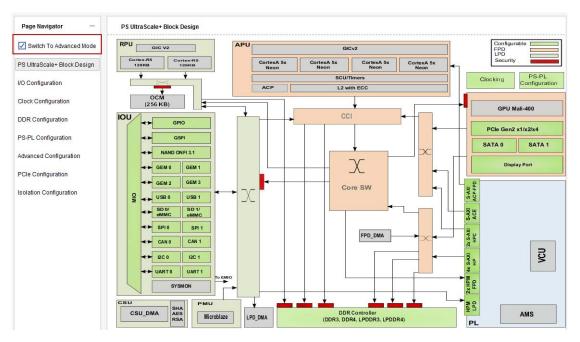

- 1. Double-click the **Zynq UltraScale+ Processing System** in the block diagram window, if it is not open.

- 2. Select Switch To Advanced Mode.

Notice the protection elements indicated by red blocks in the wizard.

Figure 2-8: PS Configuration Advanced Mode

3. To create an isolation setup, click Isolation Configuration.

This tutorial does not use Isolation Configuration and hence, no Isolation related settings are requested.

4. Click **OK** to close the Re-customize IP wizard.

*Note:* For detailed steps to create isolation configuration, see XAPP1320.

### Validating the Design and Connecting Ports

Use the following steps to validate the design:

- 1. Right-click in the white space of the Block Diagram view and select **Validate Design**. Alternatively, you can press the **F6** key.

- 2. A message dialog box opens and states "Validation successful. There are no errors or critical warnings in this design."

- 3. Click **OK** to close the message.

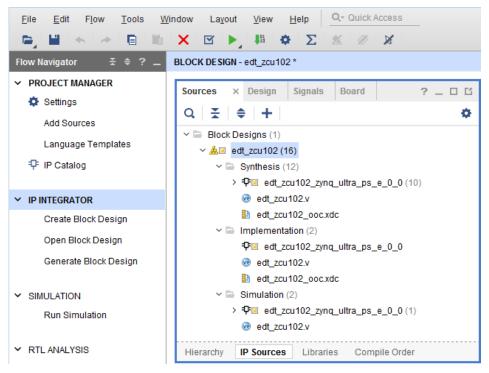

- 4. In the Block Design view, click the **Sources** tab.

- 5. Click Hierarchy.

- 6. Under Design Sources, right-click edt\_zcu102 and select Create HDL Wrapper.

The Create HDL Wrapper dialog box opens. You will use this dialog box to create a HDL wrapper file for the processor subsystem.

**TIP:** The HDL wrapper is a top-level entity required by the design tools.

- 7. Select Let Vivado manage wrapper and auto-update and click OK.

- 8. In the Block Diagram, Sources window, under **Design Sources**, expand **edt\_zcu102\_wrapper**.

- 9. Right-click the top-level block diagram, titled edt\_zcu102\_i : edt\_zcu102 (edt\_zcu102.bd) and select Generate Output Products.

The Generate Output Products dialog box opens, as shown in the following figure.

| 🝌 Generate Output Products                       | ×     |

|--------------------------------------------------|-------|

| The following output products will be generated. | 2     |

|                                                  |       |

| Preview                                          |       |

| Q                                                |       |

| ✓ ♣I edt_zcu102.bd (OOC per IP)                  |       |

| 🎒 Synthesis                                      |       |

| Implementation                                   |       |

| Dimulation                                       |       |

| Synthesis Options                                |       |

| O <u>G</u> lobal                                 |       |

| Out of context per IP                            |       |

| Out of context per <u>B</u> lock Design          |       |

| Run Settings                                     |       |

| Number of jobs: 2                                |       |

| Apply     Generate     Ca                        | ancel |

Figure 2-9: Generate Output Products Dialog Box

*Note:* If you are running the Vivado Design Suite on a Linux host machine, you might see additional options under Run Settings. In this case, continue with the default settings.

10. Click Generate.

This step builds all required output products for the selected source. For example, constraints do not need to be manually created for the IP processor system. The Vivado tools automatically generate the XDC file for the processor subsystem when **Generate Output Products** is selected.

- 11. Click **OK**, if you see the message: "Out-of-context module run was launched for generating output products".

- 12. When the Generate Output Products process completes, click **OK**.

- 13. In the Block Diagram Sources window, click the **IP Sources** tab. Here you may see the output products that you just generated, as shown in the following figure.

Figure 2-10: Outputs Generated Under IP Sources

### **Exporting Hardware**

1. Select File > Export > Export Hardware.

The Export Hardware dialog box opens. Provide the location for exporting hardware in local path.

| 🝌 Export Har                                             | dware             | ×      |  |  |

|----------------------------------------------------------|-------------------|--------|--|--|

| Export hardware platform for software development tools. |                   |        |  |  |

| Include                                                  | bitstream         |        |  |  |

| Export to:                                               | C:/edt/edt_zcu102 | ⊗ …    |  |  |

| ?                                                        | OK                | Cancel |  |  |

|                                                          |                   |        |  |  |

Figure 2-11: Export Hardware

#### 2. Click **OK**.

**?**

$\bigcirc$

**TIP:** The hardware is exported in a ZIP file (<project wrapper>.xsa). When you create the platform in Vitis IDE using hardware .xsa, the ZIP file automatically unzips and files are created in the project platform folder.

### Creating a Hardware Platform using Vitis IDE

- Launch the Vitis IDE from Windows start menu shortcut or by double-clicking the C:\Xilinx\Vitis\2019.2\bin\vitis.bat file.

- 2. Select the workspace and continue.

؇ Eclipse Launcher

$\times$

#### Select a directory as workspace

Vitis IDE uses the workspace directory to store its preferences and development artifacts.

| Workspace:   | C:\edt                                                      | ~  | Browse |        |

|--------------|-------------------------------------------------------------|----|--------|--------|

|              | is the default and do not ask again<br><b>Fer Workspace</b> |    |        |        |

| • Recent Wor | kspaces                                                     |    |        |        |

|              |                                                             | Lá | aunch  | Cancel |

Figure 2-12: Launching the Vitis IDE

- 3. In the Vitis IDE, go to File > New > Platform Project.

- 4. Enter the Hardware Platform name and click Next.

| E New Platform Project                                                                                                                                               |                  |              | ×   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|-----|

| Create new platform project                                                                                                                                          |                  |              |     |

| Enter a name for your platform project                                                                                                                               |                  |              |     |

| Project name: edt_zcu102_wrapper                                                                                                                                     |                  |              |     |

| ✓ Use default location                                                                                                                                               |                  |              |     |

| Location: C:\edt\edt_zcu102_wrapper                                                                                                                                  |                  | Browse       | 2   |

| Choose file system: default \vee                                                                                                                                     |                  |              |     |

| System Project 2<br>Project 1<br>Linux<br>App 1<br>Linux<br>App 2<br>Linux<br>App 2<br>Linux<br>App 2<br>Linux<br>App 2<br>Linux<br>App 2<br>Linux<br>App 2<br>Linux | t would run on ( |              |     |

| A72_0<br>Baremetal<br>Domain<br>Platform                                                                                                                             |                  | controls one | or  |

| A platform con                                                                                                                                                       | ntains one or m  | ore domains  | s.  |

| A workspace ca<br>and unlimited sv                                                                                                                                   |                  | nited platfo | rms |

| ⑦ < Back Next >                                                                                                                                                      | Finish           | Cance        | I   |

5. Select Create from hardware specification (XSA/DSA), then click **Next**.

| 😢 New Platform Proje                                                                                                                                                                                                                                                                                                                           | ct                   |                |                                                 |         |         | ×      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-------------------------------------------------|---------|---------|--------|

| Platform Project                                                                                                                                                                                                                                                                                                                               |                      |                |                                                 |         |         |        |

| Create new platform p                                                                                                                                                                                                                                                                                                                          | roject               |                |                                                 |         |         |        |

| Create a platform project from output of Vivado [Xilinx Shell Archive (XSA) or Device Support Archive (DSA)] or from an existing platform. A platform will enable you to specify options for the kernels, BSPs as well as settings required for creating new applications. Platforms are currently supported for embedded software developers. |                      |                |                                                 |         |         | SPs as |

| Create from hardw                                                                                                                                                                                                                                                                                                                              | are specification (  | XSA/DSA)       |                                                 |         |         |        |

|                                                                                                                                                                                                                                                                                                                                                |                      |                | n file. You can specify<br>er from the platform |         |         |        |

| Create from existin<br>Load the platform d<br>platform repository                                                                                                                                                                                                                                                                              | efinition from an ex |                | can choose any plat                             | form fi | rom the |        |

| 0                                                                                                                                                                                                                                                                                                                                              | < <u>B</u> ack       | <u>N</u> ext > | Einish                                          |         | Cancel  |        |

*Figure 2-14:* Selecting Custom Hardware

6. Browse the **.xsa/.dsa** file which is generated from Vivado.

| 😢 New Platform Pr                                                                                                                                           | Rew Platform Project - C X     |                        |                |       |     |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------|----------------|-------|-----|--|

| Platform Project                                                                                                                                            | Platform Project Specification |                        |                |       |     |  |

| Provide the hardwa                                                                                                                                          | re and software specifi        | ication for the new pl | atform project |       |     |  |

| Hardware Specification                                                                                                                                      | n                              |                        |                |       |     |  |

| XSA/DSA file: C:\e                                                                                                                                          | edt\edt_zcu102\edt_zc          | u102_wrapper.xsa       |                | Brows | e   |  |

| Software Specificatio                                                                                                                                       | n                              |                        |                |       |     |  |

| Operating system:                                                                                                                                           | standalone                     | ~                      |                |       |     |  |

| Processor:                                                                                                                                                  | psu_cortexa53_0                | ~                      |                |       |     |  |

| Note: The generated platform will have a single domain with the selected OS and processor. The<br>platform project can be modified later to add new domains |                                |                        |                |       |     |  |

| plationitipioj                                                                                                                                              |                                |                        |                |       |     |  |

|                                                                                                                                                             |                                |                        |                |       |     |  |

|                                                                                                                                                             |                                |                        |                |       |     |  |

|                                                                                                                                                             |                                |                        |                |       |     |  |

|                                                                                                                                                             |                                |                        |                |       |     |  |

|                                                                                                                                                             |                                |                        |                |       |     |  |

| ?                                                                                                                                                           | < <u>B</u> ack                 | <u>N</u> ext >         | Einish         | Can   | cel |  |

Figure 2-15: Selecting Hardware Specification

- 7. Click Finish.

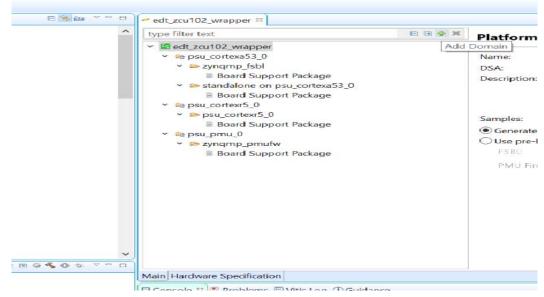

- 8. In a few minutes, the Vitis IDE generates the platform. The files that are generated are displayed in the explorer window as shown in the following figure.

| edt - edt_zcu102_wrapper/platform.spr - Vitis IDE<br>Eile Edit Developer Xilinx Project Window Help                                                       |                                                                                                                                                                                                                                                                                                                         |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                         |  |

| Explorer X          Seedt_zcu102_wrapper         > adsa         > bdsa         > cores         > zynqmp_fsbl         > zynqmp_mufw         ~ platform.spr | <ul> <li>edt_zcu102_wrapper <sup>82</sup></li> <li>type filter text</li> <li>edt_zcu102_wrapper</li> <li>get zvnqmp_fsbl</li> <li>Board Support Package</li> <li>estandalone on psu_cortexa53_0</li> <li>Board Support Package</li> <li>get psu_pmu_0</li> <li>e zynqmp_pmufw</li> <li>Board Support Package</li> </ul> |  |

Figure 2-16: Adding a Custom Platform

9. Default FSBL and PMU firmware comes with the platform project and psu\_cortexa53\_0 domain also added to the platform. We can add multiple domains to platform and we can also create FSBL like any other application.

*Note:* To add the following libraries by modifying the standalone on psu\_cortexa53\_0 domain, follow these steps:

- a. Double-click the standalone on psu\_cortexa53\_0 BSP.

- b. Click Modify BSP Settings.

- c. On the Overview page, select the **xilffs**, **xilpm**, **xilsecure** libraries.

- 10. Now build the hardware by right-clicking on **Platform > Build project**.

| Explorer 🛙                                                                                                               |                                                                                                                                                     | E 😽 🖮 💎 🤅             | □                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>edt_zcu102_wi</li> <li>edsa</li> <li>logs</li> <li>psu_cortexi</li> <li>resources</li> <li>zynqmp_fs</li> </ul> | Refresh Import Sources Export as Archive Build Project Clean Project Make Project Portable Update Hardware Specification Run As Debug As Properties | ><br>Ctrl+V<br>><br>> | type filter text         ▼ @ edt_zcu102_wrapper         * @ psu_cortexa53_0         # Board Support Package         * @ standalone on psu_cortexa53_0         # Board Support Package         * @ psu_pmu_0         * @ psu_pmu_0mufw         # Board Support Package |

Figure 2-17: Building Hardware Platform

The hardware platform is ready. You can create applications using this platform and test on zcu102 hardware.

### Creating a Vitis Domain for cortexr5\_0

To create a Vitis domain for cotexr5\_0, follow these steps:

- 1. The **edt\_zcu102\_wrapper** platform is, by default, assigned the default domain for psu\_cortexa53\_0. For applications targeting the RPU, you have to create a domain for cortexr5\_0

- 2. Double click **platform.spr**. The platform explorer opens.

- 3. Click the + in the top right corner to add the domain.

- 4. Create a domain with the following settings:

Table 2-3: Settings to Create a New Domain

| System Properties | Setting or Command to Use |

|-------------------|---------------------------|

| Name              | psu_cortexr5_0            |

| Display name      | psu_cortexr5_0            |

| OS                | Standalone                |

| Version           | Standalone (7.1)          |

| Processor         | psu_cortexr5_0            |

| Supported Runtime | C/C++                     |

5. The Vitis IDE creates a new domain and **psu\_cortexr5\_0** appears under the **edt\_zcu102\_wrapper** platform.

**Note:** Add the xilffs, xilpm, and xilsecure libraries by modifying psu\_cortexr5\_0 domain. To do so, double-click on **standalone on psu\_cortexr5\_0 bsp**, then click Modify BSP Settings. On the Overview page, select the desired libraries.

## Chapter 3

## Build Software for PS Subsystems

This chapter lists the steps to configure and build software for PS subsystems. In this chapter, you will use the Zynq<sup>®</sup> UltraScale<sup>™</sup> + hardware platform (hardware definition file) configured in the Vivado<sup>®</sup> Design Suite.

In Chapter 2, you created and exported the hardware platform from Vivado. This hardware platform contains the hardware handoff file, the processing system initialization files (psu\_init), and the PL bitstream. In this chapter, you will use the hardware platform in the Vitis IDE and PetaLinux to configure software for the processing system.

This chapter serves two important purposes. One, it helps you build and configure the software components that can be used in future chapters. Second, it describes the build steps for a specific PS subsystem.

## Processing Units in Zynq UltraScale+

The main processing units in the processing system in Zynq UltraScale+<sup>™</sup> are listed below.

- Application Processing Unit: Quad-core Arm ® Cortex ® -A53 MPCore Processors

- Real Time Processing Unit: Dual-core Arm Cortex-R5 MPCore Processors

- Graphics Processing Unit: Arm Mali 400 MP2 GPU

- Platform Management Unit (PMU)

This section demonstrates configuring these units using system software. This can be achieved either at the boot level using First Stage Boot Loader (FSBL) or via system firmware, which is applicable to the platform management unit (PMU).

You will use the Zynq UltraScale+ hardware platform in the Vitis IDE to perform the following tasks:

- 1. Create a First Stage Boot Loader (FSBL) for the Arm Cortex-A53 64-bit quad-core processor unit (APU) and the Cortex-R5 dual-core real-time processor unit (RPU).

- 2. Create bare-metal applications for APU and RPU.

- 3. Create platform management unit (PMU) firmware for the platform management unit using the Vitis IDE.

In addition to the bare-metal applications, this chapter also describes building U-Boot and Linux Images for the APU. The Linux images and U-Boot can be configured and built using the PetaLinux build system.

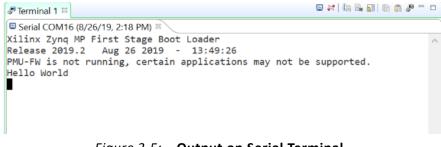

## Example Project: Running the "Hello World" Application from Arm Cortex-A53

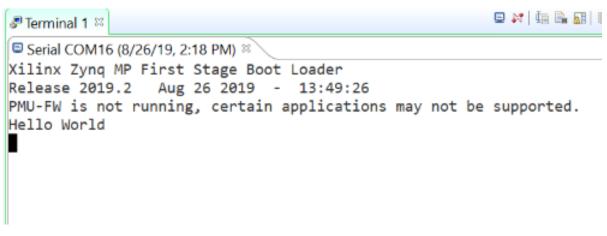

In this example, you will learn how to manage the board settings, make cable connections, connect to the board through your PC, and run a simple hello world software application from Arm Cortex-A53 in JTAG mode using System Debugger in the Vitis IDE.

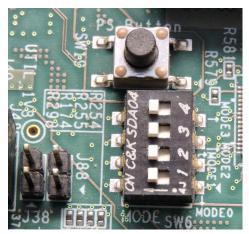

- 1. Connect the power cable to the board.

- 2. Connect a USB Micro cable between the Windows Host machine and J2 USB JTAG connector on the Target board.

- 3. Connect a USB micro cable to connector J83 on the target board with the Windows Host machine. This is used for USB to serial transfer.