# Vivado Design Suite User Guide

## Release Notes, Installation, and Licensing

UG973 (v2016.4) November 30, 2016

## **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                                               |

|------------|---------|------------------------------------------------------------------------|

| 11/30/2016 | 2016.4  | 2016.4 What's New Featuring the latest:                                |

|            |         | New Device Support.                                                    |

|            |         | New Board Support.                                                     |

| 10/05/2016 | 2016.3  | 2016.3 What's New Featuring the latest:                                |

|            |         | New Device Support.                                                    |

|            |         | New Vivado Design Edition Tools.                                       |

| 06/08/2016 | 2016.2  | 2016.2 What's New Featuring the latest:                                |

|            |         | New Device Support.                                                    |

|            |         | New Vivado Design Edition Tools.                                       |

|            |         | New Simulation section.                                                |

| 04/13/2016 | 2016.1  | Editorial updates and added new devices to the General Access section. |

| 04/06/2016 | 2016.1  | Initial version.                                                       |

## **Table of Contents**

| Revision History                                 | 2  |

|--------------------------------------------------|----|

| Chapter 1: Release Notes 2016.4                  |    |

| What's New                                       | 5  |

| Important Information                            | 6  |

| Known Issues                                     | 7  |

| Chapter 2: Architecture Support and Requirements |    |

| Operating Systems                                | 8  |

| Architectures                                    | 9  |

| Compatible Third-Party Tools                     | 9  |

| System Requirements                              | 11 |

| Chapter 3: Download and Installation             |    |

| Downloading the Vivado Design Suite Tools        | 13 |

| Installing the Vivado Design Suite Tools         | 14 |

| Installing Cable Drivers                         | 18 |

| Adding Additional Tools and Devices              | 19 |

| Network Installations                            | 20 |

| Batch Mode Installation Flow                     | 22 |

| Obtaining Quarterly Releases                     | 25 |

| Uninstalling the Vivado Design Suite Tool        | 26 |

| Chapter 4: WebTalk                               |    |

| WebTalk Participation                            | 28 |

| Setting WebTalk Install Preference               | 29 |

| Setting WebTalk User Preferences                 | 30 |

| Checking WebTalk Install and User Preferences    | 31 |

| Types of Data Collected                          | 31 |

| Transmission of Data                             | 32 |

| Chapter 5: Obtaining and Managing a License      |    |

| Licensing Overview                               | 33 |

| Generating/Installing/Managing Activation-Based Licenses | 36  |

|----------------------------------------------------------|-----|

| Generating/Installing Certificate-Based Licenses         | 50  |

| Managing Licenses On Your Machine                        | 56  |

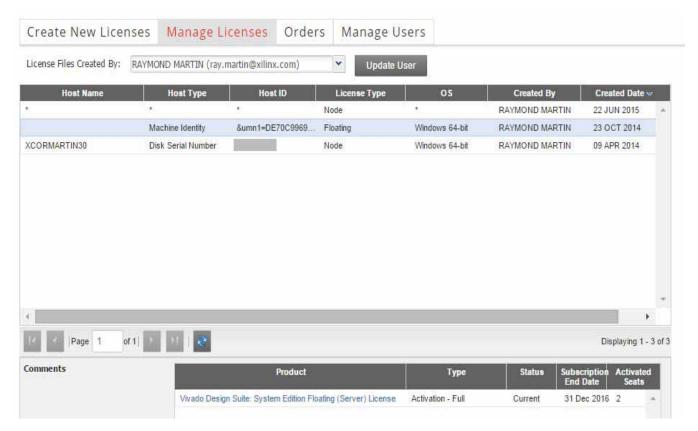

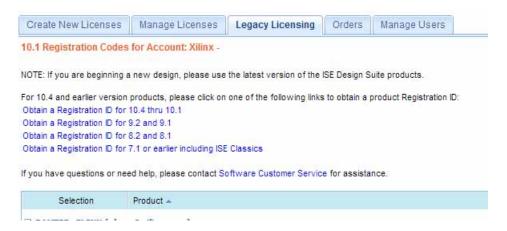

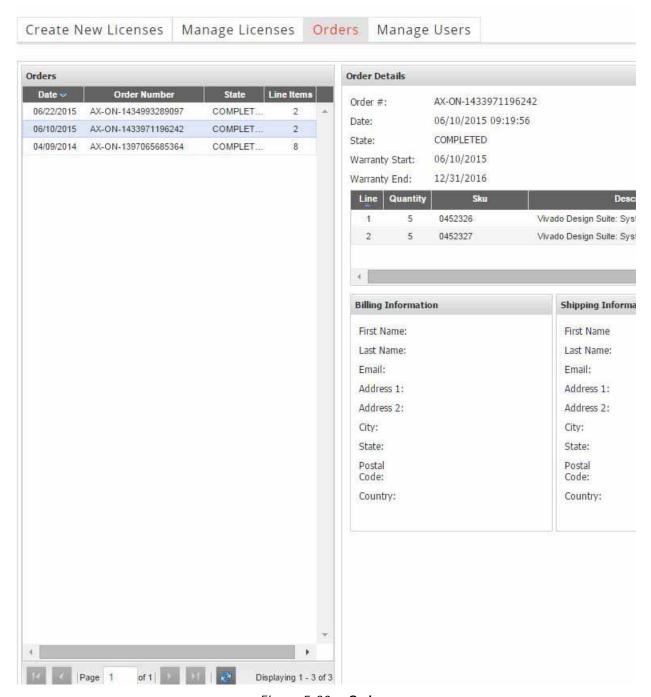

| Using the Xilinx Product Licensing Site                  | 60  |

| Chapter 6: Older Release Notes                           |     |

| Release Notes 2016.3                                     | 75  |

| Release Notes 2016.2                                     | 84  |

| Release Notes 2016.1                                     | 86  |

| Appendix A: Additional Resources and Legal Notices       |     |

| Xilinx Resources                                         | 101 |

| Solution Centers                                         | 101 |

| Documentation Navigator and Design Hubs                  | 101 |

| Licenses and End User License Agreements                 | 102 |

| References                                               |     |

| References                                               | 102 |

| Training Resources                                       |     |

## Release Notes 2016.4

#### What's New

Vivado<sup>®</sup> Design Suite 2016.4 introduces the following Device Support and Vivado System Edition Products.

#### **Device Support**

The following UltraScale+ devices are introduced in this release.

- Virtex UltraScale+:

- XCVU11P and XCVU13P

#### **Board Support**

Board support enables the use of automation to quickly configure and locate interfaces on the evaluation board. This allows quick development of connectivity platforms when used with Block and Connectivity automation. The following board support packages are introduced in this release.

- Zynq UltraScale+ MPSoC ZCU102-ES2 with support for the following interface.

- Processing System with support for:

- USB 3.0

- Gigabit Ethernet

- DisplayPort

- SATA

- DDR4 (4 GB)

- OSPI

- SD card slot

- Can bus

- Dual I2C and UARTs

- DDR4 (512 MB)

- GPIO, Dual I2C, & UART

- Virtex UltraScale+ VCU1180-ES1 with support for the following interfaces

- PCI Express (Gen4 x8)

- Dual DDR4 (4 GB each)

- GPIO, I2C, & UART

#### Multimedia IP

- Video Test Pattern Generator

- 8K resolution support and 8 pixels per clock option

- DisplayPort related test patterns

- Build time configurability allowing what test patterns to include

- Video Mixer

#### Xilinx Software Development Kit

For release notes information on the Xilinx Software Development Kit (SDK) see <u>Answer</u> Record 66230

## Important Information

## **Device Support**

**IMPORTANT**: When opening a checkpoint targeting UltraScale+ Production Evaluation parts, Vivado will issue the following warning:

Production Evaluation speedfiles are provided in advance of production release and are intended to closely approximate production level performance. Once production speedfiles become available, the design will need to be rerun with the production speedfiles.

#### Simulation

#### Export Simulation (export\_simulation)

Multiple switches have been deprecated in this release.

Table 1-1: Deprecated Switches

| Switch Name  | Default Behavior                      | User Action                             | Reason                                                                                                                                                                             |

|--------------|---------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -ip_netlist  | False                                 | None                                    | Fastest simulation is available only in pure RTL. Export simulation optimized to write scripts for fastest simulation performance.                                                 |

| -language    | Mixed                                 | Mixed language<br>simulator<br>required | In order to ensure the fastest simulation performance, export simulation will only use the language of the IP RTL                                                                  |

| -single_step | True for Cadence IES False for others | Be aware of this change                 | Cadence IES simulation will deliver irun scripts that can handle mixed language RTL simulation. Using single-step for the other simulators requires gate level simulation netlist. |

#### Integrated Simulation (launch\_simulation)

- Starting in Vivado 2016.1, the **Generate Scripts Only** capability has been deprecated and removed from the IDE.

- User should use the Export Simulation capability instead. This provides the functionality for exporting files from Vivado (IP and IP Integrator) to use in external verification environments.

#### **Vivado Design Suite Documentation Update**

In the 2016.4 Vivado Design Suite Documentation release, not all documentation will be available at first customer ship. Use the **Update Catalog** button in DocNav to stay up-to-date with the 2016.4 documentation suite.

*Note:* DocNav is a 32-bit application and requires the installation of 32-bit libraries on Linux in order to function.

#### **Known Issues**

Vivado® Design Suite Tools Known Issues can be found at Answer Record 66830.

## Architecture Support and Requirements

## **Operating Systems**

Xilinx® only supports the following operating systems on x86 and x86-64 processor architectures.

#### Microsoft Windows Support

- Windows 7 and 7 SP1 Professional (64-bit), English/Japanese.

- Windows 8.1 Professional (64-bit), English/Japanese.

- Windows 10 Professional (64-bit), English/Japanese.

- Vivado® Lab Edition is the only Xilinx toolset that supports Windows 7 SP1

Professional, 32-bit Operating System. Lab Edition also supports the 64-bit systems.

#### **Linux Support**

- Red Hat Enterprise Workstation/Server 7.1 and 7.2 (64-bit)

- Red Hat Enterprise Workstation 6.7 and 6.8 (64-bit)

- Red Hat Enterprise Workstation 5.11 (64-bit)

- SUSE Linux Enterprise 11.4 and 12.1 (64-bit)

- Cent OS 6.8 (64-bit)

- Ubuntu Linux 16.04 LTS (64-bit)

- Vivado Lab Edition is the only Xilinx toolset that supports the Red Hat Enterprise Workstation 6.6 and 6.7, 32-bit Operating Systems. Lab Edition also supports the 64-bit systems.

#### **Architectures**

The following table lists architecture support for commercial products in the Vivado Design Suite WebPACK™ tool versus all other Vivado Design Suite editions. For non-commercial support:

- All Xilinx Automotive devices are supported in the Vivado Design Suite WebPACK tool.

- Xilinx Defense-Grade FPGA devices are supported where their equivalent commercial part sizes are supported.

Table 2-1: Architecture Support

|                          | Vivado WebPACK Tool                                                                              | Vivado Design Suite<br>(All Other Editions) |

|--------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------|

| Zynq <sup>®</sup> Device | Zynq-7000 AP SoC Device                                                                          | Zynq-7000 AP Soc Device                     |

|                          | <ul> <li>XC7Z010, XC7Z015, XC7Z020,<br/>XC7Z030, XC7Z007S, XC7Z012S, and<br/>XC7Z014S</li> </ul> | • All                                       |

| Virtex® FPGA             | Virtex-7 FPGA                                                                                    | Virtex-7 FPGA                               |

|                          | • None                                                                                           | • All                                       |

|                          | Virtex UltraScale <sup>™</sup> FPGA                                                              | Virtex UltraScale FPGA                      |

|                          | • None                                                                                           | • All                                       |

|                          | Virtex UltraScale                                                                                |                                             |

|                          | • None                                                                                           |                                             |

| Kintex® FPGA             | Kintex-7 FPGA                                                                                    | Kintex-7 FPGA                               |

|                          | • XC7K70T, XC7K160T                                                                              | • All                                       |

|                          | Kintex UltraScale™ FPGA                                                                          | Kintex UltraScale FPGA                      |

|                          | • XCKU025, XCKU035                                                                               | • All                                       |

| Artix <sup>®</sup> FPGA  | Artix-7 FPGA                                                                                     | Artix-7 FPGA                                |

|                          | <ul> <li>XC7A15T, XC7A35T, XC7A50T,<br/>XC7A75T, XC7A100T, XC7A200T</li> </ul>                   | • All                                       |

## **Compatible Third-Party Tools**

**Table 2-2:** Compatible Third-Party Tools

| Third-Party Tool                            | Red Hat<br>Linux | Red Hat<br>Linux-64 | SUSE<br>Linux | Windows-7/10<br>32-bit | Windows-7/10<br>64-bit | Ubuntu |

|---------------------------------------------|------------------|---------------------|---------------|------------------------|------------------------|--------|

| Simulation                                  |                  |                     |               |                        |                        |        |

| Mentor Graphic ModelSim<br>SE/DE/PE (10.5c) | Yes              | Yes                 | Yes           | Yes                    | Yes                    | N/A    |

**Table 2-2:** Compatible Third-Party Tools

| Third-Party Tool                                                               | Red Hat<br>Linux | Red Hat<br>Linux-64 | SUSE<br>Linux | Windows-7/10<br>32-bit | Windows-7/10<br>64-bit | Ubuntu |

|--------------------------------------------------------------------------------|------------------|---------------------|---------------|------------------------|------------------------|--------|

| Mentor Graphics Questa<br>Advanced Simulator(10.5c)                            | Yes              | Yes                 | Yes           | Yes                    | Yes                    | N/A    |

| Cadence Incisive Enterprise<br>Simulator (IES) (15.20.005)                     | Yes              | Yes                 | Yes           | N/A                    | N/A                    | N/A    |

| Synopsys VCS and VCS MX (L-2016.06)                                            | Yes              | Yes                 | Yes           | N/A                    | N/A                    | N/A    |

| The MathWorks MATLAB® and Simulink® with Fixed-Point Toolbox (2016a and 2016b) | Yes              | Yes                 | N/A           | Yes                    | Yes                    | Yes    |

| Aldec Active-HDL (10.3) <sup>a</sup>                                           | N/A              | N/A                 | N/A           | Yes                    | Yes                    | N/A    |

| Aldec Riviera-PRO (2016.06)                                                    | Yes              | Yes                 | Yes           | Yes                    | Yes                    | N/A    |

| Synthesis <sup>b</sup>                                                         |                  |                     |               |                        |                        |        |

| Synopsys Synplify/Synplify<br>Pro (L-2016.03) <sup>c</sup>                     | Yes              | Yes                 | Yes           | Yes                    | Yes                    | N/A    |

| Mentor Graphics Precision<br>RTL/Plus (2015.2)                                 | Yes              | Yes                 | Yes           | Yes                    | Yes                    | N/A    |

| Equivalence Checking                                                           |                  |                     |               |                        |                        |        |

| Cadence Encounter<br>Conformal (9.1) <sup>d</sup>                              | Yes              | Yes                 | Yes           | N/A                    | N/A                    | N/A    |

| OneSpin 360 (2015_12)                                                          | Yes              | Yes                 | Yes           | N/A                    | N/A                    | N/A    |

- a. Support for Aldec simulators is offered by Aldec.

- b. Most Vivado IPs can only be synthesized by Vivado synthesis, because the RTL source can include encrypted files. To use these IPs in a third party synthesis flow, the synthesized netlist can be exported from the Vivado tool in a suitable format for use in the third-party synthesis project.

- c. Contact Synopsys for availability of Synplify Overlay or Service Pack.

- d. Cadence Encounter Conformal Support is for RTL2Gate using Synopsys Synplify only.

System Generator support is restricted to operating systems that are compatible with The MathWorks MATLAB and Simulink tools.

## **System Requirements**

This section provides information on system memory requirements, cable installation, and other requirements and recommendations.

The lab exercises require the installation of MATLAB 2014a (or later) and Vivado Design Suite 2014.2 (or later).

## **System Memory Recommendations**

For memory recommendations for the Vivado Design Suite tools, see: https://www.xilinx.com/design-tools/vivado/memory.htm.

#### Operating Systems and Available Memory

The Microsoft Windows and Linux operating system (OS) architectures have limitations on the maximum memory available to a Xilinx program. Users targeting the largest devices and most complex designs might encounter this limitation. The Vivado Design Suite has optimized memory and enabled support for applications to increase RAM memory available to Xilinx tools.

#### Linux

For 32-bit Red Hat Enterprise Linux systems, the operating system can use the hugemem kernel to allocate 4 GB to each process. More information can be found on the Red Hat support site at <a href="http://www.redhat.com/docs/manuals/enterprise/">http://www.redhat.com/docs/manuals/enterprise/</a>.

#### **Cable Installation Requirements**

Platform Cable USB II is a high-performance cable that enables Xilinx design tools to program and configure target hardware.

**Note:** The Xilinx Parallel Cable IV is no longer supported for debugging or programming.

**RECOMMENDED:** To install Platform Cable USB II, a system must have at least a USB 1.1 port. For maximum performance, Xilinx recommends using Platform Cable USB II with a USB 2.0 port.

The cable is officially supported on the 32-bit and 64-bit versions of the following operating systems: Windows-7, Red Hat Linux Enterprise, and SUSE Linux Enterprise 12. Additional platform specific notes are as follows:

- · Root privileges are required.

- SUSE Linux Enterprise 11: The fxload software package is required to ensure correct Platform Cable USB II operation. The fxload package is not automatically installed on SUSE Linux Enterprise 11 distributions, and must be installed by the user or System Administrator.

For additional information regarding Xilinx cables, refer to the following documents:

- USB Cable Installation Guide (UG344) [Ref 13]

- Platform Cable USB II Data Sheet (DS593) [Ref 14]

#### **Equipment and Permissions**

The following table lists related equipment, permissions, and network connections.

**Table 2-3:** Equipment and Permissions Requirements

| Item                  | Requirement                                                                                                                                                                                 |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Directory permissions | Write permissions must exist for all directories containing design files to be edited.                                                                                                      |

| Monitor               | 16-bit color VGA with a minimum recommended resolution of 1024 by 768 pixels.                                                                                                               |

| Drive                 | You must have a DVD-ROM for Vivado Design Suite (if you have received a DVD, rather than downloading from the web).                                                                         |

| Ports                 | To program devices, you must have an available parallel or USB port appropriate for your Xilinx programming cable. Specifications for ports are listed in the documentation for your cable. |

|                       | <b>Note:</b> Installation of the cable driver software requires Windows-10. If you are not using one of these operating systems, the cables might not work properly.                        |

*Note:* X Servers/ Remote Desktop Servers, such as Exceed, ReflectionX, and XWin32, are not supported.

#### Network Time Synchronization

When design files are located on a network machine, other than the machine with the installed software, the clock settings of both machines must be set the same. These times must be synchronized on a regular basis for continued proper functioning of the software.

## Download and Installation

This guide explains how to download and install the Vivado<sup>®</sup> Design Suite tools, which includes the Vivado Integrated Design Environment (IDE), High Level Synthesis tool, and System Generator for DSP.

## Downloading the Vivado Design Suite Tools

Xilinx® Design Tools users have multiple choices for download and installation.

Xilinx introduced **Vivado Lab Edition**, which features a dedicated and streamlined environment for programming and debugging devices in lab settings.

TIP: No license is required to use Vivado Lab Edition tools.

For users wishing to install one of the full Vivado Editions, there are three choices.

Vivado Design Suite - HLx Editions:

- WebPack and Editions: Web installer for windows

- WebPack and Editions: Web installer for Linux

- All OS Single File Download

All Editions and download options are available on the Xilinx website: https://www.xilinx.com/support/download/index.htm

Most files in the Xilinx Download Center are downloaded using the Akamai download manager. For the optimum download experience:

- Allow pop-ups from <u>entitlenow.com</u>.

- Set security settings to allow for secure and non-secure items to be displayed on the same page.

- Allow the Akamai download manager to run Java processes.

To download a full Edition of the Vivado Design Suite:

1. Select the **Vivado Design Tools** tab in the web page.

- 2. Under the Version heading, click the version of the tools you want to download.

- 3. Click the link for the installer you want to download.

To download the Vivado Lab Edition tools, go to the Vivado Design Tools tab, select a version of 2015.1 or newer, and download the file associated with the Vivado Lab Edition.

**Note:** Lab Edition installer can be run on both 32 or 64-bit machines. The Full Edition installers work only on 64-bit machines.

## Installing the Vivado Design Suite Tools

This section explains the installation process for all platforms for the Vivado Design Suite.

## **Installation Preparation**

**IMPORTANT**: Before starting installation the follow steps must be completed:

- Check the links in Important Information section in Chapter 1 for any installation issues pertaining to your system or configuration.

- Make sure your system meets the requirements described in Chapter 2, Architecture Support and Requirements.

- Disable anti-virus software to reduce installation time.

- Close all open programs before you begin installation.

- The Vivado Design Suite installer does not set global environment variables, such as XILINX, on Windows.

#### Lab Edition, Full Product Download, or DVD

If you downloaded the Lab Edition or full product installation, decompress the file and run xsetup (for Linux) or xsetup.exe (for Windows) to launch the installation. If you received a DVD, which only contains the full Edition products, launch xsetup(.exe) directly.

**RECOMMENDED**: Xilinx recommends the use of 7-zip or WinZip (v.15.0 or newer) to decompress the downloaded tar.gz file.

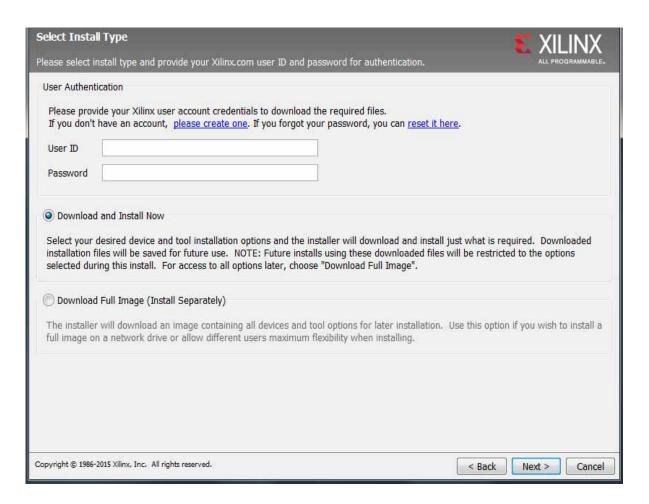

#### Lightweight Installer Download

If you downloaded the lightweight installer, launch the downloaded file. You are prompted to log in and use your regular Xilinx login credentials to continue with the installation process.

After entering your login credentials, you can select between a traditional web-based installation or a full install image download.

- The **Download and Install Now** choice allows you to select specific tools and device families on following screens, downloads only the files required to install those selections, and then installs them for you.

- The Download Full Image requires you to select a download destination and to choose whether you want a Windows only, Linux only, or an install that supports both operating systems. There are no further options to choose with the Download Full Image selection, and installation needs to be done separately by running the xsetup application from the download directory.

**Note:** Lab Edition is not supported through a lightweight installer. You may download the single-file download image for Lab Edition.

Figure 3-1: Vivado Design Suite Installation - Select Installation Source

#### Connectivity

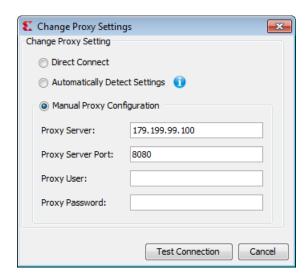

The installer connects to the internet through the system proxy settings in Windows. These settings can be found under **Control Panel > Network and Internet > Internet Options**. For Linux users, the installer uses Firefox browser proxy settings (when explicitly set) to determine connectivity.

Figure 3-2: Vivado Design Suite Installation - Connectivity

If there are connectivity issues, verify the following:

1. If you are using alternate proxy settings to the ones referred to, select the **Manual Proxy Configuration** option to specify the settings.

Figure 3-3: Vivado Design Suite Installation - Change Proxy Settings

- 2. Check if your company firewall requires a proxy authentication with a username and password. If so, select the **Manual Proxy Configuration** option in the dialog box above.

- 3. For Linux users, if either the **Use System settings** or the **Auto detect settings** option is selected in the Firefox browser, you must manually set the proxy in installer.

#### **License Agreements**

Carefully read the license agreements before continuing with the installation. If you do not agree to the terms and conditions, cancel the installation and contact Xilinx.

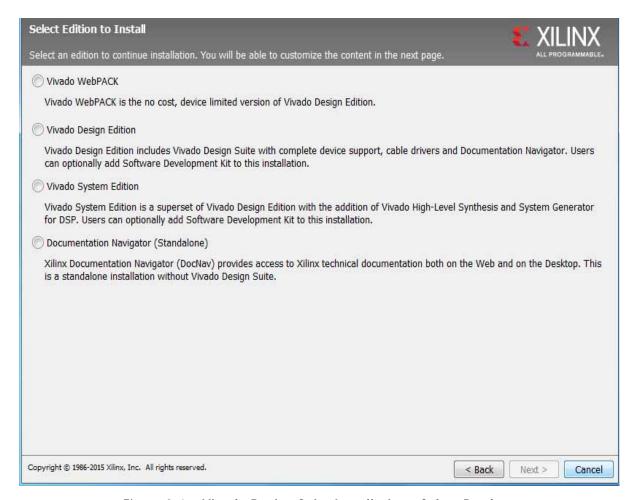

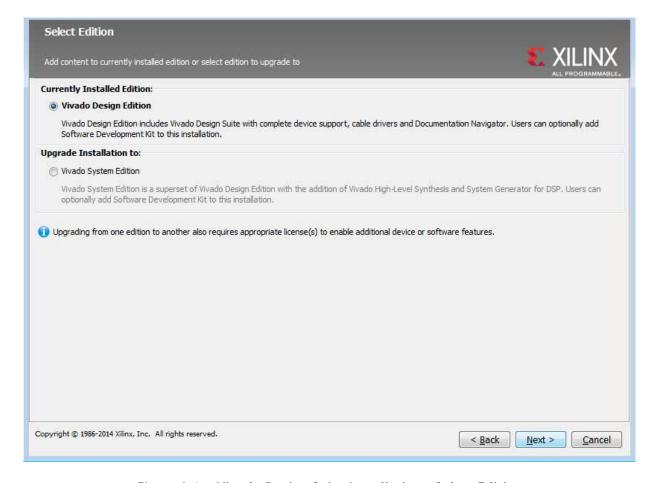

#### **Edition Selection**

Select the edition or standalone tool that is required. You can also install the Xilinx Software Development Kit (XSDK) as part of the Vivado WebPACK, System and Design editions.

Figure 3-4: Vivado Design Suite Installation - Select Products

Vivado WebPACK and Design edition users will also be able to upgrade to a higher edition post installation. See Adding Additional Tools and Devices, page 19 for more details.

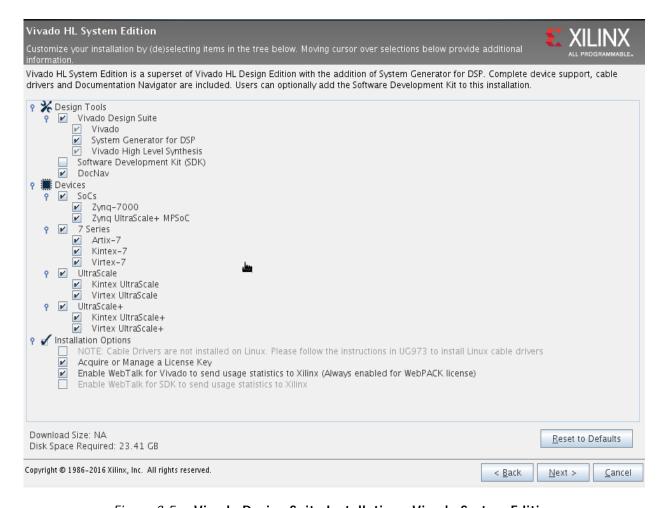

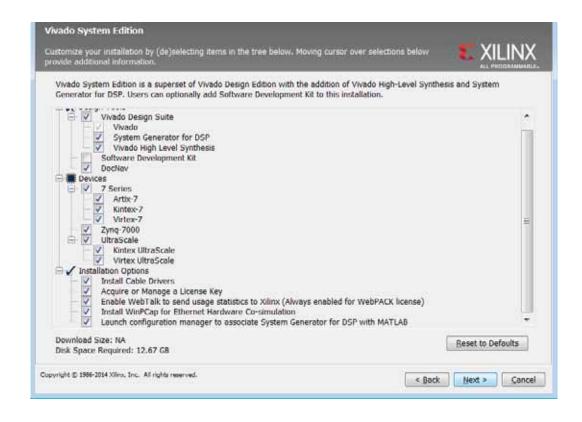

#### Tools, Devices, and Options

Customize the installation by choosing the design tools, device families and installation options. Selecting only what you need helps to minimize the time taken to download and

install the product. You will be able to add to this installation later by clicking **Add Design Tools or Devices** from either the operating system Start Menu or the **Vivado > Help** menu.

Figure 3-5: Vivado Design Suite Installation - Vivado System Edition

#### **Shortcuts and File Associations**

You can customize the creation of the program group entries (Start Menu) and the creation of desktop shortcuts. Optionally, you can also create file associations to launch Vivado project files directly with this version of Vivado. The shortcut creation and file association options can be applied to the current user or all users.

## **Installing Cable Drivers**

On Windows, Install Cable Drivers is an optional selection in the installer.

For Linux, because root or sudo access is required to install drivers, this option has been removed from the Linux installer beginning in Vivado 2015.4. The general Vivado installer can now be run on Linux without root or sudo privileges. To install cable drivers on Linux, there is now a script that must be run as root or sudo post installation.

Script Location: <Vivado Install</pre>

Dir>/data/xicom/cable\_drivers/lin64/install\_script/install\_drivers/

Script Name: install\_drivers

## **Adding Additional Tools and Devices**

You can incrementally add additional tools, devices or even upgrade Vivado editions post-install. This is useful for users that have chosen to install a subset of devices and/or tools.

To add new tools or devices:

- Start Menu > Xilinx Design Tools > Vivado < version > > Add Design Tools or Devices.

- Launch Vivado > Help > Add Design Tools or Devices.

If you have installed the Vivado WebPACK or Design Edition, you are presented with the option to upgrade the edition.

Figure 3-6: Vivado Design Suite Installation - Select Edition

Based on the above selection, you are presented with all available tools and devices that can be added to the current installation.

You can also add tools or devices from the Xilinx Information Center (XIC). See the Obtaining Quarterly Releases section for using this flow.

#### **Network Installations**

Installing to a network location provides a way for client machines to access the design tools by pointing to it on the network drive. To run the design tools on the network, the client machines must be set up correctly to ensure the environment variables, registry, and program groups all point to the network. The following sections describe the procedure for network setups.

#### **Linux Clients**

You must source settings32.(c)sh or settings64.(c)sh (whichever is appropriate for your operating system) from the area in which the design tools are installed. This sets up the environment to point to this installed location.

To run the design tools from a remotely installed location, run an X Windows display manager, and include a DISPLAY environment variable. Define DISPLAY as the name of your display. DISPLAY is typically unix:0.0. For example, the following syntax allows you to run the tools on the host named bigben and to display the graphics on the local monitor of the machine called mynode.

```

setenv DISPLAY mynode:0.0

xhost = bigbenPC Clients

```

#### Microsoft Windows Clients

- 1. Install design tools to a PC network server. Make sure your users know the location of the design tools and have access to the installation directory, and they have Administrator privileges for the following steps.

- 2. From the local client machine, browse to the following directory: network\_install\_location\.xinstall\Vivado\_<version> and run the program networkShortcutSetup.exe.

- Running this program sets up the Windows settings batch files and **Program Group** or **Desktop** shortcuts to run the Xilinx tools from the remote location.

- 3. From the client machine, launch the Vivado Design Suite tools by clicking the **Program Group** or **Desktop** shortcuts, or by running the applications on the network drive.

#### Installing to a Mounted Network Drive

Xilinx design tools are designed to be installed in a directory under ROOT (typically C:\Xilinx). The installer normally presents this option when installing to a local driver.

To work around this issue, either specify a UNC path (for example, \network\_loc\Xilinx\) or define your target installation directory as \Xilinx under the network mount point (For example: N:\Xilinx).

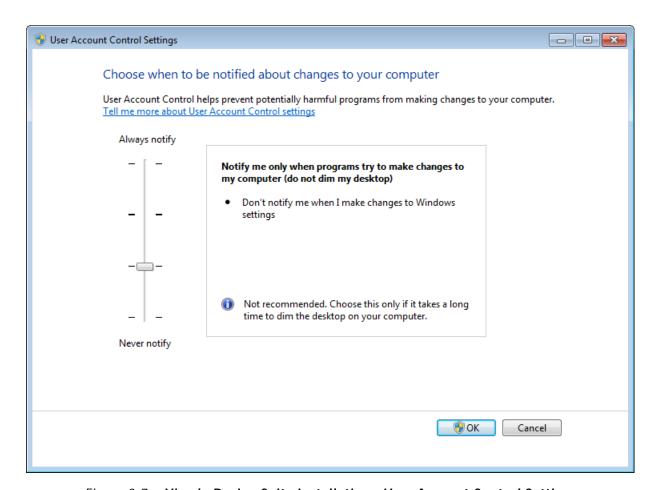

Windows 7 default security levels do not allow you to select remote mapped drives. To install Xilinx Design Tools on remote mapped drives, you must change your account control settings using the following steps:

- 1. Open the Windows Control Panel, from the Windows Start menu, and select 'User Accounts'. If your Control Panel Uses 'Category View', click 'User Accounts' on two successive screens

- 2. Click 'Change User Account Control settings' and allow the program to make changes.

- 3. Click and slide the slide-bar down to the second to lowest setting (as seen in the following figure).

- 4. Click OK.

Figure 3-7: Vivado Design Suite Installation - User Account Control Settings

**RECOMMENDED**: Xilinx recommends that you revisit this procedure to restore your settings to their previous state after installation.

**Note:** You are not able to browse to the remote mapped drives using the Xilinx installer. You need to manually type in your installation path which contains a mapped network drive.

#### **Batch Mode Installation Flow**

Beginning in Vivado 2015.1, the installer can be run as an unattended batch process. To run unattended, a standard Edition and install location must be specified or a configuration file must be present which tells the installer the install location and which of the tools, devices and options you wish to install. The installer has a mode in which it can generate a reference

option file for you based on common configurations, which you can further edit to customize your installation.

**RECOMMENDED:** It is recommended that you generate this reference for each new quarterly release, so that new devices, tools, options or other changes will be accounted for in your options file.

To begin using batch mode, open a command shell and change to the directory where you have stored your extracted installer.

**Note:** For Windows, open the command window with administrator privileges and run the xsetup.bat file, found in the \bin directory, and not xsetup.exx with the options below.

#### **Generate Configuration File**

Run: xsetup -b ConfigGen

This will put you in an interactive mode where you will see the following menu. Choose an edition from the list given below.

- 1. Vivado WebPACK

- 2. Vivado Design Edition

- 3. Vivado System Edition

- 4. Documentation Navigator (Standalone)

After you select an edition, you will be prompted for a location/filename for your configuration file and the interactive mode will exit.

Below is a sample of a WebPACK configuration file:

```

#### Vivado WebPACK Install Configuration ####

Edition=Vivado WebPACK

Destination=C:\Xilinx

Modules=Vivado:1, Vivado High Level Synthesis:0, Software Development

Kit:0,DocNav:0,Artix-7,Kintex-7,Zynq-7000:1

#### Shortcut creation ####

CreateProgramGroupShortcuts=1

CreateShortcutsForAllUsers=0

ProgramGroupFolder=Xilinx Design Tools

CreateDesktopShortcuts=1

CreateFileAssociation=1

#### Post install tasks ####

## Post install tasks can be configured as shown below.

InstallOptions=Configure WebTalk:1, Install and Initialize Trusted Storage

Licensing:1, Generating installed device list:1, Install VC++ runtime libraries for

64-bit OS:1, Install Cable Drivers:0, Acquire or Manage a License Key:0, run:xic:1

```

Basically, each option in the configuration file matches a corresponding option in the GUI. A value of 1 means that option is selected, a value of 0 means the option is unselected.

#### Run the Installer

Now that you have edited your configuration file to reflect your installation preferences, you are ready to run the installer. As part of the installer command-line, you will need to indicate your acceptance of the Xilinx and Third Party license agreements, and confirm you understand the WebTalk Terms and Conditions.

#### Xilinx End-User License Agreement (EULA)

https://www.xilinx.com/support/documentation/sw\_manuals/xilinx2016\_4/end-user-license-agreement.pdf

#### Third Party End-User License Agreement (EULA)

https://www.xilinx.com/support/documentation/sw\_manuals/xilinx2016\_4/ug763\_tplg.pdf

#### WebTalk Terms and Conditions

By indicating I AGREE, I also confirm that I have read Section 13 of the terms and conditions above concerning WebTalk and have been afforded the opportunity to read the WebTalk FAQ posted at <a href="https://www.xilinx.com/webtalk">https://www.xilinx.com/webtalk</a>. I understand that I am able to disable WebTalk later if certain criteria described in Section 13(c) apply. If they don't apply, I can disable WebTalk by uninstalling the Software or using the Software on a machine not connected to the internet. If I fail to satisfy the applicable criteria or if I fail to take the applicable steps to prevent such transmission of information, I agree to allow Xilinx to collect the information described in Section 13(a) for the purposes described in Section 13(b).

There is a command-line switch, -a or --agree for you to indicate your agreement to each of the above. If one of the above is left out of the list, or the agree switch is not specified, the installer will exit with an error and will not install.

#### **Example Command-Lines**

This is an example of the command-line for a typical new installation using a configuration file.

```

xsetup --agree XilinxEULA,3rdPartyEULA,WebTalkTerms --batch Install --config

install_config.txt

```

If you wish to use one of Xilinx's default Edition configurations, you do not have to specify the --config option, but since the destination directory is included in the configuration file, you will be required to specify this on the command-line.

```

xsetup --agree 3rdPartyEULA,WebTalkTerms,XilinxEULA --batch Install --edition

"Vivado System Edition" --location "C:\Xilinx"

```

The above command will utilize the default configuration options for the edition specified. To see the default configuration options, use the -b ConfigGen mode as described above. The Vivado installer's batch mode can also perform uninstallation and upgrades (adding additional tools and devices). For the full list of the installer's batch options run xsetup -h or xsetup --help.

## **Obtaining Quarterly Releases**

Xilinx releases quarterly versions of the Vivado Design Suite tools throughout the year. Each quarterly version contains device support updates, new features and bug fixes. The following sections describe how to obtain updates through the Xilinx Information Center.

#### **Xilinx Information Center**

Xilinx Information Center (XIC) is the next generation replacement of XilinxNotify. This functionality resides in the task bar (Windows) and periodically checks for new releases and updates from Xilinx. Users can view and dismiss notifications as well as update installations.

In addition, XIC now includes a cockpit from which you can manage all of your Xilinx tool installations. Update, check licenses or uninstall all from the new Manage Installs tab.

Figure 3-8: Xilinx Information Center (XIC)

## Uninstalling the Vivado Design Suite Tool

Before uninstalling, make sure to have moved any project files you want to keep outside your Xilinx installation directory structure, or they are deleted.

**Note:** Xilinx Documentation Navigator is not removed during uninstallation. It is intended to be a standalone application common to multiple versions of Xilinx tools. You need to uninstall it separately if it is no longer required.

#### Uninstallation

Before uninstalling, make sure to have moved any project files you want to keep outside your Xilinx installation directory structure, or they will be deleted. See below for information on uninstalling Documentation Navigator and Xilinx Information Center.

#### **Uninstalling Documentation Navigator**

Xilinx Documentation Navigator will not be removed during uninstallation. It is intended to be a standalone application common to multiple versions of Xilinx tools. If it is no longer required, you will need to uninstall separately either from the Start Menu program group entry 'Uninstall DocNav' or through the corresponding entry in the 'Uninstall or change a program' control panel option (for Windows).

#### **Uninstalling Xilinx Information Center**

Xilinx Information Center will not be removed during uninstallation. It is intended to be a standalone application common to multiple versions of Xilinx tools. If it is no longer required, you will need to uninstall separately through the corresponding entry in the 'Uninstall or change a program' control panel option (for Windows).

#### **Uninstalling on Microsoft Windows**

To uninstall the Vivado Design Suite tool product, launch the uninstaller from the launcher menu: select **Applications > Xilinx Design Tools > Vivado 2016.4 > Uninstall**.

#### **Uninstalling on Linux**

To uninstall any Xilinx product, select the Uninstall item from that product's Start Menu folder. For instance, to uninstall Vivado Design Suite: Edition, select **Start > All Programs > Xilinx Design Tools > Vivado 2016.4 > Uninstall**.

If you do not have a program group entry, use the command line option to uninstall: <install\_path>\.xinstall\Vivado\_2016.4\ xsetup.exe -Uninstall

Alternatively, use the corresponding entry in the Uninstall or change a program control panel option (for Windows).

## WebTalk

The WebTalk feature helps Xilinx® understand how you use Xilinx FPGA devices, software, and intellectual property (IP). The information collected and transmitted by WebTalk allows Xilinx to improve the features most important to you as part of our ongoing effort to provide products that meet your current and future needs. When enabled, WebTalk provides information on your use of the Vivado Design Suite tools, SDK, and Petalinux.

## WebTalk Participation

Your participation in WebTalk is voluntary except when a paid license is not found.

In these cases, WebTalk data collection and transmission always occurs, regardless of your preference settings. For all other cases, data is not transmitted if you disable WebTalk.

The following table summarizes WebTalk behavior for data transmission to Xilinx from your post-route design, based on your Xilinx license, WebTalk install preference, and user preference settings.

Table 4-1: WebTalk Behavior for Bitstream Generation or Route Design Flow

| License         | WebTalk Install<br>Preference Selected<br>as "Enabled" | WebTalk User<br>Preference<br>Selected as<br>"Enabled" | Send WebTalk Data to<br>Xilinx |

|-----------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------|

| WebPACK         | X                                                      | Х                                                      | Yes                            |

| Edition License | No                                                     | Х                                                      | No                             |

| Edition License | Yes                                                    | No                                                     | No                             |

| Edition License | Yes                                                    | Yes                                                    | Yes                            |

**Note:** If the device is a WebPACK device, the Tools first look for a WebPACK license.

## Setting WebTalk Install Preference

You can enable or disable WebTalk globally during or after installation as described below. During installation you can enable or disable WebTalk installation options by checking or unchecking the Enable WebTalk to send software, IP and device usage statistics to Xilinx (Always enabled for WebPACK license) checkbox.

Figure 4-1: WebTalk Install Options

You can enable or disable WebTalk installation options using the Tcl command config\_webtalk:

config\_webtalk -install on off

- on turns WebTalk on for the installation.

- off turns WebTalk off for the installation.

Install settings are saved in the following location:

- Windows 7 and 10: <install dir>/vivado/data/webtalk/webtalksettings

- **Linux**: <install dir>/vivado/data/webtalk/webtalksettings

**Note:** You need administrator privileges to write to the install location.

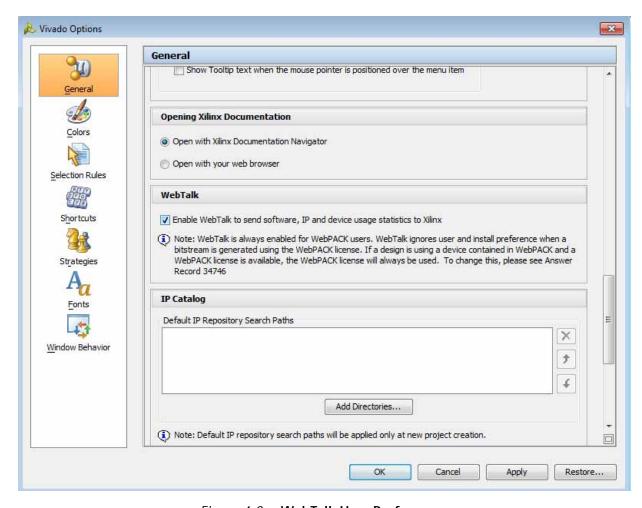

## Setting WebTalk User Preferences

You can enable or disable WebTalk user options by selecting **Tools > Options > General** as shown below.

Figure 4-2: WebTalk User Preferences

After installation, you can enable or disable WebTalk user options using the config\_webtalk Tcl command:

config\_webtalk -user on off

- on turns WebTalk on for the current user.

- off turns WebTalk off for the current user.

User settings are saved in the following location:

Windows 10 or earlier:

```

%APPDATA%\Xilinx\Common\<version>\webtalk

where:

%APPDATA% is:

C:\Users\<user>\AppData\Roaming

Linux:

%APPDATA%/.Xilinx/Common/<version>/webtalk

where:

%APPDATA% is:

/home/<user>

```

## Checking WebTalk Install and User Preferences

You can also use the config\_webtalk Tcl command to check the current status of WebTalk settings. The command line option -info reports the values for the install setting and the user setting:

```

config webtalk -info

```

## Types of Data Collected

WebTalk does not collect your design netlist or any other proprietary information that can be used to reverse engineer your design. The data Xilinx collects through WebTalk includes:

- Software version

- Platform information (for example, operating system, speed and number of processors, and main memory)

- Unique project ID

- · Authorization code

- Date of generation

- Targeted device and family information

For more information on the type of data that is collected, see the Xilinx Design Tools WebTalk web page [Ref 17]. To see the specific WebTalk data collected for your design, open the usage\_statistics\_webtalk.xml file in the project directory. You can also open the usage\_statistics\_webtalk.html file for easy viewing of the data transmitted to Xilinx. Additionally, additional data collection files for sub-flows in the Xilinx tools are also generated which include:

- usage\_statistics\_ext\_xsim.xml

- usage\_statistices\_ext\_labtools.xml

- usage\_statistics\_ext\_sdk.xml

- usage\_statistics\_ext\_petalinux.xml (along with corresponding html files)

#### **Transmission of Data**

WebTalk is invoked after bitstream or route design compilation. WebTalk bundles the collected data in an usage\_statistics\_webtalk.xml file and sends this file to Xilinx by https (hypertext transfer protocol secure) post. Every new compilation for a given design overwrites the previous usage\_statistics\_webtalk.xml file. WebTalk also writes an HTML file equivalent usage\_statistics\_webtalk.html file for easy viewing of the data transmitted to Xilinx. WebTalk also writes to the vivado.log (or runme.log) file that contains additional information about whether the file was successfully transmitted to Xilinx.

## Obtaining and Managing a License

The Xilinx® Product Licensing site is an online service for licensing and administering evaluation and full copies of Xilinx design tools and intellectual property (IP) products. This chapter describes the FLEXnet license generation functionality of the Product Licensing Site.

## **Licensing Overview**

#### Two Product Licensing Methodologies

There are now two ways in which Xilinx enforces the Xilinx End-User License Agreement at run time in the Xilinx design tools.

- Certificate-Based Licenses: This is the license enforcement method Xilinx introduced for the ISE® Design Suite in the ISE 11.1 release. A certificate, commonly referred to as a "license file (.lic)" is issued from the Xilinx Product Licensing Site. The certificate is matched to a given machine, server or licensing dongle using your entering host-id which uniquely identifies the machine. This license certificate must remain present on the machine and in the license search path, because the Vivado tools need access to this file to check for a valid license feature during run time.

- Activation Licenses: Instead of requiring a file to be present to authorize a machine, Activation uses a trusted area on the client or servers hard-drive to store the authorization credentials. Most new Vivado tools licenses purchased after April, 2014 utilize a licensing technology referred to as Activation-based licensing. This trusted storage area should be automatically installed and initialized on Windows operating systems if Vivado was installed with Administrative privileges. If not, or if using Linux, then the trusted storage area must be installed//initialized prior to any other Activation licensing activities. See either Certificate-Based Node Locked License or Activation-Based Floating License. When the Vivado tools look for a license feature, they are allowed to run if this trusted storage area contains the proper authorization. Because activation-based licenses do not use a license file, they will not work with USB license dongles.

**Note:** Flex-ID Dongle licensing for Xilinx Software is supported only on Windows platforms.

#### **Certificate Licensing Terminology**

- Host ID: An identifier, placed within certificate licenses, which binds the license to the computer using this identifier. Typical identifiers are: Hard-drive volume ID, Ethernet port MAC address, or USB Dongle ID.

- **Node-Locked License**: A node-locked license allows for the use of a single seat of a product entitlement on a specific machine.

- Floating License: A floating license resides on a network server and enables applications to check out a license when they are invoked. At any one time, the number of licenses for simultaneous users is restricted to the number of license seats purchased.

- **License Rehosting**: The act of changing the host ID of a generated license due to machine hardware changes, hard-drive failure or the moving of a license from one machine to another.

- **License Deletion**: The act of removing a license from a machine, and having the entitlement placed back into the Xilinx Product Licensing Account.

- **Affidavit of Destruction**: A click through agreement by which you certify that the license file (.lic) for a rehosted or deleted license will be destroyed and no longer used.

#### **Activation Licensing Terminology**

- **Client License**: A client license allows for the use of a single seat of a product entitlement on a specific machine. This is the activation-based equivalent of a certificate-based node-locked license.

- Server License: A server license is the activation-based equivalent of a

certificate-based floating license. A server license resides on a network server and

enables applications to check out a license when they are invoked. At any one time, the

number of licenses for simultaneous users is restricted to the number of license seats

purchased.

- **Trusted Storage**: The area where activation license host information and authorizations are stored.

- Request Creation: Activation licensing is based upon a request/fulfillment system. A request for a new license must first be recorded into trusted storage. This is done automatically by the Vivado License Manager whenever you use the Connect Now or Save Link As Button in Obtain License screen or by using similar command-line arguments for the xlicsrvrmgr tool, required for setting up a floating Activation license. After a request identifier is created, it is sent to the Xilinx Product Licensing Site along with the host information. When a license is generated on the Licensing Site, a fulfillment XML file is created with this same request identifier. When the activation fulfillment XML file is loaded into trusted storage, activation will be successful only if the request identifier on the fulfillment matches the one stored in trusted storage.

After the license is activated, the request becomes inactive and a new request can be made for additional licenses.

• Return License: With activation, license rehosting, license deletion and affidavits of destruction are no longer necessary. Activation features a methodology by which you can initiate a return of a license to Xilinx from the client or server machine. When the return request is made, the license is disabled on the local machine, and a return request is sent to the Xilinx Product Licensing Site. After processed, the return request causes an entitlement to be placed back in your Product Licensing Account, and a message is sent to trusted storage to remove the returned license from the machine.

#### **License Compatibility**

The Vivado 2014.1 and later releases recognize both certificate and activation-based licenses. If the license versions and dates are valid for the tool version being used, it does not matter whether the license is certificate or activation-based.

#### **Differences with Activation Licenses**

To authorize the trusted storage area, activation records need to be sent from the Xilinx Product Licensing Site to the client or server machine. Currently, this is done by using XML files with encrypted authorizations. When you generate an Activation license, you receive an XML file by email, much like you might have received a certificate file (.lic) in the past. The difference is that certificate lic files need to be continually accessed by the Xilinx software, and so must be retained and in a valid license search path. The XML activation record is used to load the authorization into the trusted storage area. After the authorization has been loaded, the XML activation record is no longer needed.

To generate licenses based on activation entitlements, a request for a license must first be made into the client or server computer's trusted storage area. For client (node-locked) activation license requests, Vivado License Manager or the command-line utility xlicclientmgr must be used. For server (floating) license requests, the command-line utility xlicsrvrmgr must be used. For more information on the xlicclientmgr or xlicsrvrmgr utilities, see the Xlicclientmgr Command-Line Utility or Xlicsrvrmgr Command-Line Utility section.

After this request is processed, a URL to the Xilinx Product Licensing Site will be generated and will contain the id of the request along with specific machine identification information of the Xilinx Product Licensing Site. This URL should be placed into a web browser, and if activation entitlements exist, they are accessible in the Activation-Based Licenses section of the Create New Licenses tab of the Xilinx Product Licensing Site.

If you enter the Xilinx Product Licensing Site directly or through older Xilinx license managers, the machine identification necessary to generate an activation-based license will not be present. In this case, the Activation-Based Licenses section of the website will be inactive, and only certificate licenses will be available for generation.

## Generating/Installing/Managing Activation-Based Licenses

#### Activation-Based Node-Locked License

#### Getting Started

#### **Activation Exceptions**

If you meet any of the following conditions, you are not a candidate to use Activation for your licensing solution. Please contact Xilinx Development System Customer Service for an alternate licensing solution.

- License dongles are not supported by Xilinx's activation licensing. If you wish to utilize your existing dongles, only certificate-based licenses should be used.

- If you are creating a license for a secured area where files are not allowed to be exported, certificate-based licenses which support the legacy host ID structure are a better fit.

#### **Initializing Trusted Storage**

**Windows**: If you are using Windows and installed with Administrative rights, the trusted storage area should have been installed and initialized automatically. If trusted Storage has not been initialized, perform the following steps:

- 1. Open a command window in Administrative mode by typing cmd in the Windows Start Menu search box, right clicking on the cmd.exe icon and choosing **Run as administrator**.

- 2. Run <Vivado Tools

Directory>\Vivado\2016.4\bin\unwrapped\win64.o\installanchorserv

ice exe

**Linux**: Trusted storage must be manually installed and initialized on Linux by performing the following steps:

- 1. With root or sudo access, open a command-line shell.

- 2. Run <Vivado Tools

Directory>/Vivado/2016.4/bin/unwrapped/lin64.o/install\_fnp.sh

#### Requesting a Node-Locked License From Your Machine

In order to generate node-locked (client) activation-based licenses, you must use either the Vivado License Manager GUI, or the xlicclientmgr command-line executable to access

the Xilinx License Management site. Failure to use one of these tools, and going to the Xilinx License Manage website directly in a browser will result in all activation-based licenses being non-selectable. The following instructions are for using the Vivado License Manager GUI to access the Xilinx License Management website.

- 1. Launch Vivado License Manager

- For Windows 7 and 10: Select Start > All Programs > Xilinx Design Tools > Vivado

2016.4 > Manage Xilinx Licenses.

- b. For Windows 8.1: Run the Manage Xilinx Licenses app from the full listing of Apps on your Start screen.

- c. For Linux: Type vlm in a command-line shell.

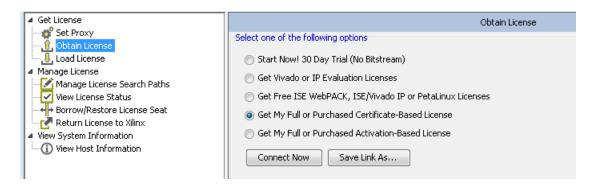

- 2. In the left window frame select **Obtain License** which is located under the **Get License** section.

- 3. In the main window frame, select either Get Free Licenses, Start 30-Day Evaluation or Get My Purchased Licenses (not Start now) and click the **Connect Now** button (Figure 5-1).

- 4. Your default web browser should now open with a Xilinx login screen.

**Note:** If your machine is not currently connected to the internet or is having proxy issues, please click the Save Link As button. This will allow you to save the required information into an HTML file. This HTML file can be opened by a web browser on any machine that is connected to the internet.

Figure 5-1: Obtain License

## Generating a Node-Locked Activation License on the Xilinx License Management Website

Whether Vivado License Manager launched your web browser, or you manually launched a browser with the HTML file provided by the **Save Link As** command, you should now be at the **Sign In To The Xilinx Licensing Site** screen.

- 1. Use your Xilinx.com username and password to sign in and confirm your address information.

- 2. Select the licensing account which contains your licenses from the **Account** drop-down menu, if necessary.

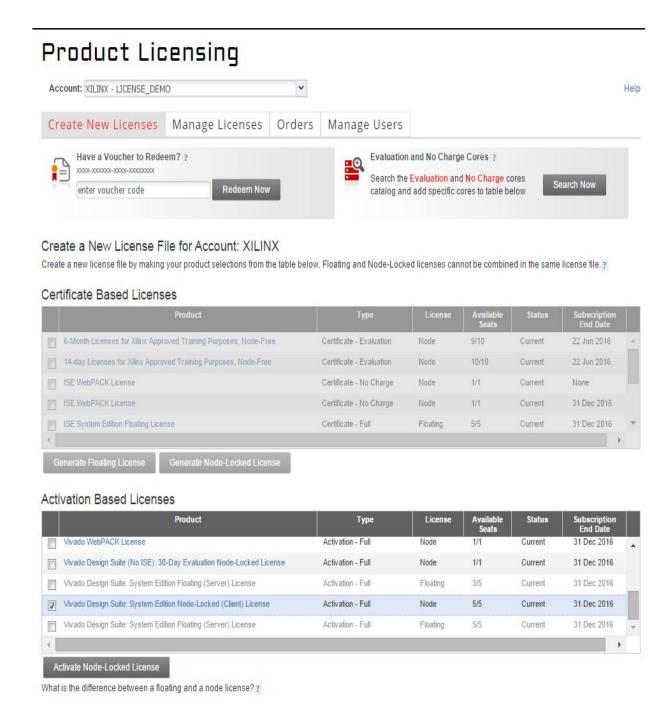

- 3. Scroll down, if necessary, to the **Activation Based Licenses** section of the webpage (Figure 5-2).

- 4. Select the Activation licenses of your choice.

**Note:** Once you check an entitlement in either the "Activation Based Licenses" area or the "Certificate Based Licenses" area, the other area will automatically become inactive. Activation and Certificate licenses must be generated separately, although multiple licenses of the same license type may be selected. To reactivate both areas, uncheck all licenses in that area.

Figure 5-2: Create New Node-Locked (Client) Activation License

- 5. Select the **Activate Node-Locked License** button.

- 6. On the pop-up dialogs confirm each page of information is correct by pressing the **Next** buttons until the license generation begins.

### Installing a Node-Locked Activation License On Your Machine

#### **One-Step Activation Method**

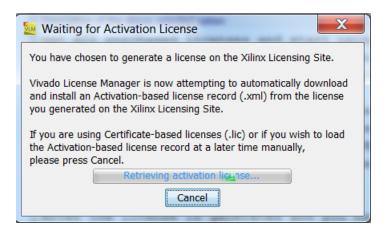

Beginning in Vivado 2014.3, pressing the **Connect Now** button in the Vivado License Manager causes the VLM to go into polling mode. After a two-minute delay, VLM shows the following dialog box (Figure 5-3).

Figure 5-3: Waiting for Activation License Dialog

If your internet and proxy connects are correct, Vivado License Manager detects the existence of your Xilinx\_License.xml file soon after you press the final **Next** button on the license generation dialogs in step 3. VLM will then automatically download and install the .xml file for you, immediately activating your license and presenting you with a **Success** dialog. You may view your installed license in the **View License Status** page under the **Manage License** heading in the left most window frame.

Your Xilinx\_License.xml file will be e-mailed to you for your records, but no further action with this file is required.

#### Manual Method

The One-Step Activation polling stops after about 15 minutes. If it has taken you longer than this to generate your license file, if you manually cancelled the polling, or if you accessed the Xilinx License Management Website on a different machine because yours was not connected to the internet, you will need to utilize the manual method for loading your license onto your machine.

- 1. Save the activation fulfillment file (.xml) attached to thee-mail to a temporary directory on your local system.

- 2. Run the Vivado License Manager.

- 3. On the left hand frame of VLM, choose Load License under the Get License section

- 4. Click the Activate License button.

- 5. Browse to your activation fulfillment file (Xilinx\_License.xml) and click **Open**.

- 6. This loads your activation fulfillment into trusted storage, where it is verified and the machine authorized for the corresponding tools.

# **Activation-Based Floating License**

### Getting Started

#### **Activation Exceptions**

If you meet any of the following conditions, you are not a candidate to use Activation for your floating license server. Contact Xilinx Development System Customer Service for an alternate licensing solution.

- Triad (triple-redundant) floating license server configurations are not supported by Xilinx's activation licensing. Certificate-based licenses must be used with triple-redundant floating servers.

- SUN-OS based activation floating license servers are not supported by Xilinx.

Certificate-based licenses do still support the SUN-OS.

- If you are creating a license for a secured area where files are not allowed to be exported, certificate-based licenses which support the legacy host ID structure are a better fit.

#### **Initializing Trusted Storage**

Trusted storage must be manually installed and initialized on your floating license server. All the files required to install, initialize and serve floating licenses are available in the platform specific ZIP files located on the Xilinx Download Center in the License Management Tools section of the current Vivado release.

#### Windows:

- 1. Extract the License Management Tools archive onto your disk. A permanent location is suggested as you will need the lmgrd and xilinxd files in this archive to actually serve your licenses.

- 2. Open a command window in Administrative mode by typing cmd in the Windows Start Menu search box, right clicking on the cmd.exe button and choosing Run as administrator.

- Run < Server Tools Directory>\<Tools Version>\win64.o\

installanchorservice.exe.

#### Linux:

Trusted storage must be manually installed and initialized on Linux by performing the following steps.

- 1. Extract the License Management Tools archive onto your disk. A permanent location is suggested as you will need the lmgrd and xilinxd files in this archive to actually serve your licenses.

- 2. With root or sudo access, open a command-line shell.

- Run <Server Tool Directory>/<Tools Version>/lnx64.o/install\_fnp.sh.

## Requesting a Floating License From Your License Server Machine

To generate floating (server) activation-based licenses, you must use the xlicsrvrmgr command-line executable run from your server machine to access the Xilinx License Management site. Failure to use this tool and going to the Xilinx License Manage website directly in a browser results in all activation-based licenses being non-selectable. To generate a floating license from an entitlement in your Xilinx License Management Account, do the following.

From your server tools directory (above), run xlicsrvrmgr -cr <outputdir>/server\_req.xml.

This creates a license request into the trusted storage area which causes XML and HTML files to be output containing your server's Host ID information.

2. Open the server\_req.html file in the browser of your choice.

This.html file effectively contains a URL with the Host ID information that activation requires to lock a floating license to your server.

3. Your web browser should now open with a Xilinx login screen.

**Note:** If your machine is not currently connected to the internet or is having proxy issues you may take this HTML to a web browser on any machine that is connected to the internet.

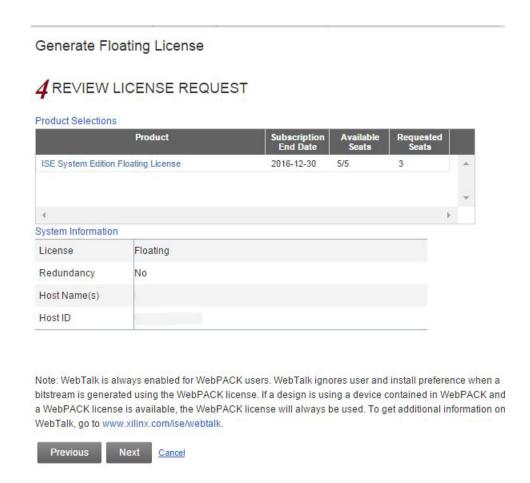

# Generating a Floating Activation License on the Xilinx License Management Website

- 1. From the **Xilinx Licensing Site** login screen, enter your Xilinx.com username and password to sign in and confirm your address information.

- 2. Select the licensing account which contains your licenses from the **Account** drop-down menu, if necessary.

- 3. Scroll down, if necessary, to the Activation Based Licenses section of the webpage (Figure 5-4.).

**Note:** After you check an entitlement in either the "Activation Based Licenses" area or the "Certificate Based Licenses" area, the other area will automatically become inactive. Activation and Certificate licenses must be generated separately, although multiple licenses of the same license type may be selected. To reactivate both areas, uncheck all licenses in that area.

4. Select the Activation licenses of your choice and click the **Activate Floating License** button..

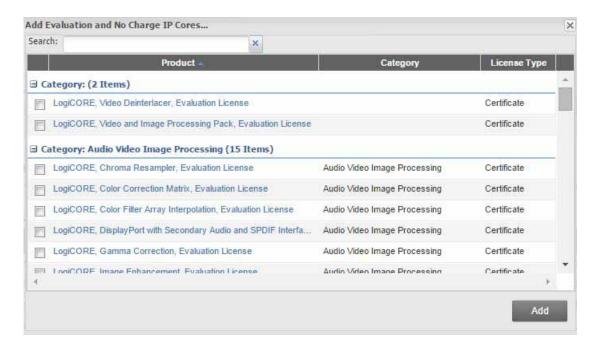

#### Activation Based Licenses

Figure 5-4: Create New Floating (Server) Activation License

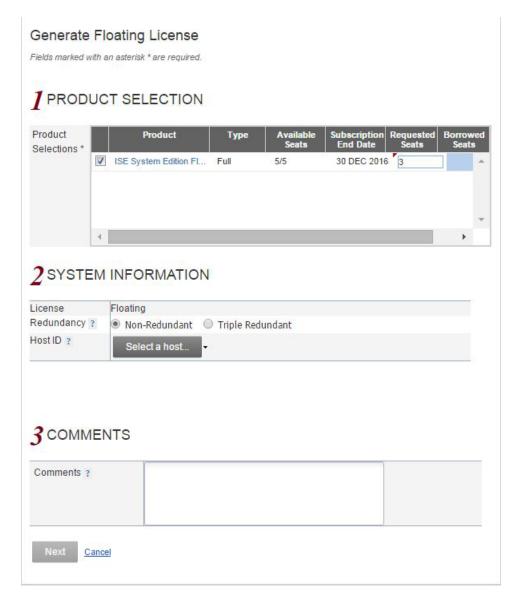

5. A dialog will open where you can specify the number of license seats from your entitlement that you wish to assign to this server in the **Requested Seats** field. The default is 0, but a non-zero number is required to continue.

**Note:** If your Vivado subscription was purchased or renewed after the launch of Vivado 2016.4, a borrow feature is enabled on your floating license. For more information on the borrow feature, see Borrowing Licenses below.

6. If the borrow feature is enabled on your licenses, you will see an additional field to the right called **Borrowed Seats** (Figure 5-5). Here you will specify the number of requested seats that are eligible to be borrowed. The default is 0, which means no seats will be available for a user to borrow and you may enter any number up to the number of requested seats in the previous column

Figure 5-5: Specifying Floating and Borrowable Seats

7. After inputting the requested and borrowed seats, press the **Next** buttons until the license generation begins.

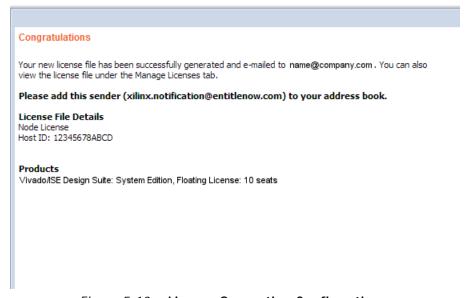

8. Your Xilinx\_License.xml file will be e-mailed to you. You will need this file to finish installing and serving your license

### Installing and Serving a Floating Activation License File On Your Machine

After you receive your Xilinx\_License.xml file, please save it off to a local directory. The following steps instructs you on how to install the license, and how to serve it on your floating server.

- From your server tools directory (above), run xlicsrvrmgr -p <response filename i.e.(xilinx\_license)>.xml.

- 2. This will store the license information into your trusted storage area.

- 3. Verify that the license is installed by viewing your trusted storage area: xlicsrvrmgr –v "format=long".

#### **License File Requirements**

Before completing the following steps, there are some things that need to be understood about Flexera's Imgrd license server utility. LMGRD and other familiar FLEX server utilities are still used for serving and managing activation-based floating licenses. While licenses in trusted storage are automatically found and served by Imgrd, Imgrd requires that a license file (.lic) be specified. For activation-based floating licenses, the license file is just needed to specify certain network basics.

```

SERVER <host_name> <host_id> <port> (Xilinx's default port=2100)

USE_SERVER

VENDOR xilinxd

```

If you already going to serve an existing Xilinx license file, like for Xilinx IP or ISE Design Suite, there is nothing further needed. If you are only going to be serving the activation-based licenses on the server, then you will need to create a basic license file (.lic) with the information listed above.

- 4. Ensure that a license file .(lic) meeting the minimum criteria above is present.

- 5. Run Imgrd to serve your licenses.

#### Windows:

<Server Tool directory>\win64.o\lmgrd -c <path\_to\_license>\license filename>.lic -l

<path to license>\<log filename>.log

#### Linux:

**Note:** For Linux users - Imgrd command requires library paths to be set. Xilinx provides a shell script to set this for you, Imgrd.sh. If you use the Imgrd command-line tool alone, you are likely to see an error

<Server Tool directory>/lnx64.o/lmgrd.sh -c

<path\_to\_license>/<license file>.lic -l <path\_to\_license>/<log

filename>1.log

**IMPORTANT:** If you are using a Windows 8.1 machine as your floating server or if you wish to support borrowing from your server, you must use the 11.13.1.3 version of lmgrd and xilinxd found in the Vivado 2016.x Server Tools download. Re-initialization of trusted storage will be required when moving from the previous 11.11.0 lmgrd and xilinxd to 11.13.1.3. If you do not wish to enable borrow and are not using a Windows 8.1 machine, you may continue to use your existing 11.11.0 lmgrd and xilinxd.

# **Borrowing Licenses**

Beginning with Vivado 2015.1, Xilinx introduces the ability to borrow activation-based licenses from a compatible server to the trusted storage of your local machine. This means that, for a period of time specified during the borrow request process, the license seat count on the server is decremented by 1, and the license is activated in the local trusted storage of the borrow client. This allows the borrow client to then have an effective node-locked Activation license, which can be taken off network, etc. At the end of the borrow time period, the license will automatically deactivate on the client's machine, and will be restored to the floating server. Vivado also gives you the ability to restore a license to the floating server early, if the borrowed seat is no longer needed.

**Note:** Borrowing licenses from a virtual machine (VM) to a physical machine is currently not supported. For more information, see <u>Answer Record 63727</u>

#### Is The Server License Borrowable?

Existing Vivado floating activation-based licenses issued prior to April, 2015 cannot be borrowed. When your Vivado subscription comes up for renewal after April, 2015, new floating activation-based entitlements from that renewal will be borrowable. However, the decision to allow borrow or not, or how many seats of a total entitlement are borrowable rests with administrator generating the license and is made during the license generation process.

From a client, it is straightforward to determine if a license is borrowable using Vivado License Manager, and this is discussed in the Borrowing Licenses section.

# Borrowing a License

At this time, it is only possible to borrow from an activation-based floating server to a node-locked client. The following steps cover how to borrow a license using Vivado License Manager.

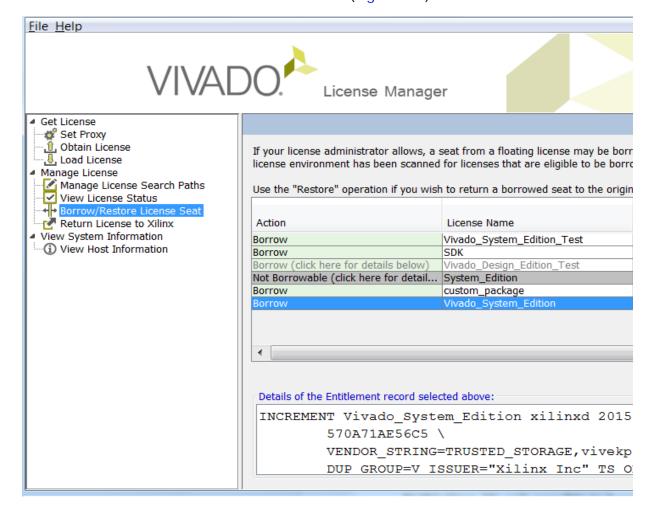

1. Open VLM and select **Borrow/Restore License Seat** which is located under the **Manage License** section in the left-hand window pane.

2. In the main area, all floating servers on your network will be queried to see if they contain borrowable activation-based licenses (Figure 5-6).

Figure 5-6: Borrow/Restore License Seat

- 3. Select the license you wish to borrow and click the **Borrow/Restore** button.

- In Figure 5-6, there is a license row where the text is gray, but the background is the normal coloration. This indicates that this license is allowed to be borrowed, but cannot be borrowed at the moment. In this case, it is because all borrowable seats have already been borrowed. If the background of a row is gray, as in the Figure, this is an indication that the license cannot ever be borrowed. Common causes for this are older server Flex software (11.11.0 or 11.6.0 11.13.1.3 is required), or the license itself is not setup for borrow (Example: A 2014.x era floating license.)

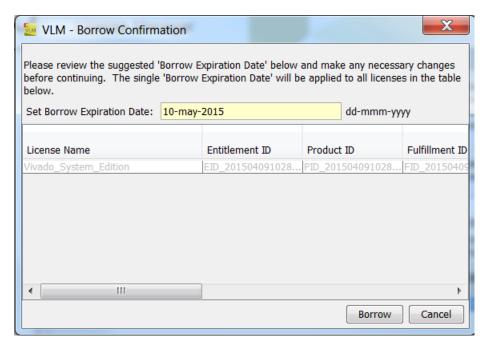

- 4. A Borrow Confirmation screen will appear, this is where you will need to specify how long you wish to borrow the license. This is done in the **Set Borrow Expiration Date** dialog box highlighted in Yellow (Figure 5-7).

The default borrow date is set 30-days from the current date, or at the expiration date of the server license, whichever comes first. You will not be allowed to enter a borrow end-date that is greater than the license expiration date.

Figure 5-7: Set Borrow Time-Limit

5. Click the **Borrow** button on the confirmation screen and the license will be decremented from the server and added to the client's local trusted storage.

The screen will refresh, and you will see that a license seat has now been added to the list with a value of **Restore** in the first column.

# Restoring a Borrowed License

If you do not wish to keep the borrowed license for the entire time you specified, you may restore it to your local license server.

- 1. Open VLM and select **Borrow/Restore License Seat** which is located under the **Manage License** section in the left-hand window pane.

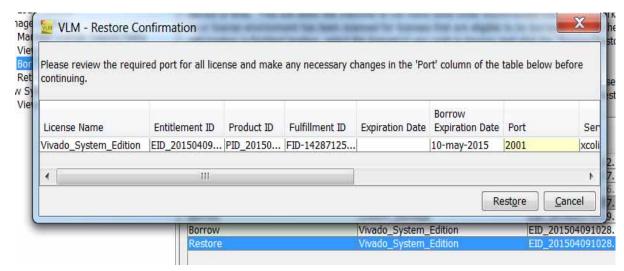

- 2. Select the license you wish to restore. Eligible licenses will have **Restore** listed next to them in the Action column (Figure 5-8).

- 3. Click the **Borrow/Restore** button and the confirmation dialog box appears.

- 4. Specify the Port that the floating license server is using.

Unfortunately, Vivado License Manager cannot detect which port the license server is using. VLM prepopulates the default Xilinx license server port, but if your server is using something different, it needs to be specified. Specifying an incorrect port will disable

the license on the local client machine, but the seat will not be available to others until the original borrow time period expires.

Figure 5-8: Set Restore Port

5. Click the **Restore** button and the license will be rendered inactive on the client machine, and the license count on the server will be incremented by one.

# **Returning Licenses**

For information on returning certificate-based licenses from your machine to Xilinx, please see Modifying Licenses. Activation-based licenses can returned to Xilinx through either Vivado License Manager (Node-Locked) or the xlicsrvmrgr command line utility (Floating).

# Returning Node-Locked (Client) Licenses

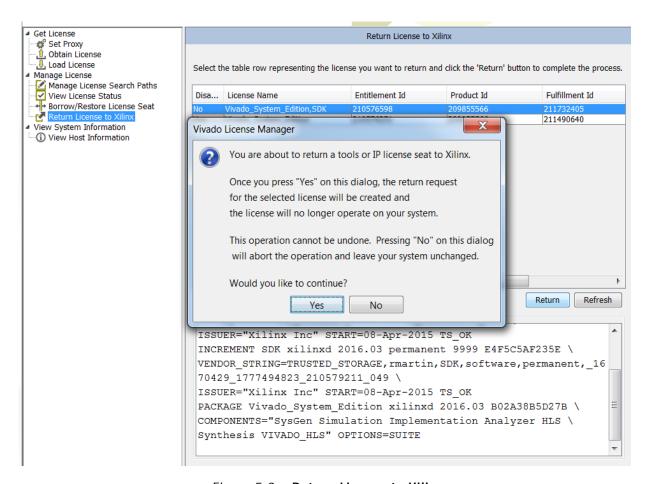

- 1. Open the Vivado License Manager.

- 2. In the left-hand window pane click **Return License to Xilinx** which is located under the Manage License section.

- 3. In the main area of the screen, a list of the node-locked licenses currently in your trusted storage area will appear.

- If **No** appears in the Disabled column, this means that license is an active license and is eligible to be returned. If **Yes** appears in the Disabled column, this usually means a return has already been attempted, but not completed (your account has not been credited).

- 4. Select the license you wish to return and verify the contents of the license by looking in the **Details** section at the bottom of the main area.

- 5. Click Return.

6. An important confirmation dialog appears (Figure 5-9).

Figure 5-9: Return License to Xilinx

When you attempt to return an Activation license, it is first marked disabled in your trusted storage area, which means it can no longer be used on your machine, before VLM attempts to contact the Xilinx License Management website and place the entitlement back in your account. Since this cannot be undone, it is recommended that you ensure a connection to the internet.

7. Vivado License Manager will contact the Xilinx License Management website and will automatically credit your account with the license return.

# Returning Floating (Server) Licenses

To return a license from a floating license server to Xilinx, you must do so from that server using the xlicsrvrmgr utility

1. Create the return request.

xlicsrvrmgr -cr <return request.xml> -r <fulfillment ID>

Notice how both the –cr (create request) flag AND –r (return request) flag are used. Fulfillment ID can be obtained by running the xlicsrvrmgr –v "format=long" command

2. Send the return request to Xilinx.

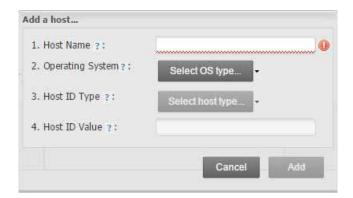

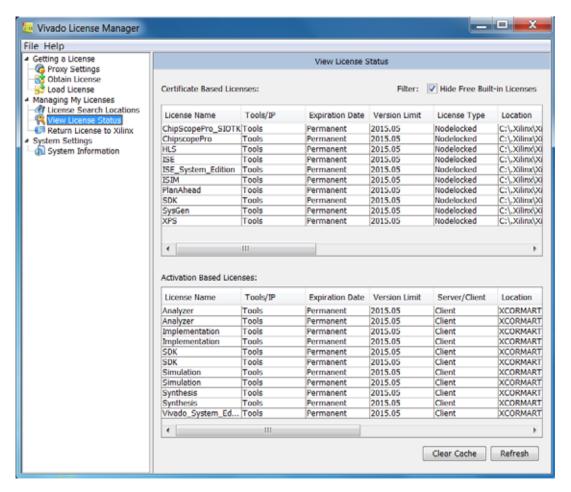

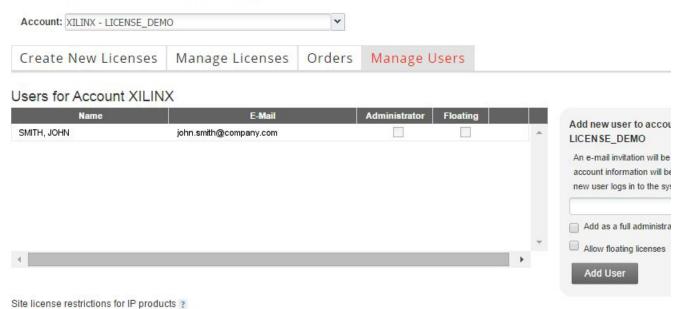

xlicsrvrmgr -returnTransaction "request=<return request.xml>" "response=<response filename.xml>" "proxy=<proxy:port>"