# UltraFast Design Methodology Guide for the Vivado Design Suite

UG949 (v2016.4) November 30, 2016

# **Revision History**

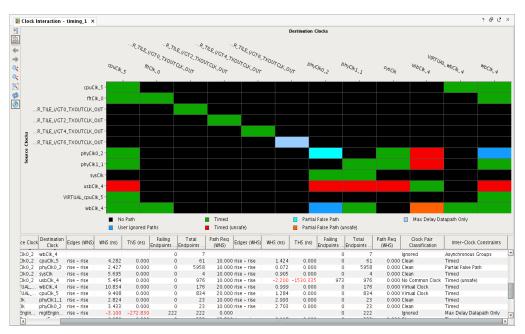

11/30/2016: Released with Vivado® Design Suite 2016.4 without changes from 2016.3.

| Date       | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 11/11/2016 | 2016.3  | Updated Add I/O Components Near the Top Level, updated When and Where to Use a Reset, updated Using DIRECT_ENABLE and DIRECT_RESET, updated Pushing the Logic from the Control Pin to the Data Pin, added information on the Clock Utilization Report in Clock Primitives, updated Clock Multiplexing, updated I/O Timing with MMCM ZHOLD/BUF_IN Compensation, added examples in Single Quad vs. Multi-Quad Interface, updated Controlling the Phase, Frequency, Duty-Cycle, and Jitter of the Clock, updated Using Gated Clocks, added Controlling and Synchronizing Device Startup, added Avoiding Local Clocks, added Clock Domain Crossing, and added information on phase shift in Using a Virtual Clock and Relaxing the Setup Requirement While Keeping Hold Unchanged in Chapter 3, Design Creation. |  |  |  |  |  |

|            |         | Updated Bottom-Up Synthesis Flow in Chapter 4, Implementation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

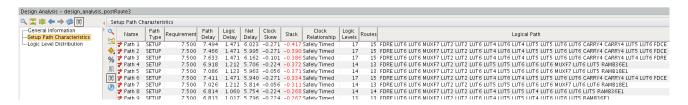

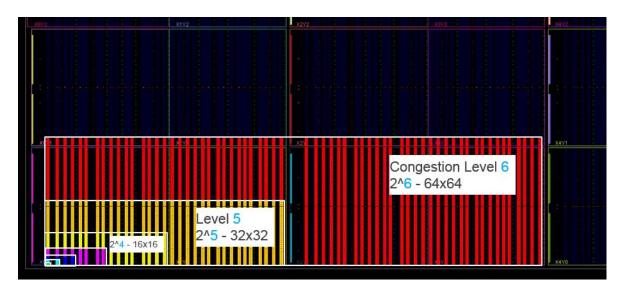

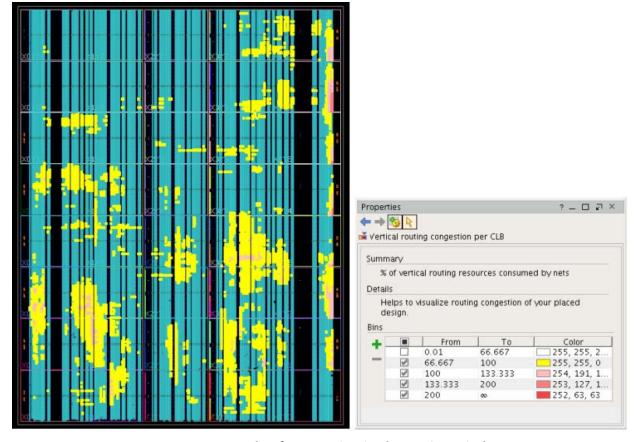

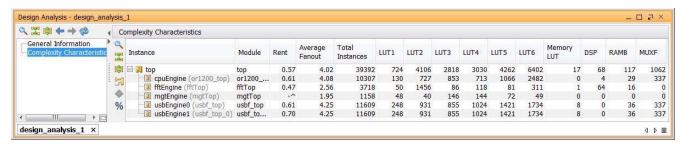

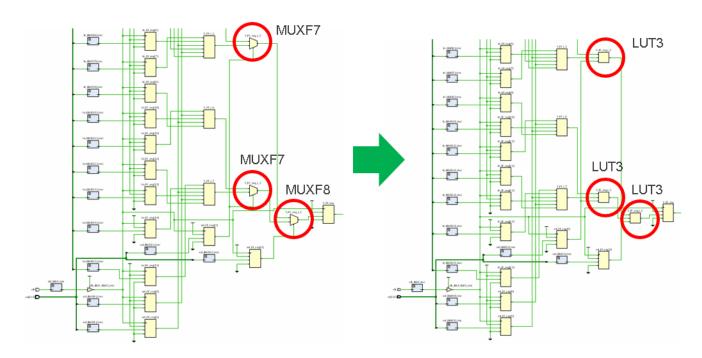

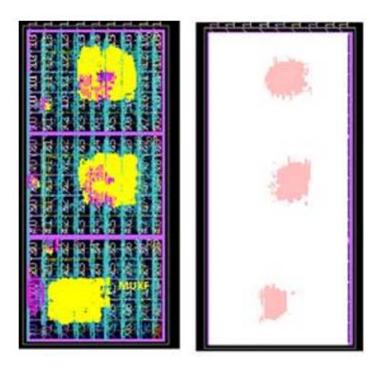

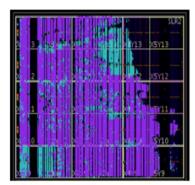

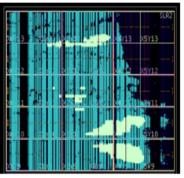

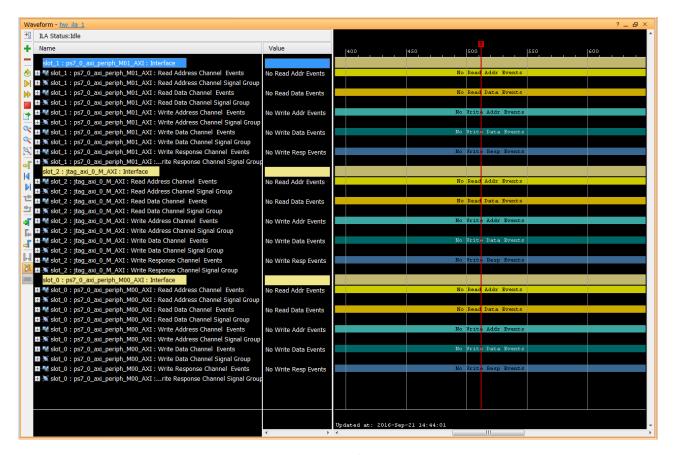

|            |         | Updated Table 5-2, added information on the Check Timing report in Verifying That No Clocks Are Missing, updated Reducing Net Delay, updated Table 5-4, updated Report Design Analysis Congestion Report, added tables for Rent Exponent and Average Fanout in Report Design Analysis Complexity Report, updated Optimizing High Fanout Nets, updated Disable LUT Combining and MUXF Inference, updated Group Critical Logic, updated Debugging Designs in Vivado IP Integrator, added Debugging AXI Interfaces in Vivado Hardware Manager, and added Using In-System IBERT in Chapter 5, Design Closure.                                                                                                                                                                                                    |  |  |  |  |  |

| 06/08/2016 | 2016.2  | Reorganized the Chapter 1, Introduction. Included an overall UltraFast Design Methodology overview.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|            |         | Reorganized content across the entire document and moved tool usage content that was better suited to the Vivado User Guides into those documents. Also removed some content that was duplicated in those guides.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|            |         | Removed Chapter 2, Using the Vivado Design Suite and merged the content with the Vivado Design Suite User Guide: Design Flows Overview (UG892).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|            |         | Moved the Source Management and Revisions Control Recommendations section to the <i>Vivado Design Suite User Guide: Design Flows Overview</i> (UG892).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|            |         | Split the Implementation Chapter 5 into two chapters, Chapter 4, Implementation and Chapter 5, Design Closure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|            |         | Added Advanced Synthesis content to Chapter 4, Implementation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|            |         | Added the latest design analysis and closure features into Chapter 3, Design Creation, Chapter 4, Implementation, and Chapter 5, Design Closure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|            |         | Removed Chapter 6, Configuration and Debug and moved some of the content into Chapter 5, Design Closure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

# **Table of Contents**

| Chapter 1: Introduction                             |

|-----------------------------------------------------|

| About the UltraFast Design Methodology              |

| Understanding UltraFast Design Methodology Concepts |

| Using the Vivado Design Suite                       |

| Accessing Additional Documentation and Training     |

| Chapter 2: Board and Device Planning                |

| Overview of Board and Device Planning 14            |

| PCB Layout Recommendations                          |

| Clock Resource Planning and Assignment              |

| I/O Planning Design Flows                           |

| Designing with SSI Devices                          |

| FPGA Power Aspects and System Dependencies          |

| Configuration                                       |

| Chapter 3: Design Creation                          |

| Overview of Design Creation                         |

| Defining a Good Design Hierarchy 35                 |

| RTL Coding Guidelines                               |

| Clocking Guidelines                                 |

| Clock Domain Crossing                               |

| Working With Intellectual Property (IP)             |

| Working with Constraints                            |

| Chapter 4: Implementation                           |

| Overview of Implementation                          |

| Running Synthesis                                   |

| Moving Past Synthesis                               |

| Implementing the Design                             |

| Chapter 5: Design Closure                           |

| Overview of Design Closure                          |

| Timing Closure                                      |

| Analyzing and Resolving Timing Violations 2        | 201         |

|----------------------------------------------------|-------------|

| Applying Common Timing Closure Techniques          | 225         |

| Power Analysis and Optimization 2                  | 43          |

| Configuration and Debug 2                          | :46         |

| Appendix A: Additional Resources and Legal Notices |             |

| Xilinx Resources                                   | 257         |

| Solution Centers                                   | <u>2</u> 57 |

| Documentation Navigator and Design Hubs            | <u>2</u> 57 |

| References                                         | 258         |

| Training Resources                                 | <b>260</b>  |

| Please Read: Important Legal Notices 2             | <b>261</b>  |

# Introduction

# About the UltraFast Design Methodology

The Xilinx<sup>®</sup> UltraFast<sup>™</sup> design methodology is a set of best practices intended to help streamline the design process for today's All Programmable devices. The size and complexity of these designs require specific steps and design tasks to ensure success at each stage of the design. Following these steps and adhering to the best practices will help you achieve your desired design goals as quickly and efficiently as possible.

Xilinx provides the following resources to help you take advantage of the UltraFast design methodology:

- This guide, which describes the various design tasks, analysis and reporting features, and best practices for design creation and closure.

- UltraFast Design Methodology checklist, which is available in the Xilinx Documentation Navigator and as a standalone spreadsheet. You can use this checklist to identify common mistakes and decision points throughout the design process.

- Methodology-related design rule checks (DRCs) for each design stage, which are available using the report\_methodology Tcl command in the Vivado® Design Suite.

- UltraFast Design Methodology System-Level Design Flow diagram representing the entire Vivado Design Suite design flow, which is available in the Xilinx Documentation Navigator. You can click a design step in the diagram to open related documentation, collateral, and FAQs to hep get you started.

# **Using This Guide**

This guide provides a set of best practices that maximize productivity for both system integration and design implementation. It includes high-level information, design guidelines, and design decision trade-offs for the following topics:

- Chapter 2, Board and Device Planning: Covers decisions and design tasks that Xilinx recommends accomplishing prior to design creation. These include I/O and clock planning, PCB layout considerations, device capacity and throughput assessment, alternate device definition, power estimation, and debugging.

- Chapter 3, Design Creation: Covers the best practices for RTL definition, IP configuration and management, and constraints assignment.

- Chapter 4, Implementation: Covers the options available and best practices for synthesizing and implementing the design.

- Chapter 5, Design Closure: Covers the various design analysis and implementation techniques used to close timing on the design or to reduce power consumption. It also includes considerations for adding debug logic to the design for hardware verification purposes.

This guide includes references to other documents such as the Vivado Design Suite User Guides, Vivado Design Suite Tutorials, and Quick-Take Video Tutorials. This guide is not a replacement for those documents. Xilinx still recommends referring to those documents for detailed information, including descriptions of tool use and design methodology. For a listing of reference documents, see Appendix A, Additional Resources and Legal Notices.

**Note:** This information is designed for use with the Vivado Design Suite, but you can use most of the conceptual information with the ISE® Design Suite as well.

# Using the UltraFast Design Methodology Checklist

To take full advantage of the UltraFast design methodology, use this guide with the UltraFast Design Methodology Checklist. The checklist is available from the Xilinx Documentation Navigator or as a standalone spreadsheet (XTP301).

The questions in the UltraFast Design Methodology Checklist highlight typical areas in which design decisions are likely to have downstream impact and draw attention to issues that are often overlooked or ignored. Each tab in the checklist:

- Targets a specific role within a typical design team.

- Includes common questions and recommended actions to take during each design flow step, including project planning, board and device planning, IP and submodule design, and top-level design closure.

- Includes a Documentation and Training section that lists resources related to the design flow step.

- Provides links to content in this guide or other Xilinx documentation, which offer guidance on addressing the design concerns raised by the questions.

**VIDEO:** For a demonstration of the checklist, see the <u>Vivado Design Suite QuickTake Video:</u> <u>Introducing the UltraFast Design Methodology Checklist.</u>

### Using the UltraFast Design Methodology DRCs

The Vivado Design Suite contains a set of methodology-related DRCs you can run using the report\_methodology Tcl command. This command has rules for each of the following design stages:

- Before synthesis in the elaborated RTL design to validate RTL constructs

- After synthesis to validate the netlist and constraints

- After implementation to validate constraints and timing related concerns.

**RECOMMENDED:** For maximum effect, run the methodology DRCs at each design stage and address any issues prior to moving to the next stage.

For more information on the design methodology DRCs, see this <u>link</u> in the *Vivado Design Suite User Guide*: *Design Analysis and Closure Techniques* (UG906) [Ref 21], and see the <u>report\_methodology</u> Tcl command in the *Vivado Design Suite Tcl Command Reference Guide* (UG835) [Ref 13].

# Using the UltraFast Design Methodology System-Level Design Flow Diagram

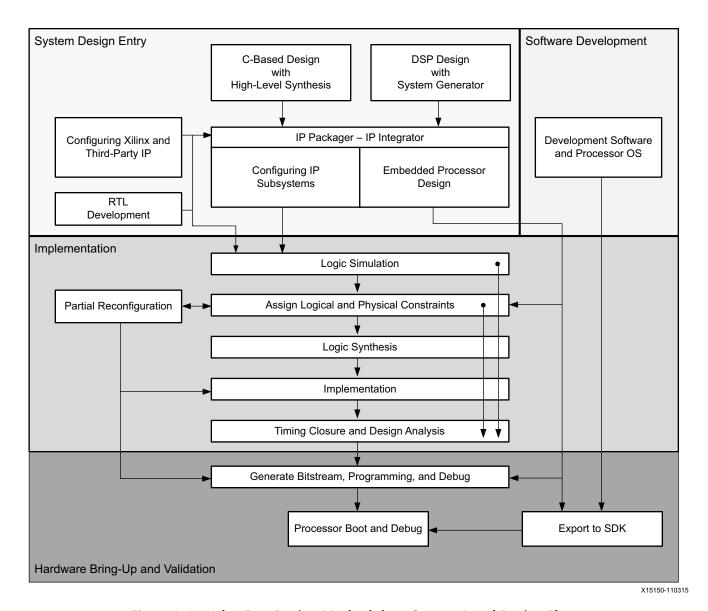

The following figure shows the various design steps and features included in the Vivado Design Suite. From the Xilinx Documentation Navigator, you can access an interactive version of this graphic in which you can click each step for links to related resources.

Figure 1-1: UltraFast Design Methodology System-Level Design Flow

# **Understanding UltraFast Design Methodology Concepts**

It is important to take the correct approach from the start of your design and to pay attention to design goals from the early stages, including RTL, clock, pin, and PCB planning. Properly defining and validating the design at each design stage helps alleviate timing closure, routing closure, and power usage issues during subsequent stages of implementation.

### Maximizing Impact Early in the Development Cycle

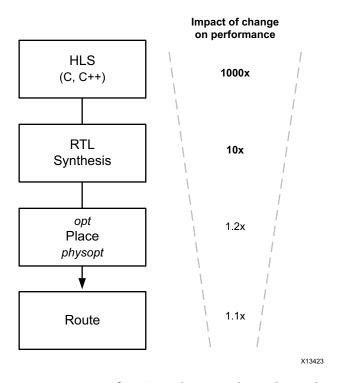

As shown in the following figure, early stages in the design flow (C, C++, and RTL synthesis) have a much higher impact on design performance, density, and power than the later implementation stages. Therefore, if the design does not meet timing goals, Xilinx recommends that you revisit the synthesis stage, including HDL and constraints, rather than iterating for a solution in the implementation stages only.

Figure 1-2: Impact of Design Changes Throughout the Flow

# Validating at Each Design Stage

The UltraFast design methodology emphasizes the importance of monitoring design budgets, such as area, power, and timing, and correcting the design from early stages as follows:

- Create optimal RTL constructs with Xilinx templates, and validate your RTL with methodology DRCs prior to synthesis.

- Because the Vivado tools use timing-driven algorithms throughout, the design must be properly constrained from the beginning of the design flow.

- Perform timing analysis after synthesis.

- To specify correct timing, you must analyze the relationship between each master clock and related generated clocks in the design. In the Vivado tools, each clock interaction is timed unless explicitly declared as an asynchronous or false path.

- Meet timing using the right constraints before proceeding to the next design stage.

- You can accelerate overall timing and implementation convergence by following this recommendation and by using the interactive analysis environment of the Vivado Design Suite.

**TIP:** You can achieve further acceleration by combining these recommendations with the HDL design guidelines in this guide.

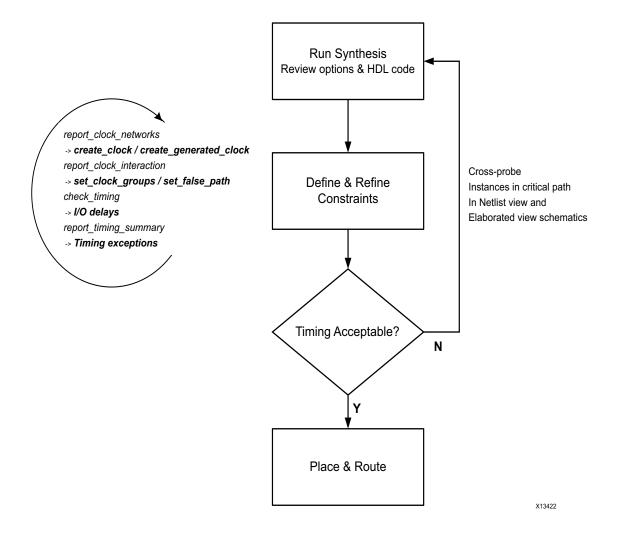

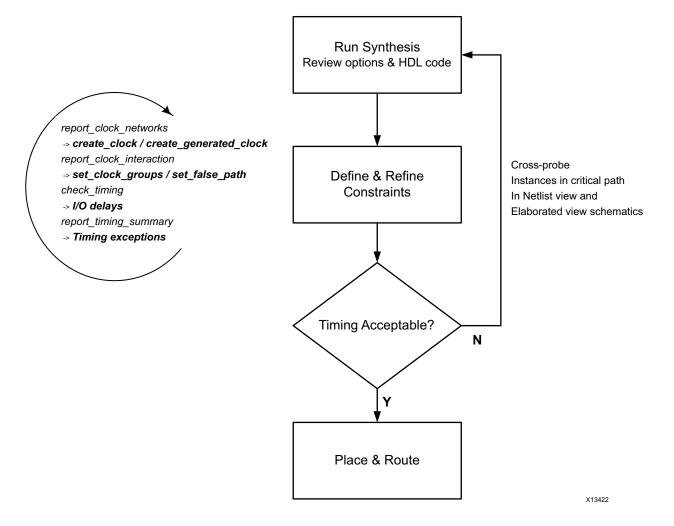

The following figure shows this recommended design methodology.

Figure 1-3: Design Methodology for Rapid Convergence

Synthesis is considered complete when the design goals are met with a positive margin or a relatively small negative timing margin. For example, if post-synthesis timing is not met, placement and routing results are not likely to meet timing. However, you can still go ahead with the rest of the flow even if timing is not met. Implementation tools might be able to close timing if they can allocate the best resources to the failing paths. In addition, proceeding with the flow provides a more accurate understanding of the negative slack magnitude, which helps you determine how much you need to improve the post-synthesis worst negative slack (WNS). You can use this information when you return to the synthesis stage with improvements to HDL and constraints.

# **Taking Advantage of Rapid Validation**

This guide also introduces the concept of rapid validation of specific aspects of the system architecture and micro-architecture as follows:

- In the context of system design, the I/O bandwidth is validated in-system, before implementing the entire design. Validating I/O bandwidth can highlight the need to revise system architecture and interface choices before finalizing on I/Os. For more information, see Interface Bandwidth Validation in Chapter 2.

- As part of design implementation, baselining is used to write the simplest set of constraints, which can identify internal device timing challenges. Baselining can identify the need to revise RTL micro-architecture choices before moving to the implementation phase. For more information, see Baselining the Design in Chapter 5.

# **Using the Vivado Design Suite**

The Vivado Design Suite has a flexible use model to accommodate various development flows and different types of designs. For detailed information on how to use the features within the Vivado Design Suite, see the *Vivado Design Suite User Guide: Design Flows Overview* (UG892) [Ref 5] and other Vivado Design Suite documentation.

# Managing Vivado Design Suite Sources with a Revision Control System

Most design teams manage their design sources and results with a commercially available revision control system. The Vivado Design Suite allows various use models for managing design and IP data. For more information on using the Vivado tools with a revision control system, see this <u>link</u> in the *Vivado Design Suite User Guide: Design Flows Overview* (UG892) [Ref 5].

### **Upgrading to New Vivado Design Suite Releases**

New releases of the Vivado Design Suite often contain updates to Xilinx IP. Carefully consider whether you want to upgrade your IP, because upgrading can result in design changes. In addition, you must follow specific rules when using IP configured with previous releases going forward. For more information, see this <u>link</u> in the *Vivado Design Suite User Guide: Designing with IP* (UG896) [Ref 9].

# **Accessing Additional Documentation and Training**

This guide supplements the information in the Vivado Design Suite documentation, including user guides, reference guides, tutorials, and QuickTake videos. The Xilinx Documentation Navigator provides access to the Vivado Design Suite documentation and support resources, which you can filter and search to find information. To open the Xilinx Documentation Navigator (DocNav):

- From the Vivado IDE, select Help > Documentation and Tutorials.

- On Windows, select Start > All Programs > Xilinx Design Tools > DocNav.

- At the Linux command prompt, enter: docnav

Xilinx Design Hubs provide links to documentation organized by design tasks and other topics, which you can use to learn key concepts and address frequently asked questions. To access the Design Hubs:

- In the Xilinx Documentation Navigator, click the **Design Hubs View** tab.

- On the Xilinx website, see the <u>Design Hubs</u> page.

**TIP:** For quick access to information on different parts of the Vivado IDE, click the Quick Help button in the window or dialog box. For detailed information on Tcl commands, enter the command followed by-help in the Tcl Console.

# **Board and Device Planning**

# **Overview of Board and Device Planning**

Properly planning the FPGA orientation on the board and assigning signals to specific pins can lead to dramatic improvements in overall system performance, power consumption, and design cycle times. Visualizing how the FPGA device interacts physically and logically with the printed circuit board (PCB) enables you to streamline the data flow through the device.

Failing to properly plan the I/O configuration can lead to decreased system performance and longer design closure times. Xilinx highly recommends that you consider I/O planning in conjunction with board planning.

For more information, see the following resources:

- Vivado Design Suite User Guide: I/O and Clock Planning (UG899) [Ref 4]

- Vivado Design Suite QuickTake Video: I/O Planning Overview

# **PCB Layout Recommendations**

The layout of the FPGA device on the board relative to other components with which it interacts can significantly impact the I/O planning.

### Aligning with Physical Components on the PCB

The orientation of the FPGA device on the PCB should first be established. Consider the location of fixed PCB components, as well as internal FPGA resources. For example, aligning the GT interfaces on the FPGA package to be as close to the components with which they interface on the PCB will lead to shorter PCB trace lengths and fewer PCB vias.

A sketch of the PCB including the critical interfaces can often help determine the best orientation for the FPGA device on the PCB, as well as placement of the PCB components. Once done, the rest of the FPGA I/O interface can be planned.

High-speed interfaces such as memory can benefit from having very short and direct connections with the PCB components with which they interface. These PCB traces often have to be matched length and not use PCB vias, if possible. In these cases, the package pins closest to the edge of the device are preferred in order to keep the connections short and to avoid routing out of the large matrix of BGA pins.

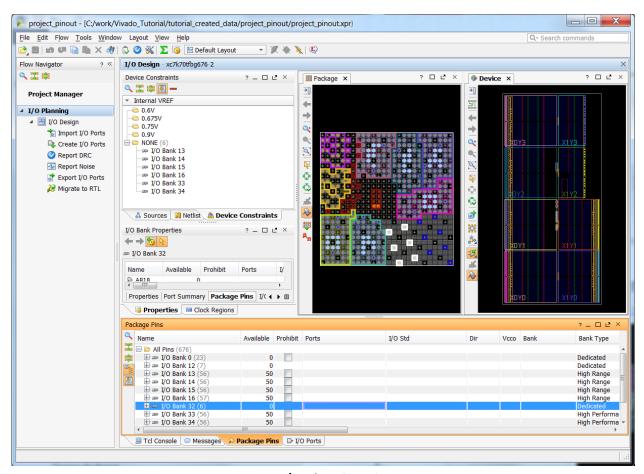

The I/O Planning View Layout in the Vivado IDE is useful in this stage for visualizing I/O connectivity relative to the physical device dimensions, showing both top-side and bottom-side views.

The following figure shows the I/O Planning view layout.

Figure 2-1: I/O Planning View Layout

### **Power Distribution System**

Board designers are faced with a unique task when designing a Power Distribution System (PDS) for an FPGA. Most other large, dense integrated circuits (such as large microprocessors) come with very specific bypass capacitor requirements. Since these devices are designed only to implement specific tasks in their hard silicon, their power supply demands are fixed, and fluctuate only within a certain range.

FPGA devices do not share this property. FPGA devices can implement an almost infinite number of applications at undetermined frequencies, and in multiple clock domains. For this reason, it is critical that you refer to the *PCB Design Guide* [Ref 37] for your device to fully understand the device PDS.

Key factors to consider during PDS design include:

- Selecting the right voltage regulators to meet the noise and current requirements based on Power Estimation. For more information, see Power Analysis and Optimization in Chapter 5.

- Setting up the XADC power supply (Vrefp and Vrefn pins).

- Running PDN simulation. The recommended amount of decoupling capacitors in the *PCB Design Guide* [Ref 37] for your device assumes worst-case situations, because FPGA devices can implement any arbitrary functionality. Running PDN simulations can help in reducing the amount of decoupling capacitors required to guarantee power supplies that are within the recommended operating range.

For more information on PDN simulation, see the Xilinx White Paper: Simulating FPGA Power Integrity Using S-Parameter Models (WP411) [Ref 52].

# **Specific Considerations for PCB Design**

The PCB should be designed considering the fastest signal interfacing with the FPGA device. These high-speed signals are extremely sensitive to trace geometry, vias, loss, and crosstalk. These aspects become even more prominent for multi-layer PCBs. For high-speed interfaces perform a signal integrity simulation. A board re-design with improved PCB material or altered trace geometries may be necessary to obtain the desired performance.

Xilinx recommends following these steps when designing your PCB:

- 1. Review the following device documentation:

- PCB Design Guide [Ref 37] for your device.

- Board design guidelines in the *Transceiver User Guide* [Ref 42] for your device.

- 2. Review memory IP and PCIe® design guidelines in the IP product guides.

- 3. Use the Vivado<sup>®</sup> tools to validate your I/O planning:

- Run simultaneous switching noise (SSN) analysis.

- Run built-in DRCs.

- Export I/O buffer information specification (IBIS) models.

- 4. Run signal integrity analysis as follows:

- For gigabit transceivers (GTs), run Spice or IBIS-AMI simulations using channel parameters.

- For lower performance interfaces, run IBIS simulation to check for issues with overshoot or undershoot.

- 5. Use the Xilinx Power Estimator (XPE) to generate an early estimate of the power consumption for the design.

- 6. Complete and adhere to the schematic checklist for your device.

# **Clock Resource Planning and Assignment**

Xilinx recommends that you select clocking resources as one of the first steps of your design, well before pinout selection. Your clocking selections can dictate a particular pinout and can also direct logic placement for that logic, especially for SSI technology devices. Proper clocking selections can yield superior results. Consider the following:

- Constraint creation, particularly in large devices with high utilization in conjunction with clock planning.

- Manual placement of clocking resources if needed for design closure. Clocking Guidelines in Chapter 3 provides more details on clocking resources, if you need to do manual placement.

- Device-specific functionality that might require up-front planning to avoid issues and take advantage of device features. For information on 7 series features, see this <u>link</u> and this <u>link</u> in the 7 Series FPGAs Clocking Resources User Guide (UG472) [Ref 41]. For

information on UltraScale™ device features, see this <u>link</u> in the *UltraScale Architecture Clocking Resources User Guide* (UG572) [Ref 41].

# I/O Planning Design Flows

The Vivado IDE allows you to interactively explore, visualize, assign, and validate the I/O ports and clock logic in your design. The environment ensures correct-by-construction I/O assignment. It also provides visualization of the external package pins in correlation with the internal die pads.

You can visualize the data flow through the device and properly plan I/Os from both an external and internal perspective. After the I/Os are assigned and configured through the Vivado IDE, constraints are then automatically created for the implementation tools.

For more information on Vivado Design Suite I/O and clock planning capabilities, see the following resources:

- Vivado Design Suite User Guide: I/O and Clock Planning (UG899) [Ref 4]

- Vivado Design Suite Tutorial: I/O and Clock Planning (UG935) [Ref 33]

- Vivado Design Suite QuickTake Video: I/O Planning Overview

# Types of Vivado Design Suite Projects for I/O Planning

You can perform I/O planning with either of the following types of projects:

I/O planning project

An I/O planning project is an easy entry point that allows you to specify select I/O constraints and generate a top-level RTL file from the defined pins.

RTL project

An RTL project allows synthesis and implementation, which enables more comprehensive design rule checks (DRCs). An RTL project also allows generation of IP cores, which is important for memory interface pinout planning and any cores using GTs.

TIP: You can also start by using an I/O planning project and migrate to an RTL project later.

You can run more comprehensive DRCs on a post-synthesis netlist. The same is true after implementation and bitstream generation. Therefore, Xilinx recommends using a skeleton design that includes clocking components and some basic logic to exercise the DRCs. This builds confidence that the pin definition for the board will not have issues later.

The recommended sign-off process is to run the RTL project through to bitstream generation to exercise all the DRCs. However, not all design cycles allow enough time for this process. Often the I/O configuration must be defined before you have synthesizable RTL. Although the Vivado tools enable pre-RTL I/O planning, the level of DRCs performed are fairly basic. Alternatively, you can use a dummy top-level design with I/O standards and pin assignments to help perform DRCs related to banking rules.

#### Pre-RTL I/O Planning

If your design cycle forces you to define the I/O configuration before you have a synthesized netlist, take great care to ensure adherence to all relevant rules. The Vivado tools include a Pin Planning Project environment that allows you to import I/O definitions using a CSV or XDC format file. You can also create a dummy RTL with just the port directions defined. Availability of port direction makes simultaneous-switching-noise (SSN) analysis more accurate as input and output signals have different contributions to SSN.

I/O ports can also be created and configured interactively. Basic I/O bank DRC rules are provided.

See the *PCB Design Guide* [Ref 37] for your device to ensure proper I/O configuration. For more information, see this <u>link</u> in the *Vivado Design Suite User Guide: I/O and Clock Planning* (UG899) [Ref 4].

#### Netlist-Based I/O Planning

The recommended time in the design cycle to assign I/Os and clock logic constraints is after the design has been synthesized. The clock logic paths are established in the netlist for constraint assignment purposes. The I/O and clock logic DRCs are also more comprehensive.

See the *PCB Design Guide* [Ref 37] for your device to ensure proper I/O configuration. For more information, see this <u>link</u> in the *Vivado Design Suite User Guide: I/O and Clock Planning* (UG899) [Ref 4].

### **Defining Alternate Devices**

It is often difficult to predict the final device size for any given design during initial planning. Logic can be added or removed during the course of the design cycle, which can result in the need to change the device size.

The Vivado tools enable you to define alternate devices to ensure that the I/O pin configuration defined is compatible across all selected devices, as long as the package is the same.

**IMPORTANT:** The device must be in the same package.

To migrate your design with reduced risk, carefully plan the following at the beginning of the design process: device selection, pinout selection, and design criteria. Take the following into account when migrating to a larger or smaller device in the same package: pinout, clocking, and resource management. For more information, see this <u>link</u> in the *Vivado Design Suite User Guide: I/O and Clock Planning* (UG899) [Ref 4].

### Pin Assignment

Good pinout selection leads to good design logic placement. Poor placement might also create longer routes, causing increased power consumption and reduced performance. These consequences of good pinout selection are particularly true for large FPGA devices, because a spread out pinout can cause related signals to span longer distances. For more information, see this <u>link</u> in the *Vivado Design Suite User Guide: I/O and Clock Planning* (UG899) [Ref 4].

#### Using Xilinx Tools in Pinout Selection

Xilinx tools assist in interactive design planning and pin selection. These tools are only as effective as the information you provide them. Tools such as the Vivado design analysis tool can assist pinout efforts. These tools can graphically display the I/O placement, show relationships among clocks and I/O components, and provide DRCs to analyze pin selection.

If a design version is available, a quick top-level floorplan can be created to analyze the data flow through the device. For more information, see the *Vivado Design Suite User Guide: Design Analysis and Closure Techniques* (UG906) [Ref 21].

### **Required Information**

For the tools to work effectively, you must provide as much information about the I/O characteristics and topologies as possible. You must specify the electrical characteristics, including the I/O standard, drive, slew, and direction of the I/O.

You must also take into account all other relevant information, including clock topology and timing constraints. Clocking choices in particular can have a significant influence in pinout selection and vice-versa, as discussed in Clocking Guidelines in Chapter 3.

For IP that have I/O requirements, such as transceivers, PCIe, and memory interfaces, you must configure the IP prior to completing I/O pin assignment, as described in Pinout Selection. For more information on specifying the electrical characteristics for an I/O, see this <u>link</u> in the *Vivado Design Suite User Guide: I/O and Clock Planning* (UG899) [Ref 4].

#### **Pinout Selection**

Xilinx recommends careful pinout selection for some specific signals as discussed below.

#### Interface Data, Address, and Control Pins

Group the same interface data, address, and control pins into the same bank. If you cannot group these components into the same bank, group them into adjacent banks. For stacked silicon interconnect (SSI) technology devices, adjacent banks must also be located within the same super logic region (SLR).

#### **Interface Control Signals**

Place the following interface control signals in the middle of the data buses they control (clocking, enables, resets, and strobes).

#### Very High Fanout, Design-Wide Control Signals

Place very high fanout, design-wide control signals towards the center of the device.

For SSI technology devices, place the signals in the SLR located in the middle of the SLR components they drive.

#### **Configuration Pins**

To design an efficient system, you must choose the FPGA configuration mode that best matches the system requirements. Factors to consider include:

- Using dedicated vs. dual purpose configuration pins.

- Each configuration mode dedicates certain FPGA pins and can temporarily use other multi-function pins during configuration only. These multi-function pins are then released for general use when configuration is completed.

- Using configuration mode to place voltage restrictions on some FPGA I/O banks.

- Choosing suitable terminations for different configuration pins.

- Using the recommended values of pullup or pulldown resistors for configuration pins.

**RECOMMENDED:** Even though configuration clocks are slow speed, perform signal integrity analysis on the board to ensure clean signals.

There are several different configuration options. Although the options are flexible, there is often an optimal solution for each system. Consider the following when choosing the best configuration option:

- Setup

- Speed

- Cost

- Complexity

See Configuration. For more information on FPGA configuration options, see *Vivado Design Suite User Guide: Programming and Debugging* (UG908) [Ref 24].

#### **Memory Interfaces**

Additional I/O pin planning steps are required when using Xilinx Memory IP. After the IP is customized, you then assign the top-level IP ports to physical package pins in either the elaborated or synthesized design in the Vivado IDE. All of the ports associated with each Memory IP are group together into an I/O Port Interface for easier identification and assignment. A Memory Bank/Byte Planner is provided to assist you with assigning Memory I/O pin groups to byte lanes on the physical device pins. For more information, see this <a href="Link">Link</a> in the Vivado Design Suite User Guide: I/O and Clock Planning (UG899) [Ref 4].

Take care when assigning memory interfaces and try to limit congestion as much as possible, especially with devices that have a center I/O column. Bunching memory interfaces together can create routing bottlenecks across the device. The Xilinx Zynq-7000 SoC and 7 Series Devices Memory Interface User Guide (UG586) [Ref 49] and the LogiCORE IP UltraScale Architecture-Based FPGAs Memory Interface Solutions Product Guide (PG150) [Ref 50] contain design and pinout guidelines. Be sure that you follow the trace length match recommendations in these guides, verify that the correct termination is used, and validate the pinout in by running the DRCs after memory IP I/O assignment.

### Gigabit Transceivers (GTs)

Gigabit transceivers (GTs) have specific pinout requirements, and you must consider the following:

- Sharing of reference clocks

- Sharing of PLLs within a guad

- Placement of hard blocks, such as PCIe, and their proximity to transceivers

- In SSI technology devices, crossing of SLR boundaries

Xilinx recommends that you use the GT wizard to generate the core. Alternatively, you can use the Xilinx IP core for the protocol. For pinout recommendations, see the related product guide.

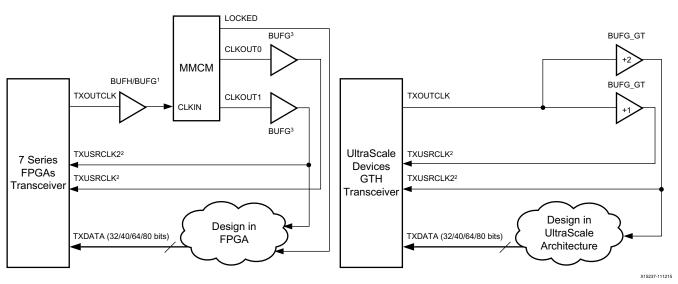

For clock resource balancing, the Vivado placer attempts to constrain loads clocked by GT output clocks (TXOUTCLK or RXOUTCLK) next to the GTs sourcing the clocks. For stacked silicon interconnect (SSI) technology devices, if the GTs are located in the clock regions adjacent to another SLR, the routing resources required for signals entering or exiting SLLs have to compete with the routing resources required by the GT output clock loads. Therefore, GTs located in clock regions next to SLR crossings might reduce the available routing connections to and from the SLL crossings available in those clock regions.

#### High Speed I/O

HP (high-performance) and HR (high-range) banks have difference in the speed with which they can transmit and receive signals. Depending upon the I/O speed you need, choose between HP or HR banks.

#### Internal VREF and DCI Cascade Constraints

Based on the settings for DCI Cascade and Internal VREF, you can free up pins to be used for regular I/Os. These settings also ensure that related DRC checks are run to validate the legality of the constraints. For more information, see the *SelectIO Resources User Guide* [Ref 40] for your device.

#### Interface Bandwidth Validation

Create small connectivity designs to validate each interface on the FPGA. These small designs exercise only the specific hardware interface, which enables the following:

- Full DRC checks on pinout, clocking, and timing

- Hardware test design when the board is returned

- Rapid implementation through the Vivado tools, providing the fastest way to debug the interface

There are multiple options to assist in generating test data for these interfaces. For some of the interface IP cores, the Vivado tools can provide the test designs:

- IBERT for SerDes

- Example design within IP cores

**TIP:** If a test design does not exist, consider using AXI traffic generators.

You might need to create a separate design for a system-level test in a production environment. Usually, this is a single design that includes tested interfaces and optionally includes processors. You can construct this design using the small connectivity designs to take advantage of design reuse. Although this design is *not* required early in the flow, it can enable better DRC checks and early software development, and you can quickly create it using the Vivado IP Integrator.

# **Designing with SSI Devices**

#### **SSI Pinout Considerations**

When planning pinouts for components that are located in a particular SLR, place the pins into the same SLR. For example, when using the device DNA information as a part of an external interface, place the pins for that interface in the master SLR in which the DNA\_PORT exists. Additional considerations include the following:

- Group all pins of a particular interface into the same SLR.

- For signals driving components in multiple SLRs, place those signals in the middle SLR.

- Balance CCIO or CMT components across SLRs.

- · Reduce SLR crossings.

### **Super Logic Region (SLR)**

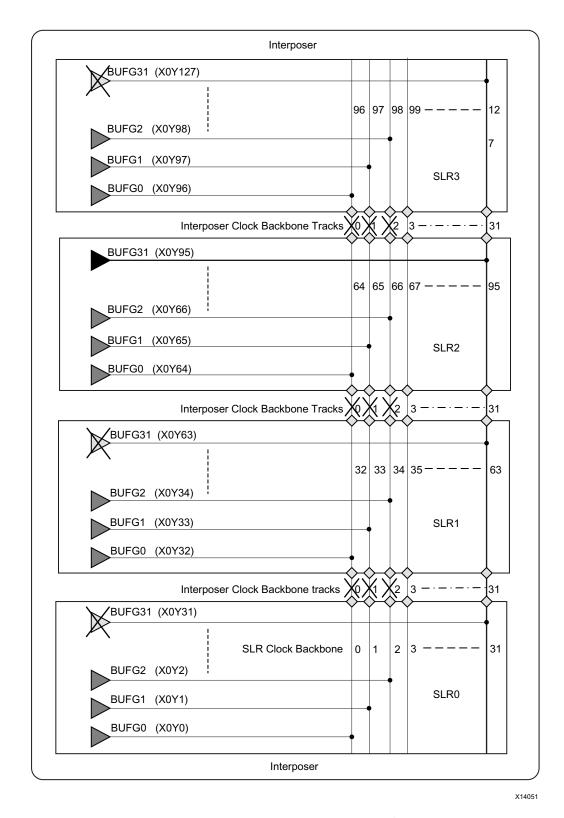

A super logic region (SLR) is a single FPGA die slice contained in an SSI technology device. Each SLR contains the main FPGA circuits, such as slices, RAMs DSP slices, and GTs.

Multiple SLR components are stacked vertically and connected through an interposer to create an SSI technology device. The bottom SLR is SLR0, and subsequent SLR components are named incrementally as they ascend vertically. For example, the XC7V2000T device includes four SLR components. The bottom SLR is SLR0, the SLR directly above SLR0 is SLR1, the SLR directly above SLR1 is SLR2, and the top SLR is SLR3.

**Note:** The Xilinx tools clearly identify SLR components in the graphical user interface (GUI) and in reports.

#### **SLR Nomenclature**

Understanding SLR nomenclature for your target device is important in:

- Pin selection

- Floorplanning

- Analyzing timing and other reports

- Identifying where logic exists and where that logic is sourced or destined

You can use the Vivado Tcl command get\_slrs to get specific information about SLRs for a particular device. For example, use the following commands:

- llength [get\_slrs] to obtain the number of SLRs in the device

- get\_slrs -of\_objects [get\_cells my\_cell] to get the SLR in which my\_cell is placed

### **Master Super Logic Region**

Every SSI technology device has a single master SLR. The master SLR contains the primary configuration logic that initiates configuration of the device and all other SLR components. The master SLR contains the circuitry that is used for configuration, DNA\_PORT, and EFUSE\_USER. When using these components, the place and route tools can assign associated pins and logic to the appropriate SLR. In general, no additional intervention is required.

**TIP:** To query which SLR is the master SLR in the Vivado Design Suite, you can enter the get\_slrs -filter IS\_MASTER Tcl command.

# Silicon Interposer

The silicon interposer is a passive layer in the SSI technology device, which routes the following between SLR components:

- Configuration

- Global clocking

- General interconnect

# Super Long Line (SLL) Routes

Super Long Line (SLL) routes connect signals from one SLR to another inside the device.

**TIP:** To determine the number of SLLs between two SLRs as well as the number of available resources, run the report\_utilization -slrTcl command on a small, post-synthesized design that includes minimal logic.

# **Propagation Limitations**

TIP: For high-speed propagation across SLRs, consider registering signals that cross SLR boundaries.

SLL signals are the only data connections between SLR components.

The following do not propagate across SLR components:

- · Carry chains

- DSP cascades

- Block RAM address cascades

- Other dedicated connections, such as DCI cascades and block RAM cascades

The tools normally take this limit on propagation into account. To ensure that designs route properly and meet your design goals, you must also take this limit into account when you build a very long DSP cascade and manually place such logic near SLR boundaries as well as when you specify a pinout for the design.

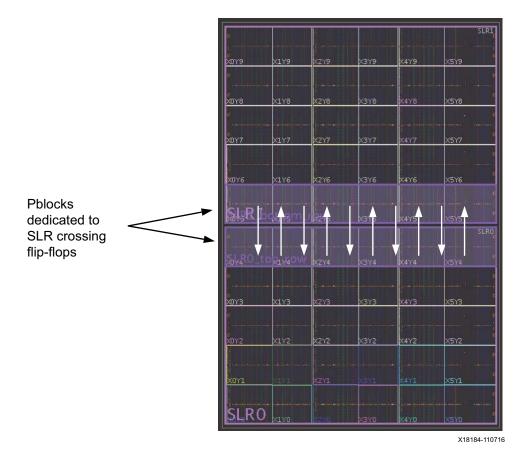

#### **SLR Utilization Considerations**

The Vivado implementation tools use a special algorithm to partition logic into multiple SLRs. For challenging designs, you can improve timing closure for designs that target SSI technology devices using the following guidelines.

To improve timing closure and compile times, you can use Pblocks to assign logic to each SLR and validate that individual SLRs do not have excessive utilization across all fabric resource types. For example, a design with BRAM utilization of 70% might cause issues with timing closure if the BRAM resources are not balanced across SLRs and one SLR is using over 85% BRAMs.

The following example utilization report for a vu160 shows that the overall BRAM utilization is 56% while the BRAM utilization in SLR0 is 89% (897 out of 1008 available). Timing closure might be more difficult to achieve for the design in SLR0 than with a balanced BRAM utilization across SLRs.

#### 3. BLOCKRAM

| +              | L    | L     | L         | ++          |

|----------------|------|-------|-----------|-------------|

| Site Type      | Used | Fixed | Available | <br>  Util% |

| Block RAM Tile | 1843 | 0     | 3276      | 56.26       |

| RAMB36/FIFO*   | 1820 | 1     | 3276      | 55.56       |

| FIFO36E2 only  | 78   |       |           | į į         |

| RAMB36E2 only  | 1742 |       |           | į į         |

| RAMB18         | 46   | 0     | 6552      | 0.70        |

| RAMB18E2 only  | 46   |       |           | į į         |

|                |      |       |           |             |

#### 14. SLR CLB Logic and Dedicated Block Utilization

| +                        | +                           | <b>.</b>                    | L                              | +                         | L                       | <b>.</b>                   | L                 | L         |

|--------------------------|-----------------------------|-----------------------------|--------------------------------|---------------------------|-------------------------|----------------------------|-------------------|-----------|

| SLR Index                | CLBs                        | (%)CLBs                     | Total LUTs                     | Memory LUTs               | (%)Total LUTs           | Registers                  | BRAMs             | DSPs      |

| SLR2<br>  SLR1<br>  SLR0 | 40109<br>  42649<br>  35379 | 89.61<br>  95.28<br>  97.62 | 167520<br>  205484<br>  163188 | 156  <br>  2297  <br>  24 | 46.78<br>57.38<br>56.29 | 327600<br>355918<br>313392 | 512<br>434<br>897 | 0   0   0 |

| Total                    | 118137                      | +<br>                       | +<br>  536192                  | +                         |                         | 996910                     | 1843              | 0         |

Xilinx recommends assigning BRAM and DSP groups to SLR Pblocks to minimize SLR crossings of shared signals. For example, an address bus that fans out to a group of BRAMs that are spread out over multiple SLRs can make timing closure more difficult to achieve, because the SLR crossing incurs additional delay for the timing critical signals.

Device resource location or user I/O selection anchors IP to SLRs, for example, GT, ILKN, PCIe, and CMAC dedicated block or memory interface controllers. Xilinx recommends the following:

- Pay special attention to dedicated block location and pinout selection to avoid data flow crossing SLR boundaries multiple times.

- Keep tightly interconnected modules and IPs within the same SLR. If that is not possible, you can add pipeline registers to allow the placer more flexibility to find a good solution despite the SLR crossing between logic groups.

- Keep critical logic within the same SLR. By ensuring that main modules are properly

pipelined at their interfaces, the placer is more likely to find SLR partitions with flip-flop

to flip-flop SLR crossings.

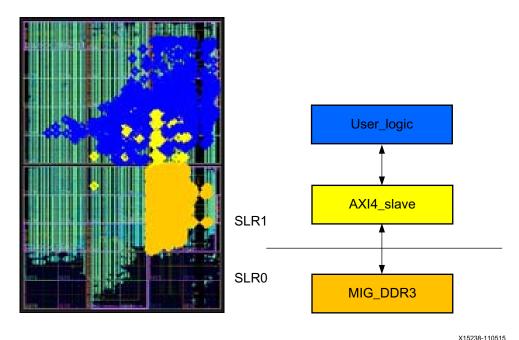

In the following figure, a memory interface that is constrained to SLR0 needs to drive user logic in SLR1. An AXI4-Lite slave interface connects to the memory IP backend, and the well-defined boundary between the memory IP and the AXI4-Lite slave interface provides a good transition from SLR0 to SLR1.

....

Figure 2-2: Memory Interface in SLR0 Driving User Logic in SLR1

### **SLR Crossing for Wide Buses**

When data flow requirements require that wide buses cross SLRs, use pipelining strategies to improve timing closure and alleviate routing congestion of long resources. For wide buses operating above 250 MHz, Xilinx recommends using at least 3 pipeline stages to cross an SLR: one at the top, one at the bottom, and one in the middle of the SLR. Additional pipeline stages might be required for very high performance buses or when traversing horizontal as well as vertical distances.

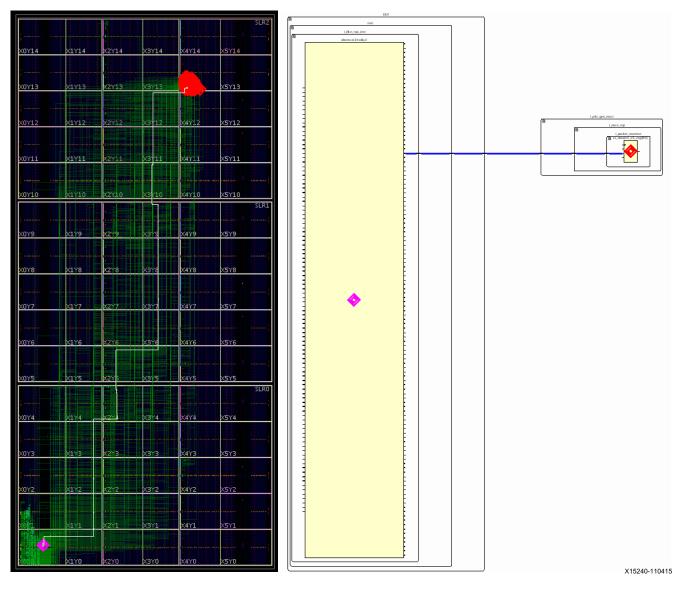

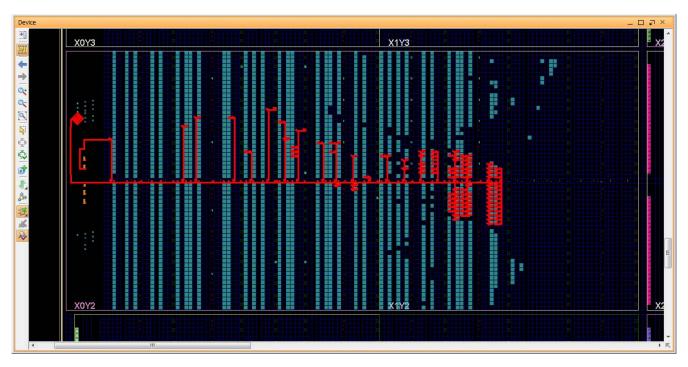

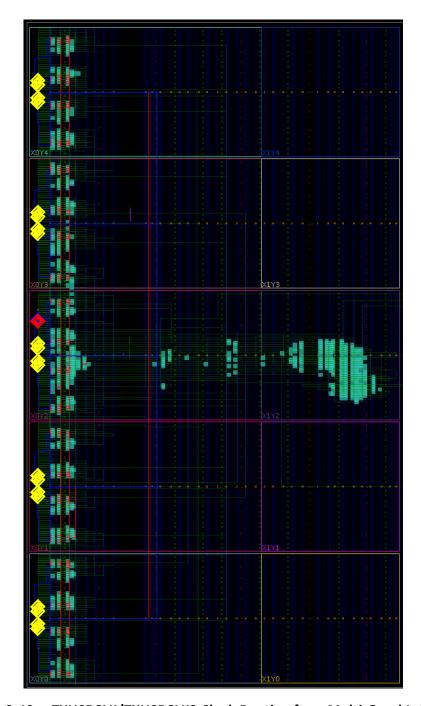

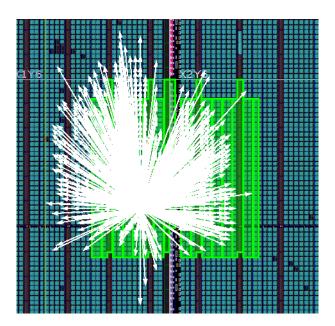

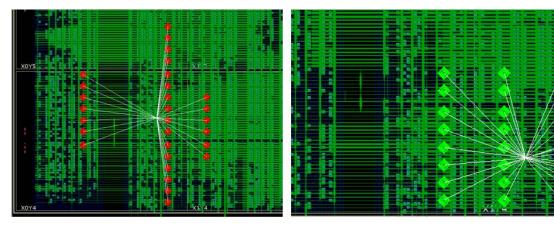

The following figure illustrates a worst case crossing for a vu190-2 device. This example starts at an Interlaken dedicated block in the bottom left of SLR0 to a packet monitor block assigned to the top right of SLR2. Without pipeline registers for the data bus to and from the packet monitor, the design misses the 300 MHz timing requirement by a wide margin.

Figure 2-3: Data Path Crossing SLR without Pipeline Flip-Flop

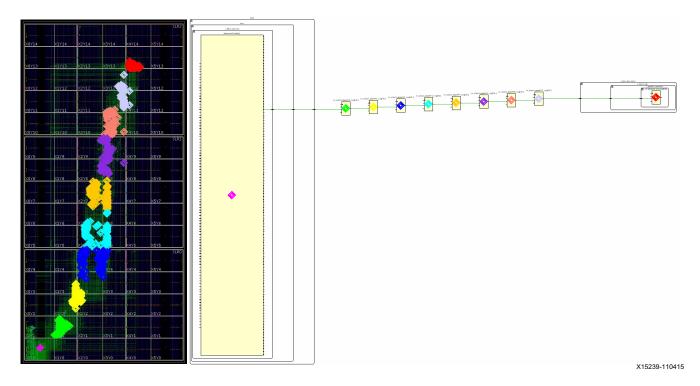

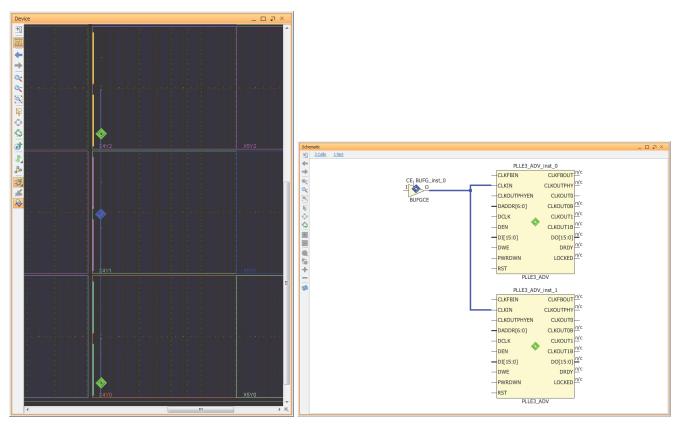

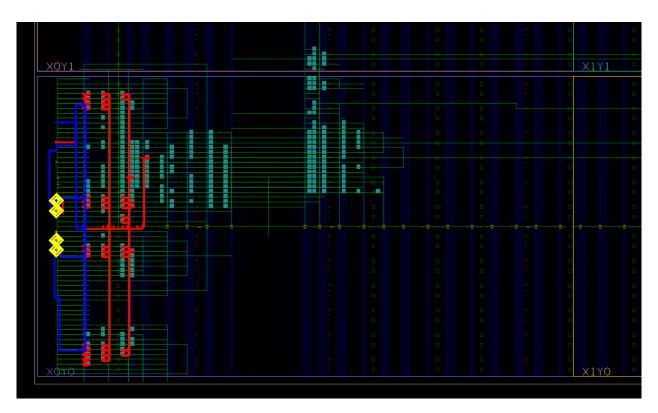

However, adding 7 pipeline stages to aid in the traversal from SLR0 to SLR2 allows the design to meet timing. It also reduces the use of vertical and horizontal long routing resources, as shown in the following figure.

Figure 2-4: Data Path Crossing SLR with Pipeline Flip-Flop Added

# **FPGA Power Aspects and System Dependencies**

When planning the PCB, you must take power into consideration:

- The FPGA device and the user design create system power supply and heat dissipation requirements.

- Power supplies must be able to meet maximum power requirements and the device

must remain within the recommended voltage and temperature operating conditions

during operation. Power estimation and thermal modeling may be required in order to

ensure that the device stays within these limits.

For these reasons, you must understand the power and cooling requirements of the FPGA device. These must be designed on the board.

# **Power Supply Paths on FPGA Devices**

Multiple power supplies are required to power an FPGA device. Some of this power must be provided in a specific sequence. Consider the use of power monitoring or sequencing circuitry to provide the correct power-on sequence to the FPGA device and GTs, as well as any additional active components on the board. More complex environments may benefit from the use of a microcontroller or system and power management bus such as SMBUS or PMBUS to control the power and reset process. Specific details regarding on/off sequencing can be found in the device data sheet.

The separate sources provide the required power for the different FPGA resources. This allows different resources to work at different voltage levels for increased performance or signal strength, while preserving a high immunity to noise and parasitic effects.

#### **Power Modes**

An FPGA device goes through several power phases from power up to power down with varying power requirements.

#### Power-On

Power-on power is the transient spike current that occurs when power is first applied to the FPGA device. This current varies for each voltage supply, and depends on the FPGA device construction; the ability of the power supply source to ramp up to the nominal voltage; and the device operating conditions, such as temperature and sequencing between the different supplies.

Spike currents are not a concern in modern FPGA device architectures when the proper power-on sequencing guidelines are followed.

#### Startup Power

Startup power is the power required during the initial bring-up and configuration of the device. This power generally occurs over a very short period of time and thus is not a concern for thermal dissipation. However, current requirements must still be met. In most cases, the active current of an operating design will be higher and thus no changes are necessary. However, for lower-power designs where active current can be low, a higher current requirement during this time may be necessary. Xilinx Power Estimator (XPE) can be used to understand this requirement. When Process is set to **Maximum**, the current requirement for each voltage rail will be specified to either the operating current or the startup current, whichever is higher. XPE will display the current value in blue if the startup current is the higher value.

#### Standby Power

Standby power (also called *design static power*) is the power supplied when the device is configured with your design and no activity is applied externally or generated internally.

Standby power represents the minimum continuous power that the supplies must provide while the design operates.

#### **Active Power**

Active power (also called *design dynamic power*) is the power required while the device is running your application. Active power includes standby power (all static power), plus power generated from the design activity (design dynamic power). Active power is instantaneous and varies at each clock cycle depending on the input data pattern and the design internal activity.

### **Environmental Factors Impacting Power**

In addition to the design itself, environmental factors affect power. These factors influence the voltage and the junction temperature of the device, which impacts the power dissipation. For details, see this <u>link</u> in the *Vivado Design Suite User Guide: Power Analysis and Optimization* (UG907) [Ref 22].

### **Power Models Accuracy**

The accuracy of the characterization data embedded in the tools evolves over time to reflect the device availability or manufacturing process maturity. For details, see this <u>link</u> in the *Vivado Design Suite User Guide: Power Analysis and Optimization* (UG907) [Ref 22].

### **FPGA Device Power and the Overall System Design Process**

From project conception to completion, various aspects of the design process affect power. For details, see this <u>link</u> in the *Vivado Design Suite User Guide: Power Analysis and Optimization* (UG907) [Ref 22].

# Worst Case Power Analysis Using Xilinx Power Estimator (XPE)

Xilinx recommends designing the board for worst-case power. For details, see this <u>link</u> in the *Vivado Design Suite User Guide: Power Analysis and Optimization* (UG907) [Ref 22].

# Configuration

Configuration is the process of loading application-specific data into the internal memory of the FPGA device.

Because Xilinx FPGA configuration data is stored in CMOS configuration latches (CCLs), the configuration data is volatile and must be reloaded each time the FPGA device is powered up.

Xilinx FPGA devices can load themselves through configuration pins from an external nonvolatile memory device. They can also be configured by an external smart source, such as a:

- Microprocessor

- DSP processor

- Microcontroller

- Personal Computer (PC)

- Board tester

Board Planning should consider configuration aspects up front, which makes it easier to configure as well as debug.

Each device family has a *Configuration User Guide* [Ref 39] that is the primary resource for detailed information about each of the supported configuration modes and their trade-offs on pin count, performance, and cost.

# **Board Design Tips**

When designing a board, it is important to consider which interfaces and pins will assist with debug capability beyond configuration. For example, Xilinx recommends that you ensure the JTAG interface is accessible even when the interface is not the primary configuration mode. The JTAG interface allows you to check the device ID and device DNA information, and you can use the interface to enable indirect flash programming solutions during prototyping.

In addition, signals such as the INIT\_B and DONE are critical for FPGA configuration debug. The INIT\_B signal has multiple functions. It indicates completion of initialization at power-up and can indicate when a CRC error is encountered. Xilinx recommends that you connect the INIT\_B and DONE signals to LEDs using LED drivers and pull-ups. For recommended pull-up values, see the *Configuration User Guide* [Ref 39] for your device.

The *Schematic Checklists* [Ref 53] include these recommendations along with other key suggestions. Use these checklists to identify and check recommended board-level pin connections.

# **Design Creation**

# **Overview of Design Creation**

After planning your device I/O, planning how to lay out your PCB, and deciding on your use model for the Vivado<sup>®</sup> Design Suite, you can begin creating your design. Design creation includes:

- Planning the hierarchy of your design

- Identifying the IP cores to use and customize in your design

- Creating the custom RTL for interconnect logic and functionality for which a suitable IP is not available

- Creating timing and physical constraints

- Specifying additional constraints, attributes, and other elements used during synthesis and implementation

When creating your design, the main points to consider include:

- Achieving the desired functionality

- Operating at the desired frequency

- Operating with the desired degree of reliability

- Fitting within the silicon resource and power budget

Decisions made at this stage affect the end product. A wrong decision at this point can result in problems at a later stage, causing issues throughout the entire design cycle. Spending time early in the process to carefully plan your design helps to ensure that you meet your design goals and minimize debug time in lab.

# **Defining a Good Design Hierarchy**

The first step in design creation is to decide how to partition the design logically. The main factor when considering hierarchy is to partition a part of the design that contains a specific function. This allows a specific designer to design a piece of IP in isolation as well as isolating a piece of code for reuse.

However, defining a hierarchy based on functionality only does not take into account how to optimize for timing closure, runtime, and debugging. The following additional considerations made during hierarchy planning also help in timing closure.

# Add I/O Components Near the Top Level

Where possible, add I/O components near the top level for design readability. When you infer a component, you provide a description of the function you want to accomplish. The synthesis tool then interprets the HDL code to determine which hardware components to use to perform the function. Components that can be inferred are simple single-ended I/O (IBUF, OBUF, OBUFT and IOBUF) and single data rate registers in the I/O.

I/O components that need to be instantiated, such as differential I/O (IBUFDS, OBUFDS) and double data-rate registers (IDDR, ODDR, ISERDES, OSERDES), should also be instantiated near the top level. When you instantiate a component, you add an instance of that component to your HDL file. Instantiation gives you full control over how the component is used. Therefore, you know exactly how the logic will be used.

# **Insert Clocking Elements Near the Top Level**

Inserting the clocking elements towards the top level allows for easier clock sharing between modules. This sharing may result in fewer clocking resources needed, which helps in resource utilization, improved performance, and power.

Aside from the module the clocks are created in, clock paths should only drive down into modules. Any paths that go through (down from top and then back to top) can create a delta cycle problem in VHDL simulation that is difficult and time consuming to debug.

### **Register Data Paths at Logical Boundaries**

Register the outputs of hierarchical boundaries to contain critical paths within a single module or boundary. Consider registering the inputs also at the hierarchical boundaries. It is always easier to analyze and repair timing paths which lie within a module, rather than a path spanning multiple modules. Any paths that are not registered at hierarchy boundaries should be synthesized with hierarchy rebuilt or flat to allow cross hierarchy optimization. Registering the datapaths at logical boundaries helps to retain traceability (for debug)

through the design process because cross hierarchical optimizations are kept to a minimum and logic does not move across modules.

# **Address Floorplanning Considerations**

A floorplan ensures that cells belonging to a specific portion in the design netlist are placed at particular locations on the device. You can use manual floorplanning to accomplish the following:

- Partition logic to a particular SLR when using SSI technology devices.

- Close timing on a design when timing is not met using standard flows.

If the cells are not contained within a level of hierarchy, all objects must be included individually in the floorplan constraint. If synthesis changes the names of these objects, you must update the constraints. A good floorplan is contained at the hierarchy level, because this requires only a one line constraint.

Floorplanning is not always required. Floorplan only when necessary.

For more information on floorplanning, see this <u>link</u> in the *Vivado Design Suite User Guide: Design Analysis and Closure Techniques* (UG906) [Ref 21].

**RECOMMENDED:** Although the Vivado tools allow cross hierarchy floorplans, these require more maintenance. Avoid cross hierarchy floorplans where possible.

# **Optimize Hierarchy for Functional and Timing Debug**

As discussed earlier in this section, keeping the critical path within the same hierarchical boundary is helpful in debugging and meeting timing requirements. Similarly, for functional debug (and modification) purposes, signals that are related should be kept in the same hierarchy. This allows the related signals to be probed and modified with relative ease, as signal names optimized by synthesis are easier to trace when contained in a single level of hierarchy.

### Apply Attributes at the Module Level

Applying attributes at the module level can keep code tidier and more scalable. Instead of having to apply an attribute at the signal level, you can apply the attribute at the module level and have the attribute propagated to all signals declared in that region. Applying attributes at the module level also allows you to override global synthesis options. For this reason, it is sometimes advantageous to add a level of hierarchy in order to apply module level constraints in the RTL.

**CAUTION!** Some attributes (e.g., DONT\_TOUCH) do not propagate from a module to all the signals inside the module.

# **Optimize Hierarchy for Advanced Design Techniques**

Advanced design techniques such as bottom-up synthesis, partial reconfiguration, and out-of-context design require planning at the hierarchical level. The design must choose the appropriate level of hierarchy for the technique being used. These techniques are not covered in this version of the document. For more information, see this <u>link</u> in the *Vivado Design Suite User Guide: Hierarchical Design* (UG905) [Ref 20].

# **Example of Upfront Hierarchical Planning for High Speed DSP Designs**

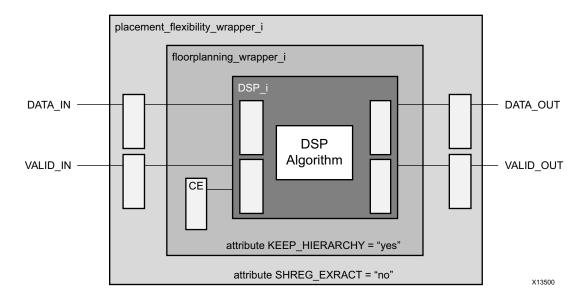

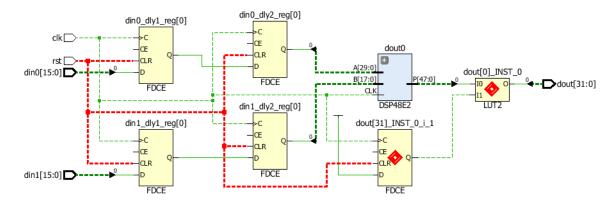

The following example is not applicable to all designs, but demonstrates what can be done with hierarchy. DSP designs generally allow latency to be added to the design. This allows registers to be added to them to be optimized for performance. In addition, registers can be used to allow for placement flexibility. This is important because at high speed, you cannot traverse the die in one clock cycle. Adding registers can allow hard-to-reach areas to be used. The following figure shows how effective hierarchy planning results in faster timing closure.

Figure 3-1: Effective Hierarchy Planning Example

There are three levels of hierarchy in this part of the design:

• DSP\_i

In the DSP\_i algorithm block, both the inputs and outputs are registered. Because registers are plentiful in an FPGA device, it is preferable to use this method to improve the timing budget.

• floorplanning\_wrapper\_i

In floorplanning\_wrapper\_i, there is a CE signal. CE signals are typically heavily-loaded and can present a timing challenge. They should be included in a floorplan. By creating a floorplanning wrapper, this module can be manually floorplanned later if needed.

In addition, KEEP\_HIERARCHY has been added at the module level to ensure that hierarchy is preserved for floorplanning regardless of any other global synthesis options.

• placement\_flexibility\_wrapper\_i

In placement\_flexibility\_wrapper\_i, the DATA\_IN, VALID\_IN, DATA\_OUT and VALID\_OUT signals are registered. Because these signals are not intended to be part of the floorplan, they are outside floorplanning\_wrapper\_i. If they were in the floorplan, they would not be able to fulfill the requirement for placement flexibility.

In addition, more registers can be added later as long as both DATA\_IN + VALID\_IN or DATA\_OUT and VALID\_OUT are treated as pairs. If more registers are added, the synthesis tool may infer SRLs which will force all registers into one component and not help placement flexibility. To prevent this, SHREG\_EXTRACT has been added at the module level and set to NO.

# **RTL Coding Guidelines**

You can create custom RTL to implement glue logic functions as well as functions without suitable IP. For optimal results, follow the coding guidelines in this section. For additional guidelines, see this link in the *Vivado Design Suite User Guide: Synthesis* (UG901) [Ref 16].

# **Using Vivado Design Suite HDL Templates**

Use the Vivado Design Suite Language Templates when creating RTL or instantiating Xilinx® primitives. The Language Templates include recommended coding constructs for proper inference to the Xilinx device architecture. Using the Language Templates can ease the design process and lead to improved results. To open the Language Templates from the Vivado IDE, select the **Language Templates** option in the **Flow Navigator**, and select the desired template.

# **Control Signals and Control Sets**

A control set is the grouping of control signals (set/reset, clock enable and clock) that drives any given SRL, LUTRAM, or register. For any unique combination of control signals, a unique control set is formed. The reason this is an important concept is registers within a 7 series slice all share common control signals and thus only registers with a common control set may be packed into the same slice. For example, if a register with a given control set has just one register as a load, the other seven registers in the slice it occupies will be unusable.

Designs with several unique control sets may have many wasted resources as well as fewer options for placement, resulting in higher power and lower performance. Designs with fewer control sets have more options and flexibility in terms of placement, generally resulting in improved results.

In UltraScale™ devices, there is more flexibility in control set mapping within a CLB. Resets that are undriven do not form part of the control set as the tie off is generated locally within the slice. However, it is good practice to limit unique control sets to give maximum flexibility in placement of a group of logic.

#### Resets

Resets are one of the more common and important control signals to take into account and limit in your design. Resets can significantly impact your design's performance, area, and power.

Inferred synchronous code may result in resources such as:

- LUTs

- Registers

- Shift Register LUTs (SRLs)

- Block or LUT Memory

- DSP48 registers

The choice and use of resets can affect the selection of these components, resulting in less optimal resources for a given design. A misplaced reset on an array can mean the difference between inferring one block RAM, or inferring several thousand registers.

Asynchronous resets described at the input or output of a multiplier might result in registers placed in the slice(s) rather than the DSP block. In these and other situations, the amount of resources is impacted. Overall power and performance can also be significantly impacted. In most cases, this impacts performance. It also has a negative impact on device utilization and power consumption.

#### When and Where to Use a Reset

Xilinx devices have a dedicated global set/reset signal (GSR). This signal sets the initial value of all sequential cells in hardware at the end of device configuration.

If an initial state is not specified, sequential primitives are assigned a default value. In most cases, the default value is zero. Exceptions are the FDSE and FDPE primitives that default to a logic one. Every register will be at a known state at the end of configuration. Therefore, it is not necessary to code a global reset for the sole purpose of initializing a device on power up.

Xilinx highly recommends that you take special care in deciding when the design requires a reset, and when it does not. In many situations, resets might be required on the control path logic for proper operation. However, resets are generally less necessary on the data path logic. Limiting the use of resets:

- Limits the overall fanout of the reset net.

- Reduces the amount of interconnect necessary to route the reset.

- Simplifies the timing of the reset paths.

- Results in many cases in overall improvement in performance, area, and power.

**RECOMMENDED:** Evaluate each synchronous block, and attempt to determine whether a reset is required for proper operation. Do not code the reset by default without ascertaining its real need.

Functional simulation should easily identify whether a reset is needed or not.

For logic in which no reset is coded, there is much greater flexibility in selecting the FPGA resources to map the logic.

The synthesis tool can then pick the best resource for that code in order to arrive at a potentially superior result by considering, for example:

- Requested functionality

- Performance requirements

- Available device resources.

- Power

## Synchronous Reset vs. Asynchronous Reset

If a reset is needed, Xilinx recommends code synchronous resets. Synchronous resets have many advantages over asynchronous resets.

- Synchronous resets can directly map to more resource elements in the FPGA device architecture.

- Asynchronous resets also impact the performance of the general logic structures. As all

Xilinx FPGA general-purpose registers can program the set/reset as either

asynchronous or synchronous, it can be perceived that there is no penalty in using

asynchronous resets. That assumption is often wrong. If a global asynchronous reset is

used, it does not increase the control sets. However, the need to route this reset signal

to all register elements increases timing complexity.

- If using asynchronous reset, remember to synchronize the deassertion of the asynchronous reset.

- Synchronous resets give more flexibility for control set remapping when higher density

or fine tuned placement is needed. A synchronous reset may be remapped to the data

path of the register if an incompatible reset is found in the more optimally placed Slice.

This can reduce wire length and increase density where needed to allow proper fitting

and improved performance.

- Asynchronous resets might require multi-cycle assertion to ensure a circuit is properly reset and stable. When properly timed, synchronous resets do not have this requirement.

- Use synchronous resets if asynchronous resets have a greater probability of upsetting memory contents to BRAMs, LUTRAMs, and SRLs during reset assertion.

- Some resources such as the DSP48 and block RAM have only synchronous resets for the register elements within the block. When asynchronous resets are used on register elements associated with these elements, those registers may not be inferred directly into those blocks without impacting functionality.

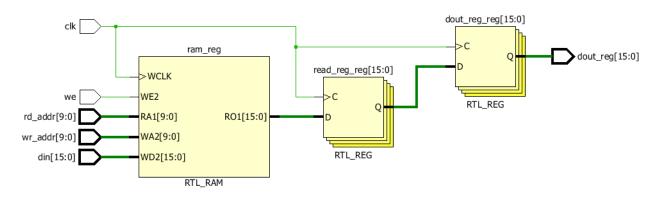

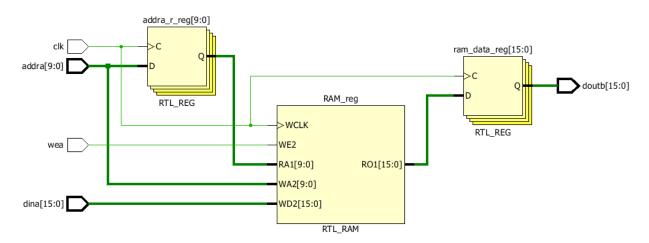

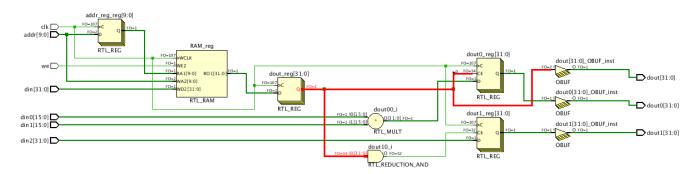

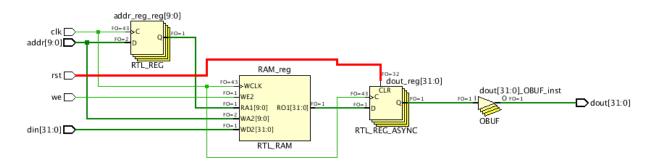

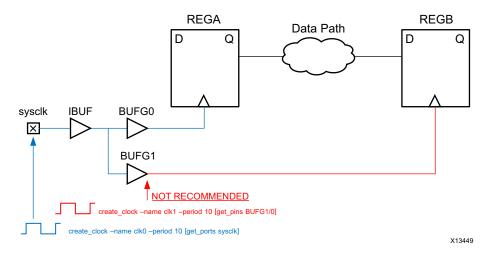

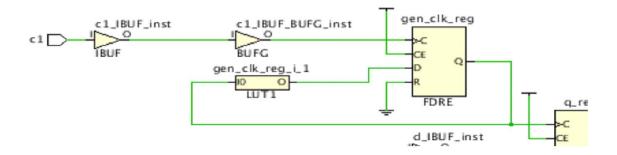

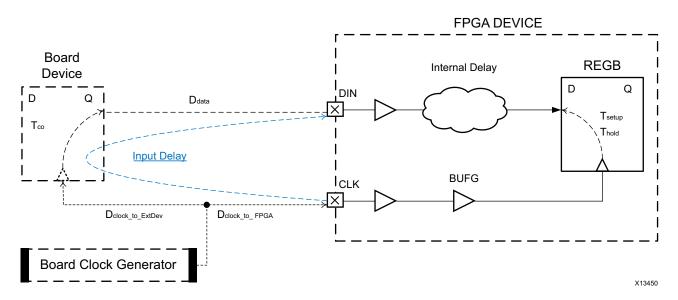

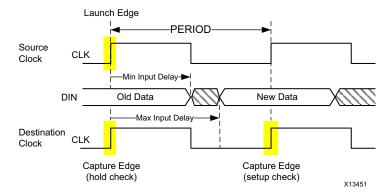

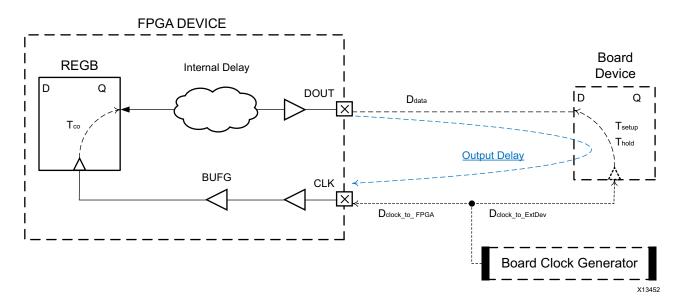

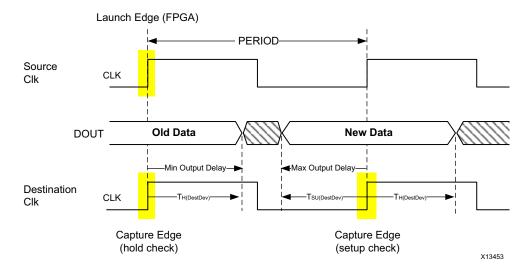

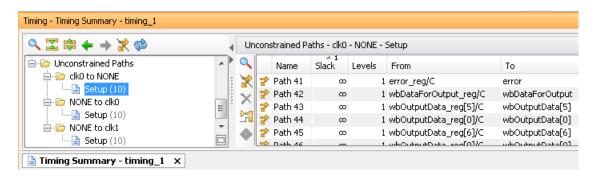

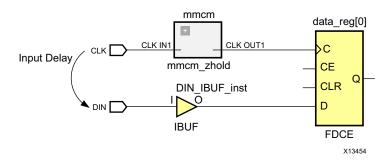

#### Reset Coding Example One: Multiplier with Asynchronous Reset