# **Design Preservation Tutorial**

PlanAhead Design Tool

UG747 (v14.1) April 24, 2012

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development of designs to operate with Xilinx hardware devices. You might not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that might be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU "AS-IS" WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© Copyright 2011 Xilinx Inc. All Rights Reserved. XILINX, the Xilinx logo, the Brand Window and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners. The PowerPC name and logo are registered trademarks of IBM Corp., and used under license. All other trademarks are the property of their respective owners.

# **Table of Contents**

| Software Requirements                                                            | 4  |

|----------------------------------------------------------------------------------|----|

| Hardware Requirements                                                            | 4  |

| Tutorial Design Description                                                      | 4  |

| Step 1: Opening an Existing PlanAhead RTL Project and Elaborating the RTL Design | 6  |

| Step 2: Setting Partitions and Drawing Pblocks                                   | 8  |

| Step 3: Synthesizing and Implementing the Design                                 | 12 |

| Step 4: Promoting Successfully Implemented Partitions                            | 17 |

| Step 5: Modifying the RTL for Top                                                | 21 |

| Step 6: Rerunning Synthesis and Implementation While Importing                   | 23 |

| Conclusion                                                                       | 25 |

### **Design Preservation Tutorial**

This tutorial provides an overview of the design preservation flow. In this tutorial, you will:

- Define partitions and Pblocks on an elaborated Register Transfer Level (RTL) design.

- Synthesize using the Xilinx® Synthesis Technology (XST) incremental synthesis software.

- Implement the partitioned design.

- Promote successful implementation results.

- Update the top-level partition.

- Rerun synthesis and implementation on the modified top level while importing the unchanged partitions.

The objective of this tutorial is to familiarize you with the partitions and the design preservation flow using the PlanAhead design tool. Many of the PlanAhead tool analysis features are covered in more detail in other tutorials, and not every command or command option is covered.

#### **Software Requirements**

The PlanAhead tool installs with the ISE® Design Suite software. Before starting the tutorial, ensure that the PlanAhead tool is operational, and that the tutorial design data is installed.

For installation instructions and information, see the *ISE Design Suite: Installation and Licensing Guide (UG798)* at <a href="http://www.xilinx.com/support/documentation/sw">http://www.xilinx.com/support/documentation/sw</a> manuals/xilinx14 1/iil.pdf.

#### **Hardware Requirements**

Xilinx recommends a minimum of 2 GB of RAM when using the PlanAhead tool on larger devices. For this tutorial, a smaller xc7k70t design is used, and the number of designs open at one time is limited. Although 1 GB is sufficient, it can impact performance.

#### **Tutorial Design Description**

The design used throughout this tutorial contains:

A RISC processor

- FFTs

- Gigabit transceivers

- Two USB port modules (to be partitioned)

- An xc6vlx75t device

A small design is used to allow the tutorial to be run with minimal hardware requirements and to enable timely completion, as well as to minimize the data size.

Download the PlanAhead\_Tutorial.zip file from the Xilinx website:

http://www.xilinx.com/support/documentation/dt\_planahead\_14-1\_tutorials.htm

Extract the zip file contents into any write-accessible location.

The unzipped PlanAhead\_Tutorial data directory is referred to in this tutorial as <Extract\_Dir>.

The tutorial sample design data is modified while performing this tutorial. A new copy of the original PlanAhead\_Tutorial data is required each time you run the tutorial.

# Step 1: Opening an Existing PlanAhead RTL Project and Elaborating the RTL Design

This tutorial uses pre-existing PlanAhead tool projects to simplify the steps and focus on the design preservation aspects of the tutorial. For a real design, you would use the New Project Wizard to create either an RTL or netlist based project. The PlanAhead tool (v. 13.1 or newer) supports RTL projects with partitions.

#### Opening an Existing PlanAhead tool RTL Project

To open an existing PlanAhead tool RTL project:

- 1. Open the PlanAhead tool.

- On Windows, double-click the Xilinx® PlanAhead 13 Desktop icon, or select:

# Start > All Programs > Xilinx Design Tools > ISE Design Suite 14.1 > PlanAhead > PlanAhead

- On Linux, go to the <Extract\_Dir> directory and type **PlanAhead**:

- 2. From the Getting Started page, click **Open Project**.

- 3. In the <Extract\_Dir> directory, open the project file located at:

- ./Projects/project\_DP\_RTL/project\_DP\_RTL.ppr

#### **Viewing Source Files**

When the project opens, the Project Manager view is visible. You can view the following design files in the Sources window:

- VHDL source files

- Verilog source files

- A User Constraints File (UCF) named top\_full.ucf. This file contains timing constraints and I/O pin locations.

#### **Elaborating an RTL Design**

You must use the Elaborated Design view to define partitions in an RTL project. When the Elaborated Design view is opened:

- The RTL code is elaborated.

- The design hierarchy is displayed.

Use this pre-synthesized view of the design to define partitions and create constraints.

To elaborate an RTL design:

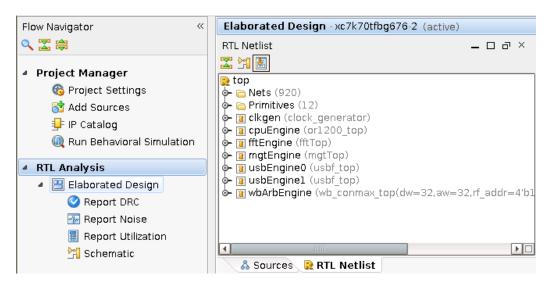

Select Flow > New Elaborated Design, or click Open Elaborated Design in the Flow Navigator.

Figure 1: Opening the Elaborated Design view

#### **Step 2: Setting Partitions and Drawing Pblocks**

Because the **usbEngine** instances have already been identified as timing-critical modules, it would be advantageous to preserve the successful implementation results of these instances. However, this fact alone does not make these instances good candidates for partitions.

The **usbEngine** instances are good choices for partitions because:

- They are logically isolated from the rest of the design.

- They have reasonable interface timing (registered inputs and outputs).

Use DRCs to help identify whether or not a module is a good choice for partitions. For more information on how to choose good module instances for partitioning, see *the Hierarchical Design Methodology Guide (UG748)*.

You can floorplan partitioned instances like any other instances. Creating Pblock (AREA\_GROUP) constraints can help achieve timing closure and improve runtime. The UCF provided with this tutorial constrains the I/O logic of the **usbEngine** along the left side of the device. The steps below show you how to create appropriate Pblock constraints for the two **usbEngine** instances.

#### **Setting Partitions for the two usbEngine Instances**

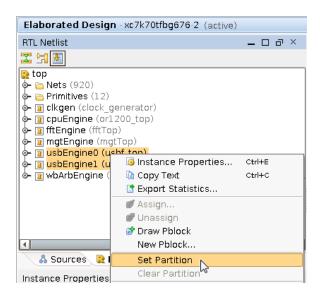

To set partitions for the two **usbEngine** instances:

- 1. From the Elaborated Design view, select the two **usbEngine** instances from the RTL Netlist tab.

- 2. Right-click.

- 3. Select Set Partition.

Figure 2: Setting Partitions on usbEngine Instances

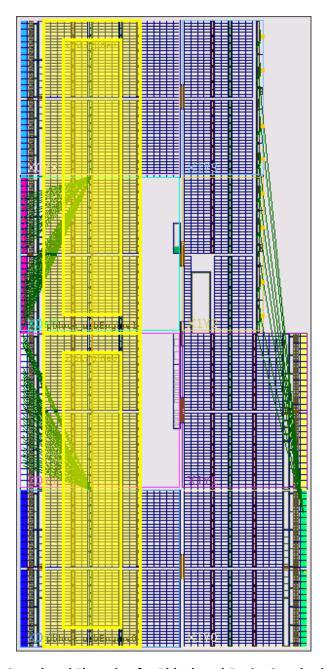

#### **Drawing Pblocks for the Two usbEngine Instances**

This step does not affect synthesis results, so it could also be done post-synthesis in the Synthesized Design view. There are some advantages to doing so, such as resource estimation to help size the Pblocks. However, for this tutorial it will be done from the Elaborated Design view.

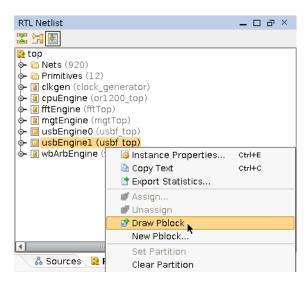

To draw Pblocks for the two **usbEngine** instances:

- 1. From the RTL Netlist window, select usbEngine1.

- 2. Right-click and select Draw Pblock.

Figure 3: Selecting the Draw Pblock Tool

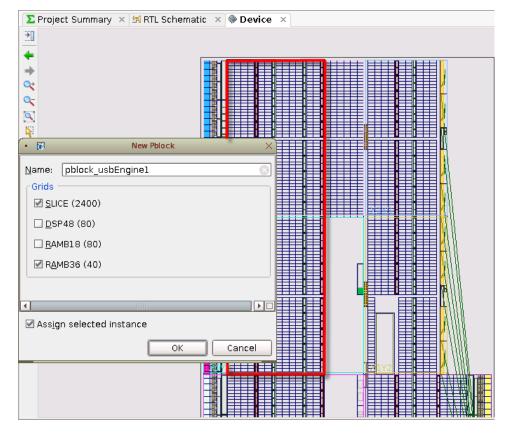

- 3. With the Draw Pblock tool active, move the cursor to the Device window.

- 4. Left click the top-left corner of the device where the CLB components start.

- 5. Without releasing the left mouse button, drag to create a rectangle covering most of the top-left quadrant of the device. See the figure below (*Pblock Rectangle for usbEngine1*).

- 6. In the New Pblock dialog box, verify that the SLICE and RAMB36 grids are selected.

- 7. Deselect other resources that are not needed. See the figure below (*Pblock Rectangle for usbEngine1*).

- 8. Verify that the number of available RAMB36 components (shown in parentheses) is 40. If the rectangle does not fully cover the region shown in the figure below (*Pblock Rectangle for usbEngine0*), the number of available RAMB36 may be less, and the design may fail to place.

Figure 4: Pblock Rectangle for usbEngine1

- 9. Click **OK**.

- 10. Repeat the steps above for **usbEngine0** on the bottom-left quadrant. See the figure below (*Completed floorplan*) for the final Pblock ranges.

Figure 5: Completed Floorplan for Pblocks usbEngine0 and usbEngine1

#### Step 3: Synthesizing and Implementing the Design

Now that all partitions have been defined, and all necessary constraints have been created, you can run synthesis and implementation. Because partitions were defined in the elaborated Hardware Description Language (HDL) design, XST does the following:

- Detects the partitions

- Runs incremental flow

- Creates an individual NGC file for each defined partition

#### **NGC Files**

The individual NGC files for each defined partition are uniquely named. Unique naming allows multiple instances of a module to be synthesized with different parameters. In this case, synthesis generates the following NGC files in the cproject\_name>.runs/synth\_1 directory:

- top.ngc

- usbEngine0#usbf\_top.ngc

- usbEngine1#usbf\_top.ngc

#### Running Synthesis outside the PlanAhead tool

If you prefer a bottom-up synthesis, or a third party incremental synthesis flow, run synthesis outside the PlanAhead tool.

Use a PlanAhead netlist project instead of the RTL project shown in this tutorial.

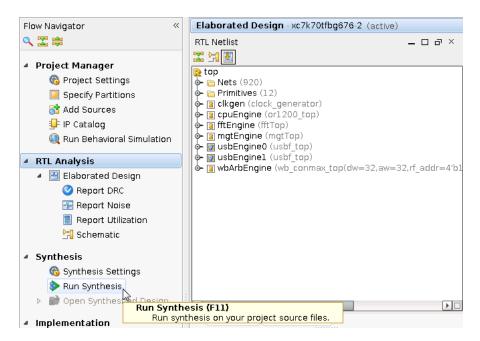

#### Running Synthesis in the PlanAhead tool

To run synthesis in the PlanAhead tool:

- 1. First check the settings on the partitions. Click **Specify Partitions** under **Project Manager** in the Flow Navigator. These current settings are correct, so click **OK**.

- 2. Click **Run Synthesis** in the Flow Navigator pane.

**Figure 6: Launch XST Incremental Synthesis**

- 3. Click Save.

- 4. When synthesis completes a dialog will appear with several options. Choose **Open Synthesized Design** and click **OK**.

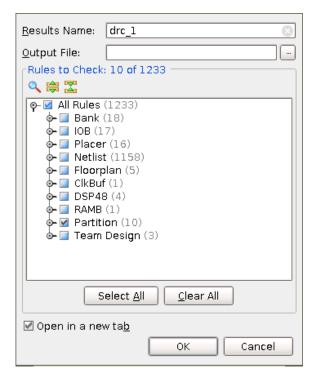

#### **Running a DRC on Partitions**

While you can run a Design Rule Check (DRC) on the Elaborted Design, there are limitations on the parameters that the software can check at this stage. Xilinx recommends that you run a DRC before launching implementation. To run a DRC, load the Synthesized Design view and run partition-specific DRCs.

To run a DRC on partitions:

1. Click **Syntheized Design** to open the view if not already open.

Opening the Synthesized Design view loads the synthesis results and allows for additional DRC checking.

- 2. In the Flow Navigator under **Synthesized Design**, click **Report DRC** (or select **Tools > Report DRC**).

- 3. From the Report DRC dialog box, deselect all rules except **Partition**.

**Figure 7: Report Partition Design Rule Check**

#### 4. Click **OK**.

#### **DRC Advisory Messages**

The DRC returns minor Advisory messages. The PlanAhead tool can report the following message types for the DRC rules:

- Advisory

- Warning

- Error

- Fatal

Ignore the Advisory messages for this tutorial. In an actual design, investigate all DRC messages, and correct any serious issues.

#### Running Implementation in the PlanAhead tool

You are now ready to run implementation in the PlanAhead tool. To implement this design with partitions, the only additional steps required were to:

- Define the partitions.

- Run a DRC check.

Because this design was already created with hierarchy in mind, you did not have to alter the design to make it work with partitions.

However, the bulk of the work required to make a partition design successful is at the RTL design stage, and not with the synthesis or implementation tools. For recommendations for good hierarchical design, see the *Hierarchical Design Methodology Guide (UG748)*.

#### Skipping Implementation

To remove the implementation runtime from this tutorial, a completed project with synthesis and implementation results can be found at:

<Extract\_Dir>/Projects/project\_DP\_RTL\_implemented/project\_DP\_RTL\_imple

mented.ppr

Select **File > Open Project** to skip this step and open the completed results.

If you skip this step, go to Step 4: Promoting Successfully Implemented Partitions.

#### **Running Implementation**

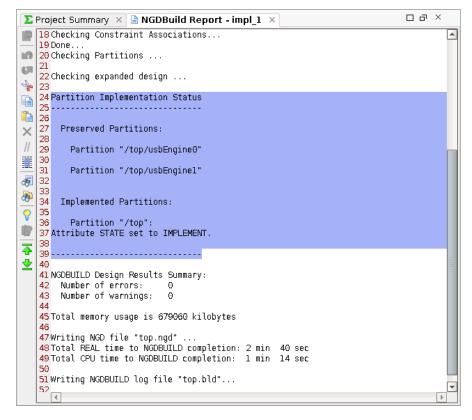

To run implementation in the PlanAhead tool:

- 1. In the Flow Navigator, click **Run Implementation**.

- 2. Click the **Report** tab to see a list of implementation reports. Each report is available as the process finishes.

- 3. After NGDBuild finishes, double-click **NGDBuild Report**.

- 4. Scroll to the bottom of the report to view the partition information.

**Figure 8: Implementation Status in Report Files**

#### This partition information:

- Appears in every report (NGDBuild, Map, and PAR)

- Allows you to verify the status of all partitions on a given run easily

### **Step 4: Promoting Successfully Implemented Partitions**

Once an implementation is successful, you can promote the results. Promoting the results makes a copy of the implementation directory in:

```

project_name>.promote\X<run_name>

```

For example:

project\_DP\_RTL.promote\Ximpl\_1

The PlanAhead tool:

- Keeps track of the latest promoted run.

- Changes the state and import location of any promoted partitions.

You can also manage these processes manually.

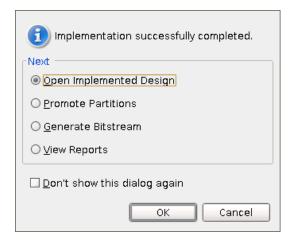

#### **Promoting the Successful Implementation Results**

After implementation has completed, the Implementation Completed dialog box opens.

Figure 9: Implementation Completed Dialog Box

To promote the successful implementation results:

1. Select Open Implemented Design and click **OK**.

Other options are also available. For example, you could promote the results by selecting **Promote Partitions** option. However, this tutorial uses another method to promote the results.

If the Implementation Completed dialog box did not open, or if you opened the completed project **project\_DP\_RTL\_implemented**, load the results by clicking **Open Implemented Design** in the Flow Navigator.

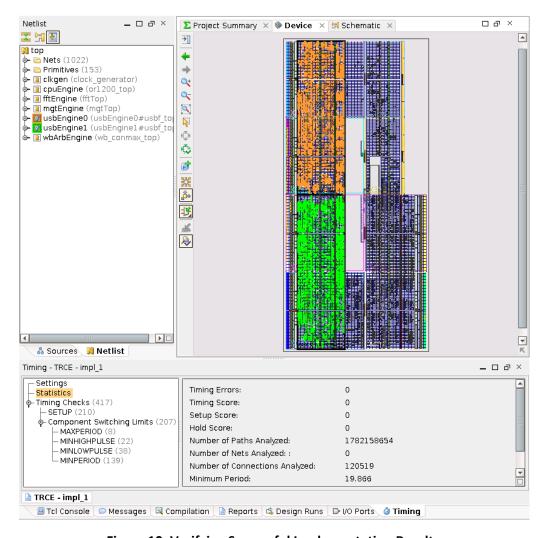

- 2. To verify that the results were successful, review the final timing score and the detailed timing report. See the figure below (*Verifying Successful Implementation Results*).

- The timing score is **0**.

- The number of timing errors is **0**.

The following figure (*Verifying Successful Implementation Results*) highlights the placed primitives of the two **usbEngine** instances. This shows that the placement was controlled by the AREA\_GROUP constraints.

Figure 10: Verifying Successful Implementation Results

- 3. To highlight the primitives of the two **usbEngine** instances as shown above:

- a) Select the two instances in the Netlist view.

- b) Right-click.

- c) Select **Highlight Primitives** → Cycle Colors.

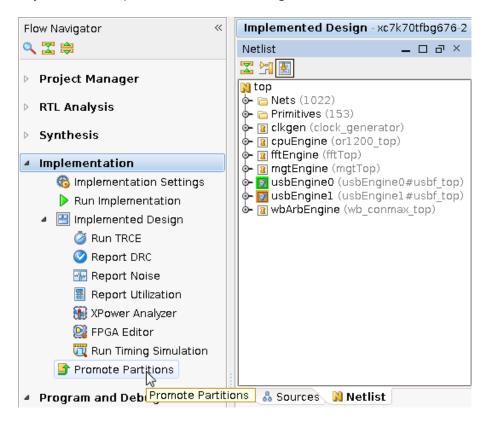

4. In the Flow Navigator, click **Promote Partitions** to promote the synthesis and implementation results. See the figure below (*Promote Partitions*).

If the Elaborated Design view is not open when you try to promote, then click **OK** when you are asked if you want to open the Elaborated Design view.

**Figure 11: Promote Partitions**

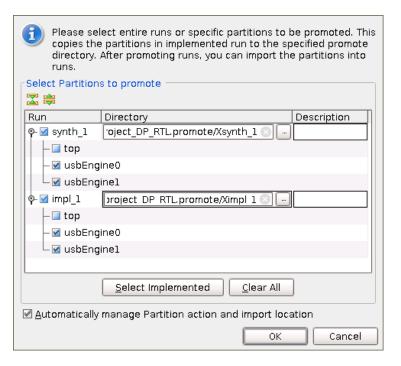

- 6. Verify that the two **usbEngine** module instances are checked for promoting for both synthesis and implementation. See the figure below (*Promote Partitions Dialog Box*).

- The top-level partition is not selected by default. However, you can promote this partition like any other partition. For this tutorial, since you update the Top partition, there is no need to promote it now.

- 7. Click **OK** to promote the two **usbEngine** partitions.

- 8. Enter a description about the promoted data (optional).

- 9. Verify that Automatically Manage Partition Action and Import Location is checked.

- Checking **Automatically Manage Partition Action and Import Location** allows the PlanAhead tool to update the partition state to import location for the next synthesis and implementation run. If this option is not checked, you must manage these attributes yourself.

**Figure 12: Promote Partitions Dialog Box**

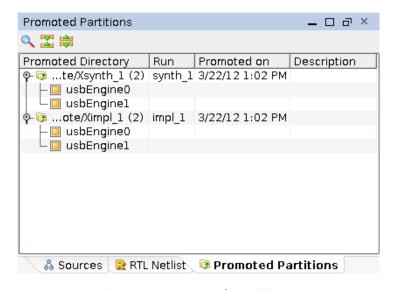

- 10. Review the changes caused by promoting partitions. See the figure below (*Promoted Partitions*).

- In the Elaborated Design view, you can see a Promoted Partitions tab.

- The Specify Partitions dialog now shows the Action on the usbEngine instances as

Import. The Specify Partitions dialog can be accessed from the Project Manager section

of the Flow Navigator, or from the Implemented Partitions section of the Project

Summary.

**Figure 13: Promoted Partitions**

#### **Step 5: Modifying the RTL for Top**

Now that you have promoted the successful synthesis and implementation results, you now make a change to the design. Such a change could be, for example, a new feature, a bug fix, or a pipeline register.

This tutorial makes a simple change to a module belonging to the Top partition. You then resynthesize and re-implement on the changed partitions (in this case Top), while preserving the two timing-critical **usbEngine** partitions.

#### **Changing the Verilog File**

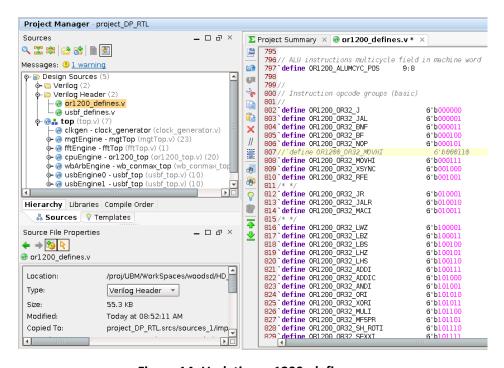

To change the Verilog file or1200\_defins.v

- 1. Click **Project Manager** in the Flow Navigator to open the Project Manager view.

- 2. From the Hierarchy tab expand the **Verilog Header** folder, and locate or1200\_defines.v as shown in the figure below (*Updating or1200\_defines.v*).

- 3. Double-click or1200\_defines.v to open it in the text editor.

Figure 14: Updating or1200\_defines.v

4. Insert two slashes (//) at the beginning of the line to comment out line 807.

```

//`define OR1200 OR32 MOVHI 6'b000110

```

5. Remove the two slashes (//) at the beginning of the line to uncomment line 808.

`define OR1200\_OR32\_MOVHI 6'b000111

6. Right-click in the editor, and select **Save File**.

**Synthesis & Implementation Out-of-Date** appears in the upper right hand corner. The software recognizes that:

- A source file has been modified.

- The current synthesis and implementation results do not reflect the latest version of the design.

# **Step 6: Rerunning Synthesis and Implementation While Importing**

You have now:

- Defined partitions

- Defined Pblocks

- Synthesized and implemented the design

- Promoted the two usbEngine instances

- Made a change to the top-level partition

You can now re-implement the modified top-level partition while maintaining an exact copy of the placement and routing results on the two USB cores.

#### **Skipping Implementation**

To remove the implementation runtime from this tutorial, a completed project with synthesis and implementation results can be found at:

<Extract\_Dir>/Projects/project\_DP\_RTL\_implemented/project\_DP\_RTL\_imple

mented.ppr

Select **File > Open Project** to skip this step and open the completed results.

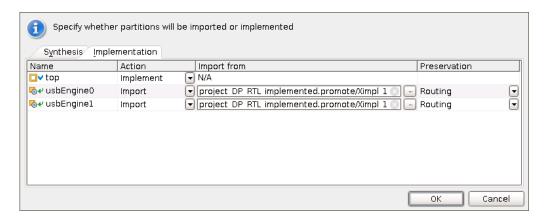

#### **Verifying the Synthesis and Implementation Partition Attributes**

To verify the synthesis partition attributes:

- 1. From the Flow Navigator, click the **Specify Partitions** button under Project Manager.

- 2. Verify in both the Synthesis and Implementation tabs:

- The top-level partition is set to Implement.

- The two usbEngine partitions are set to Import.

- 3. Click **OK**.

**Figure 15: Verifying Partitions Attributes**

#### **Running Synthesis and Implementation**

To run synthesis and implementation:

- 1. In the Flow Navigator, click **Run Implementation** to launch the implementation run.

- 2. Because Synthesis is out of date, you are prompted to launch synthesis first. Click **Yes** to launch synthesis and implementation.

- 3. Review the Partition Status section in the NGDBuild, Map, and PAR reports to verify that:

- The two **usbEngine** partitions are imported.

- All timing constraints are met.

Figure 16: Partition Implementation Status in Report Files

#### **Conclusion**

In this tutorial, you did the following:

- Defined partitions.

- Created Pblock constraints.

- Ran synthesis and implementation.

- Verified that timing was met.

- Promoted the successful results to allow for importing in future iterations.

The top module was updated. This required synthesis and implementation to be re-run. Because the USB cores were not modified, they were imported and maintained identical placement and routing results.

The output guaranteed timing results on two large, timing-critical cores for all future iterations of the design (assuming no changes to the **usbEngine** instances).