# XAUI v12.2

# LogiCORE IP Product Guide

Vivado Design Suite

PG053 October 5, 2016

# **Table of Contents**

### **IP Facts**

### **Chapter 1: Overview**

| Additional Features                | . 6 |

|------------------------------------|-----|

| About the Core                     | . 6 |

| Recommended Design Experience      | . 7 |

| Applications                       | . 7 |

| Licensing and Ordering Information | . 8 |

| Feedback                           | . 8 |

### **Chapter 2: Product Specification**

| Standards Compliance | 10 |

|----------------------|----|

| Performance          | 10 |

| Resource Utilization | 11 |

| Verification         | 11 |

| Port Descriptions    | 12 |

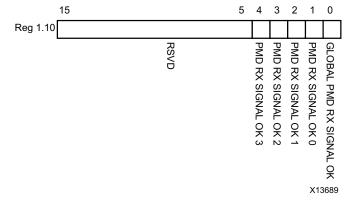

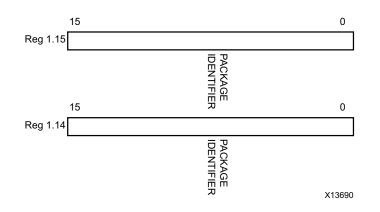

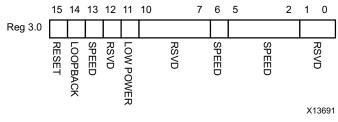

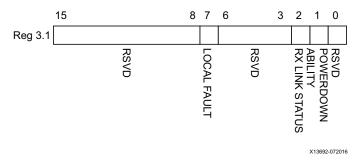

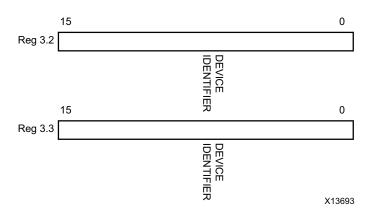

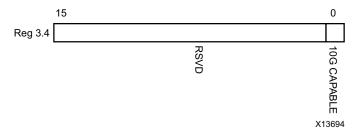

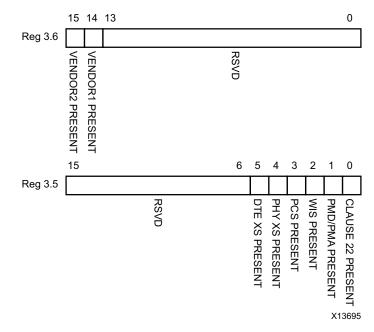

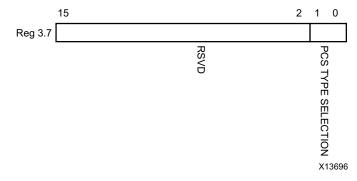

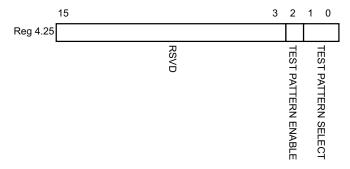

| Register Space       | 30 |

### **Chapter 3: Designing with the Core**

| General Design Guidelines                                    | 62 |

|--------------------------------------------------------------|----|

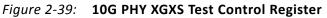

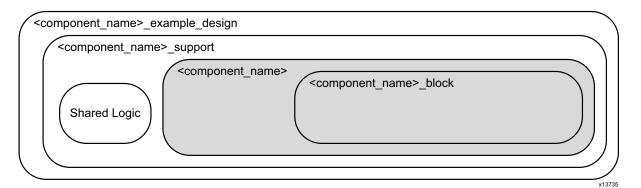

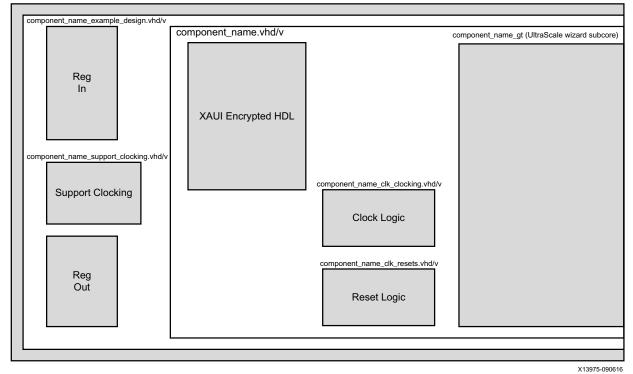

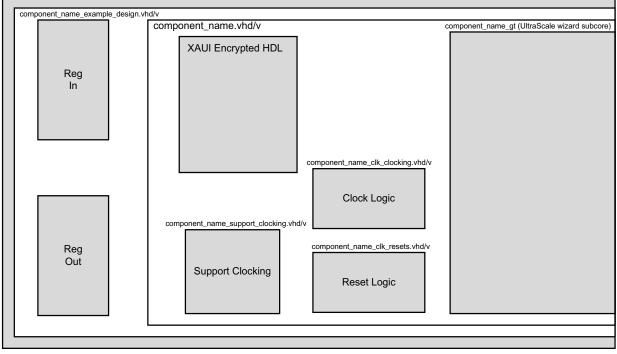

| Shared Logic                                                 | 63 |

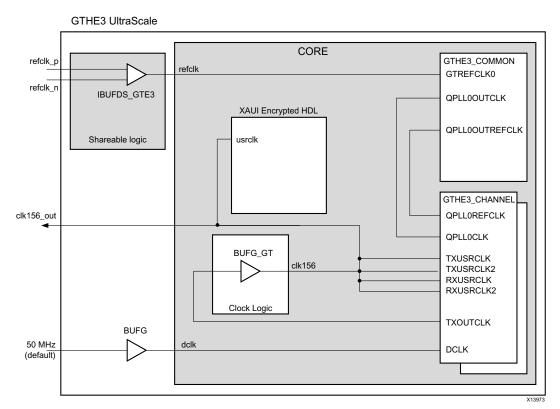

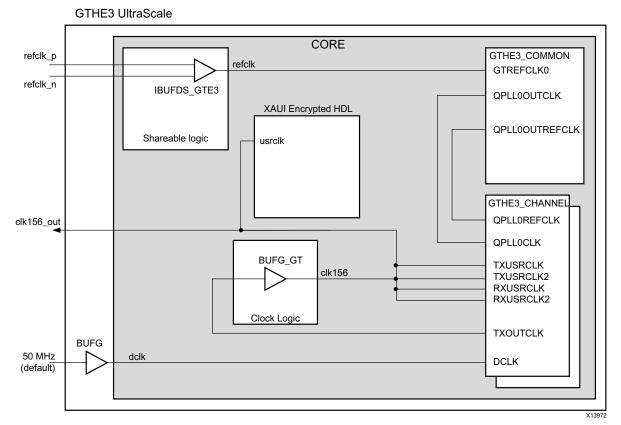

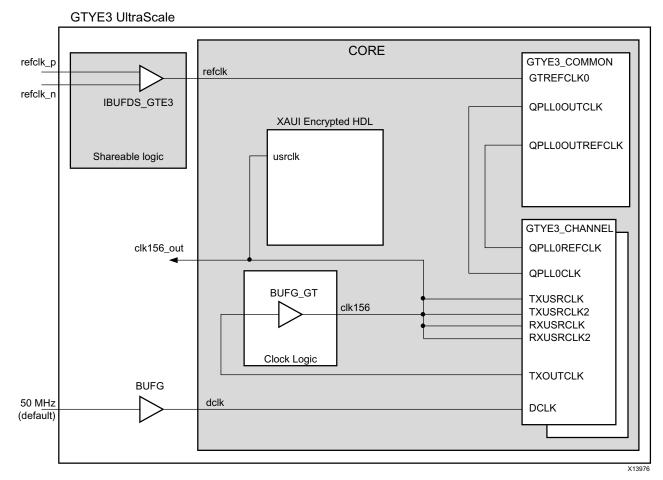

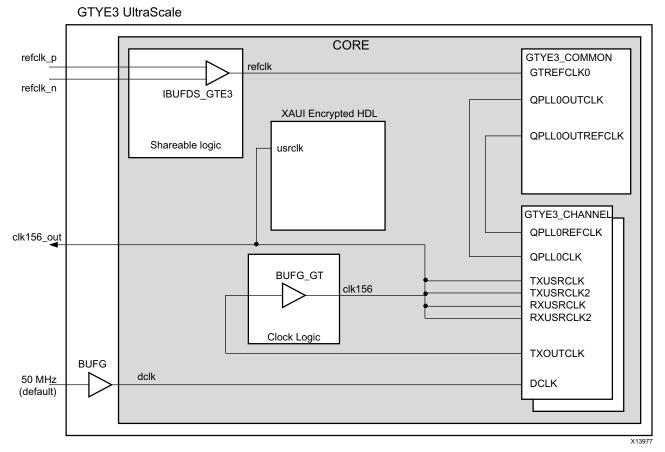

| Clocking: UltraScale Architecture                            | 64 |

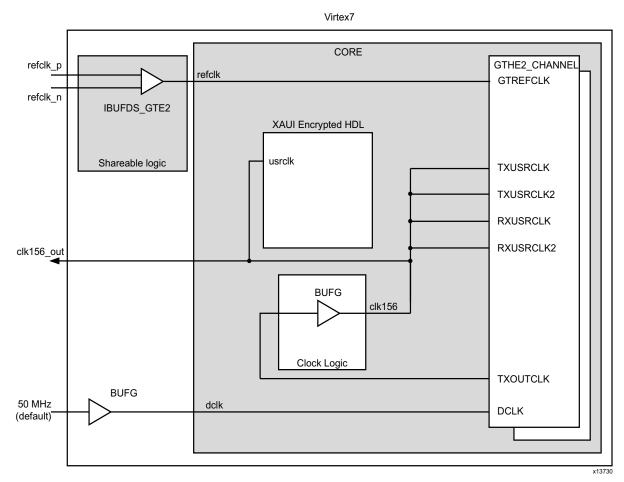

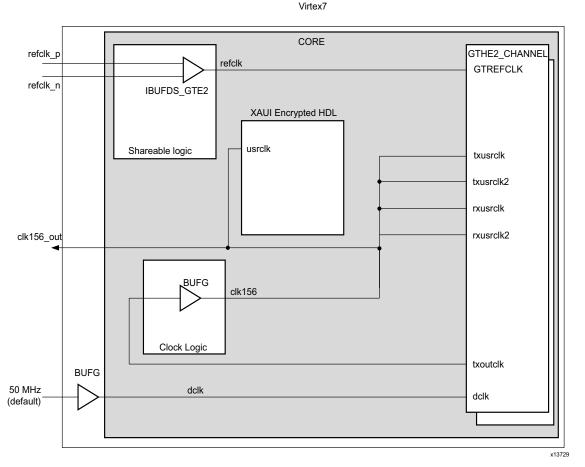

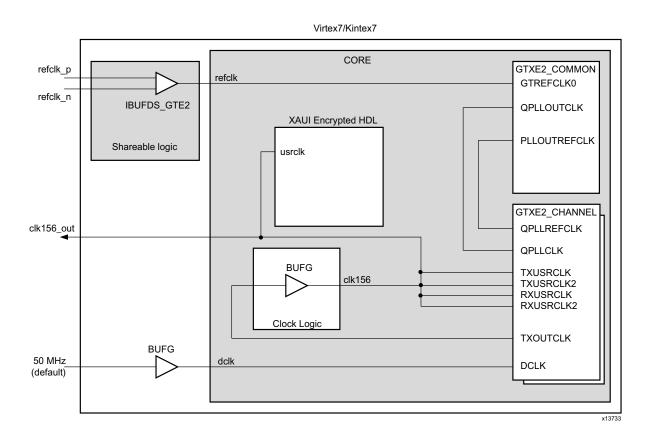

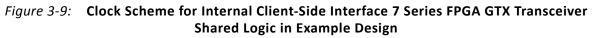

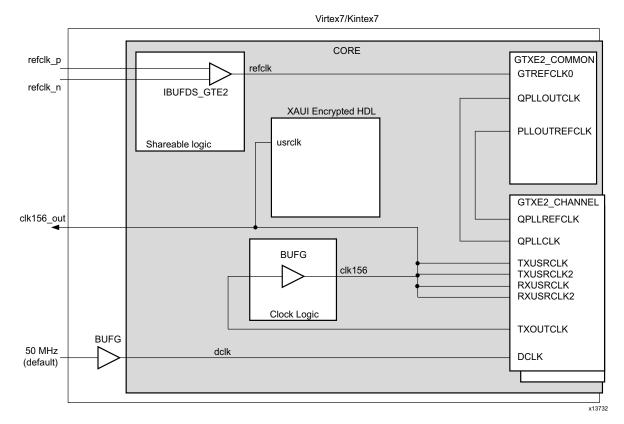

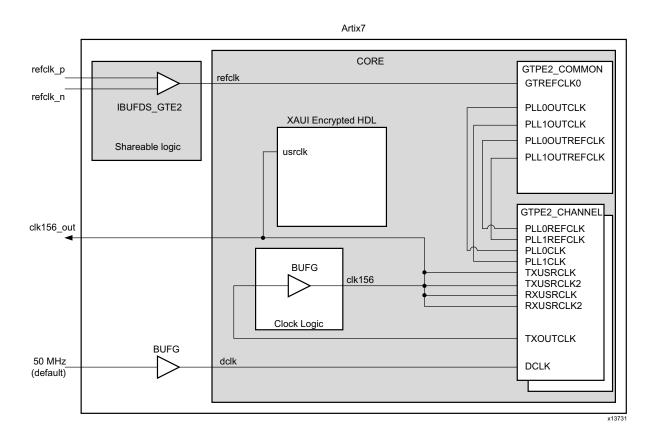

| Clocking: Zynq-7000, Virtex-7, Artix-7, and Kintex-7 Devices | 69 |

| Multiple Core Instances                                      | 76 |

| Reset Circuits                                               | 76 |

| Receiver Termination: Virtex-7 and Kintex-7 FPGAs            | 76 |

| Transmit Skew                                                | 76 |

| Data Interface: Internal XGMII Interfaces                    | 77 |

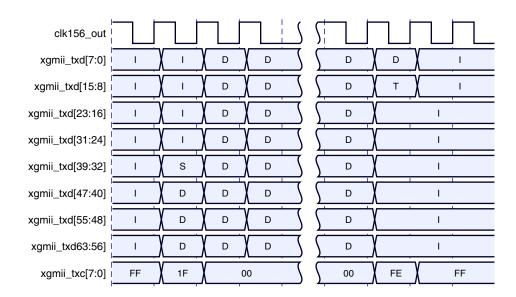

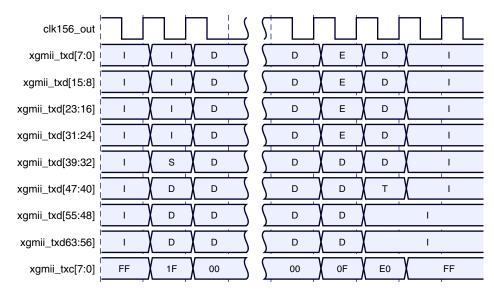

| Interfacing to the Transmit Client Interface                 | 78 |

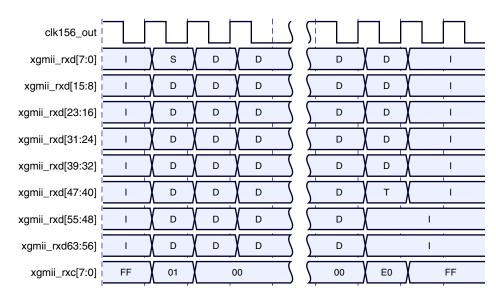

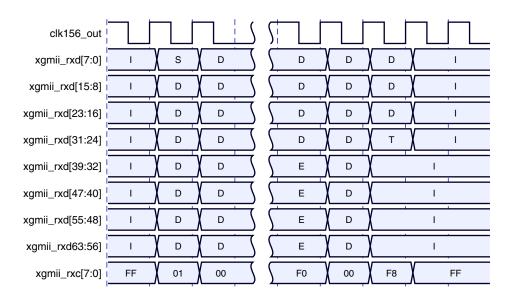

| Interfacing to the Receive Client Interface                  | 79 |

| Configuration and Status Interfaces                          | 80 |

| MDIO Interface                                               | 80 |

| Configuration and Status Vectors                             | 84 |

| Debug Port                                                   | 86 |

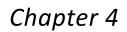

### **Chapter 4: Design Flow Steps**

| Customizing and Generating the Core | 87 |

|-------------------------------------|----|

| Output Generation                   | 91 |

| Constraining the Core               | 91 |

| Simulation                          | 94 |

| Synthesis and Implementation        | 94 |

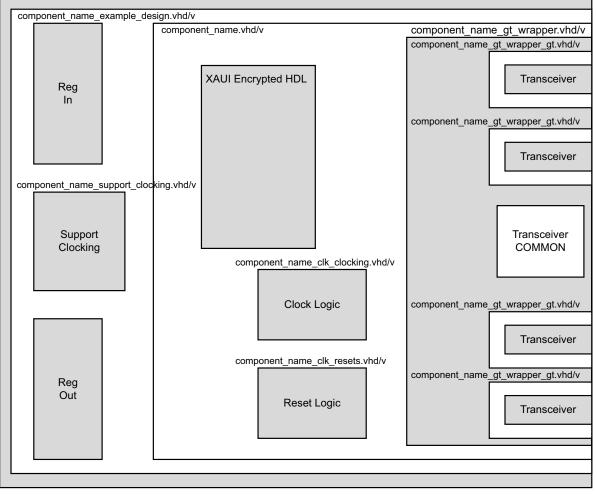

### **Chapter 5: Example Design**

### Chapter 6: Test Bench

#### **Appendix A: Verification and Interoperability**

| Simulation       | 101 |

|------------------|-----|

| Hardware Testing | 101 |

### Appendix B: Migrating and Upgrading

| Device Migration                     | 102 |

|--------------------------------------|-----|

| Migrating to the Vivado Design Suite | 102 |

| Upgrading in the Vivado Design Suite | 102 |

### **Appendix C: Debugging Designs**

| Finding Help on xilinx.com | 108 |

|----------------------------|-----|

| Technical Support          | 109 |

| Debug Tools                | 109 |

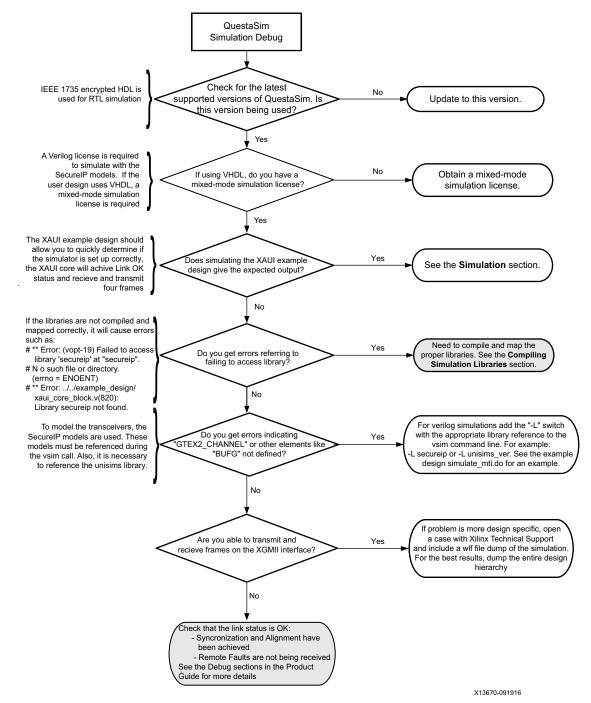

| Simulation Specific Debug  | 110 |

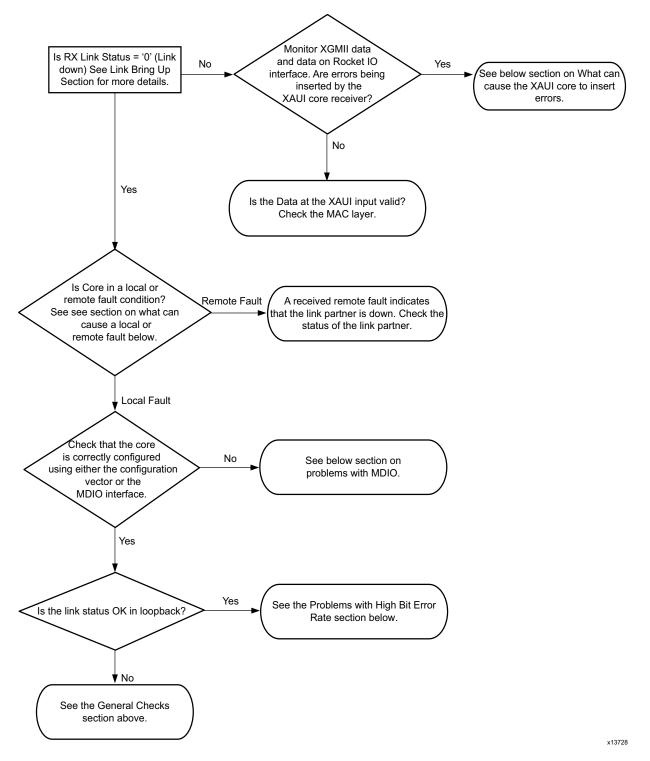

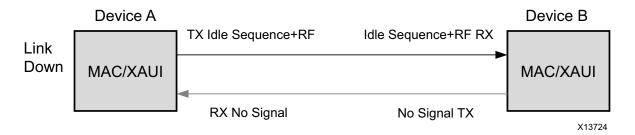

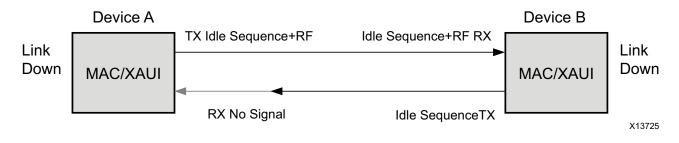

| Hardware Debug             | 111 |

### Appendix D: Additional Resources and Legal Notices

| Xilinx Resources                     | 120 |

|--------------------------------------|-----|

| References                           | 120 |

| Additional Core Resources            | 121 |

| Revision History                     | 121 |

| Please Read: Important Legal Notices | 123 |

# Introduction

The Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP eXtended Attachment Unit Interface (XAUI) core is a high-performance, low-pin count 10 Gb/s interface intended to allow physical separation between the data link layer and physical layer devices in a 10 Gigabit Ethernet system.

The XAUI core implements a single-speed full-duplex 10 Gb/s Ethernet eXtended Attachment Unit Interface (XAUI) solution for the UltraScale+, UltraScale, Zynq-7000 All Programmable SoC, and 7 series devices.

# Features

- Designed to 10 Gigabit Ethernet *IEEE* 802.3-2012 specification

- Supports 20G double-rate XAUI (Double XAUI) using four transceivers at 6.25 Gb/s.

For devices and speed grades, see Speed Grades.

- Uses four transceivers at 3.125 Gb/s line rate to achieve 10 Gb/s data rate

- Implements Data Terminal Equipment (DTE) XGMII Extender Sublayer (XGXS), PHY XGXS, and 10GBASE-X Physical Coding Sublayer (PCS) in a single netlist

- *IEEE 802.3-2012* clause 45 Management Data Input/Output (MDIO) interface (optional)

- IEEE 802.3-2012 clause 48 State Machines

- Available under the <u>Xilinx End User License</u>

<u>Agreement</u>

| LogiCORE IP Facts                                 |                                                                                        |  |  |  |

|---------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|

| Core Specifics                                    |                                                                                        |  |  |  |

| Supported Device<br>Family <sup>(1)</sup>         | UltraScale+™<br>UltraScale™<br>Zynq®-7000 All Programmable SoC<br>7 Series             |  |  |  |

| Supported User<br>Interfaces                      | 64-bit XGMII Interfac                                                                  |  |  |  |

| Resources <sup>(3)</sup>                          | Performance and Resource Utilization web page                                          |  |  |  |

|                                                   | Provided with Core                                                                     |  |  |  |

| Design Files                                      | Encrypted RTL                                                                          |  |  |  |

| Example Design                                    | VHDL and Verilog                                                                       |  |  |  |

| Test Bench                                        | VHDL Test Bench<br>Verilog Test Fixture                                                |  |  |  |

| Constraints File                                  | Xilinx Design Constraints (XDC)                                                        |  |  |  |

| Simulation Model                                  | VHDL/Verilog                                                                           |  |  |  |

| Supported S/W<br>Drivers                          | NA                                                                                     |  |  |  |

|                                                   | Tested Design Flows <sup>(4)</sup>                                                     |  |  |  |

| Design Entry                                      | Vivado® Design Suite                                                                   |  |  |  |

| Simulation                                        | Simulation For supported simulators, see th<br>Xilinx Design Tools: Release Notes Guid |  |  |  |

| Synthesis                                         | Vivado Synthesis                                                                       |  |  |  |

| Support                                           |                                                                                        |  |  |  |

| Provided by Xilinx at the Xilinx Support web page |                                                                                        |  |  |  |

#### Notes:

- 1. For a complete list of supported devices, see Vivado IP catalog. See Verification for supported speed grades.

- 2. Resource utilizations for 20 G are the same as those for 10 G.

- 3. Resource utilization depends on target device and configuration.

- 4. For the supported versions of the tools, see the <u>Xilinx Design</u> <u>Tools: Release Notes Guide</u>.

# Overview

XAUI is a four-lane, 3.125 Gb/s-per-lane serial interface. Each lane is a differential pair carrying current mode logic (CML) signaling, and the data on each lane is 8B/10B encoded before transmission. Special code groups are used to allow each lane to synchronize at a word boundary and to deskew all four lanes into alignment at the receiving end. The XAUI standard is fully specified in clauses 47 and 48 of the 10 Gigabit Ethernet *IEEE 802.3-2012* specification.

The XAUI standard was initially developed as a means to extend the physical separation possible between Media Access Controller (MAC) and PHY components in a 10 Gigabit Ethernet system distributed across a circuit board and to reduce the number of interface signals in comparison with the XGMII (10 Gigabit Ethernet Media Independent Interface).

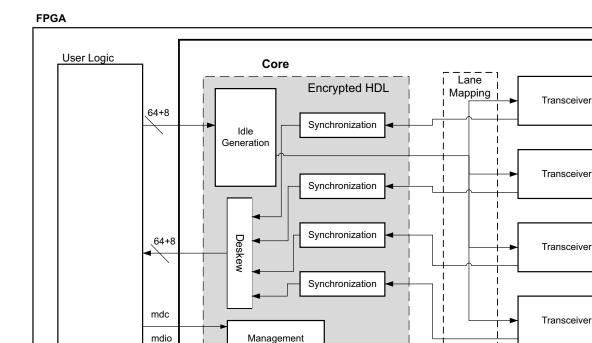

Figure 1-1 shows a block diagram of the XAUI core implementation. The major functional blocks of the core include the following:

- **Transmit Idle Generation Logic** creates the code groups to allow synchronization and alignment at the receiver.

- **Synchronization State Machine (one per lane)** identifies byte boundaries in incoming serial data.

- Deskew State Machine de-skews the four received lanes into alignment.

- **Optional MDIO Interface** is a two-wire low-speed serial interface used to manage the core.

- Four Device-Specific Transceivers (integrated in the FPGAs) provide the high-speed transceivers as well as 8B/10B encode and decode and elastic buffering in the receive datapath.

- Lane mapping: Provides mapping of individual lanes to individual transceivers as specified by parameters, XAUI Core Lane 0, XAUI Core Lane 1, XAUI Core Lane 2, and XAUI Core Lane 3.

Lane 0

Lane 1

Lane 2

Lane 3

Reference

clock

Reset

Figure 1-1: Architecture of the XAUI IP Core with Client-Side User Logic

Clocks and

Reset

Logic

# **Additional Features**

clk156\_out

# 20 Gigabit XAUI (Double XAUI) Support

By running the XAUI interface at twice the normal clock and line rates, 20 Gigabit data rate can be achieved. For devices and speed grades, see Speed Grades. Consult the release notes for the core for the specific devices supported.

# About the Core

The XAUI core is a Xilinx<sup>®</sup> Intellectual Property (IP) core, included in the latest IP Update on the Xilinx IP Center. For detailed information about the core, see the <u>XAUI product page</u>.

# **Recommended Design Experience**

Although the XAUI core is a fully-verified solution, the challenge associated with implementing a complete design varies depending on the configuration and functionality of the application. For best results, previous experience building high performance, pipelined Field Programmable Gate Array (FPGA) designs using Xilinx implementation software and Xilinx Design Constraints (XDC) is recommended.

Contact your local Xilinx representative for a closer review and estimation for your specific requirements.

# **Applications**

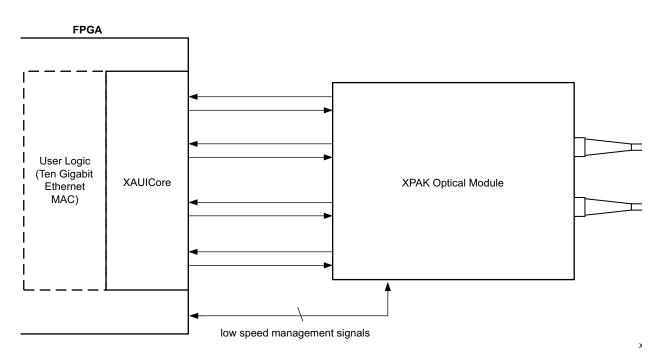

Figure 1-2 shows the XAUI core connecting a 10 Gigabit Ethernet MAC to a 10 Gigabit XPAK optical module.

*Figure 1-2:* XAUI Connecting a 10 Gigabit Ethernet MAC to an Optical Module

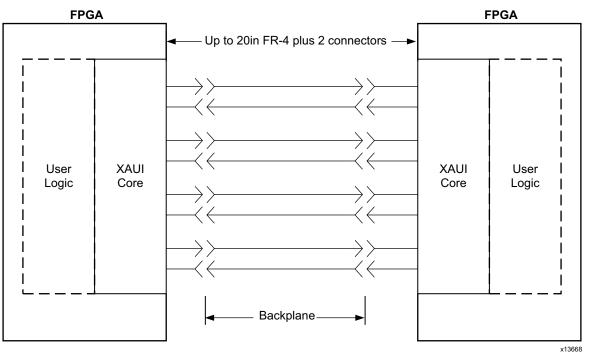

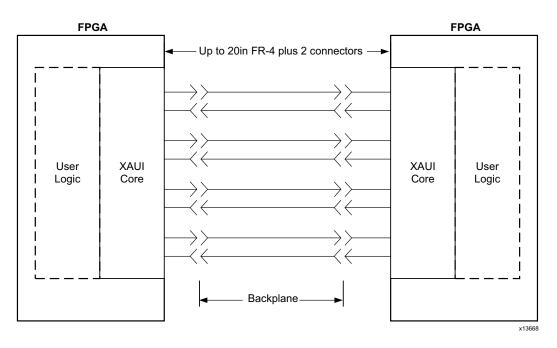

After its publication, the applications of XAUI have extended beyond 10 Gigabit Ethernet to the backplane and other general high-speed interconnect applications. Figure 1-3 shows a typical backplane and other general high-speed interconnect applications.

*Figure 1-3:* Typical Backplane Application for the XAUI Core

# **Licensing and Ordering Information**

This Xilinx LogiCORE<sup>™</sup> IP module is provided at no additional cost with the Xilinx Vivado® Design Suite under the terms of the <u>Xilinx End User License</u>. Information about this and other Xilinx LogiCORE IP modules is available at the <u>Xilinx Intellectual Property</u> page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your <u>local Xilinx sales representative</u>.

# Feedback

Xilinx welcomes comments and suggestions about the XAUI core and the documentation supplied with the core.

### Core

For comments or suggestions about the XAUI core, navigate to the <u>Xilinx Support web page</u> to log your comments. Be sure to include the following information:

- Product name

- Core version number

- Explanation of your comments

# Chapter 2

# **Product Specification**

XAUI is a four-lane, 3.125 Gb/s per-lane serial interface. 20 G–XAUI is supported in Zynq®-7000, Kintex®-7, Virtex®-7, and Artix®-7 devices (–2 speed grades) and UltraScale<sup>™</sup> architecture using four transceivers at 6.25 Gb/s. Each lane is a differential pair, carrying current mode logic (CML) signaling; the data on each lane is 8B/10B encoded before transmission. Special code groups are used to allow each lane to synchronize at a word boundary and to deskew all four lanes into alignment at the receiving end. The XAUI standard is fully specified in clauses 47 and 48 of the 10 Gigabit Ethernet specification *IEEE Std. 802.3-2012*.

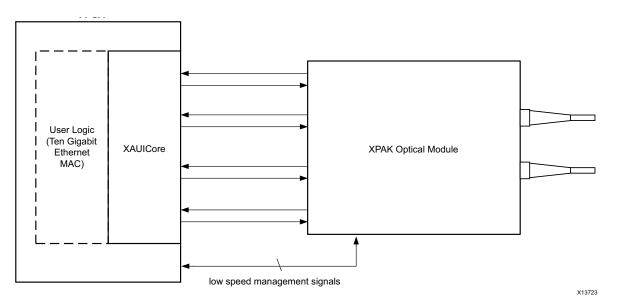

The XAUI standard was initially developed as a means to extend the physical separation possible between Media Access Controller (MAC) and physical-side interface (PHY) components in a 10 Gigabit Ethernet system distributed across a circuit board, and to reduce the number of interface signals in comparison with the Ten Gigabit Ethernet Media Independent Interface (XGMII). Figure 2-1 shows the XAUI core being used to connect to a 10 Gigabit Expansion Pack (XPAK) optical module.

Figure 2-1: Connecting XAUI to an Optical Module

After its publication, the applications of XAUI have extended beyond 10 Gigabit Ethernet to the backplane and other general high-speed interconnect applications. A typical backplane application is shown in Figure 2-2.

Figure 2-2: Typical Backplane Application for XAUI

# **Standards Compliance**

The XAUI IP core is designed to the standard specified in clauses 47 and 48 of the 10 Gigabit Ethernet specification *IEEE Std. 802.3-2012*.

# Performance

### Latency

These measurements are for the core only; they do not include the latency through the transceiver. The latency through the transceiver can be obtained from the relevant transceiver user guide.

### Transmit Path Latency

As measured from the input port xgmii\_txd[63:0] of the transmitter side XGMII (until that data appears on the txdata pins on the internal transceiver interface on the transceiver interface), the latency through the core for the internal XGMII interface configuration in the transmit direction is four clk periods of the core input usrclk.

### **Receive Path Latency**

Measured from the input into the core encrypted HDL logic from the rxdata pins of the internal transceiver interface until the data appears on xgmii\_rxdata[63:0] of the receiver side XGMII interface, the latency through the core in the receive direction is equal to 4–5 clock cycles of usrclk.

If the word appears on the upper half of the two-byte transceiver interface, the latency is five clock cycles of usrclk and it appears on the lower half of the XGMII interface. If it appears on the lower half of the two-byte interface, the latency is four clock cycles of usrclk and it appears on the upper half of the XGMII interface.

# Speed Grades

The minimum device requirements for 10G and 20G operation are listed in the following table.

| Device                   | XAUI (4x3.125G) | DXAUI (4x6.25G) |

|--------------------------|-----------------|-----------------|

| UltraScale™ Architecture | -1              | -1              |

| Zynq-7000                | -1              | -2              |

| Virtex-7                 | -1              | -2              |

| Kintex-7                 | -1              | -2              |

| Artix-7                  | -1              | -2              |

#### Table 2-1: Speed Grades

# **Resource Utilization**

For full details about performance and resource utilization, visit the <u>Performance and</u> <u>Resource Utilization web page</u>.

# Verification

The XAUI core has been verified using both simulation and hardware testing.

## Simulation

A highly parameterizable transaction-based simulation test suite was used to verify the core. Verification tests include:

- Register access over MDIO

- Loss and regain of synchronization

- Loss and regain of alignment

- Frame transmission

- Frame reception

- Clock compensation

- Recovery from error conditions

## **Hardware Verification**

The core has been used in several hardware test platforms within Xilinx. In particular, the core has been used in a test platform design with the Xilinx<sup>®</sup> 10 Gigabit Ethernet MAC. This design comprises the MAC, XAUI, a *ping* loopback First In First Out (FIFO), and a test pattern generator all under embedded processor control. This design has been used for conformance and interoperability testing at the University of New Hampshire Interoperability Lab.

# **Port Descriptions**

## **Client-Side Interface**

The signals of the client-side interface are shown in Table 2-2. See Interfacing to the Transmit Client Interface and Interfacing to the Receive Client Interface for more information on connecting to the client-side interface.

| Signal Name     | I/O | Clock Domain | Description                                           |

|-----------------|-----|--------------|-------------------------------------------------------|

| xgmii_txd[63:0] | In  | clk156_out   | Transmit data, eight bytes wide                       |

| xgmii_txc[7:0]  | In  | clk156_out   | Transmit control bits, one bit per transmit data byte |

| xgmii_rxd[63:0] | Out | clk156_out   | Received data, eight bytes wide                       |

| xgmii_rxc[7:0]  | Out | clk156_out   | Receive control bits, one bit per received data byte  |

Table 2-2: Client-Side Interface Ports

# Transceiver I/O

The transceiver interface ports of the core no longer exist because the core includes the transceiver. Instead there are the following ports, also described in Table 2-3.

- Ports corresponding to the I/O of the transceiver

- Transceiver Dynamic Reconfiguration Port

| Signal Name <sup>(1)</sup>  | I/O | Clock<br>Domain | Description                                                                                                                                                                                                                                                                             |

|-----------------------------|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xaui_tx_IN_p, xaui_tx_IN_n, | Out | N/A             | Differential complements of one another forming a differential transmit output pair. One pair for each of the 4 lanes.                                                                                                                                                                  |

| xaui_rx_IN_p, xaui_rx_IN_n, | In  | N/A             | Differential complements of one another forming a differential receiver input pair. One pair for each of the 4 lanes.                                                                                                                                                                   |

| signal_detect[3:0]          | In  | Async           | Intended to be driven by an attached 10GBASE-LX4 optical<br>module; they signify that each of the four optical receivers is<br>receiving illumination and is therefore not just putting out<br>noise. If an optical module is not in use, this four-wire bus<br>should be tied to 1111. |

#### Table 2-3: Ports Corresponding to the I/O of the Transceiver

Notes:

1. N=0,1,2,3

### **Transceiver Control and Status Ports**

Optional ports that, if enabled, allow the monitoring and control of certain important ports of the transceivers. When not selected, these ports are tied to their default values. For information on these ports, see the 7 Series FPGAs GTX/GTH Transceivers User Guide (UG476) [Ref 1], the 7 Series FPGAs GTP Transceivers User Guide (UG482) [Ref 2], the UltraScale Architecture GTH Transceivers User Guide (UG576) [Ref 3], and the UltraScale Architecture GTY Transceivers User Guide (UG578) [Ref 4]).

**IMPORTANT:** The ports in the Transceiver Control And Status Interface must be driven in accordance with the appropriate GT user guide. Using the input signals listed in Table 2-7 may result in unpredictable behavior of the IP core.

*Note:* The Dynamic Reconfiguration Port is only available if the **Transceiver Control and Status Ports** option is selected.

| Signal Name      | I/O     | Clock Domain | Description                                                                                                     |  |  |  |

|------------------|---------|--------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

|                  | GTO DRP |              |                                                                                                                 |  |  |  |

| gt0_drpaddr[8:0] | In      | dclk         | DRP address bus for channel 0                                                                                   |  |  |  |

| gt0_drpen        | In      | dclk         | DRP enable signal.<br>0: No read or write operation performed.<br>1: enables a read or write operation.         |  |  |  |

| gt0_drpdi[15:0]  | In      | dclk         | Data bus for writing configuration data to the transceiver for channel 0.                                       |  |  |  |

| gt0_drpdo[15:0]  | Out     | dclk         | Data bus for reading configuration data from the transceiver for channel 0.                                     |  |  |  |

| gt0_drprdy       | Out     | dclk         | Indicates operation is complete for write<br>operations and data is valid for read operations for<br>channel 0. |  |  |  |

Table 2-4: Transceiver Control and Status Ports (Channel 0)-7 Series FPGAs

#### Table 2-4: Transceiver Control and Status Ports (Channel 0)—7 Series FPGAs (Cont'd)

| Signal Name              | I/O | Clock Domain      | Description                                                                                                                                                                                              |  |

|--------------------------|-----|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| gt0_drpwe                | In  | dclk              | DRP write enable for channel 0.<br>0: Read operation when drpen is 1.<br>1: Write operation when drpen is 1.                                                                                             |  |

| gt0_drp_busy             | Out | dclk              | (GTPE2 all configurations or GTHE2 10G<br>configuration). Indicates the DRP interface is being<br>used internally by the serial transceiver and should<br>not be driven until this signal is deasserted. |  |

|                          |     | GT0 TX Reset a    | nd Initialization                                                                                                                                                                                        |  |

| gt0_txpmareset_in        | In  | Async             | Starts the TX PMA reset process.                                                                                                                                                                         |  |

| gt0_txpcsreset_in        | In  | Async             | Starts the TX PCS reset process.                                                                                                                                                                         |  |

| gt0_txresetdone_out      | Out | clk156_out        | When asserted the serial transceiver TX has finished reset and is ready for use.                                                                                                                         |  |

|                          |     | GT0 RX Reset a    | nd Initialization                                                                                                                                                                                        |  |

| gt0_rxpmareset_in        | In  | Async             | Starts the RX PMA reset process.                                                                                                                                                                         |  |

| gt0_rxpcsreset_in        | In  | Async             | Starts the RX PCS reset process.                                                                                                                                                                         |  |

| gt0_rxpmaresetdone_out   | Out | Async             | (GTHE2 and GTPE2) This active-High signal indicates RX PMA reset is complete.                                                                                                                            |  |

| gt0_rxresetdone_out      | Out | clk156_out        | When asserted the serial transceiver RX has finished reset and is ready for use.                                                                                                                         |  |

| GT0 Clocking             |     |                   |                                                                                                                                                                                                          |  |

| gt0_rxbufstatus_out[2:0] | Out | clk156_out        | RX buffer status.                                                                                                                                                                                        |  |

| gt0_txphaligndone_out    | Out | Async             | TX phase alignment done.                                                                                                                                                                                 |  |

| gt0_txphinitdone_out     | Out | Async             | TX phase alignment initialization done.                                                                                                                                                                  |  |

| gt0_txdlysresetdone_out  | Out | Async             | TX delay alignment soft reset done.                                                                                                                                                                      |  |

| gt0_cplllock_out         | Out | Async             | (GTHE2) This active-High PLL frequency lock signal indicates that the PLL frequency is within predetermined tolerance.                                                                                   |  |

| gt_qplllock_out          | Out | Async             | (GTXE2 and GTPE2) This active-High PLL frequency<br>lock signal indicates that the PLL frequency is<br>within predetermined tolerance.                                                                   |  |

|                          | S   | ignal Integrity a | and Functionality                                                                                                                                                                                        |  |

|                          |     | GT0 E             | ye scan                                                                                                                                                                                                  |  |

| gt0_eyescantrigger_in    | In  | clk156_out        | Causes a trigger event.                                                                                                                                                                                  |  |

| gt0_eyescanreset_in      | In  | Async             | This port is driven High and then deasserted to start the EYESCAN reset process.                                                                                                                         |  |

| gt0_eyescandataerror_out | Out | Async             | Asserts High for one rec_clk cycle when an (unmasked) error occurs while in the COUNT or ARMED state.                                                                                                    |  |

| gt0_rxrate_in[2:0]       | In  | Reserved          | This port dynamically controls the setting for the RX serial clock divider.                                                                                                                              |  |

| Signal Name               | I/O   | Clock Domain    | Description                                                                                    |  |

|---------------------------|-------|-----------------|------------------------------------------------------------------------------------------------|--|

| GT0 Loopback              |       |                 |                                                                                                |  |

| gt0_loopback_in[2:0]      | In    | Async           | Determines the loopback mode.                                                                  |  |

| GT0 Polarity              |       |                 |                                                                                                |  |

| gt0_rxpolarity_in         | In    | clk156_out      | The rxpolarity port can invert the polarity of incoming data.                                  |  |

| gt0_txpolarity_in         | In    | clk156_out      | The txpolarity port can invert the polarity of outgoing data.                                  |  |

|                           | GT0 F | RX Decision Fee | dback Equalizer (DFE)                                                                          |  |

| gt0_rxlpmen_in            | In    | Async           | (GTXE2 and GTHE2) RX datapath.<br>0: DFE. 1: LPM.                                              |  |

| gt0_rxdfelpmreset_in      | In    | Async           | (GTXE2 and GTHE2) Reset for LPM and DFE datapath.                                              |  |

| gt0_rxmonitorsel_in[1:0]  | In    | Reserved        | (GTXE2 and GTHE2) Select signal for gt0_rxmonitorout_out.                                      |  |

| gt0_rxmonitorout_out[6:0] | Out   | Async           | (GTXE2 and GTHE2) Monitor output.                                                              |  |

| gt0_rxlpmreset_in         | In    | clk156_out      | (GTPE2) This port is driven High and then deasserted to start the LPM reset process.           |  |

| gt0_rxlpmhfhold_in        | In    | Async           | (GTPE2) Determines whether the value of the high-frequency boost is either held or adapted.    |  |

| gt0_rxlpmhfovrden_in      | In    | Async           | (GTPE2) Determines whether the high-frequency boost is controlled by an attribute or a signal. |  |

| gt0_rxlpmlfhold_in        | In    | Async           | (GTPE2) Determines whether the value of the low-frequency boost is either held or adapted.     |  |

| gt0_rxlpmlfovrden_in      | In    | Async           | (GTPE2) Determines whether the low-frequency boost is controlled by an attribute or a signal.  |  |

|                           |       | GT0 TX          | ( Driver                                                                                       |  |

| gt0_txpostcursor_in[4:0]  | In    | Async           | Transmitter post-cursor TX post-emphasis control.                                              |  |

| gt0_txprecursor_in[4:0]   | In    | Async           | Transmitter post-cursor TX pre-emphasis control.                                               |  |

| gt0_txdiffctrl_in[3:0]    | In    | Async           | Driver Swing Control.                                                                          |  |

| gt0_txinhibit_in          | In    | clk156_out      | When High, this signal blocks the transmission of data.                                        |  |

|                           |       | GT0             | PRBS                                                                                           |  |

| gt0_rxprbscntreset_in     | In    | clk156_out      | Resets the PRBS error counter.                                                                 |  |

| gt0_rxprbserr_out         | Out   | clk156_out      | This non-sticky status output indicates that PRBS errors have occurred.                        |  |

| gt0_rxprbssel_in[2:0]     | In    | clk156_out      | Receiver PRBS checker test pattern control.                                                    |  |

| gt0_txprbssel_in[2:0]     | In    | clk156_out      | Transmitter PRBS generator test pattern control.                                               |  |

#### Table 2-4: Transceiver Control and Status Ports (Channel 0)—7 Series FPGAs (Cont'd)

| Table 2-4: Transceiver Control and Status Ports (Channel 0)—7 Series FPGAs (Cont'd | Table 2-4: | nd Status Ports (Channel 0)—7 Series FPGAs (Cont'd |

|------------------------------------------------------------------------------------|------------|----------------------------------------------------|

|------------------------------------------------------------------------------------|------------|----------------------------------------------------|

| Signal Name               | I/O                 | Clock Domain | Description                                                                                                                                           |  |  |

|---------------------------|---------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| gt0_txprbsforceerr_in     | In                  | clk156_out   | When this port is driven High, errors are forced in<br>the PRBS transmitter. While this port is asserted,<br>the output data pattern contains errors. |  |  |

|                           |                     | GTO R        | XX CDR                                                                                                                                                |  |  |

| gt0_rxcdrhold_in          | In                  | Async        | Hold the CDR control loop frozen.                                                                                                                     |  |  |

|                           | GT0 Digital Monitor |              |                                                                                                                                                       |  |  |

| gt0_dmonitorout_out[7:0]  | Out                 | Async        | (GTXE2) Digital Monitor Output Bus                                                                                                                    |  |  |

| gt0_dmonitorout_out[14:0] | Out                 | Async        | (GTHE2) Digital Monitor Output Bus                                                                                                                    |  |  |

| gt0_dmonitorout_out[14:0] | Out                 | Async        | (GTPE2) Digital Monitor Output Bus                                                                                                                    |  |  |

|                           |                     | GT0 S        | Status                                                                                                                                                |  |  |

| gt0_rxdisperr_out[3:0]    | Out                 | clk156_out   | Active-High indicates the corresponding byte of the received data has a disparity error                                                               |  |  |

| gt0_rxnotintable_out[3:0] | Out                 | clk156_out   | Active-High indicates the corresponding byte of the received data was not a valid character in the 8B/10B table.                                      |  |  |

| gt0_rxcommadet_out        | Out                 | clk156_out   | This signal is asserted when the comma alignment block detects a comma.                                                                               |  |  |

#### Table 2-5: Transceiver Control and Status Ports (Channel 1)—7 Series FPGAs

| Signal Name      | ١/٥ | Clock<br>Domain | Description                                                                                                                                                                                              |

|------------------|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |     | (               | GT1 DRP                                                                                                                                                                                                  |

| gt1_drpaddr[8:0] | In  | dclk            | DRP address bus for channel 1.                                                                                                                                                                           |

|                  |     |                 | DRP enable signal.                                                                                                                                                                                       |

| gt1_drpen        | In  | dclk            | <ul><li>0: No read or write operation performed.</li><li>1: enables a read or write operation.</li></ul>                                                                                                 |

| gt1_drpdi[15:0]  | In  | dclk            | Data bus for writing configuration data to the transceiver for channel 1.                                                                                                                                |

| gt1_drpdo[15:0]  | Out | dclk            | Data bus for reading configuration data from the transceiver for channel 1.                                                                                                                              |

| gt1_drprdy       | Out | dclk            | Indicates operation is complete for write operations<br>and data is valid for read operations for channel 1.                                                                                             |

|                  |     |                 | DRP write enable for channel 1.                                                                                                                                                                          |

| gt1_drpwe        | In  | dclk            | 0: Read operation when drpen is 1.<br>1: Write operation when drpen is 1.                                                                                                                                |

| gt1_drp_busy     | Out | dclk            | (GTPE2 all configurations or GTHE2 10G<br>configuration). Indicates the DRP interface is being<br>used internally by the serial transceiver and should not<br>be driven until this signal is deasserted. |

| Signal Name              | I/O | Clock<br>Domain | Description                                                                                                                  |

|--------------------------|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------|

|                          |     | GT1 TX Rese     | et and Initialization                                                                                                        |

| gt1_txpmareset_in        | In  | Async           | Starts the TX PMA reset process.                                                                                             |

| gt1_txpcsreset_in        | In  | Async           | Starts the TX PCS reset process.                                                                                             |

| gt1_txresetdone_out      | Out | clk156_out      | When asserted the serial transceiver TX has finished reset and is ready for use.                                             |

|                          |     | GT1 RX Rese     | et and Initialization                                                                                                        |

| gt1_rxpmareset_in        | In  | Async           | Starts the RX PMA reset process.                                                                                             |

| gt1_rxpcsreset_in        | In  | Async           | Starts the RX PCS reset process.                                                                                             |

| gt1_rxpmaresetdone_out   | Out | Async           | (GTHE2 and GTPE2) This active-High signal indicates RX PMA reset is complete.                                                |

| gt1_rxresetdone_out      | Out | clk156_out      | When asserted the serial transceiver RX has finished reset and is ready for use.                                             |

|                          | J.  | GT              | 1 Clocking                                                                                                                   |

| gt1_rxbufstatus_out[2:0] | Out | clk156_out      | RX buffer status.                                                                                                            |

| gt1_txphaligndone_out    | Out | Async           | TX phase alignment done.                                                                                                     |

| gt1_txphinitdone_out     | Out | Async           | TX phase alignment initialization done.                                                                                      |

| gt1_txdlysresetdone_out  | Out | Async           | TX delay alignment soft reset done.                                                                                          |

| gt1_cplllock_out         | Out | Async           | (GTHE2) This active-High PLL frequency lock signal<br>indicates that the PLL frequency is within<br>predetermined tolerance. |

|                          | 9   | Signal Integri  | ty and Functionality                                                                                                         |

|                          |     | GT              | 1 Eye scan                                                                                                                   |

| gt1_eyescantrigger_in    | In  | clk156_out      | Causes a trigger event.                                                                                                      |

| gt1_eyescanreset_in      | In  | Async           | This port is driven High and then deasserted to start the EYESCAN reset process.                                             |

| gt1_eyescandataerror_out | Out | Async           | Asserts High for one rec_clk cycle when an (unmasked) error occurs while in the COUNT or ARMED state.                        |

| gt1_rxrate_in[2:0]       | In  | Reserved        | This port dynamically controls the setting for the RX serial clock divider.                                                  |

|                          |     | GT1             | L Loopback                                                                                                                   |

| gt1_loopback_in[2:0]     | In  | Async           | Determines the loopback mode.                                                                                                |

|                          |     | GT              | 1 Polarity                                                                                                                   |

| gt1_rxpolarity_in        | In  | clk156_out      | The rxpolarity port can invert the polarity of incoming data.                                                                |

#### Table 2-5: Transceiver Control and Status Ports (Channel 1)—7 Series FPGAs (Cont'd)

gt1\_txpolarity\_in

data.

In

clk156\_out

The txpolarity port can invert the polarity of outgoing

| Table 2-5: | Transceiver Control and Status Ports (Channel 1)—7 Series FPGAs (Cont'd) |

|------------|--------------------------------------------------------------------------|

| 10010 2 5. |                                                                          |

| Signal Name                              | I/O | Clock<br>Domain | Description                                                                                                                                     |  |

|------------------------------------------|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GT1 RX Decision Feedback Equalizer (DFE) |     |                 |                                                                                                                                                 |  |

| att rylpmon in                           | In  | Acupa           | (GTXE2 and GTHE2) RX datapath.                                                                                                                  |  |

| gt1_rxlpmen_in                           | 111 | Async           | 0: DFE. 1: LPM.                                                                                                                                 |  |

| gt1_rxdfelpmreset_in                     | In  | Async           | (GTXE2 and GTHE2) Reset for LPM and DFE datapath.                                                                                               |  |

| gt1_rxmonitorsel_in[1:0]                 | In  | Reserved        | (GTXE2 and GTHE2) Select signal for gt1_rxmonitorout_out.                                                                                       |  |

| gt1_rxmonitorout_out[6:0]                | Out | Async           | (GTXE2 and GTHE2) Monitor output.                                                                                                               |  |

| gt1_rxlpmreset_in                        | In  | clk156_out      | (GTPE2) This port is driven High and then deasserted to start the LPM reset process.                                                            |  |

| gt1_rxlpmhfhold_in                       | In  | Async           | (GTPE2) Determines whether the value of the high-frequency boost is either held or adapted.                                                     |  |

| gt1_rxlpmhfovrden_in                     | In  | Async           | (GTPE2) Determines whether the high-frequency boost is controlled by an attribute or a signal.                                                  |  |

| gt1_rxlpmlfhold_in                       | In  | Async           | (GTPE2) Determines whether the value of the low-frequency boost is either held or adapted.                                                      |  |

| gt1_rxlpmlfovrden_in                     | In  | Async           | (GTPE2) Determines whether the low-frequency boost is controlled by an attribute or a signal.                                                   |  |

|                                          |     | GT              | L TX Driver                                                                                                                                     |  |

| gt1_txpostcursor_in[4:0]                 | In  | Async           | Transmitter post-cursor TX post-emphasis control.                                                                                               |  |

| gt1_txprecursor_in[4:0]                  | In  | Async           | Transmitter post-cursor TX pre-emphasis control.                                                                                                |  |

| gt1_txdiffctrl_in[3:0]                   | In  | Async           | Driver Swing Control.                                                                                                                           |  |

| gt1_txinhibit_in                         | In  | clk156_out      | When High, this signal blocks the transmission of data.                                                                                         |  |

|                                          |     | G               | T1 PRBS                                                                                                                                         |  |

| gt1_rxprbscntreset_in                    | In  | clk156_out      | Resets the PRBS error counter.                                                                                                                  |  |

| gt1_rxprbserr_out                        | Out | clk156_out      | This non-sticky status output indicates that PRBS errors have occurred.                                                                         |  |

| gt1_rxprbssel_in[2:0]                    | In  | clk156_out      | Receiver PRBS checker test pattern control.                                                                                                     |  |

| gt1_txprbssel_in[2:0]                    | In  | clk156_out      | Transmitter PRBS generator test pattern control.                                                                                                |  |

| gt1_txprbsforceerr_in                    | In  | clk156_out      | When this port is driven High, errors are forced in the PRBS transmitter. While this port is asserted, the output data pattern contains errors. |  |

|                                          |     | GT              | 1 RX CDR                                                                                                                                        |  |

| gt1_rxcdrhold_in                         | In  | Async           | Hold the CDR control loop frozen.                                                                                                               |  |

|                                          |     | GT1 D           | igital Monitor                                                                                                                                  |  |

| gt1_dmonitorout_out[7:0]                 | Out | Async           | (GTXE2) Digital Monitor Output Bus                                                                                                              |  |

| gt1_dmonitorout_out[14:0]                | Out | Async           | (GTHE2) Digital Monitor Output Bus                                                                                                              |  |

| gt1_dmonitorout_out[14:0]                | Out | Async           | (GTPE2) Digital Monitor Output Bus                                                                                                              |  |

#### Table 2-5: Transceiver Control and Status Ports (Channel 1)—7 Series FPGAs (Cont'd)

| Signal Name               | I/O        | Clock<br>Domain | Description                                                                                                      |  |  |

|---------------------------|------------|-----------------|------------------------------------------------------------------------------------------------------------------|--|--|

|                           | GT1 Status |                 |                                                                                                                  |  |  |

| gt1_rxdisperr_out[3:0]    | Out        | clk156_out      | Active-High indicates the corresponding byte of the received data has a disparity error                          |  |  |

| gt1_rxnotintable_out[3:0] | Out        | clk156_out      | Active-High indicates the corresponding byte of the received data was not a valid character in the 8B/10B table. |  |  |

| gt1_rxcommadet_out        | Out        | clk156_out      | This signal is asserted when the comma alignment block detects a comma.                                          |  |  |

#### Table 2-6: Transceiver Control and Status Ports (Channel 2)—7 Series FPGAs

| Signal Name         | I/O | Clock<br>Domain | Description                                                                                                                                                                                              |

|---------------------|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |     | (               | GT2 DRP                                                                                                                                                                                                  |

| gt2_drpaddr[8:0]    | In  | dclk            | DRP address bus for channel 2.                                                                                                                                                                           |

|                     |     |                 | DRP enable signal.                                                                                                                                                                                       |

| gt2_drpen           | In  | dclk            | <ul><li>0: No read or write operation performed.</li><li>1: enables a read or write operation.</li></ul>                                                                                                 |

| gt2_drpdi[15:0]     | In  | dclk            | Data bus for writing configuration data to the transceiver for channel 2.                                                                                                                                |

| gt2_drpdo[15:0]     | Out | dclk            | Data bus for reading configuration data from the transceiver for channel 2.                                                                                                                              |

| gt2_drprdy          | Out | dclk            | Indicates operation is complete for write operations<br>and data is valid for read operations for channel 2.                                                                                             |

|                     |     |                 | DRP write enable for channel 2.                                                                                                                                                                          |

| gt2_drpwe           | In  | dclk            | 0: Read operation when drpen is 1.<br>1: Write operation when drpen is 1.                                                                                                                                |

| gt2_drp_busy        | Out | dclk            | (GTPE2 all configurations or GTHE2 10G<br>configuration). Indicates the DRP interface is being<br>used internally by the serial transceiver and should not<br>be driven until this signal is deasserted. |

|                     |     | GT2 TX Reso     | et and Initialization                                                                                                                                                                                    |

| gt2_txpmareset_in   | In  | Async           | Starts the TX PMA reset process.                                                                                                                                                                         |

| gt2_txpcsreset_in   | In  | Async           | Starts the TX PCS reset process.                                                                                                                                                                         |

| gt2_txresetdone_out | Out | clk156_out      | When asserted the serial transceiver TX has finished reset and is ready for use.                                                                                                                         |

|                     |     | GT2 RX Res      | et and Initialization                                                                                                                                                                                    |

| gt2_rxpmareset_in   | In  | Async           | Starts the RX PMA reset process.                                                                                                                                                                         |

| gt2_rxpcsreset_in   | In  | Async           | Starts the RX PCS reset process.                                                                                                                                                                         |

#### Table 2-6: Transceiver Control and Status Ports (Channel 2)—7 Series FPGAs (Cont'd)

| Signal Name               | I/O   | Clock<br>Domain | Description                                                                                                            |  |

|---------------------------|-------|-----------------|------------------------------------------------------------------------------------------------------------------------|--|

| gt2_rxpmaresetdone_out    | Out   | Async           | (GTHE2 and GTPE2) This active-High signal indicates RX PMA reset is complete.                                          |  |

| gt2_rxresetdone_out       | Out   | clk156_out      | When asserted the serial transceiver RX has finished reset and is ready for use.                                       |  |

|                           |       | GT              | 2 Clocking                                                                                                             |  |

| gt2_rxbufstatus_out[2:0]  | Out   | clk156_out      | RX buffer status.                                                                                                      |  |

| gt2_txphaligndone_out     | Out   | Async           | TX phase alignment done.                                                                                               |  |

| gt2_txphinitdone_out      | Out   | Async           | TX phase alignment initialization done.                                                                                |  |

| gt2_txdlysresetdone_out   | Out   | Async           | TX delay alignment soft reset done.                                                                                    |  |

| gt2_cplllock_out          | Out   | Async           | (GTHE2) This active-High PLL frequency lock signal indicates that the PLL frequency is within predetermined tolerance. |  |

|                           | S     | ignal Integri   | ity and Functionality                                                                                                  |  |

|                           |       | GT              | 2 Eye Scan                                                                                                             |  |

| gt2_eyescantrigger_in     | In    | clk156_out      | Causes a trigger event.                                                                                                |  |

| gt2_eyescanreset_in       | In    | Async           | This port is driven High and then deasserted to start the EYESCAN reset process.                                       |  |

| gt2_eyescandataerror_out  | Out   | Async           | Asserts High for one rec_clk cycle when an (unmasked) error occurs while in the COUNT or ARMED state.                  |  |

| gt2_rxrate_in[2:0]        | In    | Reserved        | This port dynamically controls the setting for the RX serial clock divider.                                            |  |

| GT2 Loopback              |       |                 |                                                                                                                        |  |

| gt2_loopback_in[2:0]      | In    | Async           | Determines the loopback mode.                                                                                          |  |

|                           |       | GT              | 2 Polarity                                                                                                             |  |

| gt2_rxpolarity_in         | In    | clk156_out      | The rxpolarity port can invert the polarity of incoming data.                                                          |  |

| gt2_txpolarity_in         | In    | clk156_out      | The txpolarity port can invert the polarity of outgoing data.                                                          |  |

|                           | GT2 I | RX Decision     | Feedback Equalizer (DFE)                                                                                               |  |

| gt2_rxlpmen_in            | In    | Async           | (GTXE2 and GTHE2) RX datapath.<br>0: DFE.<br>1: LPM.                                                                   |  |

| gt2_rxdfelpmreset_in      | In    | Async           | (GTXE2 and GTHE2) Reset for LPM and DFE datapath.                                                                      |  |

| gt2_rxmonitorsel_in[1:0]  | In    | Reserved        | (GTXE2 and GTHE2) Select signal for gt2_rxmonitorout_out.                                                              |  |

| gt2_rxmonitorout_out[6:0] | Out   | Async           | (GTXE2 and GTHE2) Monitor output.                                                                                      |  |

| gt2_rxlpmreset_in         | In    | clk156_out      | (GTPE2) This port is driven High and then deasserted to start the LPM reset process.                                   |  |

#### Table 2-6: Transceiver Control and Status Ports (Channel 2)—7 Series FPGAs (Cont'd)

| Signal Name               | I/O | Clock<br>Domain | Description                                                                                                                                     |

|---------------------------|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| gt2_rxlpmhfhold_in        | In  | Async           | (GTPE2) Determines whether the value of the high-frequency boost is either held or adapted.                                                     |

| gt2_rxlpmhfovrden_in      | In  | Async           | (GTPE2) Determines whether the high-frequency boost is controlled by an attribute or a signal.                                                  |

| gt2_rxlpmlfhold_in        | In  | Async           | (GTPE2) Determines whether the value of the low-frequency boost is either held or adapted.                                                      |

| gt2_rxlpmlfovrden_in      | In  | Async           | (GTPE2) Determines whether the low-frequency boost is controlled by an attribute or a signal.                                                   |

|                           | L   | GT              | 2 TX Driver                                                                                                                                     |

| gt2_txpostcursor_in[4:0]  | In  | Async           | Transmitter post-cursor TX post-emphasis control.                                                                                               |

| gt2_txprecursor_in[4:0]   | In  | Async           | Transmitter post-cursor TX pre-emphasis control.                                                                                                |

| gt2_txdiffctrl_in[3:0]    | In  | Async           | Driver Swing Control.                                                                                                                           |

| gt2_txinhibit_in          | In  | clk156_out      | When High, this signal blocks the transmission of data.                                                                                         |

|                           |     | G               | T2 PRBS                                                                                                                                         |

| gt2_rxprbscntreset_in     | In  | clk156_out      | Resets the PRBS error counter.                                                                                                                  |

| gt2_rxprbserr_out         | Out | clk156_out      | This non-sticky status output indicates that PRBS errors have occurred.                                                                         |

| gt2_rxprbssel_in[2:0]     | In  | clk156_out      | Receiver PRBS checker test pattern control.                                                                                                     |

| gt2_txprbssel_in[2:0]     | In  | clk156_out      | Transmitter PRBS generator test pattern control.                                                                                                |

| gt2_txprbsforceerr_in     | In  | clk156_out      | When this port is driven High, errors are forced in the PRBS transmitter. While this port is asserted, the output data pattern contains errors. |

|                           | 1   | G               | IZ RX CDR                                                                                                                                       |

| gt2_rxcdrhold_in          | In  | Async           | Hold the CDR control loop frozen.                                                                                                               |

|                           | 1   | GT2 D           | igital Monitor                                                                                                                                  |

| gt2_dmonitorout_out[7:0]  | Out | Async           | (GTXE2) Digital Monitor Output Bus                                                                                                              |

| gt2_dmonitorout_out[14:0] | Out | Async           | (GTHE2) Digital Monitor Output Bus                                                                                                              |

| gt2_dmonitorout_out[14:0] | Out | Async           | (GTPE2) Digital Monitor Output Bus                                                                                                              |

|                           | 1   | G               | T2 Status                                                                                                                                       |

| gt2_rxdisperr_out[3:0]    | Out | clk156_out      | Active-High indicates the corresponding byte of the received data has a disparity error                                                         |

| gt2_rxnotintable_out[3:0] | Out | clk156_out      | Active-High indicates the corresponding byte of the received data was not a valid character in the 8B/10B table.                                |

| gt2_rxcommadet_out        | Out | clk156_out      | This signal is asserted when the comma alignment block detects a comma.                                                                         |

| Signal Name              | I/O | Clock<br>Domain | Description                                                                                                                                                                                              |

|--------------------------|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |     | (               | GT3 DRP                                                                                                                                                                                                  |

| gt3_drpaddr[8:0]         | In  | dclk            | DRP address bus for channel 3.                                                                                                                                                                           |

|                          |     |                 | DRP enable signal.                                                                                                                                                                                       |

| gt3_drpen                | In  | dclk            | 0: No read or write operation performed.<br>1: enables a read or write operation.                                                                                                                        |

| gt3_drpdi[15:0]          | In  | dclk            | Data bus for writing configuration data to the transceiver for channel 3.                                                                                                                                |

| gt3_drpdo[15:0]          | Out | dclk            | Data bus for reading configuration data from the transceiver for channel 3.                                                                                                                              |

| gt3_drprdy               | Out | dclk            | Indicates operation is complete for write operations<br>and data is valid for read operations for channel 3.                                                                                             |

|                          |     |                 | DRP write enable for channel 3.                                                                                                                                                                          |

| gt3_drpwe                | In  | dclk            | 0: Read operation when drpen is 1.<br>1: Write operation when drpen is 1.                                                                                                                                |

| gt3_drp_busy             | Out | dclk            | (GTPE2 all configurations or GTHE2 10G<br>configuration). Indicates the DRP interface is being<br>used internally by the serial transceiver and should not<br>be driven until this signal is deasserted. |

|                          |     | GT3 TX Res      | et and Initialization                                                                                                                                                                                    |

| gt3_txpmareset_in        | In  | Async           | Starts the TX PMA reset process.                                                                                                                                                                         |

| gt3_txpcsreset_in        | In  | Async           | Starts the TX PCS reset process.                                                                                                                                                                         |

| gt3_txresetdone_out      | Out | clk156_out      | When asserted the serial transceiver TX has finished reset and is ready for use.                                                                                                                         |

|                          |     | GT3 RX Res      | et and Initialization                                                                                                                                                                                    |

| gt3_rxpmareset_in        | In  | Async           | Starts the RX PMA reset process.                                                                                                                                                                         |

| gt3_rxpcsreset_in        | In  | Async           | Starts the RX PCS reset process.                                                                                                                                                                         |

| gt3_rxpmaresetdone_out   | Out | Async           | (GTHE2 and GTPE2) This active-High signal indicates RX PMA reset is complete.                                                                                                                            |

| gt3_rxresetdone_out      | Out | clk156_out      | When asserted the serial transceiver RX has finished reset and is ready for use.                                                                                                                         |

|                          |     | GT              | 3 Clocking                                                                                                                                                                                               |

| gt3_rxbufstatus_out[2:0] | Out | clk156_out      | RX buffer status.                                                                                                                                                                                        |

| gt3_txphaligndone_out    | Out | Async           | TX phase alignment done.                                                                                                                                                                                 |

| gt3_txphinitdone_out     | Out | Async           | TX phase alignment initialization done.                                                                                                                                                                  |

| gt3_txdlysresetdone_out  | Out | Async           | TX delay alignment soft reset done.                                                                                                                                                                      |

| gt3_cplllock_out         | Out | Async           | (GTHE2) This active-High PLL frequency lock signal indicates that the PLL frequency is within predetermined tolerance.                                                                                   |

#### Table 2-7: Transceiver Control and Status Ports (Channel 3)—7 Series FPGAs

| Signal Name               | I/O   | Clock<br>Domain | Description                                                                                           |

|---------------------------|-------|-----------------|-------------------------------------------------------------------------------------------------------|

|                           | S     | ignal Integri   | ity and Functionality                                                                                 |

|                           |       | GT              | 3 Eye Scan                                                                                            |

| gt3_eyescantrigger_in     | In    | clk156_out      | Causes a trigger event.                                                                               |

| gt3_eyescanreset_in       | In    | Async           | This port is driven High and then deasserted to start the EYESCAN reset process.                      |

| gt3_eyescandataerror_out  | Out   | Async           | Asserts High for one rec_clk cycle when an (unmasked) error occurs while in the COUNT or ARMED state. |

| gt3_rxrate_in[2:0]        | In    | Reserved        | This port dynamically controls the setting for the RX serial clock divider.                           |

|                           |       | GT              | 3 Loopback                                                                                            |

| gt3_loopback_in[2:0]      | In    | Async           | Determines the loopback mode.                                                                         |

|                           |       | GT              | 3 Polarity                                                                                            |

| gt3_rxpolarity_in         | In    | clk156_out      | The rxpolarity port can invert the polarity of incoming data.                                         |

| gt3_txpolarity_in         | In    | clk156_out      | The txpolarity port can invert the polarity of outgoing data.                                         |

|                           | GT3 F | RX Decision     | Feedback Equalizer (DFE)                                                                              |

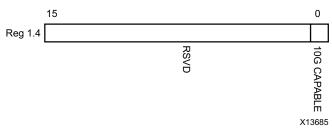

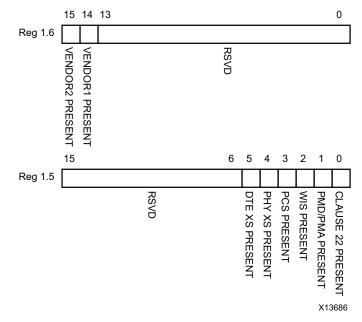

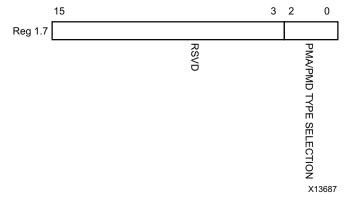

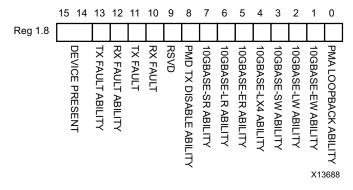

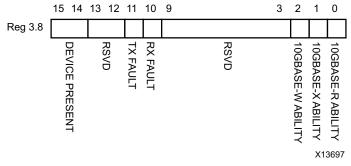

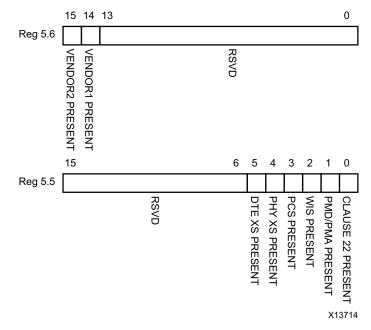

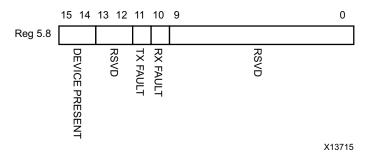

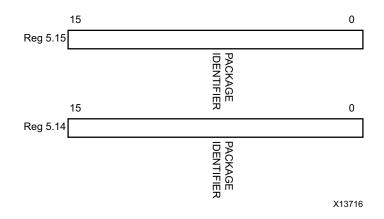

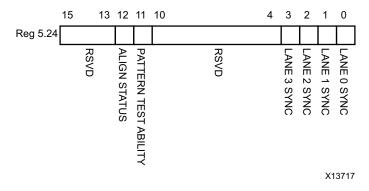

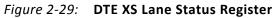

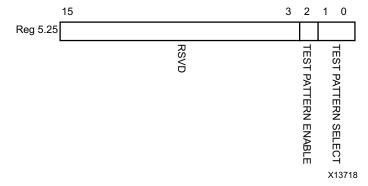

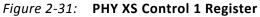

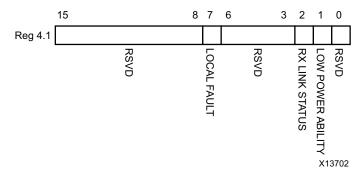

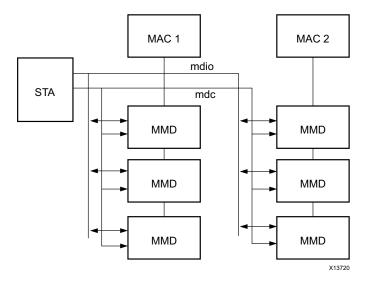

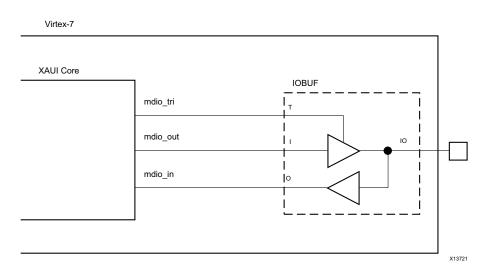

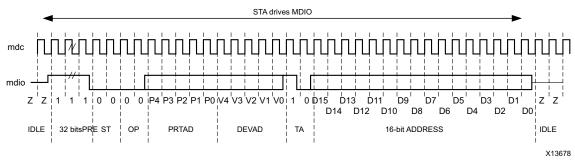

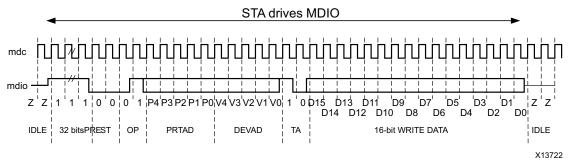

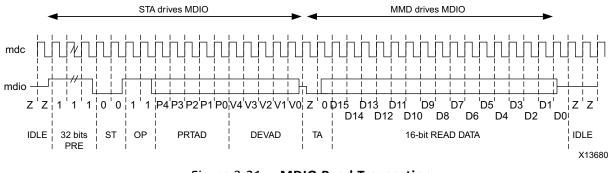

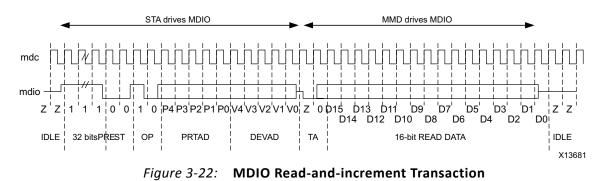

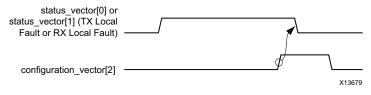

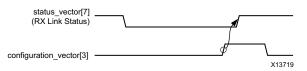

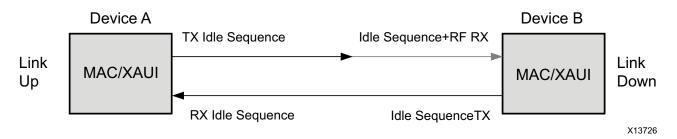

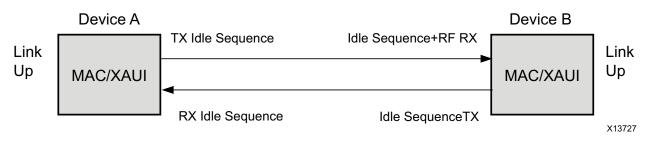

| gt3_rxlpmen_in            | In    | Async           | (GTXE2 and GTHE2) RX datapath.<br>0: DFE. 1: LPM.                                                     |