# Video PHY Controller v2.1

# LogiCORE IP Product Guide

**Vivado Design Suite**

PG230 December 20, 2017

# **Table of Contents**

| Chapter 1: Overview                                        |

|------------------------------------------------------------|

| Applications                                               |

| Unsupported Features 5                                     |

| Licensing and Ordering Information                         |

| Chapter 2: Product Specification                           |

| Video PHY 7                                                |

| Performance                                                |

| Resource Utilization                                       |

| Port Descriptions                                          |

| Sideband Definitions                                       |

| Register Space                                             |

| Chapter 3: Designing with the Core                         |

| Clocking                                                   |

| Resets                                                     |

| Interrupts                                                 |

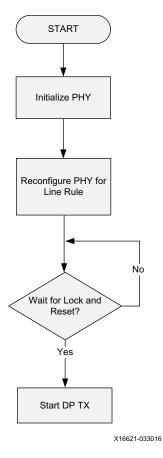

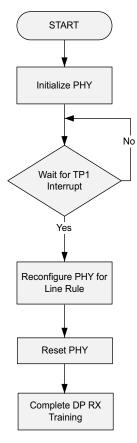

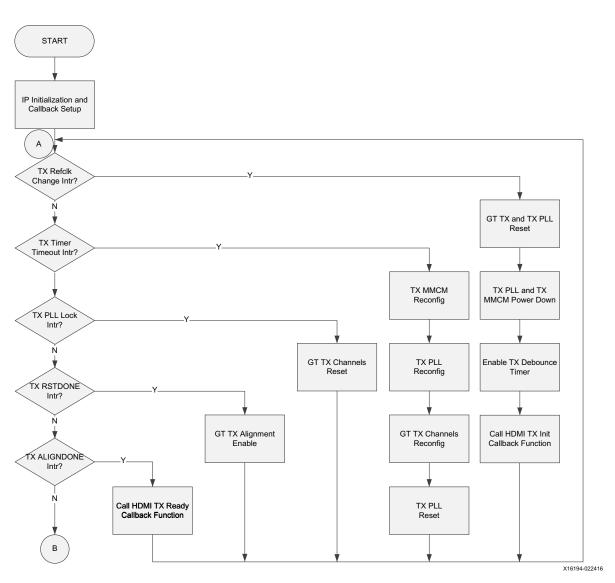

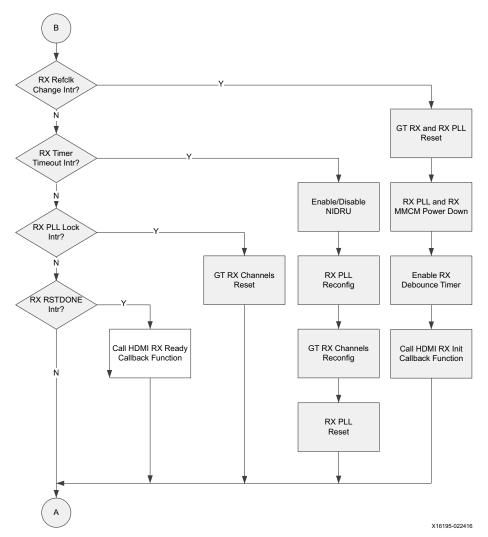

| Program and Interrupt Flow                                 |

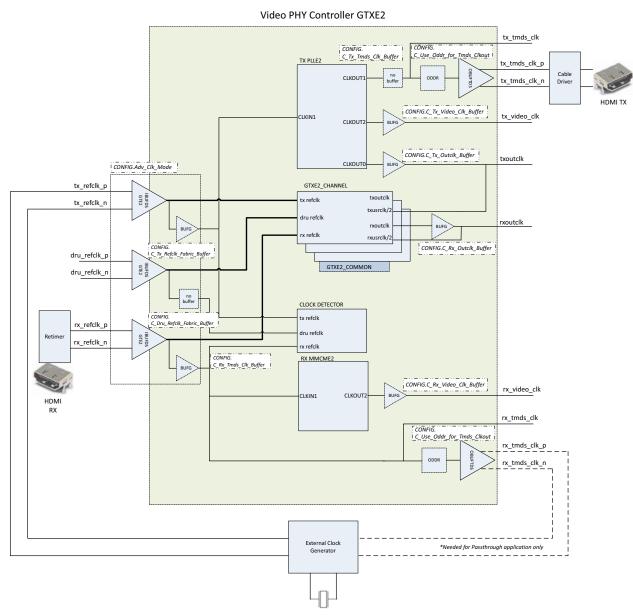

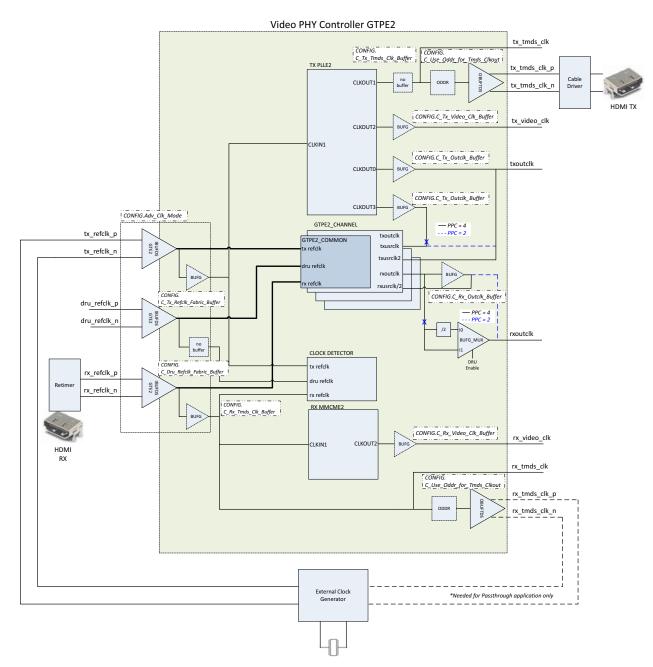

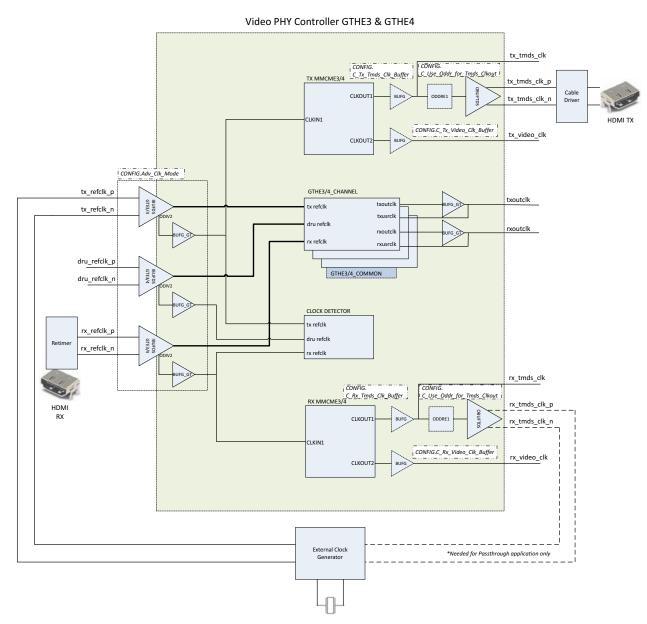

| Video PHY Controller HDMI Implementation                   |

| Chapter 4: Design Flow Steps                               |

| Customizing and Generating the Core                        |

| Constraining the Core                                      |

| Board Design Guidelines                                    |

| Simulation                                                 |

| Synthesis and Implementation                               |

| Chapter 5: Example Design                                  |

| HDMI VPHY Example Design                                   |

| DisplayPort VPHY Example Design 92                         |

| Appendix A: Verification, Compliance, and Interoperability |

| Simulation                                                 |

| Hardware Testing 93                                        |

| Appendix B: Migrating and Upgrading                                                              |     |

|--------------------------------------------------------------------------------------------------|-----|

| Software Driver                                                                                  | 94  |

| Appendix C: Debugging                                                                            |     |

| Finding Help on Xilinx.com                                                                       | 96  |

| Interface Debug                                                                                  | 98  |

| HDMI Debugging                                                                                   | 99  |

| Appendix D: Application Software Development  Appendix E: Additional Resources and Legal Notices |     |

| Xilinx Resources                                                                                 | 106 |

| Documentation Navigator and Design Hubs                                                          | 106 |

| References                                                                                       | 107 |

| Revision History                                                                                 | 108 |

| Please Read: Important Legal Notices                                                             |     |

# Introduction

The Xilinx® Video PHY Controller LogiCORE™ IP core is designed for enabling plug-and-play connectivity with Video (DisplayPort and HDMI® technology) MAC Transmit or Receive subsystems<sup>(1)</sup>. The interface between the video MAC and PHY layers are standardized to enable ease of use in accessing shared transceiver resources. The AXI4-Lite register interface is provided to enable dynamic accesses of transceiver controls/status.

#### **Features**

- AXI4-Lite support for register accesses

- Protocol Support: DisplayPort, HDMI

- Full transceiver dynamic reconfiguration port (DRP) accesses and transceiver functions

- Independent TX and RX path line rates (device specific)

- Single quad support

- Phase-locked loop (PLL) switching support from software

- Transmit and Receiver user clocking

- Protocol specific functions (For example, **HDMI Clock Detector**)

- Non-integer data recovery unit (NI-DRU) support for lower line rates. NI-DRU support is for the HDMI protocol only.

- Advanced Clocking Support.

- 1. For HDMI, appropriate HDMI 2.0 cable driver (TX) and EQ/ retimer (RX) devices are required to meet HDMI électrical compliance. Video PHY Controller is not compliant with TMDS specification.

| LogiCORE IP Facts Table                           |                                                                                                                                   |  |  |  |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Core Specifics                                    |                                                                                                                                   |  |  |  |

| Supported Device                                  | HDMI Video PHY Controller  UltraScale+™ Families (GTHE4) (2)  UltraScale Families (GTHE3)  7-Series (GTXE2)  Artix®-7 (GTPE2) (6) |  |  |  |

| Family <sup>(1)</sup>                             | DisplayPort Video PHY Controller  UltraScale+™ Families (GTHE4) (2)  UltraScale Families (GTHE3)  7-Series (GTXE2) (3)            |  |  |  |

| Supported User<br>Interfaces                      | AXI4-Lite, AXI4-Stream                                                                                                            |  |  |  |

| Resources                                         | Performance and Resource Utilization                                                                                              |  |  |  |

| P                                                 | Provided with Core                                                                                                                |  |  |  |

| Design Files                                      | Verilog                                                                                                                           |  |  |  |

| Example Design                                    | Not Provided                                                                                                                      |  |  |  |

| Test Bench                                        | Not Provided                                                                                                                      |  |  |  |

| Constraints File                                  | Xilinx Design Constraints (XDC)                                                                                                   |  |  |  |

| Simulation Model                                  | Not Provided                                                                                                                      |  |  |  |

| Supported<br>S/W Driver <sup>(4)</sup>            | Standalone                                                                                                                        |  |  |  |

| Tes                                               | sted Design Flows <sup>(5)</sup>                                                                                                  |  |  |  |

| Design Entry                                      | Vivado® Design Suite                                                                                                              |  |  |  |

| Simulation                                        | For supported simulators, see the Xilinx Design Tools: Release Notes Guide.                                                       |  |  |  |

| Synthesis                                         | Vivado Synthesis                                                                                                                  |  |  |  |

|                                                   | Support                                                                                                                           |  |  |  |

| Provided by Xilinx at the Xilinx Support web page |                                                                                                                                   |  |  |  |

#### Notes:

- 1. For a complete list of supported devices, see the Vivado IP

- 2. The maximum line rate for DisplayPort is 2.7 Gbps for GTHE4 Zynq UltraScale+ -1LI (0.72V) devices operated at 16-bit or 20-bit internal datapath.

- 3. For Kintex-7: QPLL1/2 does not cover all DP line rate range and user is encouraged to use CPLL for Tx path.

- 4. Standalone driver details can be found in the software development kit (SDK) directory (<install directory>/SDK/ <release>/data/embeddedsw/doc/xilinx\_drivers.htm). Linux OS and driver support information is available from the Xilinx Wiki page.

- 5. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

- 6. GTPE2 -1, -1L, and -2LE (0.9V) parts are not supported by the HDMI Video PHY Controller because the maximum line rate for those devices is 3.75 Gbps. GTPE2 DisplayPort Video PHY support will be discontinued on 2017.4.

# Overview

This chapter contains an overview of the core as well as details about applications, licensing, and standards. The Video PHY Controller core is a feature-rich soft IP core incorporating all the necessary logic to properly interface with media access control (MAC) layers and perform physical-side interface (PHY) functionality. Xilinx® IP cores have been successfully tested on hardware and verified. For additional details on the interoperability results, contact your local Xilinx sales representative.

# **Applications**

The Video PHY controller core is the supported method of configuring and using the PHY layer with video MAC controllers.

By separating the PHY layer from the controller layer, the Video PHY provides users with the flexibility of sharing GTs between a video interface input and output or between two different video interfaces such as HDMI and Displayport.

# **Unsupported Features**

- Multi MAC controllers support (Complex use cases)

- GTY transceiver

- The Video PHY Controller core does not currently support mixed MAC controller support, that is, HDMI on the input and DisplayPort output and so on. The current Video PHY Controller core supports MAC on both the input and output.

- The Video PHY Controller core does not support multiple protocols per instance (for example, two HDMIs in one VPHY.)

- The Video PHY Controller does not support standalone usage. It is designed to be used with Xilinx HDMI or DisplayPort MAC Subsystems.

# **Licensing and Ordering Information**

This Xilinx LogiCORE™ IP module is provided under the terms of the Xilinx Core License Agreement. The module is shipped as part of the Vivado® Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your local Xilinx sales representative for information on pricing and availability.

For more information, visit the Video PHY Controller product web page.

Information about other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# **Product Specification**

The Video PHY Controller core is the supported method of configuring and using transceivers with MAC subsystems. The core simplifies serial transceiver (GT) usage by providing a standardized interface and software programmability of serial transceiver functions. These concepts, as well as technical specifications, are described in this chapter.

## Video PHY

The PHY is intended to simplify the use of serial transceivers and adds domain-specific configurability. The Video PHY Controller IP is not intended to be used as a stand alone IP and must be used with Xilinx Video MACs such as HDMI 1.4/2.0 Transmitter/Receiver Subsystems and DisplayPort TX/RX Subsystems. The core enables simpler connectivity between MAC layers for TX and RX paths. However, it is still important to understand the behavior, usage, and any limitations of the transceivers. See the device specific transceiver user guide for details.

This chapter introduces the Video PHY Layer and architects Video IP Solutions with a clear boundary between the Link Layer and PHY Layer.

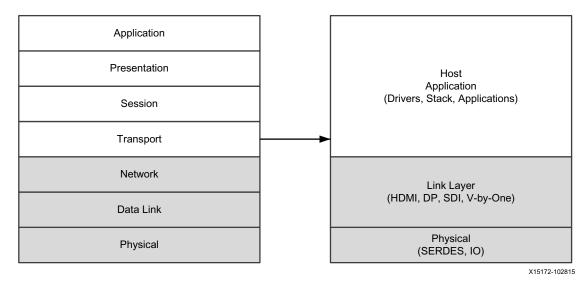

Figure 2-1 shows the standard OSI Model and mapping it with Video IP Solutions.

Figure 2-1: OSI Mapping of Video Systems

In accordance with the OSI model, the major PHY component for video IP cores is SerDes. Standardizing the SerDes delivery model provides benefits and flexibility for a video MAC layer at the system level.

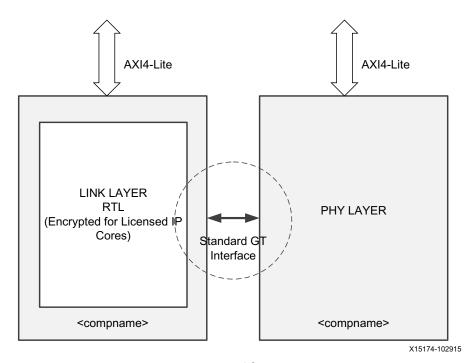

Figure 2-2 shows the boundary between these MAC and PHY layers and key highlights are:

- AXI4-Lite interface to provide software access

- AXI4-Stream-based GT channel interface for easier connectivity between different video link layers. (GT is also referred to as a serial transceiver.)

Figure 2-2: Video IP Layer

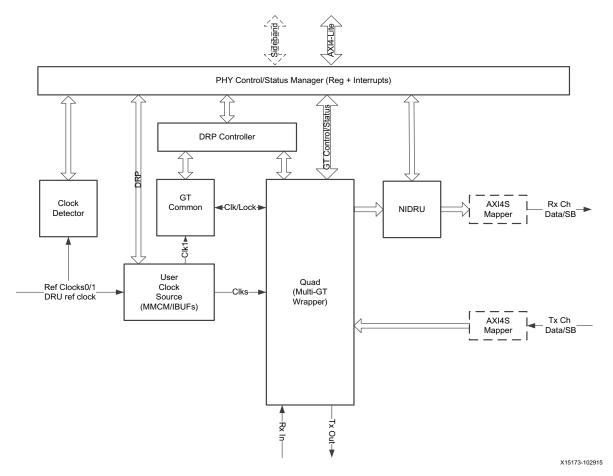

Figure 2-3 shows an overview of the internal structure of the Video PHY Controller core.

Figure 2-3: Video PHY Controller Core Block Diagram

# **PHY Control/Status Manager**

This block manages AXI4-Lite bus protocol accesses and handles memory map accesses and interrupt management.

#### **DRP Controller**

This block controls the handshake between AXI4-Lite access and GT DRP access. For example, this block latches DRP\_RDY and holds it until a read from AXI4-Lite is done. After a proper RDY handshake, a new dynamic reconfiguration port (DRP) transaction can be initiated.

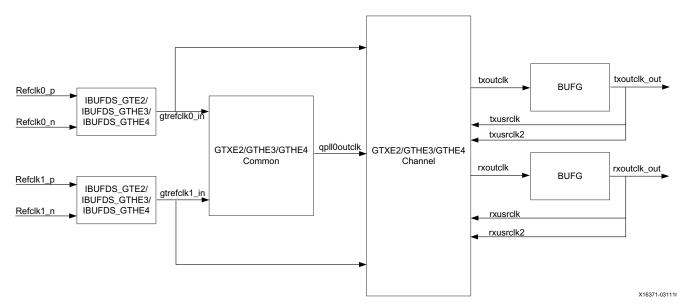

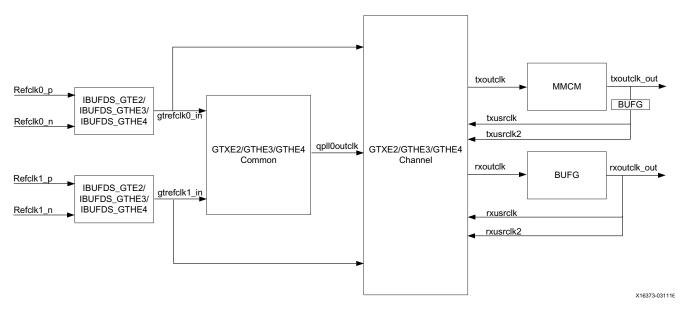

#### **User Clock Source**

This block has the GT Input clock buffers and generates USRCLK and USRCLK2 for GTs. In cases where the TX buffer is bypassed, a Mixed-mode clock manager (MMCM) generates the required output clocks based on TX/RXOUTCLK.

In HDMI, along with generating USRCLK and USRCLK2, this block also produces video clocks and differential and single-ended TX Transition Minimized Differential Signaling (TMDS) CLK as per requirement of the HDMI 1.4/2.0 Transmitter Subsystem LogiCORE IP Product Guide (PG235) [Ref 18] and HDMI 1.4/2.0 Receiver Subsystem LogiCORE IP Product Guide (PG236) [Ref 19]. It also buffers the RX TMDS CLK and forwards it as differential and single-ended clocks for generic use.

**Note:** The video clock maximum frequency is 297 MHz across all transceiver types except GTPE2 which is maxed at 148.5 MHz. This means GTPE2 cannot support video formats with video clocks > 148.5 MHz. For more information on HDMI clocking requirements, see the "Clocking" sections of HDMI 1.4/2.0 Transmitter Subsystem LogiCORE IP Product Guide (PG235) [Ref 18] and HDMI 1.4/2.0 Receiver Subsystem LogiCORE IP Product Guide (PG236) [Ref 19].

#### **GT Common**

This block controls the COMMON primitive of the serial transceiver. It has the external PLL management and DRP access. This block is available as part of the PHY top level in 7 series devices. For UltraScale™ devices, this block is part of the GT wizard core.

#### **AXI4-Stream Mapper**

This block/logic maps the GT input or output data according to the AXI4-Stream protocol defined in the GT specification.

#### **NI-DRU**

This block is used in applications where lower line rates (those below the rates supported by the respective GTs) are needed. In HDMI, the NI-DRU is enabled when the RX TMDS clock is below the threshold of the specific GT type.

- GTXE2 Thresholds:

- QPLL = 74.125 MHz

- CPLL = 80.000 MHz

- GTPE2 Thresholds:

- $\bullet$  PLL0/1 = 80.000 MHz

- GTHE3 and GTHE4 Thresholds:

- QPLL0 = 61.250 MHz

CPLL = 100.00 MHz

Note: QPLL1, is not used in NI-DRU mode.

NI-DRU requires an additional fixed reference clock to the GT RX on top of the RX TMDS clock to run the low line rate data recovery. For more information on the reference clock frequency requirement per transceiver type, see Video PHY HDMI Reference Clocks Requirements in Chapter 4.

#### **Performance**

The PHY Controller is designed to operate in coordination with the performance characteristics of the transceiver primitives it instantiates. For the DisplayPort protocol, a 2-byte and 4-byte internal datapaths are configured.

The following documents provide information about DC and AC switching characteristics. The frequency ranges specified by these documents must be adhered to for proper transceiver and core operation.

- Virtex UltraScale FPGAs Data Sheet: DC and AC Switching Characteristics (DS893) [Ref 2]

- Kintex UltraScale FPGAs Data Sheet: DC and AC Switching Characteristics (DS892)

[Ref 3]

- Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics (DS182) [Ref 4]

- Virtex-7 T and XT FPGAs Data Sheet: DC and AC Switching Characteristics (DS183) [Ref 5]

- Zynq UltraScale+ MPSoC Data Sheet: DC and AC Switching Characteristics (DS925) [Ref 6]

- Artix-7 FPGAs Data Sheet: DC and AC Switching Characteristics (DS181) [Ref 7]

#### **Resource Utilization**

For full details about performance and resource utilization, visit Performance and Resource Utilization.

The maximum clock frequency results were obtained by double-registering input and output ports to reduce dependence on I/O placement. The inner level of registers used a separate clock signal to measure the path from the input registers to the first output register through the core. The results are post-implementation, using tool default settings except for high effort.

The resource usage results do not include the characterization registers and represent the true logic used by the core. LUT counts include SRL16s or SRL32s.

Clock frequency does not take clock jitter into account and should be derated by an amount appropriate to the clock source jitter specification. The maximum achievable clock frequency and the resource counts might also be affected by other tool options, additional logic in the FPGA, using a different version of Xilinx tools, and other factors.

# **Port Descriptions**

Table 2-1 describes the ports and its interface definitions.

Table 2-1: PHY Controller Ports

| Name                                                      | Direction | Width      | Clock<br>Domain | Description                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------|-----------|------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                           |           | Clocking a | nd Reset        |                                                                                                                                                                                                                                                                            |

| mgtrefclk0_pad_(p/n)_in                                   | Input     | 1          |                 | Available when Advanced Clock Mode is disabled or when GTREFCLK0 is selected as one of the input clock sources in HDMI. User clock module instantiates input buffers.  • 7 series: Connects to GTREFCLK0  • UltraScale and UltraScale+: Connects to GTREFCLK00, GTREFCLK01 |

| mgtrefclk1_pad_(p/n)_in                                   | Input     | 1          |                 | Available when Advanced Clock Mode is disabled or when GTREFCLK1 is selected as one of the input clock sources in HDMI. User clock module instantiates input buffers.  • 7 series: Connects to GTREFCLK1  • UltraScale and UltraScale+: Connects to GTREFCLK10, GTREFCLK11 |

| mgtrefclk0_in<br>(For DisplayPort)                        | Input     | 1          |                 | Available when Advanced Clock Mode is enabled. You must instantiate input buffers at the system level. 7 series: Connects to GTREFCLK0                                                                                                                                     |

| mgtrefclk1_in<br>(For DisplayPort)                        | Input     | 1          |                 | Available when Advanced Clock Mode is enabled. You must instantiate input buffers at the system level. 7 series: Connects to GTREFCLK1                                                                                                                                     |

| gtgrefclk_in<br>(For 7 series devices and<br>DisplayPort) | Input     | 1          |                 | Available when Advanced Clock Mode is enabled. You must instantiate input buffers at the system level. Connects to GTGREFCLKO.                                                                                                                                             |

Table 2-1: PHY Controller Ports (Cont'd)

| Name                                                                     | Direction | Width | Clock<br>Domain | Description                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------|-----------|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

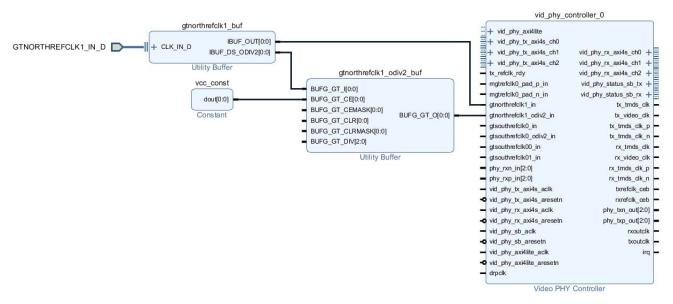

| gtnorthrefclk(0/1)_in                                                    | Input     | 1     |                 | Available when Advanced Clock Mode is enabled (DisplayPort) or when GTNORTHCLK0/1 is selected as one of the input clock sources. You must instantiate input buffers at the system level. Connects to GTNORTHREFCLK_0/1 ports.              |

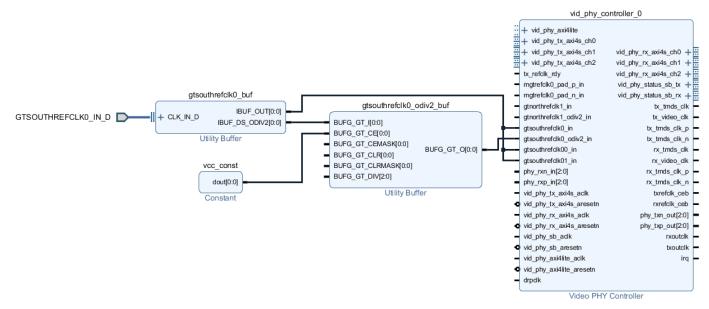

| gtsouthrefclk(0/1)_in                                                    | Input     | 1     |                 | Available when Advanced Clock Mode is enabled (DisplayPort) or when GTSOUTHREFCLK0/1 is selected as one of the input clock sources. You must instantiate input buffers at the system level. Connects to GTSOUTHREFCLK_0/1 ports.           |

| gtnorthrefclk(0/1)_odiv2_in<br>(For UltraScale and<br>UltraScale+ HDMI)  | Input     | 1     |                 | Available when GTNORTHREFCLK0/1 is selected as one of the input clock sources. This must be connected to the ODIV2 output of the gtnorthrefclk0/1_in input buffer. The ODIV2 output must be configured to output a divided-by-1 clock.     |

| gtsouthrefclk(0/1)_ odiv2_in<br>(For UltraScale and<br>UltraScale+ HDMI) | Input     | 1     |                 | Available when GTSOUTHREFCLK0/1 is selected as one of the input clock sources. This must be connected to the ODIV2 output of the gtsouthrefclk0/1_in input buffer. The ODIV2 output must be configured to output a divided-by-1 clock.     |

| gtnorthrefclk00_in<br>(For UltraScale and<br>UltraScale+ devices)        | Input     | 1     |                 | Available when Advanced Clock Mode is enabled (DisplayPort) or when GTNORTHREFCLK0 is selected as one of the input clock sources and QPLL0 is active. You must instantiate input buffers at the system level. Connects to GTNORTHREFCLK00. |

| gtnorthrefclk01_in<br>(For UltraScale and<br>UltraScale+ devices)        | Input     | 1     |                 | Available when Advanced Clock Mode is enabled (DisplayPort) or when GTNORTHREFCLK0 is selected as one of the input clock sources and QPLL1 is active. You must instantiate input buffers at the system level. Connects to GTNORTHREFCLK01. |

Table 2-1: PHY Controller Ports (Cont'd)

| Name                                                              | Direction | Width | Clock<br>Domain | Description                                                                                                                                                                                                                                |

|-------------------------------------------------------------------|-----------|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtnorthrefclk10_in<br>(For UltraScale and<br>UltraScale+ devices) | Input     | 1     |                 | Available when Advanced Clock Mode is enabled (DisplayPort) or when GTNORTHREFCLK1 is selected as one of the input clock sources and QPLL0 is active. You must instantiate input buffers at the system level. Connects to GTNORTHREFCLK10. |

| gtnorthrefclk11_in<br>(For UltraScale and<br>UltraScale+ devices) | Input     | 1     |                 | Available when Advanced Clock Mode is enabled (DisplayPort) or when GTNORTHREFCLK1 is selected as one of the input clock sources and QPLL1 is active. You must instantiate input buffers at the system level. Connects to GTNORTHREFCLK11. |

| gtsouthrefclk00_in<br>(For UltraScale and<br>UltraScale+ devices) | Input     | 1     |                 | Available when Advanced Clock Mode is enabled (DisplayPort) or when GTSOUTHREFCLK0 is selected as one of the input clock sources and QPLL0 is active. You must instantiate input buffers at the system level. Connects to GTSOUTHREFCLK00. |

| gtsouthrefclk01_in<br>(For UltraScale and<br>UltraScale+ devices) | Input     | 1     |                 | Available when Advanced Clock Mode is enabled (DisplayPort) or when GTSOUTHREFCLK0 is selected as one of the input clock sources and QPLL1 is active. You must instantiate input buffers at the system level. Connects to GTSOUTHREFCLK01. |

| gtsouthrefclk10_in<br>(For UltraScale and<br>UltraScale+ devices) | Input     | 1     |                 | Available when Advanced Clock Mode is enabled (DisplayPort) or when GTSOUTHREFCLK1 is selected as one of the input clock sources and QPLL0 is active. You must instantiate input buffers at the system level. Connects to GTSOUTHREFCLK10. |

| gtsouthrefclk11_in<br>(For UltraScale and<br>UltraScale+ devices) | Input     | 1     |                 | Available when Advanced Clock Mode is enabled (DisplayPort) or when GTSOUTHREFCLK1 is selected as one of the input clock sources and QPLL1 is active. You must instantiate input buffers at the system level. Connects to GTSOUTHREFCLK11. |

| gteastrefclk(0/1)_in<br>(For HDMI and GTPE2<br>devices)           | Input     |       |                 | Available when GTEASTREFCLK0/1 is selected as one of the input clock sources. Connects to GTEASTREFCLK0/1 ports.                                                                                                                           |

Table 2-1: PHY Controller Ports (Cont'd)

| Name                                                    | Direction | Width | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------|-----------|-------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwestrefclk(0/1)_in<br>(For HDMI and GTPE2<br>devices) | Input     |       |                 | Available when GTWESTREFCLK0/1 is selected as one of the input clock sources. Connects to GTWESTREFCLK0/1 ports.                                                                                                                                                                                                            |

| drpclk<br>(For UltraScale and<br>UltraScale+ devices)   | Input     | 1     |                 | Free running clock that is used to bring up the UltraScale device GT and to clock GT helper blocks.                                                                                                                                                                                                                         |

| vid_phy_tx_axi4s_aclk                                   | Input     | 1     |                 | Transmit Interface Clock                                                                                                                                                                                                                                                                                                    |

| vid_phy_tx_axi4s_aresetn                                | Input     | 1     | TXUSRCLK2       | Transmit Interface Reset Unused port. It can be tied HIGH or left unconnected.                                                                                                                                                                                                                                              |

| vid_phy_rx_axi4s_aclk                                   | Input     | 1     |                 | Receive Interface Clock                                                                                                                                                                                                                                                                                                     |

| vid_phy_rx_axi4s_aresetn                                | Input     | 1     | RXUSRCLK2       | Receive Interface Reset Unused port. It can be tied HIGH or left unconnected.                                                                                                                                                                                                                                               |

| vid_phy_sb_aclk                                         | Input     | 1     |                 | Sideband Interface Clock<br>Connect to AXI4-Lite Clock.                                                                                                                                                                                                                                                                     |

| vid_phy_sb_aresetn                                      | Input     | 1     | Sideband        | Sideband Interface Reset Unused port. It can be tied HIGH, left unconnected or connected to the ARESETN port of the PROC_SYS_RESET IP under vid_phy_sb_aclk clock domain.                                                                                                                                                   |

| txoutclk                                                | Output    | 1     |                 | Buffered clock sent out for fabric.<br>Available in HDMI when TX is enabled.                                                                                                                                                                                                                                                |

| rxoutclk                                                | Output    | 1     |                 | Buffered clock sent out for fabric.<br>Available in HDMI when RX is enabled.                                                                                                                                                                                                                                                |

| vid_phy_axi4lite_aclk                                   | Input     | 1     |                 | AXI Bus Clock                                                                                                                                                                                                                                                                                                               |

| vid_phy_axi4lite_aresetn                                | Input     | 1     | AXI4-Lite       | AXI Reset. Active-Low.  Must be connected to ARESETN that is synched to vid_phy_axi4lite_aclk port (i.e. peripheral_aresetn port of Processor System Reset IP)                                                                                                                                                              |

| tx_refclk_rdy<br>(For HDMI)                             | Input     | 1     | Async           | Active High (default): 1- Locked 0 - Unlocked. TX Reference Clock ready or lock indicator. Refer to Video PHY HDMI Reference Clocks Requirements in Chapter 4 for details about tx_refclk_rdy port implementation. Active level is controlled by Tx RefClk Rdy Active GUI parameter. If set to Low, 1 - Unlocked 0 - Locked |

| tx_tmds_clk<br>(For HDMI)                               | Output    | 1     |                 | TX TMDS Clock                                                                                                                                                                                                                                                                                                               |

Table 2-1: PHY Controller Ports (Cont'd)

| Name                                    | Direction | Width                                  | Clock<br>Domain | Description                                                                                                                                                                                                                              |

|-----------------------------------------|-----------|----------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_tmds_clk_p/n<br>(For HDMI)           | Output    | 1                                      |                 | Differential TX TMDS Clock output                                                                                                                                                                                                        |

| tx_video_clk<br>(For HDMI)              | Output    | 1                                      |                 | TX Video Clock                                                                                                                                                                                                                           |

| txrefclk_ceb<br>(For HDMI)              | Output    | 1                                      | AXI4-Lite       | TX external reference clock IBUFDS CEB. Available when TX selects reference clock source from NORTH, SOUTH, EAST, or WEST. Example GTNORTHREFCLK_0/1.                                                                                    |

| rx_tmds_clk<br>(For HDMI)               | Output    | 1                                      |                 | RX TMDS Clock                                                                                                                                                                                                                            |

| rx_tmds_clk_p/n<br>(For HDMI)           | Output    | 1                                      |                 | 3-state differential RX TMDS Clock output                                                                                                                                                                                                |

| rx_video_clk<br>(For HDMI)              | Output    | 1                                      |                 | RX Video Clock                                                                                                                                                                                                                           |

| rxrefclk_ceb<br>(For HDMI)              | Output    | 1                                      | AXI4-Lite       | RX external reference clock IBUFDS CEB. Available when RX selects reference clock source from NORTH, SOUTH, EAST, or WEST. Example GTNORTHREFCLK_0/1.                                                                                    |

|                                         |           | GT Chan                                | nels            |                                                                                                                                                                                                                                          |

| phy_rx[p/n]_in                          | Input     | 1* Num.<br>channels                    | Serial          | Positive and Negative inputs of the transceiver channel.                                                                                                                                                                                 |

| phy_tx[p/n]_out                         | Output    | 1* Num.<br>channels                    | Serial          | Positive and Negative outputs of the transceiver channel.                                                                                                                                                                                |

| vid_phy_tx_axi4s_ch <i>_<br/>tready</i> | Output    | 1                                      | TXUSRCLK2       | AXI4-Stream based tready indicator <i>: Transceiver channel index</i>                                                                                                                                                                    |

| vid_phy_tx_axi4s_ch <i>_<br/>tvalid</i> | Input     | 1                                      | TXUSRCLK2       | AXI4-Stream based tvalid indicator. <i>: Transceiver channel index</i>                                                                                                                                                                   |

| vid_phy_tx_axi4s_ch <i>_<br/>tdata</i>  | Input     | TX_DATA_WIDTH                          | TXUSRCLK2       | AXI4-Stream based tdata bus <i>: Transceiver channel index GT Mapping: TXDATA_IN</i>                                                                                                                                                     |

| vid_phy_tx_axi4s_ch < i > _<br>tuser    | Input     | TX_USER_WIDTH For DisplayPort: 12 bits | TXUSRCLK2       | AXI4-Stream based tuser bus <i>: Transceiver channel index GT Mapping: {TXCHARDISPVAL, TXCHARDISPMODE, TXCHARISK} In UltraScale and UltraScale+ devices, TXCHARDISPVAL and TXCHARDISPMODE are represented using TXCTLR0 and TXCTRL1.</i> |

| vid_phy_rx_axi4s_ch <i>_<br/>tready</i> | Input     | 1                                      | RXUSRCLK2       | AXI4-Stream based tready indicator <i>: Transceiver channel index</i>                                                                                                                                                                    |

Table 2-1: PHY Controller Ports (Cont'd)

| Name                                    | Direction | Width                                        | Clock<br>Domain | Description                                                                                                                                                                                                                                  |

|-----------------------------------------|-----------|----------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vid_phy_rx_axi4s_ch <i>_<br/>tvalid</i> | Output    | 1                                            | RXUSRCLK2       | AXI4-Stream based tvalid indicator.<br><i>: Transceiver channel index</i>                                                                                                                                                                    |

| vid_phy_rx_axi4s_ch <i>_<br/>tdata</i>  | Output    | RX_DATA_WIDTH                                | RXUSRCLK2       | AXI4-Stream based tdata bus <i>: Transceiver channel index GT Mapping: RXDATAOUT</i>                                                                                                                                                         |

| vid_phy_rx_axi4s_ch <i>_<br/>tuser</i>  | Output    | RX_USER_WIDTH<br>For DisplayPort:<br>12 bits | RXUSRCLK2       | AXI4-Stream based tuser bus <i>: Transceiver channel index GT Mapping: {RXNOTINTABLE, RXDISPERR, RXCHARISK} In UltraScale and UltraScale+ devices, RXNOTINTABLE, RXDISPERR, RXCHARISK are represented using RXCTRL0, RXCTR1 and RXCTRL3.</i> |

|                                         |           | Sideband Signal                              | s (Optional)    |                                                                                                                                                                                                                                              |

| vid_phy_control_sb_tx_<br>tready        | Output    | 1                                            | Sideband        | AXI4-Stream based tready indicator                                                                                                                                                                                                           |

| vid_phy_control_sb_tx_tdata             | Input     | 1                                            | Sideband        | AXI4-Stream based tdata bus<br>Not used by the DisplayPort Protocol                                                                                                                                                                          |

| vid_phy_control_sb_tx_<br>tvalid        | Input     | 1                                            | Sideband        | AXI4-Stream based tvalid                                                                                                                                                                                                                     |

| vid_phy_status_sb_tx_tready             | Input     | 1                                            | Sideband        | AXI4-Stream based tready indicator                                                                                                                                                                                                           |

| vid_phy_status_sb_tx_tdata              | Output    | 8 (DisplayPort)<br>1 (HDMI)                  | Sideband        | AXI4-Stream based tdata bus For DisplayPort Protocol, refer to Table 2-2. For the HDMI protocol, refer to Table 2-3.                                                                                                                         |

| vid_phy_status_sb_tx_tvalid             | Output    | 1                                            | Sideband        | AXI4-Stream based tvalid                                                                                                                                                                                                                     |

| vid_phy_control_sb_rx_<br>tready        | Output    | 1                                            | Sideband        | AXI4-Stream based tready indicator                                                                                                                                                                                                           |

| vid_phy_control_sb_rx_tdata             | Input     | 8                                            | Sideband        | AXI4-Stream based tdata bus<br>For DisplayPort Protocol, refer to<br>Table 2-4.                                                                                                                                                              |

| vid_phy_control_sb_rx_<br>tvalid        | Input     | 1                                            | Sideband        | AXI4-Stream based tvalid                                                                                                                                                                                                                     |

| vid_phy_status_sb_rx_tready             | Input     | 1                                            | Sideband        | AXI4-Stream based tready indicator                                                                                                                                                                                                           |

| vid_phy_status_sb_rx_tdata              | Output    | 16 (DisplayPort)<br>2 (HDMI)                 | Sideband        | AXI4-Stream based tdata bus For DisplayPort Protocol, refer to Table 2-5. For the HDMI protocol, refer to Table 2-6.                                                                                                                         |

| vid_phy_status_sb_rx_tvalid             | Output    | 1                                            | Sideband        | AXI4-Stream based tvalid                                                                                                                                                                                                                     |

Table 2-1: PHY Controller Ports (Cont'd)

| Name                     | Direction         | Width | Clock<br>Domain | Description          |  |  |  |

|--------------------------|-------------------|-------|-----------------|----------------------|--|--|--|

|                          | AXI4-Lite Signals |       |                 |                      |  |  |  |

| vid_phy_axi4lite_awaddr  | Input             | 10    | AXI4-Lite       | Write address        |  |  |  |

| vid_phy_axi4lite_awprot  | Input             | 3     | AXI4-Lite       | Protection type      |  |  |  |

| vid_phy_axi4lite_awvalid | Input             | 1     | AXI4-Lite       | Write address valid  |  |  |  |

| vid_phy_axi4lite_awready | Output            | 1     | AXI4-Lite       | Write address ready  |  |  |  |

| vid_phy_axi4lite_awdata  | Input             | 32    | AXI4-Lite       | Write data bus       |  |  |  |

| vid_phy_axi4lite_awstrb  | Input             | 4     | AXI4-Lite       | Write strobes        |  |  |  |

| vid_phy_axi4lite_wvalid  | Input             | 1     | AXI4-Lite       | Write valid          |  |  |  |

| vid_phy_axi4lite_wready  | Output            | 1     | AXI4-Lite       | Write ready          |  |  |  |

| vid_phy_axi4lite_bresp   | Output            | 2     | AXI4-Lite       | Write response       |  |  |  |

| vid_phy_axi4lite_bvalid  | Output            | 1     | AXI4-Lite       | Write response valid |  |  |  |

| vid_phy_axi4lite_bready  | Input             | 1     | AXI4-Lite       | Response ready       |  |  |  |

| vid_phy_axi4lite_araddr  | Input             | 10    | AXI4-Lite       | Read address         |  |  |  |

| vid_phy_axi4lite_arprot  | Input             | 3     | AXI4-Lite       | Protection type      |  |  |  |

| vid_phy_axi4lite_arvalid | Input             | 1     | AXI4-Lite       | Read address valid   |  |  |  |

| vid_phy_axi4lite_arready | Output            | 1     | AXI4-Lite       | Read address ready   |  |  |  |

| vid_phy_axi4lite_rdata   | Output            | 32    | AXI4-Lite       | Read data            |  |  |  |

| vid_phy_axi4lite_rresp   | Output            | 2     | AXI4-Lite       | Read response        |  |  |  |

| vid_phy_axi4lite_rvalid  | Output            | 1     | AXI4-Lite       | Read valid           |  |  |  |

| vid_phy_axi4lite_rready  | Input             | 1     | AXI4-Lite       | Read ready           |  |  |  |

| irq                      | Output            | 1     | AXI4-Lite       | Interrupt output     |  |  |  |

# **Sideband Definitions**

## **DisplayPort Transmit — Control Path**

No control signals are transferred from the DisplayPort Link to DisplayPort PHY Layer.

### DisplayPort Transmit — Status Path

The following status is transferred to the Link Layer. The status bits are driven using the AXI4-Lite Clock.

Table 2-2: DisplayPort Transmit Status Sideband Definition

| Bit Position | Status Details                                                   |

|--------------|------------------------------------------------------------------|

| 0            | Bank 0, GT Channel 0, TX Reset Done                              |

| 1            | Based on TXSYSCLKSEL[0], CPLL Channel 0/QPLL Lock is transferred |

| 2            | Bank 1, GT Channel 1, TX Reset Done                              |

| 3            | Based on TXSYSCLKSEL[0], CPLL Channel 1/QPLL Lock is transferred |

| 4            | Bank 0, GT Channel 2, TX Reset Done                              |

| 5            | Based on TXSYSCLKSEL[2], CPLL Channel 2/QPLL Lock is transferred |

| 6            | Bank 0, GT Channel 3, TX Reset Done                              |

| 7            | Based on TXSYSCLKSEL[3], CPLL Channel 3/QPLL Lock is transferred |

## **HDMI Transmit** — Status Path

The following status is transferred to the Link Layer. The status bits are driven using the AXI4-Lite Clock.

Table 2-3: HDMI Transmit Status Sideband Definition

| Bit Position | Status Details                                                                                               |

|--------------|--------------------------------------------------------------------------------------------------------------|

| 0            | TX Link Ready. This signal is asserted to indicate that the GT TX initialization is completed (txresetdone). |

| 1            | TX Video Ready. This signal is asserted to indicate that the video clock from TX DCM block is stable.        |

# **DisplayPort Receive — Control Path**

The following control is transferred from the Link Layer. The control bits are driven using the AXI4-Lite Clock.

Table 2-4: DisplayPort Receive Control Sideband Definition

| <b>Bit Position</b> | Status Details                                                                                                                                                                         |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0                   | Training Iteration GT Reset.  Pulse generated for every access of the DPCD TRAINING_LANEO_SET register which can be used to reset the GT to eliminate buffer errors and bad CDR locks. |  |

| 1                   | Start of TP1 Reset. Pulse generated whenever TP1 pattern starts. This can be used to reset the GT for a clean start of training sequence.                                              |  |

# DisplayPort Receive — Status Path

The following status is transferred to the Link Layer. The status bits are driven using the AXI4-Lite Clock.

Table 2-5: Receive Status Sideband Definition

| Bit Position                                                       | Status Details                                                   |  |

|--------------------------------------------------------------------|------------------------------------------------------------------|--|

| 0                                                                  | Bank 0, GT Channel 0, RX Reset Done                              |  |

| 1                                                                  | Based on RXSYSCLKSEL[0], CPLL Channel 0/QPLL Lock is transferred |  |

| 2                                                                  | Bank 0, GT Channel 0, RX Byte Is Aligned output                  |  |

| 3                                                                  | Bank 0, GT Channel 1, RX Reset Done                              |  |

| 4                                                                  | Based on RXSYSCLKSEL[0], CPLL Channel 1/QPLL Lock is transferred |  |

| 5                                                                  | Bank 0, GT Channel 1, RX Byte Is Aligned output                  |  |

| 6 Bank 0, GT Channel 2, RX Reset Done                              |                                                                  |  |

| 7 Based on RXSYSCLKSEL[0], CPLL Channel 2/QPLL Lock is transferred |                                                                  |  |

| 8                                                                  | Bank 0, GT Channel 2, RX Byte Is Aligned output                  |  |

| 9                                                                  | Bank 0, GT Channel 3, RX Reset Done                              |  |

| 10                                                                 | Based on RXSYSCLKSEL[0], CPLL Channel 3/QPLL Lock is transferred |  |

| 11                                                                 | Bank 0, GT Channel 3, RX Byte Is Aligned output                  |  |

#### **HDMI Receive** — Status Path

The following status is transferred to the Link Layer. The status bits are driven using the AXI4-Lite Clock.

Table 2-6: HDMI Receive Status Sideband Definition

| Bit Position | Status Details                                                                                               |

|--------------|--------------------------------------------------------------------------------------------------------------|

| 0            | RX Link Ready. This signal is asserted to indicate that the GT RX initialization is completed (rxresetdone). |

| 1            | RX Video Ready. This signal is asserted to indicate that the video clock from the RX DCM block is stable.    |

# **Register Space**

The PHY configuration data is implemented as a set of distributed registers that can be read or written from the AXI4-Lite interface. These registers are synchronous to the AXI4-Lite domain.

Any bits not specified in Table 2-7 are considered reserved and return 0 upon read. The power-on reset values of control registers are 0 unless specified in the definition. Only address offsets are listed in Table 2-7 and the base address is configured by the AXI interconnect at the system level.

Table 2-7: Register Map

| Address | Access | Register Name                   | Details                                                                                                                                                                                                                                                                                                                                                                     |

|---------|--------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000  | RO     | Version Register (VR)           | For video_phy_controller_v2_0, VR is 32'h02_00_00_00. [31:24]: Core major version. [23:16]: Core minor version. [15:12]: Core version revision. [11:8]: Core Patch details. [7:0]: Internal revision.                                                                                                                                                                       |

| 0x0004  |        |                                 | Reserved                                                                                                                                                                                                                                                                                                                                                                    |

| 0x0008  |        |                                 | Reserved                                                                                                                                                                                                                                                                                                                                                                    |

| 0x000C  | RW     | Bank Select (BSR)               | [4:0]: TX Bank Selection (Default value is 0) [12:8]: RX Bank Selection (Default value is 0)                                                                                                                                                                                                                                                                                |

|         |        | Shared Fe                       | atures and Resets                                                                                                                                                                                                                                                                                                                                                           |

| 0x0010  | RW     | Reference Clock Selection (RCS) | [3:0]: QPLL (GTXE2) / QPLL0REFCLKSEL (GTHE3/GTHE4) / PLL0REFCLKSEL (GTPE2) [7:4]: CPLLREFCLKSEL [11:8]: QPLL1REFCLKSEL (For UltraScale/UltraScale+devices)/PLL1REFCLKSEL (GTPE2) [15:12]: Reserved [19:16]: Reserved [23:20]: Reserved [27:24]: {TXSYSCLKSEL[1:0], RXSYSCLKSEL[1:0]} [31:28]: {TXPLLCLKSEL[1:0], RXPLLCLKSEL[1:0]} - For UltraScale and UltraScale+ devices |

| 0x0014  | RW     | PLL Reset (PR)                  | DisplayPort only. Not used in HDMI.  0: CPLLRESET  1: QPLL0RESET  2: QPLL1RESET – For UltraScale and UltraScale+ devices                                                                                                                                                                                                                                                    |

| 0x0018  | RO     | PLL Lock Status (PLS)           | 0: CPLLLOCK - Ch0 1: CPLLLOCK - Ch1 2: CPLLLOCK - Ch2 3: CPLLLOCK - Ch3 4: QPLL/QPLL0LOCK/PLL0LOCK 5: QPLL1LOCK - For UltraScale/UltraScale+ devices PLL1LOCK                                                                                                                                                                                                               |

Table 2-7: Register Map (Cont'd)

| Address | Access | Register Name           | Details            |

|---------|--------|-------------------------|--------------------|

| 0x001C  | RW     | TX Initialization (TXI) | Channel 1:         |

|         |        |                         | • 0: GTTXRESET     |

|         |        |                         | • 1: TXPMARESET    |

|         |        |                         | • 2: TXPCSRESET    |

|         |        |                         | • 3: TXUSERRDY     |

|         |        |                         | • 6:4: Reserved    |

|         |        |                         | • 7: PLL_GT_RESET  |

|         |        |                         | Channel 2:         |

|         |        |                         | • 8: GTTXRESET     |

|         |        |                         | • 9: TXPMARESET    |

|         |        |                         | • 10: TXPCSRESET   |

|         |        | • 11: TXUSERRDY         |                    |

|         |        |                         | • 14:12: Reserved  |

|         |        |                         | • 15: PLL_GT_RESET |

|         |        |                         | Channel 3:         |

|         |        |                         | • 16: GTTXRESET    |

|         |        |                         | • 17: TXPMARESET   |

|         |        |                         | • 18: TXPCSRESET   |

|         |        | • 19: TXUSERRDY         |                    |

|         |        | • 22:20: Reserved       |                    |

|         |        |                         | • 23: PLL_GT_RESET |

|         |        | Channel 4:              |                    |

|         |        |                         | • 24: GTTXRESET    |

|         |        |                         | • 25: TXPMARESET   |

|         |        |                         | • 26: TXPCSRESET   |

|         |        |                         | • 27: TXUSERRDY    |

|         |        |                         | • 30:28: Reserved  |

|         |        |                         | • 31: PLL_GT_RESET |

Table 2-7: Register Map (Cont'd)

| Address | Access | Register Name                                              | Details                                                    |

|---------|--------|------------------------------------------------------------|------------------------------------------------------------|

| 0x0020  | RO     | TX Initialization Status (TXIS)                            | Channel 1: • 0: TXRESETDONE                                |

|         |        |                                                            | • 1: TXPMARESETDONE <sup>(1)</sup>                         |

|         |        |                                                            | • 2: GTPOWERGOOD (For UltraScale+ devices) <sup>(2)</sup>  |

|         |        |                                                            | • 7:3: Reserved                                            |

|         |        |                                                            | Channel 2:                                                 |

|         |        |                                                            | 8: TXRESETDONE                                             |

|         |        | • 9: TXPMARESETDONE <sup>(1)</sup>                         |                                                            |

|         |        |                                                            | • 10: GTPOWERGOOD (For UltraScale+ devices) <sup>(2)</sup> |

|         |        |                                                            | • 15:11: Reserved                                          |

|         |        |                                                            | Channel 3:                                                 |

|         |        |                                                            | • 16: TXRESETDONE                                          |

|         |        |                                                            | • 17: TXPMARESETDONE <sup>(1)</sup>                        |

|         |        | • 18: GTPOWERGOOD (For UltraScale+ devices) <sup>(2)</sup> |                                                            |

|         |        | • 23:19: Reserved                                          |                                                            |

|         |        | Channel 4:                                                 |                                                            |

|         |        |                                                            | • 24: TXRESETDONE                                          |

|         |        |                                                            | • 25: TXPMARESETDONE <sup>(1)</sup>                        |

|         |        |                                                            | • 26: GTPOWERGOOD (For UltraScale+ devices) <sup>(2)</sup> |

|         |        |                                                            | • 31:27: Reserved                                          |

Table 2-7: Register Map (Cont'd)

| Address | Access | Register Name           | Details                            |

|---------|--------|-------------------------|------------------------------------|

| 0x0024  | RW     | RX Initialization (RXI) | Channel 1:                         |

|         |        |                         | 0: GTRXRESET                       |

|         |        |                         | • 1: RXPMARESET                    |

|         |        |                         | • 2: RXDFELPMRESET <sup>(3)</sup>  |

|         |        |                         | • 3: EYESCANRESET <sup>(4)</sup>   |

|         |        |                         | • 4: RXPCSRESET <sup>(4)</sup>     |

|         |        |                         | • 5: RXBUFRESET                    |

|         |        |                         | • 6: RXUSERRDY <sup>(5)</sup>      |

|         |        |                         | • 7: PLL_GT_RESET                  |

|         |        |                         | Channel 2:                         |

|         |        |                         | 8: GTRXRESET                       |

|         |        |                         | • 9: RXPMARESET                    |

|         |        |                         | • 10: RXDFELPMRESET <sup>(3)</sup> |

|         |        |                         | • 11: EYESCANRESET <sup>(4)</sup>  |

|         |        |                         | • 12: RXPCSRESET <sup>(4)</sup>    |

| i       |        |                         | • 13: RXBUFRESET                   |

|         |        |                         | • 14: RXUSERRDY <sup>(5)</sup>     |

|         |        |                         | • 15: PLL_GT_RESET                 |

|         |        |                         | Channel 3:                         |

|         |        |                         | • 16: GTRXRESET                    |

|         |        |                         | • 17: RXPMARESET                   |

|         |        |                         | • 18: RXDFELPMRESET <sup>(3)</sup> |

|         |        |                         | • 19: EYESCANRESET <sup>(4)</sup>  |

|         |        |                         | • 20: RXPCSRESET <sup>(4)</sup>    |

|         |        |                         | • 21: RXBUFRESET                   |

|         |        |                         | • 22: RXUSERRDY <sup>(5)</sup>     |

|         |        |                         | • 23: PLL_GT_RESET                 |

|         |        |                         | Channel 4:                         |

|         |        |                         | • 24: GTRXRESET                    |

|         |        |                         | • 25: RXPMARESET                   |

|         |        |                         | • 26: RXDFELPMRESET <sup>(3)</sup> |

|         |        |                         | • 27: EYESCANRESET <sup>(4)</sup>  |

| 1       |        |                         | • 28: RXPCSRESET <sup>(4)</sup>    |

|         |        |                         | • 29: RXBUFRESET                   |

|         |        |                         | • 30: RXUSERRDY <sup>(5)</sup>     |

|         |        |                         | • 31: PLL_GT_RESET                 |

Table 2-7: Register Map (Cont'd)

| Address | Access | Register Name                           | Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|--------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0028  | RO     | RX Initialization Status (RXIS)         | Channel 1:  O: RXRESETDONE  1: RXPMARESETDONE <sup>(6)</sup> 2: GTPOWERGOOD (For UltraScale+ devices) <sup>(2)</sup> 7:3: Reserved Channel 2:  8: RXRESETDONE  9: RXPMARESETDONE <sup>(6)</sup> 10: GTPOWERGOOD (For UltraScale+ devices) <sup>(2)</sup> 15:11: Reserved Channel 3:  16: RXRESETDONE  17: RXPMARESETDONE <sup>(6)</sup> 18: GTPOWERGOOD (For UltraScale+ devices) <sup>(2)</sup> 23:19: Reserved Channel 4:  24: RXRESETDONE  25: RXPMARESETDONE <sup>(6)</sup> 26: GTPOWERGOOD (For UltraScale+ devices) <sup>(2)</sup> 31:27: Reserved |

| 0x002C  | RW     | IBUFDS GTxx Control<br>(IBUFDSGTxxCTRL) | This control is used manage CEB pin of IBUFDS_GTE2/3 based on device. Low (0) to enable; High (1) to disable.  0: GTREFCLK0_CEB  1: GTREFCLK1_CEB  Bank based programming. You must change the appropriate Bank number when working with Multi-Quad.                                                                                                                                                                                                                                                                                                     |

Table 2-7: Register Map (Cont'd)

| Address | Access | Register Name            | Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|--------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |        | ı                        | Power Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0x0030  | RW     | Power Down Control (PDC) | Channel 1:  O: CPLLPD(7)  1: QPLL0PD/PLL0PD  2: QPLL1PD (For UltraScale and UltraScale+ devices)/PLL1PD  4:3: RXPD[1:0]  6:5: TXPD[1:0]  7: Reserved Channel 2:  8: CPLLPD  9: QPLL0PD(8)  10: QPLL1PD (For UltraScale and UltraScale+ devices)  12:11: RXPD[1:0]  14:13: TXPD[1:0]  15: Reserved Channel 3:  16: CPLLPD  17: QPLL0PD(8)  18: QPLL1PD (For UltraScale and UltraScale+ devices)  20:19: RXPD[1:0]  22:21: TXPD[1:0]  22:21: TXPD[1:0]  23: Reserved Channel 4:  24: CPLLPD  25: QPLL0PD(8)  26: QPLL1PD (For UltraScale and UltraScale+ devices)  28:27: RXPD[1:0]  30:29: TXPD[1:0]  31: Reserved  Reserved |

|         |        |                          | Loopback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0x0038  | RW     | Loopback Control (LBC)   | Channel 1:  • 2:0: LOOPBACK[2:0]  • 7:3: Reserved Channel 2:  • 10:8: LOOPBACK[2:0]  • 15:11: Reserved Channel 3:  • 18:16: LOOPBACK[2:0]  • 23:19: Reserved Channel 4:  • 26:24: LOOPBACK[2:0]  • 31:27: Reserved                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 2-7: Register Map (Cont'd)

| Address | Access | Register Name                     | Details                                                                                                                                            |

|---------|--------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x003C  |        |                                   | Reserved                                                                                                                                           |

|         | I      | Dynamic Re                        | econfiguration Port (DRP)                                                                                                                          |

| 0x0040  | RW     | DRP CONTROL Channel1<br>(DRPCCH1) | 11:0: DRPADDR[8:0] 12: DRPEN 13: DRPWE 14: DRP Reset (For UltraScale and UltraScale+ devices) <sup>(8)</sup> 15: Reserved 31:16: DRPDI [15:0]      |

| 0x0044  | RW     | DRP CONTROL Channel2<br>(DRPCCH2) | 11:0: DRPADDR[8:0] 12: DRPEN 13: DRPWE 14: DRP Reset (For UltraScale and UltraScale+ devices) <sup>(8)</sup> 15: Reserved 31:16: DRPDI [15:0]      |

| 0x0048  | RW     | DRP CONTROL Channel3<br>(DRPCCH3) | 11:0: DRPADDR[8:0] 12: DRPEN 13: DRPWE 14: DRP Reset (For UltraScale and UltraScale+ devices) <sup>(8)</sup> 15: Reserved 31:16: DRPDI [15:0]      |

| 0x004C  | RW     | DRP CONTROL Channel4<br>(DRPCCH4) | 11:0: DRPADDR[8:0] 12: DRPEN 13: DRPWE 14: DRP Reset (For UltraScale and UltraScale+ devices) <sup>(8)</sup> 15: Reserved 31:16: DRPDI [15:0]      |

| 0x0050  | RO     | DRP STATUS Channel1<br>(DRPSCH1)  | 15:0: DRPDO[15:0] – Valid for Read Transfers<br>16: DRPRDY (Indicates valid transfer)<br>17: DRPBUSY (Indicated DRP port free)<br>31:18: Reserved  |

| 0x0054  | RO     | DRP STATUS Channel2<br>(DRPSCH2)  | 15:0: DRPDO[15:0] – Valid for Read Transfers<br>16: DRPRDY (Indicates valid transfer)<br>17: DRP BUSY (Indicated DRP port free)<br>31:18: Reserved |

| 0x0058  | RO     | DRP STATUS Channel3<br>(DRPSCH3)  | 15:0: DRPDO[15:0] – Valid for Read Transfers<br>16: DRPRDY (Indicates valid transfer)<br>17: DRP BUSY (Indicated DRP port free)<br>31:18: Reserved |

| 0x005C  | RO     | DRP STATUS Channel4<br>(DRPSCH4)  | 15:0: DRPDO[15:0] – Valid for Read Transfers 16: DRPRDY (Indicates valid transfer) 17: DRP BUSY (Indicated DRP port free) 31:18: Reserved          |

Table 2-7: Register Map (Cont'd)

| Address               | Access                | Register Name              | Details                                                                                                                                   |

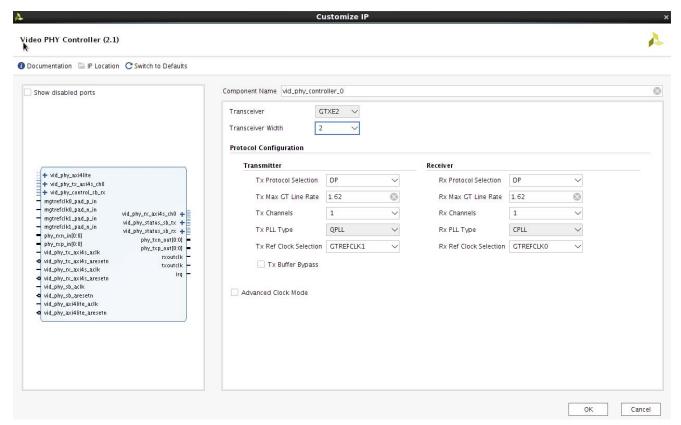

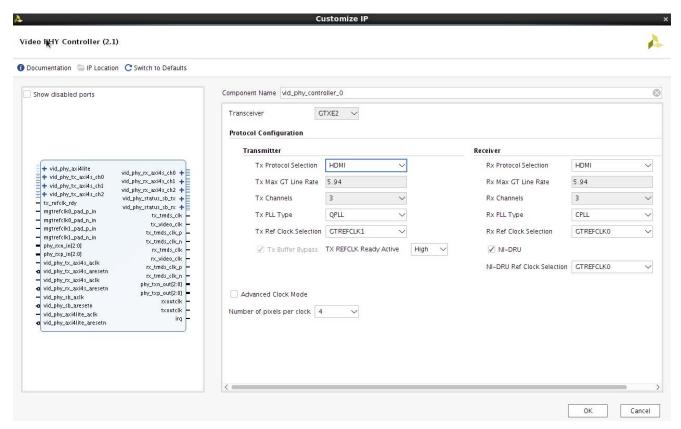

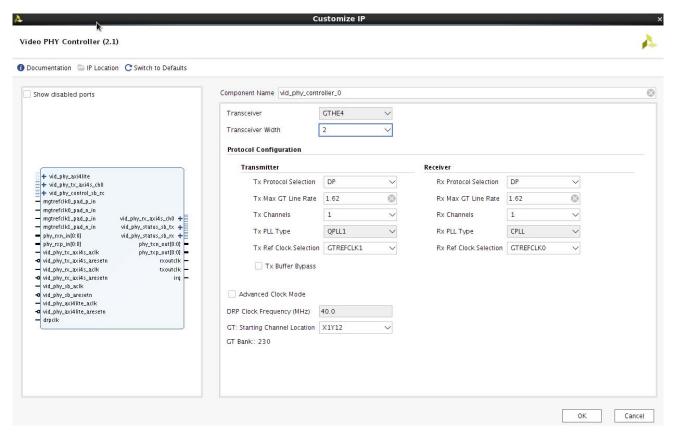

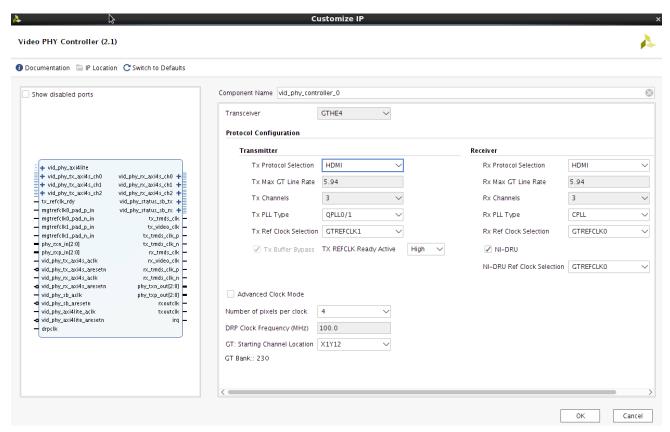

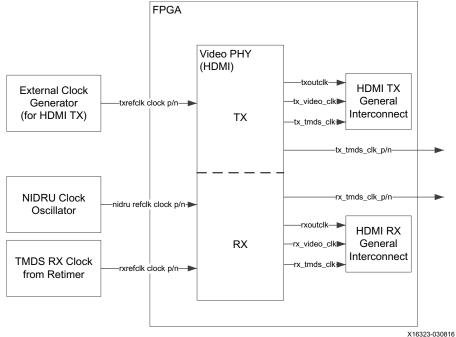

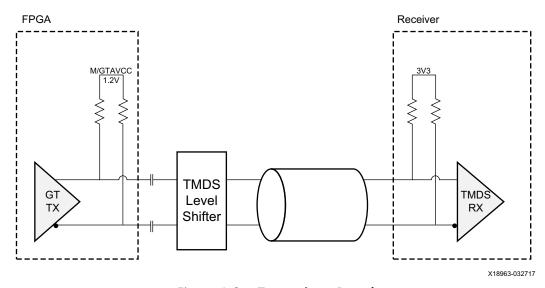

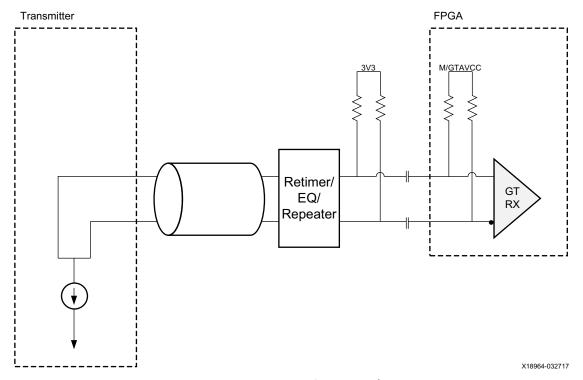

|-----------------------|-----------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|