# Video over IP FEC **Transmitter v2.0**

# LogiCORE IP Product Guide

**Vivado Design Suite**

PG206 October 5, 2016

# **Table of Contents**

#### **IP Facts**

| Chapter 1. Overview                                        |    |

|------------------------------------------------------------|----|

| Feature Summary                                            | 7  |

| Applications                                               | 7  |

| Licensing and Ordering Information                         | 8  |

| Chapter 2: Product Specification                           |    |

| Architecture Overview                                      | 9  |

| Standards                                                  | 10 |

| Performance                                                | 10 |

| Resource Utilization                                       | 10 |

| Port Descriptions                                          |    |

| Register Space                                             | 20 |

|                                                            |    |

| Chapter 3: Designing with the Core                         |    |

| General Design Guidelines                                  | 26 |

| Chapter 4: Design Flow Steps                               |    |

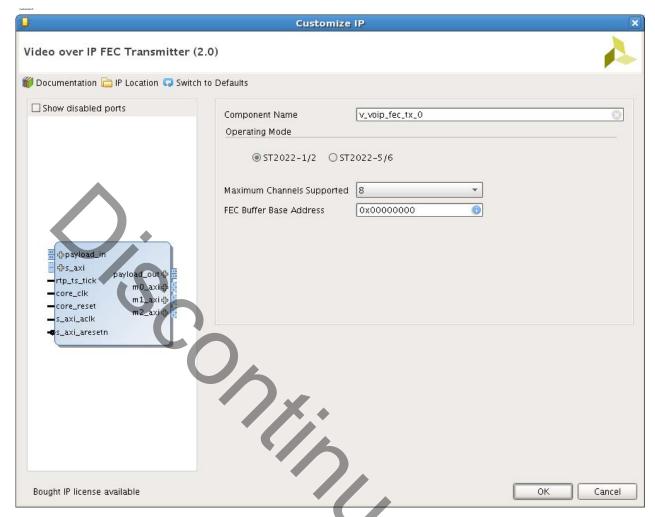

| Customizing and Generating the Core                        | 29 |

| Constraining the Core                                      | 31 |

| Simulation                                                 | 32 |

| Synthesis and Implementation                               | 32 |

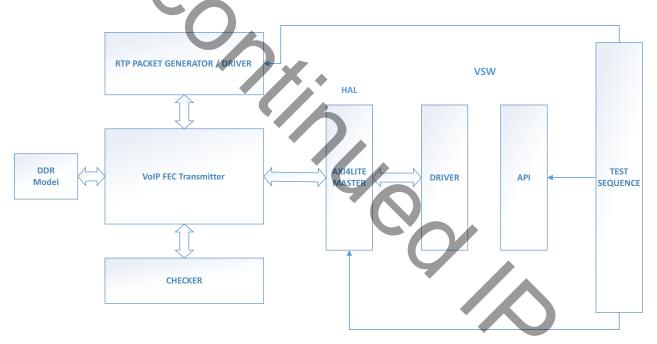

| Chapter 5: Test Bench                                      |    |

| Appendix A: Verification, Compliance, and Interoperability |    |

| Appendix B: Migrating and Upgrading                        |    |

| Upgrading in the Vivado Design Suite                       | 36 |

| Appendix C: Debugging                                      |    |

| Finding Help on Xilinx.com                                 | 38 |

| Debug Tools                                                |    |

| •                                                          | -  |

| KOGRA | MMABLE»                                                           |

|-------|-------------------------------------------------------------------|

| Н     | imulation Debug                                                   |

| Δрр   | endix D: Additional Resources and Legal Notices and Legal Notices |

|       | ilinx Resources                                                   |

|       | eferences 40                                                      |

|       | evision History                                                   |

| Н     | lease Read: Important Legal Notices                               |

#### Introduction

The Xilinx® LogiCORE™ IP Video over IP FEC Transmitter is a broadcast application module that transmits additional redundant packets along with the original incoming packets to help the receiver recover the possible loss of packets due to a network error. The redundant packets are Real time Transport Protocol (RTP) encapsulated payloads using SMPTE ST 2022-1 and SMPTE ST 2022-5 Forward Error Correction (FEC) method. It is capable of handling number of video streams and is suited for deploying SMPTE ST 2022-1 stream in 1 Gb/s networks and SMPTE ST 2022-5 streams in 10 Gb/s networks. This core is used for developing Internet Protocol-based systems that reduce the overall cost of distribution and routing of audio and video data.

#### **Features**

- SMPTE ST 2022-1 and SMPTE ST 2022-5 based FEC encoding

- Up to 512 channels for SMPTE ST 2022-1 based FEC encoding scheme and up to 8 channels for SMPTE ST 2022-5 based FEC encoding scheme (configurable at compilation time)

- FEC matrix selection per channel

- SMPTE ST 2022-1 FEC matrix selection per channel

- 1 <= FEC L <= 20

- 4 <= FEC D <= 20

- FEC L \* FEC D <= 100

| LogiCORE IP Facts Table                           |                                                                             |  |  |  |  |  |

|---------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|

|                                                   | Core Specifics                                                              |  |  |  |  |  |

| Supported<br>Device Family <sup>(1)</sup>         | UltraScale+™, UltraScale,<br>Zynq®-7000, Virtex®-7, Kintex®-7               |  |  |  |  |  |

| Supported User<br>Interfaces                      | AXI4-Lite, AXI4-Stream, AXI-4                                               |  |  |  |  |  |

| Resources                                         | See Resource Utilization.                                                   |  |  |  |  |  |

|                                                   | Provided with Core                                                          |  |  |  |  |  |

| Design Files                                      | Encrypted HDL                                                               |  |  |  |  |  |

| Example Design                                    | N/A                                                                         |  |  |  |  |  |

| Test Bench                                        | Verilog                                                                     |  |  |  |  |  |

| Constraints File                                  | XDC                                                                         |  |  |  |  |  |

| Simulation<br>Model                               | Encrypted RTL                                                               |  |  |  |  |  |

| Supported<br>S/W Driver <sup>(2)</sup>            | N/A                                                                         |  |  |  |  |  |

|                                                   | Tested Design Flows <sup>(3)</sup>                                          |  |  |  |  |  |

| Design Entry                                      | Vivado® Design Suite<br>Vivado                                              |  |  |  |  |  |

| Simulation                                        | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |  |  |  |  |

| Synthesis                                         | Vivado Synthesis                                                            |  |  |  |  |  |

| Support                                           |                                                                             |  |  |  |  |  |

| Provided by Xilinx at the Xilinx Support web page |                                                                             |  |  |  |  |  |

#### Notes:

- For a complete list of supported devices, see the Vivado IP catalog.

- Standalone driver details can be found in the SDK directory (<install\_directory>/doc/usenglish/xilinx\_drivers.htm). Linux OS and driver support information is available from the Xilinx Wiki page.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

#### Features continued

- SMPTE ST 2022-5 FEC matrix selection per channel

- 1 <= FEC L <= 1020

- 4 <= FEC D <= 255

- SD-SDI stream

- FEC L \* FEC D <= 1500

- HD-SDI stream

- FEC L \* FEC D <= 3000

- 3G-SDI stream

- FEC L \* FEC D <= 6000

- FEC interleaving selection per channel

- Block aligned

- Non block aligned

- FEC operating mode configurable per channel

- Packet bypass (No FEC)

- 1D FEC (Column)

- 2D FEC (Column and Row)

# Overview

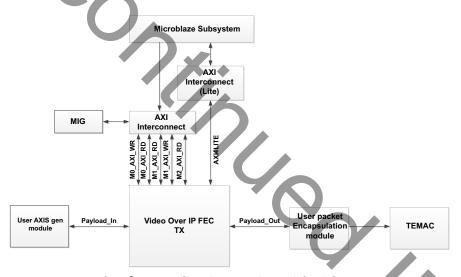

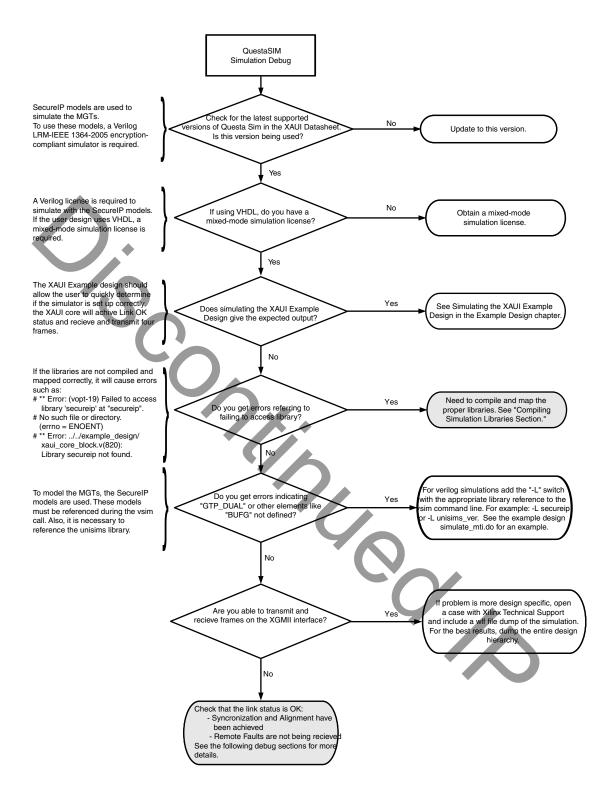

As broadcast and communications markets converge, and the use of IP networks for transport of video streams becomes more attractive to broadcasters and telecommunication companies alike, the adoption of Ethernet for the transmission of multiple compressed media streams is becoming a major customer requirement. The industry is primarily looking at the SMPTE ST 2022 set of standards to create an open and interoperable way of connecting video over Ethernet equipment together and ensuring that Quality of Service (QoS) is high and packet loss is kept to a minimum or recovered through FEC. As shown in Figure 1-1, Video over IP FEC is currently aimed at multiple SMPTE ST 2022-1 streams carried on 1GbE networks and SMPTE ST 2022-5 streams carried on 1GGE networks.

Figure 1-1: Video over IP FEC Usage in Contribution or Distribution Networks

The core includes Forward Error Correction (FEC). FEC protects the transport streams during the transport over IP networks. With FEC, the transmitter adds systematically generated redundant data. This carefully designed redundancy allows the receiver to detect and correct a limited number of packet errors occurring anywhere in the video without the need to ask the transmitter for additional video data. These errors, in the form of lost video packets, can be caused by many reasons, from thermal noise to storage system defects and transmission noise introduced by the environment. FEC gives the receiver the ability to correct these errors without needing a reverse channel to request retransmission of data. In real time systems, the latency is too great to request a retransmission. The ability of Xilinx FPGAs to bridge the broadcast and the communications industries by providing a modular device with highly integrable interfaces helps broadcasters reduce costs as well as reduce the overall time it takes to acquire, edit and produce content. Now that video can be reliably delivered over 1 Gbps or 10 Gbps Ethernet, broadcasters can replace some of the expensive mobile infrastructures supporting outside live broadcasts, as well as enable remote production from existing fixed studio set ups, which dramatically reduces both capital expenditure and operating expenses.

#### **Feature Summary**

The SMPTE ST 2022-1/2 and SMPTE ST 2022-5/6 supported Video over IP FEC Transmitter core generates the Forward Error Correction packets in accordance with SMPTE ST 2022-1 and SMPTE ST 2022-5 for recovery of IP packets lost due to network transmission errors. The core supports up to 8 channel in SMPTE ST 2022-5/6 operating mode and up to 512 channels in SMPTE ST 2022-1/2 operating mode. The core support multiple FEC mode operation depends on input packet type and user preferences. The core has symmetric and well-defined input and output payload interface which following same AXI4-Stream protocol.

# **Applications**

The SMPTE ST 2022-1 or SMPTE ST 2022-5 supported Video over IP FEC Transmitter core is used to transport compressed and uncompressed constant bit rate video streams over an IP network.

#### **Licensing and Ordering Information**

This Xilinx LogiCORE™ IP module is provided under the terms of the Xilinx Core License Agreement. The module is shipped as part of the Vivado® Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your local Xilinx sales representative for information about pricing and availability.

For more information, visit the Video over IP FEC Transmitter v2.0 product web page.

Information about other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

#### **License Checkers**

If the IP requires a license key, the key must be verified. The Vivado® design tools have several license checkpoints for gating licensed IP through the flow. If the license check succeeds, the IP can continue generation. Otherwise, generation halts with error. License checkpoints are enforced by the following tools:

- Vivado Synthesis

- Vivado Implementation

- write\_bitstream (Tcl command)

**IMPORTANT:** IP license level is ignored at checkpoints. The test confirms a valid license exists. It does not check IP license level.

# **Product Specification**

#### **Architecture Overview**

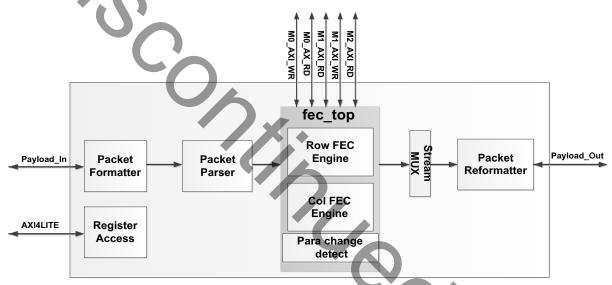

Figure 2-1 shows the Video over IP FEC Transmitter core architecture.

Figure 2-1: Architecture Overview of Video over IP FEC Transmitter

The main functional blocks of the core are:

**Packet Formatter**: Extract packet data and side-band info from AXI4-Stream payload in interface, and store packet data and meta-data in Block RAMs.

**Packet Parser**: Coordinate row and column FEC engine to process incoming RTP packets. At same time, it passes the RTP packets to stream Multiplex to be sent out.

**Row FEC Engine**: Do row FEC calculation and prepare row FEC packets. It store intermediate packet data in DDR.

**Col FEC Engine:** Do column FEC calculation and prepare column FEC packets. It store intermediate packet data in DDR.

**Para Change Detect**: Detects channel parameter change (FEC L, FEC D, Interleave, payload length, FEC mode). When any of these parameter change, the FEC engine stops the current

FEC calculation and completely restarts a new matrix based on new parameters from next RTP packet. Note, parameter change does not cause RTP packet corruption but stops the current matrix calculation. (Note, the RTP packet after parameter change is skipped for FEC calculation).

**Stream MUX**: Multiplex the three packet streams to be sent out: RTP packets, column and row FEC packets.

**Packet Reformatter**: Inverse function of packet formatter. Prepares AXI4-Stream payload out protocol based on packet data and side band info from FEC engine.

**Register Access**: Register configuration and status read-back on the core.

#### **Standards**

The SMPTE ST 2022-1 and SMPTE ST 2022-5 supported Video over IP FEC Transmitter core is compliant with the AXI4, AXI4-Stream, and AXI4-Lite interconnect standards. See the Video IP: AXI Feature Adoption section of the Vivado AXI Reference Guide (UG1037) [Ref 1] for additional information.

#### **Performance**

#### **Maximum Frequencies**

The maximum achievable clock frequency and all resource counts can be affected by other tool options, additional logic in the FPGA device, different versions of Xilinx® tools, and other factors.

#### **Resource Utilization**

For details about resource utilization, visit Performance and Resource Utilization.

Resource Utilization is calculated using  $core\_clk$  and the frequency of other clock fixed at  $s\_axi\_aclk=100$  MHz. The maximum clock frequency results were obtained by double-registering input and output ports to reduce dependence on I/O placement. The inner level of registers used a separate clock signal to measure the path from the input registers to the first output register through the core. The results are post-implementation, using tool default settings except for high effort.

The resource usage results do not include the "characterization" registers and represent the true logic used by the core. LUT counts include SRL16s or SRL32s.

Clock frequency does not take clock jitter into account and should be de rated by an amount appropriate to the clock source jitter specification. The maximum achievable clock frequency and the resource counts might also be affected by other tool options, additional logic in the FPGA, using a different version of Xilinx tools, and other factors.

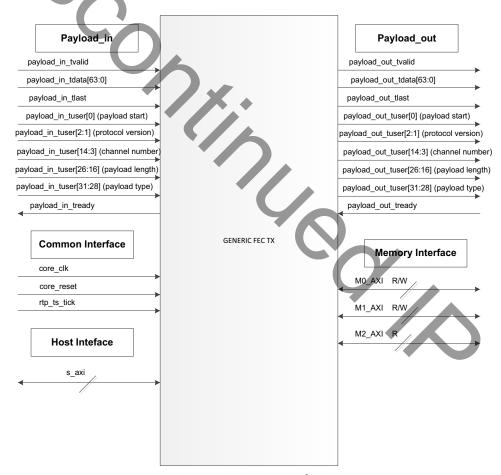

## **Port Descriptions**

The SMPTE ST 2022-1 or SMPTE ST 2022-5 supported Video over IP FEC Transmitter core uses industry-standard control and data interfaces to connect to other system components. The following sections describe the various interfaces available with the core. Figure 2-2 provides an I/O diagram of the core.

Figure 2-2: Core I/Os

#### **Common Interface**

Table 2-1 describes the common interface signals.

**Table 2-1:** Common Interface Signals

| Signal Name | Direction | Width | Description                                                                                                                                                                                |

|-------------|-----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| core_clock  | In        | 1     | Main operating clock for the core. It applies to all the interfaces except the host interface.                                                                                             |

| core_reset  | In        | 1     | Main reset for the core. It applies to payload_in and payload_out interfaces. It is synchronous to core_clock and is Active High.                                                          |

| rtp_ts_tick | In        | 1     | Data Pulse Input which is synced to core_clk to generate ST 2022-1 or ST 2022-5 RTP timestamp. The frequency of the pulse is 90 kHz for ST 2022-1/2 mode and 27 MHz for STm 2022-5/6 mode. |

# Stream Payload In Interface (payload\_in)

Table 2-2 describes the stream payload in interface signals.

Table 2-2: Transmitter Stream Payload In Signals

| Signals           | Direction | Width | Description                                                 |

|-------------------|-----------|-------|-------------------------------------------------------------|

| payload_in_tvalid | In        | 1     | High only from the start to the end of the packet transfer. |

| payload_in_tdata  | In        | 64    | Packet Data                                                 |

| payload_in_tlast  | In        | 1     | High only at the last word of the output packet             |

0//

Table 2-2: Transmitter Stream Payload In Signals (Cont'd)

| Signals           | Direction | Width |          | De                       | scription                      | 1                                                      |  |

|-------------------|-----------|-------|----------|--------------------------|--------------------------------|--------------------------------------------------------|--|

| payload_in_tuser  | In        | 32    | Bit      | Abbreviation Description |                                |                                                        |  |

|                   |           |       | 0        | Packet Start             |                                | nly at the first valid word nput packet.               |  |

|                   |           |       | 2:1      | Protocol<br>Version      | Protoco                        | ol version (set to "00")                               |  |

|                   |           |       | 14:3     | Channel<br>Number        | Shall be                       | e valid at packet start                                |  |

|                   |           |       | 15       | Reserved                 | +                              |                                                        |  |

|                   |           |       | 26:16    | Packet Length            |                                | e valid at packet start. It<br>um of packet length in  |  |

|                   |           |       | 27       | Reserved                 |                                |                                                        |  |

| <b>U</b>          |           |       | 31:28    | Packet Type              | Shall be valid at packet start |                                                        |  |

|                   |           |       |          |                          | Value                          | Description                                            |  |

|                   |           |       |          |                          | 0000                           | UDP encapsulated                                       |  |

|                   |           |       |          |                          | 0001                           | RTP encapsulated<br>ST2022-2 compliant<br>media packet |  |

|                   |           |       |          |                          | 0101                           | RTP encapsulated<br>ST2022-6 compliant<br>media packet |  |

|                   |           |       |          |                          | 1000                           | RTP encapsulated<br>RFC4175 compliant<br>media packet  |  |

|                   |           |       |          | <b>40</b>                | 1001                           | RTP encapsulated<br>RFC3190 compliant<br>media packet  |  |

| payload_in_tready | Out       | 1     | Asserted | l low in between p       | oacket tra                     | insfers.                                               |  |

Note: First packet byte is in bit[7:0] of the first word transfer. Able to accept up to 2KB per packet transfer.

# Stream Payload Out Interface (payload\_out)

Table 2-3 describes the stream payload out interface signals.

Table 2-3: Transmitter Stream Payload Out Signals

| Signals            | Direction | Width | Description                                                 |

|--------------------|-----------|-------|-------------------------------------------------------------|

| payload_out_tvalid | Out       | 1     | High only from the start to the end of the packet transfer. |

| payload_out_tdata  | Out       | 1     | Packet Data                                                 |

| payload_out_tlast  | Out       | 1     | High only at the last word of the output packet             |

Table 2-3: Transmitter Stream Payload Out Signals (Cont'd)

| Signals            | Direction | Width |          |                     | Descrip    | tion                                                       |    |    |    |    |    |  |      |

|--------------------|-----------|-------|----------|---------------------|------------|------------------------------------------------------------|----|----|----|----|----|--|------|

| payload_out_tuser  | Out       | 32    | Bit      | Abbreviation        | Descripti  | on                                                         |    |    |    |    |    |  |      |

|                    |           |       | 0        | Packet Start        | High only  | y at the first valid word of the acket.                    |    |    |    |    |    |  |      |

|                    |           |       | 2:1      | Protocol<br>Version | Protocol   | version (set to "00")                                      |    |    |    |    |    |  |      |

|                    |           |       | 14:3     | Channel<br>Number   | Shall be   | valid at packet start                                      |    |    |    |    |    |  |      |

|                    |           |       | 15       | Reserved            |            |                                                            |    |    |    |    |    |  |      |

|                    | *         |       | 26:16    | Packet Length       |            | valid at packet start. It is the<br>acket length in bytes. |    |    |    |    |    |  |      |

|                    | (0)       |       | 27       | Reserved            |            |                                                            |    |    |    |    |    |  |      |

|                    | 0         |       | 31:28    | Packet Type         | Shall be   | valid at packet start                                      |    |    |    |    |    |  |      |

|                    |           |       | 0        |                     | Values     | Description                                                |    |    |    |    |    |  |      |

|                    |           |       |          |                     | 0000       | UDP encapsulated                                           |    |    |    |    |    |  |      |

|                    |           |       |          | Ó.                  | Ó.         | Ó.                                                         | Ó. | Ó. | Ó. | Ó. | Ó. |  | 0001 |

|                    |           |       |          |                     | 0010       | RTP encapsulated ST2022-1 compliant Column FEC             |    |    |    |    |    |  |      |

|                    |           |       |          |                     | 0011       | RTP encapsulated ST2022-1 compliant Row FEC packet         |    |    |    |    |    |  |      |

|                    |           |       |          | 1                   | 0101       | RTP encapsulated ST2022-6 compliant media packet           |    |    |    |    |    |  |      |

|                    |           |       |          | (                   | 0110       | RTP encapsulated ST2022-5 compliant Column packet          |    |    |    |    |    |  |      |

|                    |           |       |          |                     | 0111       | RTP encapsulated ST2022-5 compliant Row FEC packet         |    |    |    |    |    |  |      |

|                    |           |       |          |                     | 1000       | RTP encapsulated RFC4175 compliant media packet            |    |    |    |    |    |  |      |

|                    |           |       |          |                     | 1001       | RTP encapsulated RFC3190 compliant media packet            |    |    |    |    |    |  |      |

| payload_out_tready | In        | 1     | Asserted | l low in between    | packet tra | nnsfers.                                                   |    |    |    |    |    |  |      |

**Note:** First packet byte is in bit[7:0] of the first word transfer. Able to transfer up to 2KB per packet.

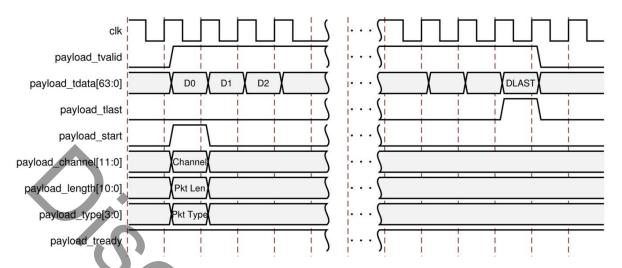

Figure 2-3 shows a waveform diagram of the stream payload protocol.

Figure 2-3: Stream Payload Protocol Waveform

# Host Interface (S\_AXI)

Table 2-4 describes the host interface signals. Refer to AXI Reference Guide (UG1037) [Ref 7] on AXI-Lite interface and its protocol.

Table 2-4: Host Interface Signals

| Signal Name   | Direction | Width | Description                                                                                           |

|---------------|-----------|-------|-------------------------------------------------------------------------------------------------------|

| s_axi_aclk    | In        | 1     | AXI4-Lite clock.                                                                                      |

| s_axi_aresetn | In        | 1     | AXI4-Lite active low reset.                                                                           |

| s_axi_awaddr  | In        | 32    | AXI4-Lite Write Address Bus.                                                                          |

| s_axi_awvalid | In        | 1     | AXI4-Lite Write Address Channel Write Address Valid.                                                  |

| s_axi_wdata   | In        | 32    | AXI4-Lite Write Data Bus.                                                                             |

| s_axi_wstrb   | In        | 4     | AXI4-Lite Write Data Channel Data Byte Strobes.                                                       |

| s_axi_wvalid  | In        | 1     | AXI4-Lite Write Data Channel Write Data Valid.                                                        |

| s_axi_awready | Out       | 1     | AXI4-Lite Write Address Channel Write Address Ready. Indicates DMA ready to accept the write address. |

| s_axi_wready  | Out       | 1     | AXI4-Lite Write Data Channel Write Data Ready.<br>Indicates DMA is ready to accept the write data.    |

| s_axi_bresp   | Out       | 2     | AXI4-Lite Write Response Channel. Indicates results of the write transfer.                            |

| s_axi_bvalid  | Out       | 1     | AXI4-Lite Write Response Channel Response Valid. Indicates response is valid.                         |

| s_axi_bready  | In        | 1     | AXI4-Lite Write Response Channel Ready. Indicates target is ready to receive response.                |

| s_axi_arvalid | In        | 1     | AXI4-Lite Read Address Channel Read Address Valid.                                                    |

Table 2-4: Host Interface Signals (Cont'd)

| Signal Name                          | Direction | Width | Description                                                                                        |  |  |  |

|--------------------------------------|-----------|-------|----------------------------------------------------------------------------------------------------|--|--|--|

| s_axi_arready                        | Out       | 1     | Ready. Indcicates DMA is ready to accept the read address.                                         |  |  |  |

| s_axi_araddr                         | In        | 32    | AXI4-Lite Read Address Bus.                                                                        |  |  |  |

| s_axi_rready                         | In        | 1     | AXI4-Lite Read Data Channel Read Data Ready.<br>Indicates target is ready to accept the read data. |  |  |  |

| s_axi_rdata                          | Out       | 32    | AXI4-Lite Read Data Bus.                                                                           |  |  |  |

| s_axi_rresp                          | Out       | 2     | AXI4-Lite Read Response Channel Response.<br>Indicates results of the read transfer.               |  |  |  |

| s_axi_rvalid                         | Out       | 1     | AXI4-Lite Read Data Channel Read Data Valid.                                                       |  |  |  |

| Table 4. AXI4-Lite Interface Signals |           |       |                                                                                                    |  |  |  |

# Memory Interface (M\*\_AXI\_\*)

See the AXI Reference Guide (UG1037) [Ref 7] for more information on AXI-MM interface and its protocol. The AXI-MM port data width is 256.

Table 2-5: Memory Interface Signals

| Signal Name                                                 | Direction | Width | Description                                  |  |  |  |  |  |

|-------------------------------------------------------------|-----------|-------|----------------------------------------------|--|--|--|--|--|

| M0_AXI_WR: COLUMN FEC DDR Write: Intermediate Result to DDR |           |       |                                              |  |  |  |  |  |

| m0_axi_awlen                                                | Out       | 8     | Write Address Channel Burst Length Code.     |  |  |  |  |  |

| m0_axi_awsize                                               | Out       | 3     | Write Address Channel Transfer Size Code.    |  |  |  |  |  |

| m0_axi_awburst                                              | Out       | 2     | Write Address Channel Burst Type.            |  |  |  |  |  |

| m0_axi_awcache                                              | Out       | 4     | Write Address Channel Cache Characteristics. |  |  |  |  |  |

| m0_axi_awprot                                               | Out       | 3     | Write Address Channel Protection Bits.       |  |  |  |  |  |

| m0_axi_awaddr                                               | Out       | 32    | Write Address Channel Address.               |  |  |  |  |  |

| m0_axi_awvalid                                              | Out       | 1     | Write Address Channel Valid.                 |  |  |  |  |  |

| m0_axi_awready                                              | In        | 1     | Write Address Channel Ready.                 |  |  |  |  |  |

| m0_axi_wdata                                                | Out       | 256   | Write Data Channel Data.                     |  |  |  |  |  |

| m0_axi_wstrb                                                | Out       | 32    | Write Data Channel Data Byte Strobes.        |  |  |  |  |  |

| m0_axi_wlast                                                | Out       | 1     | Write Data Channel Last Data Beat.           |  |  |  |  |  |

| m0_axi_wvalid                                               | Out       | 1     | Write Data Channel Valid.                    |  |  |  |  |  |

| m0_axi_wready                                               | In        | 1     | Write Data Channel Ready.                    |  |  |  |  |  |

| m0_axi_bresp                                                | In        | 2     | Write Response Channel Response Code.        |  |  |  |  |  |

| m0_axi_bvalid                                               | In        | 1     | Write Response Channel Valid.                |  |  |  |  |  |

| m0_axi_bready                                               | Out       | 1     | Write Response Channel Ready.                |  |  |  |  |  |

| m0_axi_awid                                                 | Out       | 1     | Write Address Channel Transaction ID.        |  |  |  |  |  |

Table 2-5: Memory Interface Signals (Cont'd)

| Signal Name                                      | Direction   | Width              | Description                                      |  |  |  |  |

|--------------------------------------------------|-------------|--------------------|--------------------------------------------------|--|--|--|--|

| m0_axi_awlock                                    | Out         | 2                  | Write Data Channel Atomic Access Type.           |  |  |  |  |

| m0_axi_awqos                                     | Out         | 4                  | Write Data Channel Quality of Service.           |  |  |  |  |

| m0_axi_bid                                       | In          | 1                  | Write Response Channel Transaction ID.           |  |  |  |  |

| M0_AXI_RD: COLUMN FEC DDR Read: preload from DDR |             |                    |                                                  |  |  |  |  |

| m0_axi_arlen                                     | Out         | 8                  | Read Address Channel Burst Length code.          |  |  |  |  |

| m0_axi_arsize                                    | Out         | 3                  | Read Address Channel Transfer Size code.         |  |  |  |  |

| m0_axi_arburst                                   | Out         | 2                  | Read Address Channel Burst Type.                 |  |  |  |  |

| m0_axi_arcache                                   | Out         | 4                  | Read Address Channel Cache Characteristics.      |  |  |  |  |

| m0_axi_arprot                                    | Out         | 3                  | Read Address Channel Protection Bits.            |  |  |  |  |

| m0_axi_araddr                                    | Out         | 32                 | Read Address Channel Address.                    |  |  |  |  |

| m0_axi_arvalid                                   | Out         | 1                  | Read Address Channel Valid.                      |  |  |  |  |

| m0_axi_arready                                   | In          | 1                  | Read Address Channel Ready.                      |  |  |  |  |

| m0_axi_rready                                    | Out         | 1                  | Read Data Channel Ready.                         |  |  |  |  |

| m0_axi_rdata                                     | In          | 256                | Read Data Channel Data.                          |  |  |  |  |

| m0_axi_rlast                                     | In          | 1 1                | Read Data Channel Last Data Beat.                |  |  |  |  |

| m0_axi_rvalid                                    | In          | 1                  | Read Data Channel Valid.                         |  |  |  |  |

| m0_axi_rresp                                     | In          | 2                  | Read Data Channel Response Code.                 |  |  |  |  |

| m0_axi_arid                                      | Out         | 1                  | Read Address Channel Transaction ID.             |  |  |  |  |

| m0_axi_arlock                                    | Out         | 2                  | Read Address Channel Atomic Access Type.         |  |  |  |  |

| m0_axi_arqos                                     | Out         | 4                  | Read Address Channel Channel Quality of Service. |  |  |  |  |

| m0_axi_rid                                       | In          | 1                  | Read Data Channel Transaction ID.                |  |  |  |  |

| M1_AXI_RD: COLUMN FEC I                          | DDR Read: r | esult FEC packet 1 | from DDR                                         |  |  |  |  |

| m1_axi_arlen                                     | Out         | 8                  | Read Address Channel Burst Length code.          |  |  |  |  |

| m1_axi_arsize                                    | Out         | 3                  | Read Address Channel Transfer Size code.         |  |  |  |  |

| m1_axi_arburst                                   | Out         | 2                  | Read Address Channel Burst Type.                 |  |  |  |  |

| m1_axi_arcache                                   | Out         | 4                  | Read Address Channel Cache Characteristics.      |  |  |  |  |

| m1_axi_arprot                                    | Out         | 3                  | Read Address Channel Protection Bits.            |  |  |  |  |

| m1_axi_araddr                                    | Out         | 32                 | Read Address Channel Address.                    |  |  |  |  |

| m1_axi_arvalid                                   | Out         | 1                  | Read Address Channel Valid.                      |  |  |  |  |

| m1_axi_arready                                   | In          | 1                  | Read Address Channel Ready.                      |  |  |  |  |

| m1_axi_rready                                    | Out         | 1                  | Read Data Channel Ready.                         |  |  |  |  |

| m1_axi_rdata                                     | In          | 256                | Read Data Channel Data.                          |  |  |  |  |

| m1_axi_rlast                                     | In          | 1                  | Read Data Channel Last Data Beat.                |  |  |  |  |

Table 2-5: Memory Interface Signals (Cont'd)

| Signal Name            | Direction   | Width              | Description                                      |

|------------------------|-------------|--------------------|--------------------------------------------------|

| m1_axi_rvalid          | In          | 1                  | Read Data Channel Valid.                         |

| m1_axi_rresp           | In          | 2                  | Read Data Channel Response Code.                 |

| m1_axi_arid            | Out         | 1                  | Read Address Channel Transaction ID.             |

| m1_axi_arlock          | Out         | 2                  | Read Address Channel Atomic Access Type.         |

| m1_axi_arqos           | Out         | 4                  | Read Address Channel Channel Quality of Service. |

| m1_axi_rid             | In          | 1                  | Read Data Channel Transaction ID.                |

| M1_AXI_WR: ROW FEC DDF | Write: inte | rmediate result to | DDR                                              |

| m1_axi_awlen           | Out         | 8                  | Write Address Channel Burst Length Code.         |

| m1_axi_awsize          | Out         | 3                  | Write Address Channel Transfer Size Code.        |

| m1_axi_awburst         | Out         | 2                  | Write Address Channel Burst Type.                |

| m1_axi_awcache         | Out         | 4                  | Write Address Channel Cache Characteristics.     |

| m1_axi_awprot          | Out         | 3                  | Write Address Channel Protection Bits.           |

| m1_axi_awaddr          | Out         | 32                 | Write Address Channel Address.                   |

| m1_axi_awvalid         | Out         | 1                  | Write Address Channel Valid.                     |

| m1_axi_awready         | In          | 1                  | Write Address Channel Ready.                     |

| m1_axi_wdata           | Out         | 256                | Write Data Channel Data.                         |

| m1_axi_wstrb           | Out         | 32                 | Write Data Channel Data Byte Strobes.            |

| m1_axi_wlast           | Out         | 1                  | Write Data Channel Last Data Beat.               |

| m1_axi_wvalid          | Out         | 1                  | Write Data Channel Valid.                        |

| m1_axi_wready          | In          | 1                  | Write Data Channel Ready.                        |

| m1_axi_bresp           | In          | 2                  | Write Response Channel Response Code.            |

| m1_axi_bvalid          | In          | 1                  | Write Response Channel Valid.                    |

| m1_axi_bready          | Out         | 1                  | Write Response Channel Ready.                    |

| m1_axi_awid            | Out         | 1                  | Write Address Channel Transaction ID.            |

| m1_axi_awlock          | Out         | 2                  | Write Data Channel Atomic Access Type.           |

| m1_axi_awqos           | Out         | 4                  | Write Data Channel Quality of Service.           |

| m1_axi_bid             | In          | 1                  | Write Response Channel Transaction ID.           |

| M2_AXI_RD: ROW FEC DDR | Read: prelo | ad from DDR        |                                                  |

| m2_axi_arlen           | Out         | 8                  | Read Address Channel Burst Length code.          |

| m2_axi_arsize          | Out         | 3                  | Read Address Channel Transfer Size code.         |

| m2_axi_arburst         | Out         | 2                  | Read Address Channel Burst Type.                 |

| m2_axi_arcache         | Out         | 4                  | Read Address Channel Cache Characteristics.      |

| m2_axi_arprot          | Out         | 3                  | Read Address Channel Protection Bits.            |

Table 2-5: Memory Interface Signals (Cont'd)

| Signal Name    | Direction | Width | Description                                      |

|----------------|-----------|-------|--------------------------------------------------|

| m2_axi_araddr  | Out       | 32    | Read Address Channel Address.                    |

| m2_axi_arvalid | Out       | 1     | Read Address Channel Valid.                      |

| m2_axi_arready | In        | 1     | Read Address Channel Ready.                      |

| m2_axi_rready  | Out       | 1     | Read Data Channel Ready.                         |

| m2_axi_rdata   | In        | 256   | Read Data Channel Data.                          |

| m2_axi_rlast   | In        | 1     | Read Data Channel Last Data Beat.                |

| m2_axi_rvalid  | In        | 1     | Read Data Channel Valid.                         |

| m2_axi_rresp   | In        | 2     | Read Data Channel Response Code.                 |

| m2_axi_arid    | Out       | 1     | Read Address Channel Transaction ID.             |

| m2_axi_arlock  | Out       | 2     | Read Address Channel Atomic Access Type.         |

| m2_axi_arqos   | Out       | 4     | Read Address Channel Channel Quality of Service. |

| m2_axi_rid     | In        | 1     | Read Data Channel Transaction ID.                |

Note: The ROW FEC result is not written into DDR and is different from COL FEC result.

# **Register Space**

The Video over IP FEC Transmitter register space is partitioned to general and channel-specific registers.

Table 2-6: Host Interface (S\_AXI [AXI4-Lite]) Register Map

| Address         |                | Cleared Access with Default Value |               |            | De          | escrip         | tion                                                        |

|-----------------|----------------|-----------------------------------|---------------|------------|-------------|----------------|-------------------------------------------------------------|

| Offset<br>(HEX) | Register Name  | Type                              | SOFT<br>reset | (HEX)      | Bit Range   |                | Value                                                       |

|                 | <b>/</b>       |                                   | G             | eneral     |             |                |                                                             |

| 0x0000          | control        | R/W                               | N             | 0x00000000 | Control     |                |                                                             |

|                 | 0              |                                   |               |            | 31:2        | Rese           | rved                                                        |

|                 |                |                                   |               |            | 1           | Chan           | inel Update                                                 |

|                 |                |                                   | )×            | •          |             | allow<br>regis | pulse to<br>configured<br>ters to take<br>t for the<br>nel. |

|                 |                |                                   |               | 4          | 0           | Soft           | reset                                                       |

|                 |                |                                   |               |            |             | 1              | Reset all<br>VoIP FEC<br>Transmitter<br>Registers           |

|                 |                |                                   |               | 40         | <b>7</b> /  | 0              | Un-Reset all<br>VoIP FEC<br>Transmitter<br>Registers        |

| 0x0004          | status         | R                                 | N             | 0x00000000 | Status      |                |                                                             |

|                 |                |                                   |               |            | 31:1        |                | Reserved                                                    |

|                 |                |                                   |               |            |             | 0              | Upda                                                        |

|                 |                |                                   |               |            | Ť           | 1              | Updating configured parameters to the core                  |

|                 |                |                                   |               |            |             | 0              | No updating                                                 |

| 0x0008          | channel_access | R/W                               | Υ             | 0x00000000 | Channel Acc | ess            |                                                             |

|                 |                |                                   |               |            | 31:12       | Rese           | rved                                                        |

|                 |                |                                   |               |            | 11:0        |                | channel<br>ber to access<br>ters                            |

Table 2-6: Host Interface (S\_AXI [AXI4-Lite]) Register Map (Cont'd)

| Address         |                  |                | Cleared               | - 6 1.1.1              | De                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | escrip        | tion                                              |                                                                          |           |                 |  |       |       |              |

|-----------------|------------------|----------------|-----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------|--------------------------------------------------------------------------|-----------|-----------------|--|-------|-------|--------------|

| Offset<br>(HEX) | Register Name    | Access<br>Type | with<br>SOFT<br>reset | Default Value<br>(HEX) | Bit Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               | Value                                             |                                                                          |           |                 |  |       |       |              |

| 0x000C          | sys_config       | R              | N                     | 0x00000000             | System Conf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | figurat       | tion                                              |                                                                          |           |                 |  |       |       |              |

|                 |                  |                |                       |                        | 31:26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Rese          | rved                                              |                                                                          |           |                 |  |       |       |              |

|                 |                  |                |                       |                        | 25:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Supp          | mum<br>oorted FEC L<br>umn FEC)                   |                                                                          |           |                 |  |       |       |              |

|                 |                  |                |                       |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20            | Maximum<br>FEC L for<br>ST2022-1/2                |                                                                          |           |                 |  |       |       |              |

|                 | 10               |                |                       |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 102<br>0      | Maximum<br>FEC L for<br>ST2022-5/6                |                                                                          |           |                 |  |       |       |              |

|                 |                  |                |                       |                        | 15:12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Rese          | rved                                              |                                                                          |           |                 |  |       |       |              |

|                 |                  |                |                       |                        | 11:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Maxi<br>Char  | ber of<br>mum<br>inels<br>ported                  |                                                                          |           |                 |  |       |       |              |

|                 |                  |                | R N 0x02              | 0x02000000             | Hardware Version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |                                                   |                                                                          |           |                 |  |       |       |              |

| 0x0010          | version          | R              |                       |                        | 31:24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Version major |                                                   |                                                                          |           |                 |  |       |       |              |

|                 |                  |                |                       |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               | 23:16                                             | Versi                                                                    | ion minor |                 |  |       |       |              |