# Video Timing Controller v6.1

# LogiCORE IP Product Guide

PG016 May 22, 2019

# **Table of Contents**

## **IP Facts**

# **Chapter 1: Overview**

| Feature Summary        | 7 |

|------------------------|---|

| Applications           | 7 |

| Licensing and Ordering | 8 |

# **Chapter 2: Product Specification**

| Standards                          | . 9 |

|------------------------------------|-----|

| Performance                        | . 9 |

| Resource Utilization               | 10  |

| Core Interfaces and Register Space | 10  |

# **Chapter 3: Designing with the Core**

| Basic Architecture         | 39 |

|----------------------------|----|

| Control Signals and Timing | 40 |

| Use Model                  | 53 |

| Clocking                   | 56 |

| Resets                     | 57 |

| Protocol Description       | 58 |

# Chapter 4: Customizing and Generating the Core

| Vivado Integrated Design Environment (IDE) | 59 |

|--------------------------------------------|----|

| Graphical User Interface                   | 60 |

| Output Generation                          | 71 |

# **Chapter 5: Constraining the Core**

| equired Constraints | /3 |

|---------------------|----|

|                     | -  |

| Chapter 6: Simulation                                      |

|------------------------------------------------------------|

| Chapter 7: Synthesis and Implementation                    |

| Chapter 8: Detailed Example Design                         |

| Chapter 9: Test Bench Demonstration Test Bench             |

| Appendix A: Verification, Compliance, and Interoperability |

| Simulation                                                 |

| Hardware Testing                                           |

| Appendix B: Upgrading                                      |

| Migrating to the Vivado Design Suite       81              |

| Upgrading in Vivado Design Suite                           |

| Appendix C: Debugging                                      |

| Finding Help on Xilinx.com    83                           |

| Debug Tools                                                |

| Hardware Debug                                             |

| Interface Debug                                            |

| Appendix D: Additional Resources                           |

| Xilinx Resources                                           |

| Documentation Navigator and Design Hubs         88         |

| References                                                 |

| Revision History                                           |

| Please Read: Important Legal Notices       90              |

|                                                            |

|                                                            |

|                                                            |

# **IP Facts**

#

# Introduction

The Xilinx® LogiCORE<sup>™</sup> IP Video Timing Controller core is a general purpose video timing generator and detector. The core is highly programmable through a comprehensive register set allowing control of various timing generation parameters. This programmability is coupled with a comprehensive set of interrupt bits which provides easy integration into a processor system for in-system control of the block in real-time. The Video Timing Controller is provided with an optional AXI4-Lite compliant interface.

# Features

- Support for progressive or interlaced video frame sizes up to 8192 x 8192

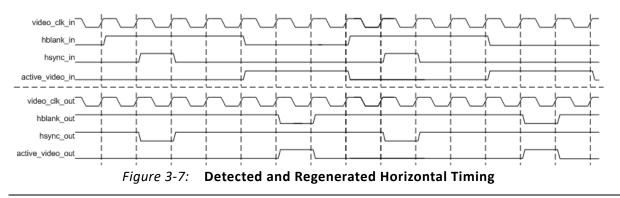

- Direct regeneration of output timing signals with independent timing and polarity inversion

- Automatic detection and generation of horizontal and vertical video timing signals

- Support for multiple combinations of blanking or synchronization signals

- Automatic detection of input video control signal polarities

- Support for detection and generation of horizontal delay of vertical blank/sync

- Programmable output video signal polarities

- Generation of up to 16 additional independent output frame synchronization signals

- Optional AXI4-Lite processor interface

- High number of interrupts and status registers for easy system control and integration

| LogiCORE IP Facts Table                                                                        |  |  |  |

|------------------------------------------------------------------------------------------------|--|--|--|

| Core Specifics                                                                                 |  |  |  |

| UltraScale+™ Families,<br>UltraScale™ Architecture, Zynq <sup>®</sup> -7000,<br>7 Series FPGAs |  |  |  |

| AXI4-Lite <sup>(2)</sup>                                                                       |  |  |  |

| See Resource Utilization.                                                                      |  |  |  |

| Provided with Core                                                                             |  |  |  |

| Product Guide                                                                                  |  |  |  |

| Encrypted RTL                                                                                  |  |  |  |

| Not Provided                                                                                   |  |  |  |

| Verilog                                                                                        |  |  |  |

| XDC                                                                                            |  |  |  |

| Encrypted RTL, VHDL or Verilog Structural                                                      |  |  |  |

| Standalone                                                                                     |  |  |  |

| Tested Design Flows <sup>(4)</sup>                                                             |  |  |  |

|                                                                                                |  |  |  |

| Design Entry<br>Tools           | Vivado <sup>®</sup> Design Suite                                               |  |  |

|---------------------------------|--------------------------------------------------------------------------------|--|--|

| Simulation                      | For supported simulators, see the Xilinx Design<br>Tools: Release Notes Guide. |  |  |

| Synthesis Tools                 | Vivado Synthesis                                                               |  |  |

| Support                         |                                                                                |  |  |

| Provided by Xilinx at the, Inc. |                                                                                |  |  |

- 1. For a complete listing of supported devices, see the Vivado IP Catalog.

- 2. Refer to the *Video IP: AXI Feature Adoption* section of AXI Reference Guide [Ref 1].

- Standalone driver details can be found in the SDK directory (<install\_directory>/SDK/<release>/data/embeddedsw/doc/ xilinx\_drivers.htm). Linux OS and driver support information is available from the Xilinx Wiki page.

- 4. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Chapter 1

# Overview

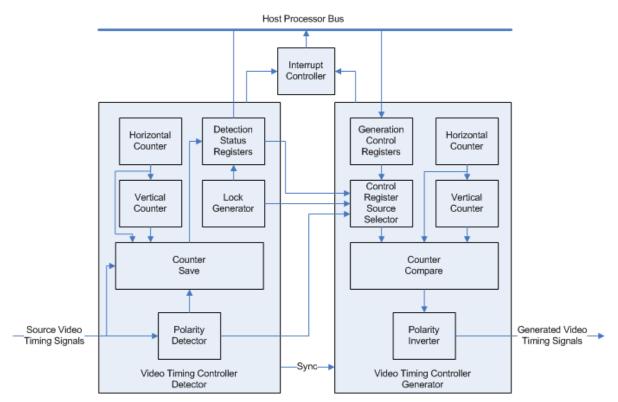

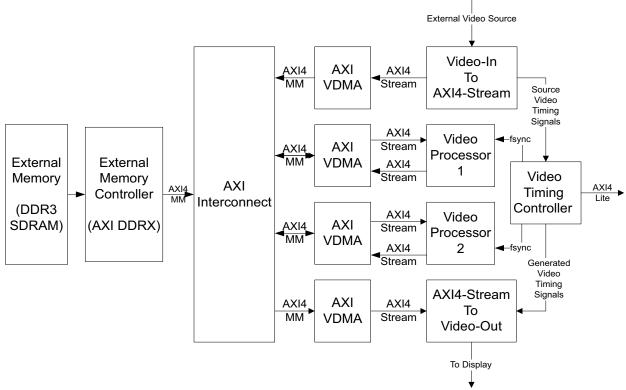

All video systems require management of video timing signals, which are used to synchronize processes. The Video Timing Controller serves the function of both detecting and generating these timing signals.

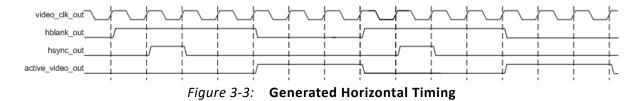

The input side of this core automatically detects horizontal and vertical synchronization pulses, polarity, blanking timing and active video pixels. While on the output, it generates the horizontal and vertical blanking and synchronization pulses used with a standard video system including support for programmable pulse polarity. The core is commonly used with the Video in to AXI4-Stream core to detect the format and timing of incoming video data or with the AXI4-Stream to Video out core to generate outgoing video timing for downstream sinks such as a video monitor.

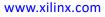

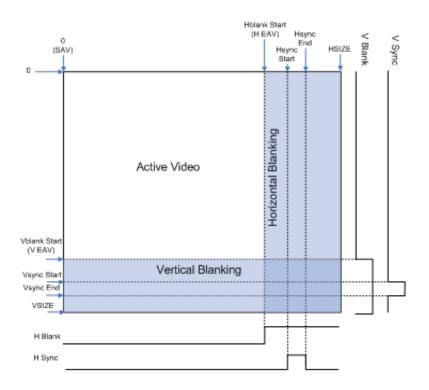

Figure 1-1 shows a typical video frame including timing signals.

**IMPORTANT:** All signals are shown with active-High polarity.

Figure 1-1: Example Video Frame and Timing Signals

A video frame can be completely described in terms of timing by only a few definitions. A video frame comprises active video and blanking periods. The vertical and horizontal synchronization signals describe the video frame timing, which includes active and blanking data. In addition, the frame synchronization signals can be used to synchronize video data from one component to another within a video system. There are additional signals that can also be used to control the video system, such as a signal to differentiate valid chroma samples.

Video systems may utilize different combinations of blank, synchronization or active signals with various polarities to synchronize processing and control video data. The Video Timing Controller simplifies working with video timing signals by providing a highly programmable and flexible core that allows detection and generation of the various timing signals within a video system.

www.xilinx.com

# **Feature Summary**

The Video Timing Controller core supports the AXI4-Lite interface and a constant-mode interface. The AXI4-Lite interface allows the core to be easily incorporated into a Vivado project. The Constant interface utilizes core parameters configurable by the Graphical User Interface (GUI) to setup the core for fixed-mode operation. These configurable options allow the Video Timing Controller core to be easily integrated with AXI4 based processor systems, with non-AXI4-compliant processors systems with some additional logic, and in systems without a processor.

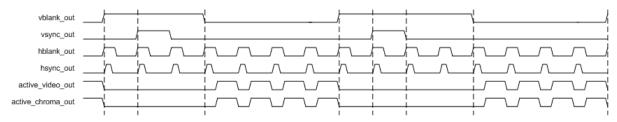

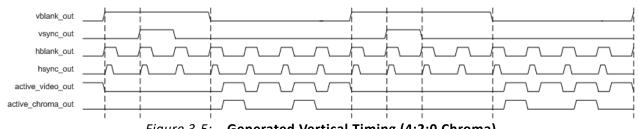

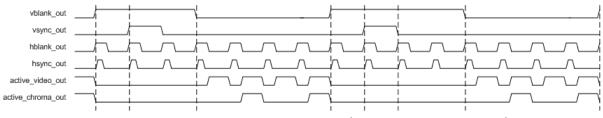

The Video Timing Controller core supports detecting video frame sizes up to 8192 clocks by 8192 lines (including horizontal and vertical blanking). The detection typically requires three to five input video frames to detect and lock. The Video Timing Controller core automatically detects the timing involved with horizontal/vertical blanks and syncs. The timing of the active\_video and the active\_chroma signals are also detected. This allows the user to easily determine the video frame size via the core register (AXI4-Lite) interface. The minimum set of signals used for detection is either vertical blank, horizontal blank and active video or vertical sync, horizontal sync and active video. The polarities of each input signal is also detected and reported via the register interface to allow easy use of each signal once the polarity is known.

The core also supports generating and regenerating (matching the detected input) video frame sizes up to 8192 clocks by 8192 lines (including blanking time). The output can be the same format or a different format as the detected input. This allows detecting one format and generating a different format. The output can also be synchronized to the detected input and has separate signal polarity settings as well. This allows regenerating the input with different signal polarities or with slight timing adjustments (such as delayed or shorted active video).

The Video Timing Controller core supports up to 16 frame sync output signals. These are toggled high for one clock cycle during each frame. These frame syncs allow triggering timing critical hardware processes at different times during a frame.

# **Applications**

- Video Surveillance

- Industrial Imaging

- Video Conferencing

- Machine Vision

- Video Systems requiring timing detection or timing generation

# **Licensing and Ordering**

This Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP module is provided at no cost under the terms of the Xilinx Core License Agreement. The module is shipped as part of the Vivado<sup>®</sup> Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your local Xilinx sales representative for information about pricing and availability.

For more information, visit the Video Timing Controller product web page.

Information about other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# Chapter 2

# **Product Specification**

# Standards

The Video Timing Controller core is compliant with the AXI4-Lite interconnect standards. Refer to the *Video IP: AXI Feature Adoption* section of the *Vivado AXI Reference Guide* (UG1037) [Ref 1] for additional information.

# Performance

The following sections detail the performance characteristics of the Video Timing Controller core.

# **Maximum Frequencies**

This section contains typical clock frequencies for the target devices. The maximum achievable clock frequency can vary. The maximum achievable clock frequency and all resource counts can be affected by other tool options, additional logic in the FPGA device, using a different version of Xilinx tools and other factors.

- Virtex ® -7, Kintex ® -7, Zynq ® -7000 (XC7Z030, XC7Z045) Devices: 225 MHz

- Artix ® -7, Zynq-7000 (XC7Z010, XC7Z020) Devices: 150 MHz

- Kintex UltraScale<sup>™</sup>, Kintex UltraScale+<sup>™</sup> (XKU035, XCKU15P) Devices: 400 MHz.

# Latency

The Video Timing Controller core does not read or generate data, and therefore, does not have a specific data latency.

The Video Timing Controller core monitors and generates control signals. The output control signals can be configured to be the same as the input with no latency, or the output signals can be configured to incur a multi-clock or multi-line delay.

# Throughput

The Video Timing Controller core does not read or generate data, and does not have a specific throughput.

# **Resource Utilization**

For details about resource utilization, visit Performance and Resource Utilization.

# **Core Interfaces and Register Space**

This chapter provides detailed descriptions for each interface. In addition, detailed information about configuration and control registers is included.

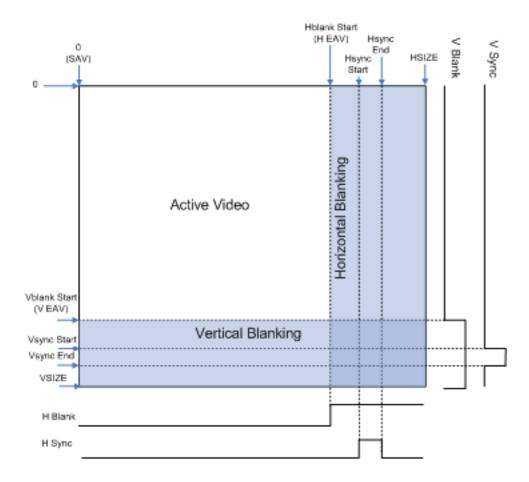

# **Port Descriptions**

The Video Timing Controller (VTC) core uses the AXI4-Lite industry standard control interface to connect to other system components. The following sections describe the various interfaces available with the core. Some signals are optional and not present for all configurations of the core. The AXI4-Lite interface and the IRQ pin are present only when the core is configured via the GUI with an AXI4-Lite control interface. The INTC\_IF interface is present only when the core is configured via the GUI with the GUI with the INTC interface enabled. Figure 2-1 illustrates an I/O diagram of the VTC core.

Figure 2-1: TC Core Top-Level Signaling Interface

## **Core Interfaces**

### **Control Interface**

Video systems commonly use an integrated processor system to dynamically control the parameters within the system. This is especially important when several independent image processing cores are integrated into a single FPGA. The Video Timing Controller core can be configured with an AXI4-Lite interface.

## Common I/O Signals

The signals not included in the AXI4-Lite interface are specified in Table 2-1.

| Name        | Direction | Width      | Description                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk         | In        | 1          | Video Core Clock                                                                                                                                                                                                                                                                                                                                              |

| clken       | In        | 1          | Video Core active-High Clock Enable                                                                                                                                                                                                                                                                                                                           |

| det_clken   | In        | 1          | Video Timing Detection Core active-High Clock Enable                                                                                                                                                                                                                                                                                                          |

| gen_clken   | In        | 1          | Video Timing Generator Core active-High Clock Enable                                                                                                                                                                                                                                                                                                          |

| resetn      | In        | 1          | Video Core active-Low Synchronous Reset                                                                                                                                                                                                                                                                                                                       |

| irq         | Output    | 1          | Interrupt request output, active-High edge                                                                                                                                                                                                                                                                                                                    |

| intc_if     | Output    | 32         | OPTIONAL EXTERNAL INTERRUPT CONTROLLER INTERFACE<br>Available when the "Include INTC Interface" or C_HAS_INTC_IF has<br>been selected.<br>Bits [31:8] are the same as the bits [31:8] in the status register<br>(0x0004).<br>Bits [5:0] are the same as bits [21:16] of the error register (0x0008).<br>Bits [7:6] are reserved and are always 0.             |

|             | De        | tector Int | erface (Video Timing Input Interface)                                                                                                                                                                                                                                                                                                                         |

| field_id_in | Input     | 1          | INPUT FIELD ID<br>Used to set the field_id polarity in the Detector Polarity Register<br>(Address Offset 0x002C).<br>Optional. Only valid when interlace support and field id are enabled.                                                                                                                                                                    |

| hsync_in    | Input     | 1          | INPUT HORIZONTAL SYNCHRONIZATION<br>Used to set the DETECTOR HSYNC register.<br>Polarity is auto-detected.<br>Optional. Either horizontal blank or horizontal synchronization<br>signal inputs must be present. Both do not have to be present.<br>If the hsync_in input is not connected, then the "Horizontal Sync<br>Detection" option must be deselected. |

| hblank_in   | Input     | 1          | INPUT HORIZONTAL BLANK<br>Used to set the DETECTOR HSIZE register.<br>Polarity is auto-detected.<br>Optional. Either horizontal blank or horizontal synchronization<br>signal inputs must be present. Both do not have to be present.<br>If the hblank_in input is not connected, then the "Horizontal Blank<br>Detection" option must be deselected.         |

Table 2-1:

Common Port Descriptions

### Table 2-1: Common Port Descriptions (Cont'd)

| Name             | Direction | Width      | Description                                                                                                                                                                                                                                                                                                                                                             |

|------------------|-----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vsync_in         | Input     | 1          | INPUT VERTICAL SYNCHRONIZATION<br>Used to set the DETECTOR F0_VSYNC_V and the F0_VSYNC_H<br>registers.<br>Polarity is auto-detected.<br>Optional. One of the following inputs must be present: active video,<br>vertical blank or vertical synchronization.<br>If the vsync_in input is not connected, then the "Vertical Sync<br>Detection" option must be deselected. |

| vblank_in        | Input     | 1          | INPUT VERTICAL BLANK<br>Used to set the DETECTOR_VSIZE and the F0_VBLANK_H registers.<br>Polarity is auto-detected.<br>Optional. One of the following inputs must be present: active video,<br>vertical blank or vertical synchronization.<br>If the vblank_in input is not connected, then the "Vertical Blank<br>Detection" option must be deselected.                |

| active_video_in  | Input     | 1          | INPUT ACTIVE VIDEO<br>Used to set the DETECTOR ACTIVE_SIZE register.<br>Polarity is auto-detected.<br>Optional. One of the following inputs must be present: active video,<br>vertical blank or vertical synchronization.<br>If the active_video_in input is not connected, then the "Active Video<br>Detection" option must be deselected.                             |

| active_chroma_in | Input     | 1          | INPUT ACTIVE CHROMA<br>Used to set the VIDEO_FORMAT and the CHROMA_PARITY bits in the<br>Detector Encoding Register.<br>Polarity is auto-detected.<br>Optional.<br>If the active_chroma_in input is not connected, then the "Active<br>Chroma Detection" option must be deselected.                                                                                     |

|                  | Gen       | erator Int | erface (Video Timing Output Interface)                                                                                                                                                                                                                                                                                                                                  |

| field_id_out     | Output    | 1          | OUTPUT FIELD ID<br>Generated field id signal. Polarity configured by the Generator<br>Polarity Register (Address Offset 0x006C)<br>Optional. Only enabled when interlaced support and field id<br>generation is enabled.                                                                                                                                                |

| hsync_out        | Output    | 1          | OUTPUT HORIZONTAL SYNCHRONIZATION<br>Generated horizontal synchronization signal. Polarity configured by<br>the control register. Asserted active during the cycle set by the<br>HSYNC_START bits and deasserted during the cycle set by the<br>HSYNC_END bits in the GENERATOR HSYNC register.                                                                         |

| hblank_out       | Output    | 1          | OUTPUT HORIZONTAL BLANK<br>Generated horizontal blank signal. Polarity configured by the control<br>register. Asserted active during the cycle set by ACTIVE_HSIZE and<br>deasserted during the cycle set by the FRAME_HSIZE bits in the<br>GENERATOR HSIZE register.                                                                                                   |

| Table 2-1: | Common Port Descriptions (Cont'd) |

|------------|-----------------------------------|

|------------|-----------------------------------|

| Name              | Direction | Width                     | Description                                                                                                                                                                                                                                                                                                                           |

|-------------------|-----------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vsync_out         | Output    | 1                         | OUTPUT VERTICAL SYNCHRONIZATION<br>Generated vertical synchronization signal. Polarity configured by the<br>control register. Asserted active during the line set by the<br>F#_VSYNC_VSTART bits and deasserted during the line set by the<br>F#_VSYNC_VEND bits in the GENERATOR F#_VSYNC_V registers.                               |

| vblank_out        | Output    | 1                         | OUTPUT VERTICAL BLANK<br>Generated vertical blank signal. Polarity configured by the control<br>register. Asserted active during the line set by the ACTIVE_VSIZE bits<br>and deasserted during the line set by the GENERATOR VSIZE<br>register.                                                                                      |

| active_video_out  | Output    | 1                         | OUTPUT ACTIVE VIDEO<br>Generated active video signal. Polarity configured by the control<br>register. Active for non blanking lines. Asserted active during the<br>first cycle of the field/frame and deasserted during the cycle set by<br>the GENERATOR ACTIVE_SIZE register                                                        |

| active_chroma_out | Output    | 1                         | OUTPUT ACTIVE CHROMA<br>Generated active chroma signal. Denotes which lines contain valid<br>chroma samples (used for YUV 4:2:0). Polarity configured by the<br>GENERATOR POLARITY register. Active for non-blanking lines<br>configured y the VIDEO_FORMAT and the CHROMA_PARITY bits in<br>the GENERATOR Encoding Register.         |

|                   |           | Fran                      | ne Synchronization Interface                                                                                                                                                                                                                                                                                                          |

| fsync_out         | Output    | [Frame<br>Syncs -<br>1:0] | FRAME SYNCHRONIZATION OUTPUT<br>Each Frame Synchronization bit toggles for only one clock cycle<br>during each frame. The number of bits is configured with the Frame<br>Syncs GUI parameter.<br>Each bit is independently configured for horizontal and vertical<br>clock cycle position with the Frame Sync 0-15 Config registers). |

| fsync_in          | Input     | 1                         | FRAME SYNCHRONIZATION INPUT<br>This is a one clock cycle pulse (active-High) input. The video timing<br>generator will be synchronized to the input if used.                                                                                                                                                                          |

#### Notes:

1. All ports are little-endian.

The clk, clken and resetn, det\_clken, and gen\_clken signals are shared between the core and the Video Timing interfaces. The AXI4-Lite control interface has its own set of clock, clock enable and reset pins: S\_AXI\_ACLK, S\_AXI\_ACLKEN and S\_AXI\_ARESETn.

## The clk Pin

The Video Timing interfaces must be synchronous to the core clock signal clk. All Video Timing interface input signals are sampled on the rising edge of clk. All Video Timing output signal changes occur after the rising edge of clk. If the clk signal is not running, the AXI4-Lite interface asserts the slave error response (0x2) for all addresses. The clken pin is an active-high, synchronous clock-enable input pertaining to Video Timing interfaces.

Setting clken low (de-asserted) halts the operation of the core despite rising edges on the clk pin. Internal states are maintained, and output signal levels are held until clken is asserted again. When clken is de-asserted, core inputs are not sampled, except resetn, which supersedes clken. This clock must be running for AXI4-Lite registers to be read and/ or written, since all core registers reside within the core clock domain. This clock enable must be asserted high for AXI4-Lite registers to be read and/or written, since all core registers reside within the clock enable is deasserted, the AXI4-Lite interface asserts the slave error response (0x2) for all addresses.

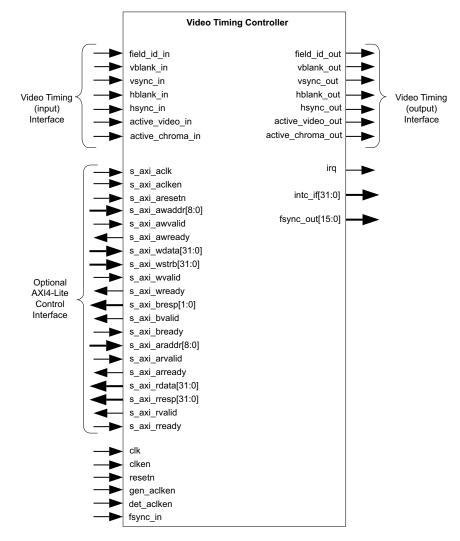

# The det\_clken Pin

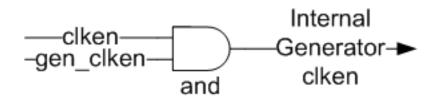

The det\_clken pin is an active-High, synchronous clock-enable pertaining to the Video Timing Controller detector (input) interface. This clock enable allows halting the detector independently from the generator. The internal detector clock enable is a logical "AND" between the clken and det\_clken inputs. The internal logic that controls the detector sub-core clock enable is shown in Figure 2-2.

Figure 2-2: Detector Internal Clock Enable Logic

### The gen\_clken Pin

The gen\_clken pin is an active-High, synchronous clock-enable pertaining to the Video Timing Controller generator (output) interface. This clock enable allows halting the generator independently from the detector. The internal generator clock enable is a logical "AND" between the clken and get\_clken inputs. For example, to enable the detector while halting the generator, drive clken to '1', det\_clken to '1' and gen\_clken to '0'. The internal logic that controls the generator sub-core clock enable is shown in Figure 2-3.

www.xilinx.com

Figure 2-3: Generator Internal Clock Enable Logic

# The resetn Pin

The resetn pin is an active-Low, synchronous reset input pertaining to only Video Timing interfaces. resetn supersedes clken, and when set to 0, the core resets at the next rising edge of clk even if clken is de-asserted. The resetn signal must be synchronous to the clk and must be held low for a minimum of 32 clock cycles of the slowest clock. This reset must be asserted high for AXI4-Lite registers to be read and/or written, since all core registers reside within the core clock domain. If the reset is asserted low, the AXI4-Lite interface asserts the slave error response (0x2) for all addresses.

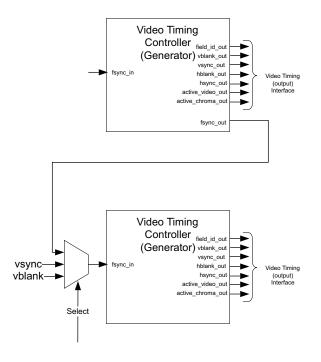

# The fsync\_in Pin

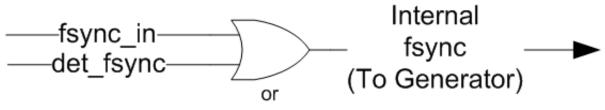

The fsync\_in pin is an active-High input. The video timing generator is synchronized to the fsync\_in input if used. The fsync\_in should be driven high for only one clock cycle per frame. This resets all internal generator counters and starts the generated frame timing synchronized to this input. Internally, the fsync\_in pin is logically "OR" combined with the internal frame sync det\_fsync, produced by the detector. The internal frame sync det\_fsync is generated by the video timing detector and can be used to synchronize the generator timing to the detector timing. The internal logic for this is show in Figure 2-4. If the fsync\_in input is used, then the detector must be disabled. Likewise, if the detector is used, then the fsync\_in pin must be driven to '0'. The use of the external fsync\_in pin and the detector can be changed at run-time but it is important that fsync\_in and det fsync are never asserted simultaneously.

Figure 2-4: Video Timing Controller Internal fsync Logic

### **AXI4-Lite Interface**

The AXI4-Lite interface creates a core that can be easily added to an Vivado Project as a processor peripheral. This section describes the I/O signals associated with the Video Timing Controller AXI4-Lite interface.

| Pin Name                                         | Dir                                           | Width                      | Description                                                                                                                                                                                                                         |  |  |  |  |

|--------------------------------------------------|-----------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AXI Write Address Channel Signals <sup>(1)</sup> |                                               |                            |                                                                                                                                                                                                                                     |  |  |  |  |

| s_axi_aclk                                       | I                                             | 1                          | AXI4-Lite Clock                                                                                                                                                                                                                     |  |  |  |  |

| s_axi_aclken                                     | I                                             | 1                          | AXI4-Lite active-High Clock Enable                                                                                                                                                                                                  |  |  |  |  |

| s_axi_aresetn                                    | I                                             | 1                          | AXI4-Lite active-Low Synchronous Reset                                                                                                                                                                                              |  |  |  |  |

| s_axi_awaddr                                     | I                                             | [(c_s_axi_addr_width-1):0] | AXI4-Lite Write Address Bus. The write address bus gives the address of the write transaction.                                                                                                                                      |  |  |  |  |

| s_axi_awvalid                                    | I                                             | 1                          | <ul> <li>AXI4-Lite Write Address Channel Write Address Valid. This signal indicates that valid write address is available.</li> <li>1 = Write address is valid.</li> <li>0 = Write address is not valid.</li> </ul>                 |  |  |  |  |

| s_axi_awready                                    | 0                                             | 1                          | AXI4-Lite Write Address Channel Write Address Ready.<br>Indicates core is ready to accept the write address.<br>1 = Ready to accept address.<br>0 = Not ready to accept address.                                                    |  |  |  |  |

|                                                  | AXI Write Data Channel Signals <sup>(1)</sup> |                            |                                                                                                                                                                                                                                     |  |  |  |  |

| s_axi_wdata                                      | I                                             | [(c_s_axi_data_width-1):0] | AXI4-Lite Write Data Bus.                                                                                                                                                                                                           |  |  |  |  |

| s_axi_wstrb                                      | I                                             | [c_s_axi_data_width/8-1:0] | AXI4-Lite Write Strobes. This signal indicates which byte lanes to update in memory.                                                                                                                                                |  |  |  |  |

| s_axi_wvalid                                     | I                                             | 1                          | <ul> <li>AXI4-Lite Write Data Channel Write Data Valid. This signal indicates that valid write data and strobes are available.</li> <li>1 = Write data/strobes are valid.</li> <li>0 = Write data/strobes are not valid.</li> </ul> |  |  |  |  |

| s_axi_wready                                     | 0                                             | 1                          | <ul> <li>AXI4-Lite Write Data Channel Write Data Ready. Indicates core is ready to accept the write data.</li> <li>1 = Ready to accept data.</li> <li>0 = Not ready to accept data.</li> </ul>                                      |  |  |  |  |

| s_axi_wready                                     | 0                                             | 1                          | <ul> <li>AXI4-Lite Write Data Channel Write Data Ready. Indicates core is ready to accept the write data.</li> <li>1 = Ready to accept data.</li> <li>0 = Not ready to accept data.</li> </ul>                                      |  |  |  |  |

Table 2-2: AXI4-Lite Signals

### Table 2-2: AXI4-Lite Signals (Cont'd)

|                            |   | AXI Write Resp                 | oonse Channel Signals <sup>(1)</sup>                                                                                                                                                                                                                                        |

|----------------------------|---|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_axi_bresp <sup>(2)</sup> | 0 | [1:0]                          | <ul> <li>AXI4-Lite Write Response Channel. Indicates results of the write transfer.</li> <li>00b = OKAY - Normal access has been successful.</li> <li>01b = EXOKAY - Not supported.</li> <li>10b = SLVERR - Error.</li> <li>11b = DECERR - Not supported.</li> </ul>        |

| s_axi_bvalid               | 0 | 1                              | <ul> <li>AXI4-Lite Write Response Channel Response Valid. Indicates response is valid.</li> <li>1 = Response is valid.</li> <li>0 = Response is not valid.</li> </ul>                                                                                                       |

| s_axi_bready               | I | 1                              | <ul> <li>AXI4-Lite Write Response Channel Ready. Indicates Master is ready to receive response.</li> <li>1 = Ready to receive response.</li> <li>0 = Not ready to receive response.</li> </ul>                                                                              |

|                            |   | AXI Read Add                   | Iress Channel Signals <sup>(1)</sup>                                                                                                                                                                                                                                        |

| s_axi_araddr               | I | [(C_S_AXI_ADDR_WIDTH-1)<br>:0] | AXI4-Lite Read Address Bus. The read address bus gives the address of a read transaction.                                                                                                                                                                                   |

| s_axi_arvalid              | I | 1                              | AXI4-Lite Read Address Channel Read Address Valid.<br>1 = Read address is valid.<br>0 = Read address is not valid.                                                                                                                                                          |

| s_axi_arready              | 0 | 1                              | <ul> <li>AXI4-Lite Read Address Channel Read Address Ready.</li> <li>Indicates core is ready to accept the read address.</li> <li>1 = Ready to accept address.</li> <li>0 = Not ready to accept address.</li> </ul>                                                         |

|                            |   | AXI Read Da                    | ata Channel Signals <sup>(1)</sup>                                                                                                                                                                                                                                          |

| s_axi_rdata                | 0 | [(C_S_AXI_DATA_WIDTH-1):<br>0] | AXI4-Lite Read Data Bus.                                                                                                                                                                                                                                                    |

| s_axi_rresp <sup>(2)</sup> | 0 | [1:0]                          | <ul> <li>AXI4-Lite Read Response Channel Response. Indicates results of the read transfer.</li> <li>00b = OKAY - Normal access has been successful.</li> <li>01b = EXOKAY - Not supported.</li> <li>10b = SLVERR - Error.</li> <li>11b = DECERR - Not supported.</li> </ul> |

| s_axi_rvalid               | 0 | 1                              | <ul> <li>AXI4-Lite Read Data Channel Read Data Valid. This signal indicates that the required read data is available and the read transfer can complete.</li> <li>1 = Read data is valid.</li> <li>0 = Read data is not valid.</li> </ul>                                   |

#### Table 2-2: AXI4-Lite Signals (Cont'd)

| s_axi_rready | I | 1 | AXI4-Lite Read Data Channel Read Data Ready. Indicates master is ready to accept the read data. |

|--------------|---|---|-------------------------------------------------------------------------------------------------|

|              |   |   | 1 = Ready to accept data.                                                                       |

|              |   |   | 0 = Not ready to accept data.                                                                   |

#### Notes:

- 1. The function and timing of these signals are defined in the AMBA AXI Protocol Version: 2.0 Specification.

- 2. For signals S\_AXI\_RRESP[1:0] and S\_AXI\_BRESP[1:0], the core does not generate the Decode Error ('11') response. Other responses such as '00' (OKAY) and '10' (SLVERR) are generated by the core based upon certain conditions.

#### Notes:

- 1. The function and timing of these signals are defined in the AMBA AXI Protocol Version: 2.0 Specification.

- 2. For signals S\_AXI\_RRESP[1:0] and S\_AXI\_BRESP[1:0], the core does not generate the Decode Error ('11') response. Other responses such as '00' (OKAY) and '10' (SLVERR) are generated by the core based upon certain conditions.

# **AXI4-Lite Register Set**

The AXI4-Lite Interface provides a memory mapped interface for all programmable registers within the core. All registers default to the values specified in Page 2 of the core GUI. All other bits default to 0x00000000 on Power-on/Reset unless otherwise noted. For complete detailed register description, refer from Table 2-4 to Table 2-37.

| Address<br>Offset    | Name                                     | Access<br>Type | Double<br>Buffered | Default<br>Value | Description                                                                       |

|----------------------|------------------------------------------|----------------|--------------------|------------------|-----------------------------------------------------------------------------------|

| 0x0000               | CONTROL<br>(XVTC_CTL)                    | R/W            | Yes                | 0                | General Control                                                                   |

| 0x0004               | STATUS<br>(XVTC_STATS)                   | R/W            | No                 | 0                | Core/Interrupt Status<br>All Status bits are<br>write-1-to-clear                  |

| 0x0008               | ERROR<br>(XVTC_ERROR)                    | R/W            | No                 | 0                | Additional Status & Error<br>Conditions<br>All Error bits are<br>write-1-to-clear |

| 0x000C               | IRQ_ENABLE<br>(XVTC_IER)                 | R/W            | No                 | 0                | Interrupt Enable/Clear                                                            |

| 0x0010               | VERSION<br>(XVTC_VER)                    | R              | N/A                | 0x06010001       | Core Hardware Version                                                             |

| 0x0014<br><br>0x001C | RESERVED                                 | R              | N/A                | 0                | RESERVED                                                                          |

| 0x0020               | DETECTOR<br>ACTIVE_SIZE<br>(XVTC_DASIZE) | R              | N/A                | 0                | Horizontal and Vertical Frame<br>Size (without blanking)                          |

#### Table 2-3: AXI4-Lite Address Map

### Table 2-3: AXI4-Lite Address Map (Cont'd)

| Address<br>Offset | Name                                         | Access<br>Type | Double<br>Buffered | Default<br>Value     | Description                                                              |

|-------------------|----------------------------------------------|----------------|--------------------|----------------------|--------------------------------------------------------------------------|

| 0x0024            | DETECTOR<br>TIMING_STATUS<br>(XVTC_DTSTAT)   | R              | N/A                | 0                    | Timing Measurement Status                                                |

| 0x0028            | DETECTOR ENCODING<br>(XVTC_DFENC)            | R              | N/A                | 0                    | Frame encoding                                                           |

| 0x002C            | DETECTOR POLARITY<br>(XVTC_DPOL)             | R              | N/A                | 0                    | Blank, Sync polarities                                                   |

| 0x0030            | DETECTOR HSIZE<br>(XVTC_DHSIZE)              | R              | N/A                | 0                    | Horizontal Frame Size (with blanking)                                    |

| 0x0034            | DETECTOR VSIZE<br>(XVTC_DVSIZE)              | R              | N/A                | 0                    | Vertical Frame Size (with blanking)                                      |

| 0x0038            | DETECTOR HSYNC<br>(XVTC_DHSYNC)              | R              | N/A                | 0                    | Start and end cycle index of<br>HSync                                    |

| 0x003C            | DETECTOR<br>F0_VBLANK_H<br>(XVTC_DVBHOFF)    | R              | N/A                | 0                    | Start and end cycle index of<br>VBlank for field 0.                      |

| 0x0040            | DETECTOR<br>F0_VSYNC_V<br>(XVTC_DVSYNC)      | R              | N/A                | 0                    | Start and end line index of VSync for field 0.                           |

| 0x0044            | DETECTOR<br>F0_VSYNC_H<br>(XVTC_DVSHOFF)     | R              | N/A                | 0                    | Start and end cycle index of VSync for field 0.                          |

| 0x0048            | DETECTOR<br>F1_VBLANK_H<br>(XVTC_DVBHOFF_F1) | R              | N/A                | 0                    | Start and end cycle index of<br>VBlank for field 1.                      |

| 0x004C            | DETECTOR<br>F1_VSYNC_V<br>(XVTC_DVSYNC_F1)   | R              | N/A                | 0                    | Start and end line index of<br>VSync for field 1.                        |

| 0x0050            | DETECTOR<br>F1_VSYNC_H<br>(XVTC_DVSHOFF_F1)  | R              | N/A                | 0                    | Start and end cycle index of<br>VSync for field 1.                       |

| 0x0060            | GENERATOR<br>ACTIVE_SIZE<br>(XVTC_GASIZE_F0) | R/W            | Yes                | Specified via<br>GUI | Horizontal and Vertical Frame<br>Size (without blanking) for<br>field 0. |

| 0x0064            | GENERATOR<br>TIMING_STATUS<br>(XVTC_GTSTAT)  | R              | No                 | Specified via<br>GUI | Timing Measurement Status                                                |

| 0x0068            | GENERATOR<br>ENCODING<br>(XVTC_GFENC)        | R/W            | Yes                | Specified via<br>GUI | Frame encoding                                                           |

| 0x006C            | GENERATOR POLARITY<br>(XVTC_GPOL)            | R/W            | Yes                | Specified via<br>GUI | Blank, Sync polarities                                                   |

### Table 2-3: AXI4-Lite Address Map (Cont'd)

| Address<br>Offset    | Name                                                      | Access<br>Type | Double<br>Buffered | Default<br>Value     | Description                                                               |

|----------------------|-----------------------------------------------------------|----------------|--------------------|----------------------|---------------------------------------------------------------------------|

| 0x0070               | GENERATOR HSIZE<br>(XVTC_GHSIZE)                          | R/W            | Yes                | Specified via<br>GUI | Horizontal Frame Size (with blanking)                                     |

| 0x0074               | GENERATOR VSIZE<br>(XVTC_GVSIZE)                          | R/W            | Yes                | Specified via<br>GUI | Vertical Frame Size (with blanking)                                       |

| 0x0078               | GENERATOR HSYNC<br>(XVTC_GHSYNC)                          | R/W            | Yes                | Specified via<br>GUI | Start and end cycle index of<br>HSync                                     |

| 0x007C               | GENERATOR<br>F0_VBLANK_H<br>(XVTC_GVBHOFF)                | R/W            | Yes                | Specified via<br>GUI | Start and end cycle index of<br>VBlank for field 0.                       |

| 0x0080               | GENERATOR<br>F0_VSYNC_V<br>(XVTC_GVSYNC)                  | R/W            | Yes                | Specified via<br>GUI | Start and end line index of VSync for field 0.                            |

| 0x0084               | GENERATOR<br>F0_VSYNC_H<br>(XVTC_GVSHOFF)                 | R/W            | Yes                | Specified via<br>GUI | Start and end cycle index of<br>VSync for field 0.                        |

| 0x0088               | GENERATOR<br>F1_VBLANK_H<br>(XVTC_GVBHOFF_F1)             | R/W            | Yes                | Specified via<br>GUI | Start and end cycle index of<br>VBlank for field 1.                       |

| 0x008C               | GENERATOR<br>F1_VSYNC_V<br>(XVTC_GVSYNC_F1)               | R/W            | Yes                | Specified via<br>GUI | Start and end line index of<br>VSync for field 1.                         |

| 0x0090               | GENERATOR<br>F1_VSYNC_H<br>(XVTC_GVSHOFF_F1)              | R/W            | Yes                | Specified via<br>GUI | Start and end cycle index of VSync for field 1.                           |

| 0x0094               | GENERATOR<br>ACTIVE_SIZE<br>(XVTC_GASIZE_F1)              | R/W            | Yes                | Specified via<br>GUI | Horizontal and Vertical Frame size for field 1.                           |

| 0x0095 RESERVED      |                                                           | R              | N/A                | 0                    | RESERVED                                                                  |

| 0x00FC               |                                                           |                |                    |                      |                                                                           |

| 0x0100<br><br>0x013c | FRAME SYNC 0 - 15<br>CONFIG<br>(XVTC_FS00 -<br>XVTC_FS15) | R/W            | Yes                | 0                    | Horizontal start clock and<br>vertical start line of Frame<br>Sync 0 - 15 |

| 0x0140               | GENERATOR GLOBAL<br>DELAY<br>(XVTC_GGD)                   | R/W            | Yes                | 0                    | Horizontal cycle and vertical line delay of generator.                    |

### Table 2-4: Control Register (Address Offset 0x0000)

| 0x0000                    | CONTROL | Read/Write                                                                                                                                                                                                                                                                                          |

|---------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                      | Bits    | Description                                                                                                                                                                                                                                                                                         |

| SW_RESET                  | 31      | Core reset.<br>Writing a '1' resets the core. This bit automatically clears when reset complete.                                                                                                                                                                                                    |

| FSYNC_RESET               | 30      | Frame Sync Core reset.<br>Writing a '1' resets the core after the start of the next input<br>frame. This bit automatically clears when reset complete.                                                                                                                                              |

| RESERVED                  | 29:27   | Reserved                                                                                                                                                                                                                                                                                            |

| FIELD_ID_POL_SRC          | 26      | Field ID Polarity Source Select<br>0: selects generated polarity from detection register (0x002c)<br>1: selects generated polarity from generators register (0x006c)                                                                                                                                |

| ACTIVE_CHROMA_POL_<br>SRC | 25      | Active Chroma Polarity Source Select<br>0: selects generated polarity from detection register (0x002c)<br>1: selects generated polarity from generator register (0x006c)                                                                                                                            |

| ACTIVE_VIDEO_POL_SRC      | 24      | Active Video Polarity Source Select<br>0: selects generated polarity from detection register (0x002c)<br>1: selects generated polarity from generator register (0x006c)                                                                                                                             |

| HSYNC_POL_SRC             | 23      | Horizontal Sync Polarity Source Select<br>0: selects generated polarity from detection register (0x002c)<br>1: selects generated polarity from generator register (0x006c)                                                                                                                          |

| VSYNC_POL_SRC             | 22      | Vertical Sync Polarity Source Select<br>0: selects generated polarity from detection register (0x002c)<br>1: selects generated polarity from generator register (0x006c)                                                                                                                            |

| HBLANK_POL_SRC            | 21      | Horizontal Blank Polarity Source Select<br>0: selects generated polarity from detection register (0x002c)<br>1: selects generated polarity from generator register (0x006c)                                                                                                                         |

| VBLANK_POL_SRC            | 20      | Vertical Blank Polarity Source Select<br>.0: selects generated polarity from detection register (0x002c)<br>1: selects generated polarity from generator register (0x006c)                                                                                                                          |

| RESERVED                  | 19      | RESERVED                                                                                                                                                                                                                                                                                            |

| CHROMA_SRC                | 18      | <ul> <li>Generator Chroma Polarity and Encoding Source Select</li> <li>0: selects Polarity and encoding from detection registers 0x0028</li> <li>and 0x002C.</li> <li>1: selects Polarity and encoding from generator registers 0x0068</li> <li>and 0x006C.</li> </ul>                              |

| VBLANK_HOFF_SRC           | 17      | Generator Vertical Blank Offset Source Select<br>0: selects F0_VBLANK_HSTART from detection register (0x003c)<br>selects F0_VBLANK_HEND from detection register (0x003c)<br>1: selects F0_VBLANK_HSTART from generator register (0x007c)<br>selects F0_VBLANK_HEND from generator register (0x007c) |

### Table 2-4: Control Register (Address Offset 0x0000) (Cont'd)

| 0x0000           | CONTROL | Read/Write                                                                                                                                                                                                                                                                                                               |

|------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name             | Bits    | Description                                                                                                                                                                                                                                                                                                              |

| VSYNC_END_SRC    | 16      | Generator Vertical Sync End Source Select<br>0: selects F0_VSYNC_HEND from detection register (0x0044)<br>selects F0_VSYNC_VEND from detection register (0x0040)<br>1: selects F0_VSYNC_HEND from generator register (0x0084)<br>selects F0_VSYNC_VEND from generator register (0x0080)                                  |

| VSYNC_START_SRC  | 15      | Generator Vertical Sync Start Source Select<br>0: selects F0_VSYNC_HSTART from detection register (0x0044)<br>selects F0_VSYNC_VSTART from detection register (0x0040)<br>1: selects F0_VSYNC_HSTART from generator register (0x0084)<br>selects F0_VSYNC_VSTART from generator register (0x0080)                        |

| ACTIVE_VSIZE_SRC | 14      | Generator Vertical Active Size Source Select<br>0: selects ACTIVE_VSIZE from detection register (0x0020)<br>1: selects ACTIVE_VSIZE from generator register (0x0060)                                                                                                                                                     |

| FRAME_VSIZE_SRC  | 13      | Generator Vertical Frame Size Source Select<br>0: selects FRAME_VSIZE from detection register (0x0034)<br>1: selects FRAME_VSIZE from generator register (0x0074)                                                                                                                                                        |

| RESERVED         | 12      | Reserved                                                                                                                                                                                                                                                                                                                 |

| HSYNC_END_SRC    | 11      | Generator Horizontal Sync End Source Select<br>0: selects HSYNC_END from detection register (0x0038)<br>1: selects HSYNC_END from generator register (0x0078)                                                                                                                                                            |

| HSYNC_START_SRC  | 10      | Generator Horizontal Sync Start Source Select<br>0: selects HSYNC_START from detection register (0x0038)<br>1: selects HSYNC_START from generator register (0x0078)                                                                                                                                                      |

| ACTIVE_HSIZE_SRC | 9       | Generator Horizontal Active Size Source Select<br>0: selects ACTIVE_HSIZE from detection register (0x0020)<br>1: selects ACTIVE_HSIZE from generator register (0x0060)                                                                                                                                                   |

| FRAME_HSIZE_SRC  | 8       | Generator Horizontal Frame Size Source Select<br>0: selects FRAME_HSIZE from detection register (0x0030)<br>1: selects FRAME_HSIZE from generator register (0x0070)                                                                                                                                                      |

| RESERVED         | 7:6     | Reserved                                                                                                                                                                                                                                                                                                                 |

| SYNC_ENABLE      | 5       | Generator Synchronization Enable.<br>Enables the generator to synchronize to the Detector or to the<br>fsync_in pin.<br>1: Generator synchronizes to the Detector or to fsync_in<br>0: Generator does not synchronize.                                                                                                   |

| RESERVED         | 4       | Reserved                                                                                                                                                                                                                                                                                                                 |

| DET_ENABLE       | 3       | Detection Enable.<br>1: Perform timing signal detection for enabled signals.<br>0: If SW_ENABLE is '0', No detection will be performed. All<br>'locked' status bits will be driven low. SW_ENABLE must be '0' to<br>utilize the DET_ENABLE bit. If SW_ENABLE is '1', both the<br>detector and generator will be enabled. |

| Table 2-4: | Control Register ( | Address Offset 0x0000) (Cont'd) |

|------------|--------------------|---------------------------------|

|------------|--------------------|---------------------------------|

| 0x0000     | CONTROL | Read/Write                                                                                                                                                                                                                                                                                                                                                                              |

|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name       | Bits    | Description                                                                                                                                                                                                                                                                                                                                                                             |

| GEN_ENABLE | 2       | Generation Enable.<br>1: Enable hardware to generate output. Set this bit high only<br>after the software has configured the generator registers.<br>0: If SW_ENABLE is '0', The generation hardware will not generate<br>video timing output signals. SW_ENABLE must be '0' to utilize<br>the DET_ENABLE bit. If SW_ENABLE is '1', both the detector and<br>generator will be enabled. |

| REG_UPDATE | 1       | Register Update. Generator and Fsync Registers are<br>double-buffered.<br>1: Update the Generator and Fsync registers at the start of next<br>frame.<br>0: Do not update the Generator and Fsync registers.                                                                                                                                                                             |

| SW_ENABLE  | 0       | Core Enable.<br>1: Enable both the Video Timing Generator and Detector.<br>0: Generator or Detector can be selectively enabled with bits 2<br>and 3 of the CONTROL register.                                                                                                                                                                                                            |

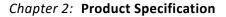

The DET\_ENABLE bit allows enabling the detector independently from the generator. The internal detector enable is a logical "OR" between the DET\_ENABLE and SW\_ENABLE bits in the control register. The internal logic that controls the detector sub-core enable is shown in Figure 2-5. The SW\_ENABLE bit allows setting one bit to '1' to enable both the detector and the generator. To enable the detector or the generator only, the SW\_ENABLE bit must be set to '0' and the detector/generator ENABLE bits (Control Register bits [3:2]) set independently.

*Figure 2-5:* **Detector Internal Enable Logic**

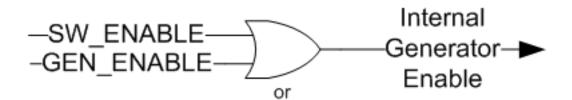

The internal generator enable is a logical "OR" between the GEN\_ENABLE and SW\_ENABLE bits in the control register. The internal logic that controls the generator sub-core enable is shown in Figure 2-6.

Figure 2-6: Generator Internal Enable Logic

| Table 2-52 Status Register (Address Offset UXUUU4 | Table 2-5: | Status Register (Address Offset 0x0004) |

|---------------------------------------------------|------------|-----------------------------------------|

|---------------------------------------------------|------------|-----------------------------------------|

| 0x0004           | STATUS | Read/Write                                                                                                                                                                                                                                                                                            |  |  |

|------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name             | Bits   | Description                                                                                                                                                                                                                                                                                           |  |  |

| FSYNC            | 31:16  | Frame Synchronization Interrupt Status. Bits 16-31 are set high when frame syncs<br>0-15 are set respectively.                                                                                                                                                                                        |  |  |

| RESERVED         | 15:14  | Reserved                                                                                                                                                                                                                                                                                              |  |  |

| GEN_ACTIVE_VIDEO | 13     | Generated Active Video Interrupt Status. Set high during the first cycle the output active video is asserted.                                                                                                                                                                                         |  |  |

| GEN_VBLANK       | 12     | Generated Vertical Blank Interrupt Status. Set high during the first cycle the output vertical blank is asserted.                                                                                                                                                                                     |  |  |

| DET_ACTIVE_VIDEO | 11     | Detected Active Video Interrupt Status. Set high during the first cycle the input active video is asserted active after lock.                                                                                                                                                                         |  |  |

| DET_VBLANK       | 10     | Detected Vertical Blank Interrupt Status. Set high during the first cycle the input vertical blank is asserted active after lock.                                                                                                                                                                     |  |  |

| LOCK_LOSS        | 9      | Loss-of-Lock Status. Set High when any detection signals have<br>lost locked. Signals that have detection disabled will not affect<br>this bit.<br>Check ERROR (0x0008) Register for signal lock status.                                                                                              |  |  |

| LOCK             | 8      | Lock Status. Set High when all detection signals have locked.<br>Signals that have detection disabled will not affect this bit.<br>Check ERROR (0x0008) Register for signal lock status. The<br>detector typically takes from 3 to 5 video frame periods to lock<br>onto the incoming video standard. |  |  |

| RESERVED         | 7:0    | Reserved                                                                                                                                                                                                                                                                                              |  |  |

Notes:

1. Writing a '1' to a bit in the STATUS register will clear the corresponding interrupt when set. Writing a '1' to a bit that is cleared, will have no effect.

| Table 2-6: | Error Register (Address Offset 0x0008) |

|------------|----------------------------------------|

|------------|----------------------------------------|

| 0x0008             | ERROR | Read/Write                                                                           |

|--------------------|-------|--------------------------------------------------------------------------------------|

| Name               | Bits  | Description                                                                          |

| RESERVED           | 31:22 | Reserved                                                                             |

| ACTIVE_CHROMA_LOCK | 21    | Active Chroma Lock Status. Set high when the active chroma timing remains unchanged. |

| Table 2-6: | Error Register (Address Offset 0x0008) |

|------------|----------------------------------------|

|------------|----------------------------------------|

| 0x0008            | ERROR | Read/Write                                                                                 |

|-------------------|-------|--------------------------------------------------------------------------------------------|

| Name              | Bits  | Description                                                                                |

| ACTIVE_VIDEO_LOCK | 20    | Active Video Lock Status. Set high when the active video timing remains unchanged.         |

| HSYNC_LOCK        | 19    | Horizontal Sync Lock Status. Set high when the horizontal sync timing remains unchanged.   |

| VSYNC_LOCK        | 18    | Vertical Sync Lock Status. Set high when the vertical sync timing remains unchanged.       |

| HBLANK_LOCK       | 17    | Horizontal Blank Lock Status. Set high when the horizontal blank timing remains unchanged. |

| VBLANK_LOCK       | 16    | Vertical Blank Lock Status Set high when the vertical blank timing remains Unchanged.      |

| RESERVED          | 15:0  | Reserved                                                                                   |

#### Notes:

1. Writing a '1' to a bit in the ERROR register will clear the corresponding bit when set. Writing a '1' to a bit that is cleared, will have no effect.

#### Table 2-7: IRQ Enable Register (Address Offset 0x000C)

| 0x000C           | IRQ_ENABLE | Read/Write                                |

|------------------|------------|-------------------------------------------|

| Name             | Bits       | Description                               |

| FSYNC            | 31:16      | Frame Synchronization Interrupt Enable    |

| RESERVED         | 15:14      | Reserved                                  |

| GEN_ACTIVE_VIDEO | 13         | Generated Active Video Interrupt Enable   |

| GEN_VBLANK       | 12         | Generated Vertical Blank Interrupt Enable |

| DET_ACTIVE_VIDEO | 11         | Detected Active Video Interrupt Enable    |

| DET_VBLANK       | 10         | Detected Vertical Blank Interrupt Enable  |

| LOCK_LOSS        | 9          | Loss-of-Lock Interrupt Enable             |

| LOCK             | 8          | Lock Interrupt Enable                     |

| RESERVED         | 7:0        | Reserved                                  |

#### Notes:

1. Setting a bit high in the IRQ\_ENABLE register enables the corresponding interrupt. Bits that are low mask the corresponding interrupt from triggering.

#### Table 2-8: Version Register (Address Offset 0x0010)

| 0x0010   | VERSION | Read                                               |

|----------|---------|----------------------------------------------------|

| Name     | Bits    | Description                                        |

| MAJOR    | 31:24   | Major version as a hexadecimal value (0x00 - 0xFF) |

| MINOR    | 23:16   | Minor version as a hexadecimal value (0x00 - 0xFF) |

| REVISION | 15:12   | Revision as a hexadecimal value (0x0 - 0xF)        |

| Name   | Bits    | Description |

|--------|---------|-------------|

| 0x0010 | VERSION |             |

|        | 0 1     |             |

### Table 2-8: Version Register (Address Offset 0x0010) (Cont'd)

| 0x0010            | VERSION | Read                                                                                   |

|-------------------|---------|----------------------------------------------------------------------------------------|

| Name              | Bits    | Description                                                                            |

| PATCH_REVISION    | 11:8    | Core Revision as a single 4-bit hexadecimal value (0x0 - 0xF) Used for patch tracking. |

| INTERNAL_REVISION | 7:0     | Internal revision number. Hexadecimal value (0x00 - 0xFF)                              |

#### Table 2-9: Detector Active Size Register (Address Offset 0x0020)

| 0x0020       | DETECTOR<br>ACTIVE_SIZE | Read                                                                                                          |

|--------------|-------------------------|---------------------------------------------------------------------------------------------------------------|

| Name         | Bits                    | Description                                                                                                   |