# **SMPTE 2022-1/2** Video over IP **Receiver v2.0**

## LogiCORE IP Product Guide

**Vivado Design Suite**

PG181 October 5, 2016

## **Table of Contents**

| IP Facts                                                   |

|------------------------------------------------------------|

| Chapter 1: Overview                                        |

| Feature Summary                                            |

| Applications                                               |

| Licensing and Ordering Information                         |

| Chapter 2: Product Specification                           |

| Standards                                                  |

| Performance                                                |

| Resource Utilization                                       |

| Port Descriptions                                          |

| Register Space   20                                        |

| Register Configuration   35                                |

| Chapter 3: Designing with the Core                         |

| General Design Guidelines                                  |

| Clocking                                                   |

| Resets                                                     |

| Memory Requirements                                        |

| Chapter 4: Design Flow Steps                               |

| Customizing and Generating the Core 45                     |

| Constraining the Core                                      |

| Clock Placement                                            |

| Simulation                                                 |

| Synthesis and Implementation                               |

| Chapter 5: Test Bench                                      |

| Appendix A: Verification, Compliance, and Interoperability |

| Appendix B: Migrating and Upgrading                        |

| Migrating to the Vivado Design Suite                       |

|                                                            |

| Upgrading in the Vivado Design Suite               | 53 |

|----------------------------------------------------|----|

| Appendix C: Debugging                              |    |

| Finding Help on Xilinx.com                         | 55 |

| Debug Tools                                        | 57 |

| Interface Debug                                    | 57 |

| IP Core Debug                                      | 58 |

| Appendix D: Additional Resources and Legal Notices |    |

| Xilinx Resources                                   | 60 |

| References                                         | 60 |

| Revision History                                   | 61 |

| Please Read: Important Legal Notices               | 61 |

|                                                    |    |

## IP Facts

. . . . . . . .

#

## Introduction

The Xilinx LogiCORE<sup>™</sup> IP SMPTE 2022-1/2 Video over IP Receiver core is used for broadcast applications that require bridging between constant bit rate MPEG-2 transport streams and 1 Gb/s IP networks. The module can recover IP packets lost due to network transmission errors and ensure integrity of transport streams. This core is used for developing Internet Protocol–based systems that reduce the overall cost of distribution and routing of audio and video data.

## Features

- Up to 16 channels of CBR MPEG-2 transport streams in accordance with SMPTE 2022-2

- Per-channel forward error correction (FEC) in accordance with SMPTE 2022-1

- Level A and Level B FEC operations

- Block-aligned and non-block-aligned FEC operations support

- Supports Virtual Local Area Network (VLAN) filtering

- AXI4-Stream data interfaces

- AXI4-Lite control interface

- Configurable channel filtering based on any combinations of the following:

- IP source address

- IP destination address

- User Datagram Protocol (UDP) source port

- UDP destination port

- Real-time Transport Protocol (RTP) Synchronization Source (SSRC) identifier

- VLAN tag value

- Seamless switching (SMPTE2022-7)

- RTP timestamp check bypass

- Include or remove FEC engine or secondary link during compile time

| LogiCORE IP Facts Table                   |                                                                                                   |  |  |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                           | Core Specifics                                                                                    |  |  |  |  |  |

| Supported<br>Device Family <sup>(1)</sup> | UltraScale+™ Families,<br>UltraScale™ Architecture, Zynq-7000®,<br>Virtex-7®, Kintex-7®, Artix-7® |  |  |  |  |  |

| Supported User<br>Interfaces              | AXI4-Lite, AXI4-Stream, AXI-4                                                                     |  |  |  |  |  |

| Resources                                 | See Table 2-1 through Table 2-3                                                                   |  |  |  |  |  |

|                                           | Provided with Core                                                                                |  |  |  |  |  |

| Design Files                              | Encrypted HDL                                                                                     |  |  |  |  |  |

| Example Design                            | XAPP1194-kc705_smpte2022_12_4ch_rx                                                                |  |  |  |  |  |

| Test Bench                                | Verilog                                                                                           |  |  |  |  |  |

| Constraints File                          | XDC                                                                                               |  |  |  |  |  |

| Simulation<br>Model                       | Encrypted RTL                                                                                     |  |  |  |  |  |

| Supported<br>S/W Driver                   | N/A                                                                                               |  |  |  |  |  |

#### Tested Design Flows<sup>(2)</sup>

| Design Entry | Vivado® Design Suite                                                                        |

|--------------|---------------------------------------------------------------------------------------------|

| Simulation   | For supported simulators, see the <u>Xilinx</u><br><u>Design Tools: Release Notes Guide</u> |

| Synthesis    | Vivado Synthesis                                                                            |

|              | Support                                                                                     |

Provided by Xilinx at the Xilinx Support web page

#### Notes:

- 1. For a complete list of supported devices, see Vivado IP catalog.

- 2. For the supported versions of the tools, see the <u>Xilinx Design</u> <u>Tools: Release Notes Guide</u>.

Features (continued)

- Statistic indicators

- Received packet

- Reordered packet, Duplicated packet count

- Recovered packet count

- Valid packet count, Unrecoverable packet count

- Out of range packet count

- Packet interval measure

- Buffer overflow flag

- Seamless protect flag

- Link differential measure

### Chapter 1

## Overview

As broadcast and communications markets converge, broadcasters and telecommunication companies increasingly use IP networks for video stream transport. Xilinx devices bridge the broadcast and the communications industries by providing highly integrated real-time video interfaces that help broadcasters reduce costs and the time it takes to acquire, edit, and produce content.

Now that video can be delivered reliably over Ethernet, broadcasters can replace expensive mobile infrastructures that support outside live broadcasts, as well as enable remote production from existing fixed studios. This dramatically reduces both capital expenditure and operating expenses. As a result, using Ethernet to transmit multiple compressed media streams is a major customer requirement. The industry implements primarily the SMPTE 2022 set of standards to create an open and interoperable way to transmit video over Ethernet, ensure quality of service (QoS), and minimize packet loss.

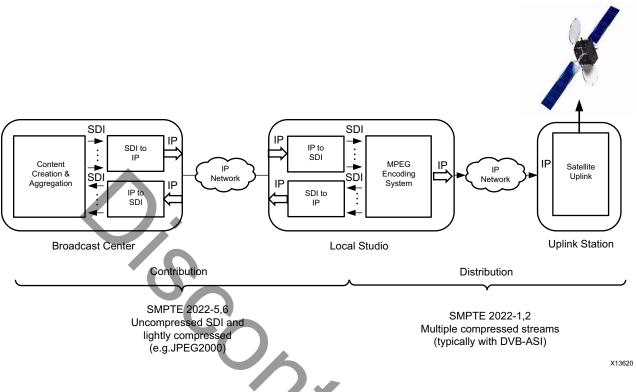

As shown in Figure 1-1, SMPTE 2022-1/2 receiver core primarily targets distribution networks where multiple transport streams are carried over 1 Gb/s Ethernet networks. The core includes Forward Error Correction (FEC), which protects transport streams over IP networks. With FEC, the receiver adds systematically generated redundant data that allows the receiver to detect and correct a limited number of packet errors.

#### Figure 1-1: SMPTE 2022-1/2 in Distribution Networks

Video packets are lost for a variety of reasons, including thermal noise, storage system defects, and transmission noise introduced by the environment. FEC enables the receiver to correct these errors without using a reverse channel to request retransmission, which is not feasible in real-time systems because the latency is too great.

#### **Feature Summary**

The core de-capsulates Ethernet packets into transport streams and can recover IP packets lost because of network transmission errors, ensuring the data integrity of MPEG transport streams. The core operates seamlessly when receiving and filtering VLAN tagged Ethernet packets.

You configure and instantiate the core by using the Vivado® design tools. Core functionality is controlled through registers via an AXI4-Lite interface.

## **Applications**

- Transport compressed constant bit rate MPEG-2 transport streams over IP networks.

- Support real-time audio/video applications in primary distribution.

### **Licensing and Ordering Information**

This Vivado® Design Suite IP module is provided under the terms of the <u>Xilinx Core License</u> <u>Agreement</u>. The module is shipped as part of the Vivado Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your local Xilinx sales representative for information about pricing and availability.

For more information, see the <u>SMPTE 2022-1/2 Video over IP</u> product web page.

Information about other Xilinx LogiCORE IP modules is available at the <u>Xilinx Intellectual</u> <u>Property</u> page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your <u>local Xilinx sales representative</u>.

#### **License Checkers**

If the IP requires a license key, the key must be verified. The Vivado design tools have several license check points for gating licensed IP through the flow. If the license check succeeds, the IP can continue generation. Otherwise, generation halts with error. License checkpoints are enforced by the following tools:

Vivado design tools: Vivado Synthesis, Vivado Implementation, write\_bitstream (Tcl command)

**IMPORTANT:** IP license level is ignored at checkpoints. The test confirms a valid license exists. It does not check IP license level.

## Chapter 2

## **Product Specification**

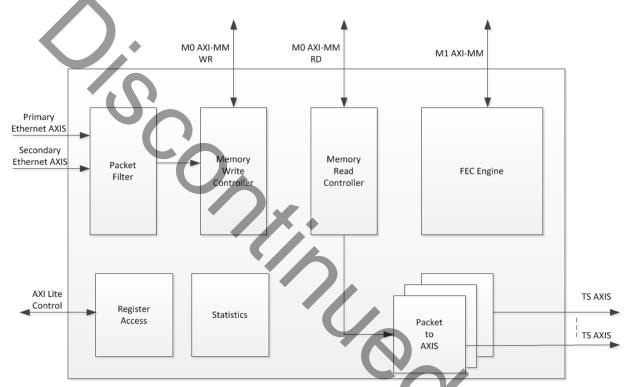

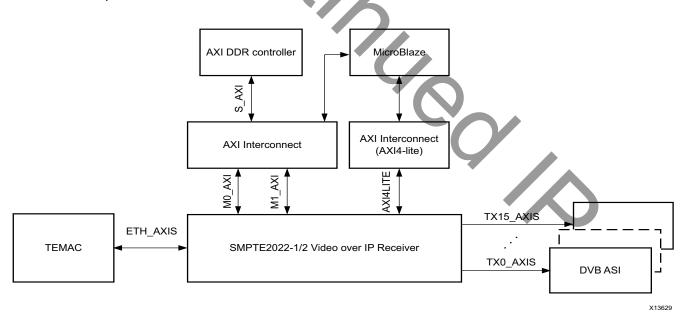

Figure 2-1 shows a block diagram of SMPTE 2022-1/2 Video over IP Receiver core.

*Figure 2-1:* Architecture Overview of SMPTE 2022-1/2 Video over IP Receiver Core The main functional blocks of the core are:

- Packet filter Demultiplex the Ethernet packets into channel streams.

- Memory write controller Puts Ethernet packets into the DDR memory buffer.

- Memory read controller Retrieves Ethernet packets from the DDR memory buffer.

- Packet to AXIS Convert the payload of the packets into AXI-Stream format

- FEC engine Performs FEC recovery on packet loss in the DDR memory buffer.

- Register access Register configuration and status read-back on the core.

- Statistics counters

## Standards

The SMPTE 2022-1/2 Video over IP Receiver core is compliant with the AXI4, AXI4-Stream and AXI4-Lite interconnect standards. See the Video IP: AXI Feature Adoption section of the *Vivado AXI Reference Guide* (UG1037)[Ref 1] for additional information. The function of the core is compliant with SMPTE 2022-1/2 standard.

## Performance

#### **Maximum Frequencies**

The maximum achievable clock frequency and all resource counts can be affected by other tool options, additional logic in the FPGA device, different versions of Xilinx tools, and other factors. See Table 2-1 through Table 2-3 for device family–specific information.

### **Resource Utilization**

Resources required for this core have been estimated for Zynq®-7000, Virtex-7®, Kintex-7®, and Artix®-7 devices. UltraScale<sup>™</sup> results are expected to be similar to 7 series results. These values were generated using Xilinx Vivado® Design Suite. They are derived from post-synthesis reports, and might change during MAP and PAR.

#### Virtex-7 FPGAs

Table 2-1 provides approximate resource counts for the various core options on Virtex-7 FPGAs.

|         |                |                    |       |       | -      | -               | -            |              |          |               |

|---------|----------------|--------------------|-------|-------|--------|-----------------|--------------|--------------|----------|---------------|

| CHANNEL | FEC<br>INCLUDE | HITLESS<br>INCLUDE | FFs   | LUTs  | Slices | LUT<br>FF Pairs | 36k<br>BRAMs | 18k<br>BRAMs | DSP48E1s | Fmax<br>(Mhz) |

| 1       | 0              | 0                  | 7007  | 3506  | 2489   | 6517            | 11           | 0            | 0        | 304           |

| 4       | 0              | 0                  | 17293 | 9198  | 7166   | 16736           | 29           | 0            | 0        | 281           |

| 8       | 0              | 0                  | 31010 | 16056 | 9717   | 27113           | 53           | 0            | 0        | 242           |

| 16      | 0              | 0                  | 58460 | 29844 | 18412  | 51993           | 101          | 0            | 0        | 234           |

| 1       | 1              | 0                  | 10928 | 5641  | 3277   | 9608            | 25           | 1            | 0        | 274           |

| 4       | 1              | 0                  | 21211 | 11499 | 7407   | 19728           | 55           | 1            | 0        | 250           |

| 8       | 1              | 0                  | 36012 | 18483 | 11613  | 32138           | 95           | 1            | 0        | 219           |

| 16      | 1              | 0                  | 65629 | 33722 | 19761  | 57961           | 175          | 1            | 0        | 212           |

Table 2-1:

Resource Utilization for Virtex-7 FPGAs (xcv7vx690t Speed -1)

| CHANNEL | FEC<br>INCLUDE | HITLESS<br>INCLUDE | FFs   | LUTs  | Slices | LUT<br>FF Pairs | 36k<br>BRAMs | 18k<br>BRAMs | DSP48E1s | Fmax<br>(Mhz) |

|---------|----------------|--------------------|-------|-------|--------|-----------------|--------------|--------------|----------|---------------|

| 1       | 0              | 1                  | 9571  | 4197  | 2841   | 8164            | 15           | 0            | 0        | 288           |

| 4       | 0              | 1                  | 24994 | 10968 | 7381   | 21081           | 33           | 0            | 0        | 274           |

| 8       | 0              | 1                  | 45489 | 19002 | 12907  | 37187           | 57           | 0            | 0        | 258           |

| 16      | 0              | 1                  | 86521 | 35004 | 25338  | 71664           | 105          | 0            | 0        | 234           |

| 1       | 1              | 1                  | 13895 | 6523  | 4102   | 11980           | 29           | 1            | 0        | 274           |

| 4       | 1              | 1                  | 29650 | 13620 | 9545   | 26077           | 59           | 1            | 0        | 250           |

| 8       | 1              | 1                  | 51973 | 22662 | 15422  | 43661           | 99           | 1            | 0        | 219           |

| 16      | 1              | 1                  | 96567 | 41714 | 28936  | 81843           | 179          | 1            | 0        | 204           |

#### Table 2-1: Resource Utilization for Virtex-7 FPGAs (xcv7vx690t Speed -1) (Cont'd)

#### **Kintex-7 FPGAs**

Table 2-2 provides approximate resource counts for the various core options on Kintex-7 FPGA and Zynq-7000 Devices with Kintex Based Programmable Logic.

| CHANNEL | FEC<br>INCLUDE | HITLESS<br>INCLUDE | FFs   | LUTs  | Slices | LUT<br>FF Pairs | 36k<br>BRAMs | 18k<br>BRAMs | DSP48E1s | Fmax<br>(Mhz) |

|---------|----------------|--------------------|-------|-------|--------|-----------------|--------------|--------------|----------|---------------|

| 1       | 0              | 0                  | 6991  | 3493  | 2219   | 6247            | 11           | 0            | 0        | 288           |

| 4       | 0              | 0                  | 17309 | 9210  | 5406   | 15458           | 29           | 0            | 0        | 266           |

| 8       | 0              | 0                  | 31010 | 16059 | 10399  | 27865           | 53           | 0            | 0        | 242           |

| 16      | 0              | 0                  | 58449 | 29409 | 17974  | 51182           | 101          | 0            | 0        | 219           |

| 1       | 1              | 0                  | 10928 | 5638  | 3379   | 9739            | 25           | 1            | 0        | 274           |

| 4       | 1              | 0                  | 21211 | 11494 | 6857   | 19053           | 55           | 1            | 0        | 258           |

| 8       | 1              | 0                  | 36012 | 18480 | 11425  | 31903           | 95           | 1            | 0        | 219           |

| 16      | 1              | 0                  | 65629 | 33722 | 20424  | 58369           | 175          | 1            | 0        | 196           |

| 1       | 0              | 1                  | 9571  | 4194  | 2966   | 8309            | 15           | 0            | 0        | 296           |

| 4       | 0              | 1                  | 24994 | 10964 | 6957   | 20830           | 33           | 0            | 0        | 258           |

| 8       | 0              | 1                  | 45489 | 19000 | 14569  | 38308           | 57           | 0            | 0        | 234           |

| 16      | 0              | 1                  | 86521 | 35006 | 25290  | 71142           | 105          | 0            | 0        | 226           |

| 1       | 1              | 1                  | 13876 | 6515  | 4145   | 11869           | 29           | 1            | 0        | 266           |

| 4       | 1              | 1                  | 29650 | 13620 | 9108   | 25671           | 59           | 1            | 0        | 242           |

| 8       | 1              | 1                  | 51954 | 22407 | 15283  | 43267           | 99           | 1            | 0        | 219           |

| 16      | 1              | 1                  | 96666 | 41480 | 28053  | 80508           | 179          | 1            | 0        | 156           |

Table 2-2: Resource Utilization for Kirtex-7 FPGAs (xc7k325t Speed -1)

#### Artix-7 FPGAs

Table 2-3 provides approximate resource counts for the various core options on Artix-7FPGA and Zynq-7000 Devices with Artix Based Programmable Logic.

| CHANNEL | FEC<br>INCLUDE | HITLESS<br>INCLUDE | FFs   | LUTs  | Slices | LUT<br>FF Pairs | 36k<br>BRAMs | 18k<br>BRAMs | DSP48E1s | Fmax<br>(Mhz) |

|---------|----------------|--------------------|-------|-------|--------|-----------------|--------------|--------------|----------|---------------|

| 1       | 0              | 0                  | 7007  | 3504  | 2317   | 6341            | 11           | 0            | 0        | 204           |

| 4       | 0              | 0                  | 17293 | 9195  | 5641   | 15772           | 29           | 0            | 0        | 180           |

| 8       | 0              | 0                  | 31026 | 15926 | 10471  | 27906           | 53           | 0            | 0        | 172           |

| 16      | 0              | 0                  | 58449 | 29413 | 17364  | 50687           | 101          | 0            | 0        | 156           |

| 1       | 1              | 0                  | 10912 | 5662  | 3284   | 9533            | 25           | 1            | 0        | 204           |

| 4       | 1              | 0                  | 21195 | 11482 | 7061   | 19270           | 55           | 1            | 0        | 180           |

| 8       | 1              | 0                  | 36012 | 18484 | 11405  | 31763           | 95           | 1            | 0        | 148           |

| 16      | 1              | 0                  | 65629 | 33681 | 18869  | 56810           | 175          | 1            | 0        | 140           |

| 1       | 0              | 1                  | 9590  | 4207  | 3045   | 8332            | 15           | 0            | 0        | 204           |

| 4       | 0              | 1                  | 24994 | 10967 | 7614   | 21142           | 33           | 0            | 0        | 196           |

| 8       | 0              | 1                  | 45489 | 19012 | 14109  | 38217           | 57           | 0            | 0        | 180           |

| 16      | 0              | 1                  | 86521 | 35977 | 23584  | 69319           | 105          | 0            | 0        | 164           |

| 1       | 1              | 1                  | 13876 | 6548  | 4359   | 12017           | 29           | 1            | 0        | 196           |

| 4       | 1              | 1                  | 29669 | 13635 | 8983   | 25417           | 59           | 1            | 0        | 172           |

| 8       | 1              | 1                  | 51954 | 22361 | 15940  | 43779           | 99           | 1            | 0        | 156           |

| 16      | 1              | 1                  | 96567 | 42730 | 26741  | 79352           | 179          | 1            | 0        | 148           |

Table 2-3:

Resource Utilization for Artix-7 FPGAs (xc7a200t Speed -1)

The maximum clock frequency results were obtained by double-registering input and output ports to reduce dependence on I/O placement. The inner level of registers used a separate clock signal to measure the path from the input registers to the first output register through the core. The results are post-implementation, using tool default settings except for high effort.

The resource usage results do not include the "characterization" registers and represent the true logic used by the core. LUT counts include SRL16s or SRL32s.

Clock frequency does not take clock jitter into account and should be derated by an amount appropriate to the clock source jitter specification. The maximum achievable clock frequency and the resource counts might also be affected by other tool options, additional logic in the FPGA, using a different version of Xilinx tools, and other factors.

## **Port Descriptions**

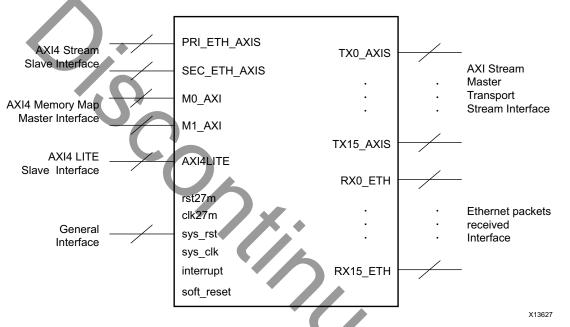

The SMPTE 2022-1/2 Video over IP Receiver core uses industry-standard control and data interfaces to connect to other system components. The following sections describe the various interfaces available with the core. Figure 2-2 provides an I/O diagram of the core. The number of TX\_AXIS interfaces depends on the number of channels configured through the GUI. SEC\_ETH\_AXIS interface is available when seamless switching is enabled. M1\_AXI interface is enabled when the FEC engine is included.

#### **General Interface Signals**

Table 2-4 summarizes the signals which are either shared by, or not part of, the AXI4-Stream, AXI-4, or AXI4-Lite control interfaces.

| Table 2-4: | Common | Interface | Signals |

|------------|--------|-----------|---------|

|------------|--------|-----------|---------|

| Signal Name Direction Wi |     | Width | Description                                              |

|--------------------------|-----|-------|----------------------------------------------------------|

| rst27m                   | In  | 1     | 27 MHz domain reset.                                     |

| clk27m                   | In  | 1     | 27 MHz clock. Used for timekeeping.                      |

| sys_rst                  | In  | 1     | System domain reset.                                     |

| sys_clk                  | In  | 1     | System clock.                                            |

| Interrupt                | Out | 1     | This signal is reserved for future use.                  |

| Soft_reset               | Out | 1     | Core reset generated from specific control register bit. |

#### **AXI4 Memory Interface**

The SMPTE 2022-1/2 Video over IP Receiver core uses an AXI4 interface to connect to the AXI4 interconnects. The AXI4 Interconnect provides access to external memory through the AXI DDR controller. See the *LogiCORE IP AXI Interconnect Product Guide* (PG059) [Ref 3] for more information.

| Signal Name    | Direction | Width | Description                               |

|----------------|-----------|-------|-------------------------------------------|

| m0_axi_awid    | Out       | 1     | Write Address Channel Transaction ID.     |

| m0_axi_awaddr  | Out       | 32    | Write Address Channel Address.            |

| m0_axi_awlen   | Out       | 8     | Write Address Channel Burst Length code.  |

| m0_axi_awsize  | Out       | 3     | Write Address Channel Transfer Size code. |

| m0_axi_awburst | Out       | 2     | Write Address Channel Burst Type.         |

| m0_axi_awlock  | Out       | 2     | Write Address Channel Atomic Access Type. |

| m0_axi_awcache | Out       | 4     | Write Address Channel Cache               |

|                |           |       | Characteristics.                          |

| m0_axi_awprot  | Out       | 3     | Write Address Channel Protection Bits.    |

| m0_axi_awqos   | Out       | 4     | Write Address Channel Quality of Service. |

| m0_axi_awvalid | Out       | 1     | Write Address Channel Valid.              |

| m0_axi_awready | In        | 1     | Write Address Channel Ready.              |

| m0_axi_wdata   | Out       | 128   | Write Data Channel Data.                  |

| m0_axi_wstrb   | Out       | 16    | Write Data Channel Data Byte Strobes.     |

| m0_axi_wlast   | Out       | 1     | Write Data Channel Last Data Beat.        |

| m0_axi_wvalid  | Out       | 1     | Write Data Channel Valid.                 |

| m0_axi_wready  | In        | 1     | Write Data Channel Ready.                 |

| m0_axi_bid     | In        | 1     | Write Response Channel Transaction ID.    |

| m0_axi_bresp   | In        | 2     | Write Response Channel Response Code.     |

| m0_axi_bvalid  | In        | 1     | Write Response Channel Valid.             |

| m0_axis_bready | Out       | 1     | Write Response Channel Ready.             |

| m0_axi_arid    | Out       | 1     | Read Address Channel Transaction ID.      |

| m0_axi_araddr  | Out       | 32    | Read Address Channel Address              |

| m0_axi_arlen   | Out       | 8     | Read Address Channel Burst Length code.   |

| m0_axi_arsize  | Out       | 3     | Read Address Channel Transfer Size code.  |

| m0_axi_arburst | Out       | 2     | Read Address Channel Burst Type.          |

Table 2-5: AXI4 Memory Interface Signals

| Table 2-5: | AXI4 Memory Interface Signals (Cont'd) |

|------------|----------------------------------------|

|------------|----------------------------------------|

| Signal Name    | Direction | Width | Description                                    |  |  |  |  |

|----------------|-----------|-------|------------------------------------------------|--|--|--|--|

| m0_axi_arlock  | Out       | 2     | Read Address Channel Atomic Access Type.       |  |  |  |  |

| m0_axi_arcache | Out       | 4     | Read Address Channel Cache<br>Characteristics. |  |  |  |  |

| m0_axi_arprot  | Out       | 3     | Read Address Channel Protection Bits.          |  |  |  |  |

| m0_axi_arqos   | Out       | 4     | AXI4 Read Address Channel Quality of Service.  |  |  |  |  |

| m0_axi_arvalìd | Out       | 1     | Read Address Channel Valid.                    |  |  |  |  |

| m0_axi_arready | In        | 1     | Read Address Channel Ready.                    |  |  |  |  |

| m0_axi_rid     | In        | 1     | Read Data Channel Data Transaction ID.         |  |  |  |  |

| m0_axi_rdata   | In        | 128   | Read Data Channel Data.                        |  |  |  |  |

| m0_axi_rresp   | In        | 2     | Read Data Channel Response Code.               |  |  |  |  |

| m0_axi_rlast   | In        | 1     | Read Data Channel Last Data Beat.              |  |  |  |  |

| m0_axi_rvalid  | In        | 1     | Read Data Channel Valid.                       |  |  |  |  |

| m0_axi_rready  | Out       | 1     | Read Data Channel Ready.                       |  |  |  |  |

| m1_axi_awid    | Out       | 1     | Write Address Channel Transaction ID.          |  |  |  |  |

| m1_axi_awaddr  | Out       | 32    | Write Address Channel Address.                 |  |  |  |  |

| m1_axi_awlen   | Out       | 8     | Write Address Channel Burst Length code.       |  |  |  |  |

| m1_axi_awsize  | Out       | 3     | Write Address Channel Transfer Size code.      |  |  |  |  |

| m1_axi_awburst | Out       | 2     | Write Address Channel Burst Type .             |  |  |  |  |

| m1_axi_awlock  | Out       | 2     | Write Address Channel Atomic Access Type.      |  |  |  |  |

| m1_axi_awcache | Out       | 4     | Write Address Channel Cache                    |  |  |  |  |

| - · ·          |           | 2     | Characteristics                                |  |  |  |  |

| m1_axi_awprot  | Out       | 3     | Write Address Channel Protection Bits.         |  |  |  |  |

| m1_axi_awqos   | Out       | 4     | Write Address Channel Quality of Service.      |  |  |  |  |

| m1_axi_awvalid | Out       | 1     | Write Address Channel Valid.                   |  |  |  |  |

| m1_axi_awready | In        | 1     | Write Address Channel Ready.                   |  |  |  |  |

| m1_axi_wdata   | Out       | 128   | Write Data Channel Data.                       |  |  |  |  |

| m1_axi_wstrb   | Out       | 16    | Write Data Channel Data Byte Strobes.          |  |  |  |  |

| m1_axi_wlast   | Out       | 1     | Write Data Channel Last Data Beat.             |  |  |  |  |

| m1_axi_wvalid  | Out       | 1     | Write Data Channel Valid.                      |  |  |  |  |

| m1_axi_wready  | In        | 1     | Write Data Channel Ready.                      |  |  |  |  |

| m1_axi_bid     | In        | 1     | Write Response Channel Transaction ID.         |  |  |  |  |

| Signal Name    | Direction | Width | Description                              |  |  |  |  |  |

|----------------|-----------|-------|------------------------------------------|--|--|--|--|--|

| m1_axi_bresp   | In        | 2     | Write Response Channel Response Code.    |  |  |  |  |  |

| m1_axi_bvalid  | In        | 1     | Write Response Channel Valid.            |  |  |  |  |  |

| m1_axis_bready | Out       | 1     | Write Response Channel Ready.            |  |  |  |  |  |

| m1_axi_arid    | Out       | 1     | Read Address Channel Transaction ID.     |  |  |  |  |  |

| m1_axi_araddr  | Out       | 32    | Read Address Channel Address             |  |  |  |  |  |

| m1_axi_arlen   | Out       | 8     | Read Address Channel Burst Length code.  |  |  |  |  |  |

| m1_axi_arsize  | Out       | 3     | Read Address Channel Transfer Size code. |  |  |  |  |  |

| m1_axi_arburst | Out       | 2     | Read Address Channel Burst Type.         |  |  |  |  |  |

| m1_axi_arlock  | Out       | 2     | Read Address Channel Atomic Access Type. |  |  |  |  |  |

| m1_axi_arcache | Out       | 4     | Read Address Channel Cache               |  |  |  |  |  |

|                |           |       | Characteristics.                         |  |  |  |  |  |

| m1_axi_arprot  | Out       | 3     | Read Address Channel Protection Bits.    |  |  |  |  |  |

| m1_axi_arqos   | Out       | 4     | AXI4 Read Address Channel Quality of     |  |  |  |  |  |

|                |           |       | Service.                                 |  |  |  |  |  |

| m1_axi_arvalid | In        | 1     | Read Address Channel Valid.              |  |  |  |  |  |

| m1_axi_arready | In        | 1     | Read Address Channel Ready.              |  |  |  |  |  |

| m1_axi_rid     | In        | 1     | Read Data Channel Data Transaction ID.   |  |  |  |  |  |

| m1_axi_rdata   | In        | 128   | Read Data Channel Data.                  |  |  |  |  |  |

| m1_axi_rresp   | In        | 2     | Read Data Channel Response Code.         |  |  |  |  |  |

| m1_axi_rlast   | In        | 1     | Read Data Channel Last Data Beat.        |  |  |  |  |  |

| m1_axi_rvalid  | In        | 1     | Read Data Channel Valid.                 |  |  |  |  |  |

| m1_axi_rready  | Out       | 1     | Read Data Channel Ready.                 |  |  |  |  |  |

|                | 1         | 1     |                                          |  |  |  |  |  |

#### Table 2-5: AXI4 Memory Interface Signals (Cont'd)

### Explanation of the AXI\_MM Port Function

#### Table 2-6: AXI\_MM Port

| Port          | Description                           |  |  |  |  |  |

|---------------|---------------------------------------|--|--|--|--|--|

| m0 port write | Incoming packet processing            |  |  |  |  |  |

| m0 port read  | Outgoing packet processing            |  |  |  |  |  |

| m1 port write | FEC recovery processing               |  |  |  |  |  |

| m1 port read  | m1 port read: FEC recovery processing |  |  |  |  |  |

#### **Ethernet AXI4 Stream Slave Interface**

See the *LogiCORE Tri-Mode Ethernet MAC Product Guide* (PG051) [Ref 4] for more information.

| Signal Name           | Direction | Width | Description                                                |  |  |  |

|-----------------------|-----------|-------|------------------------------------------------------------|--|--|--|

| pri_eth_rst           | In        | 1     | Active-High reset from TEMAC.                              |  |  |  |

| pri_eth_clk           | In        | 1     | Recovered clock from TEMAC.                                |  |  |  |

| pri_s_axis_tdata[7:0] | In        | 8     | AXI4-Stream Data from TEMAC.                               |  |  |  |

| pri_s_axis_tvalid     | In        | 1     | AXI4-Stream Data Valid from TEMAC.                         |  |  |  |

| pri_s_axis_tlast      | In        | 1     | AXI4-Stream signal from TEMAC indicating an end of packet. |  |  |  |

| pri_s_axis_tuser      | In        | 1     | AXI4-Stream User Sideband Interface from TEMAC.            |  |  |  |

| sec_eth_rst           | In        | 1     | Active-High reset from TEMAC.                              |  |  |  |

| sec_eth_clk           | In        | 1     | Recovered clock from TEMAC.                                |  |  |  |

| sec_s_axis_tdata[7:0] | In        | 8     | AXI4-Stream Data from TEMAC.                               |  |  |  |

| sec_s_axis_tvalid     | In        | 1     | AXI4-Stream Data Valid from TEMAC.                         |  |  |  |

| sec_s_axis_tlast      | In        | 1     | AXI4-Stream signal from TEMAC indicating an end of packet. |  |  |  |

| sec_s_axis_tuser      | In        | 1     | AXI4-Stream User Sideband Interface from TEMAC.            |  |  |  |

Table 2-7: AXI4 Stream Interface Signal

#### **AXI4-Lite Control Interface**

The AXI4-Lite interface allows user to dynamically control parameters within the SMPTE 2022-1/2 Video over IP Receiver core. You can configure the core using an embedded ARM or soft system processor such as MicroBlaze.

You can control the core through the AXI4-Lite interface using read and write transactions to the SMPTE 2022-1/2 Video over IP Receiver register space.

The AXI4-Lite slave interface facilitates integrating the core into a processor system, or along with other video or AXI4-Lite compliant IP, connecting via the AXI4-Lite interface to

an AXI4-Lite master. See the *LogiCORE IP AXI Interconnect Product Guide* (PG059) [Ref 3] for more information.

| Signal Name   | Direction | Width | Description                                                                                              |

|---------------|-----------|-------|----------------------------------------------------------------------------------------------------------|

| s_axi_clk     | In        | 1     | AXI4-Lite Clock.                                                                                         |

| s_axi_aresetn | In        | 1     | AXI4-Lite Active-Low Reset.                                                                              |

| s_axi_awaddr  | In        | 9     | AXI4-Lite Write Address Bus.                                                                             |

| s_axi_awvalid | In        | 1     | AXI4-Lite Write Address Channel Write Address Valid.                                                     |

| s_axi_wdata   | In        | 32    | AXI4-Lite Write Data Bus.                                                                                |

| s_axi_wstrb   | In        | 4     | AXI4-Lite Write Data Channel Data Byte Strobes.                                                          |

| s_axi_wvalid  | In        | 1     | AXI4-Lite Write Data Channel Write Data Valid.                                                           |

| s_axi_awready | Out       | 1     | AXI4-Lite Write Address Channel Write Address Ready.<br>Indicates DMA ready to accept the write address. |

| s_axi_wready  | Out       | 1     | AXI4-Lite Write Data Channel Write Data Ready.<br>Indicates DMA is ready to accept the write data.       |

| s_axi_bresp   | Out       | 2     | AXI4-Lite Write Response Channel. Indicates results of the write transfer.                               |

| s_axi_bvalid  | Out       | 1     | AXI4-Lite Write Response Channel Response Valid.<br>Indicates response is valid.                         |

| s_axi_bready  | In        | 1     | AXI4-Lite Write Response Channel Ready. Indicates target is ready to receive response.                   |

| s_axi_arvalid | In        | 1     | AXI4-Lite Read Address Channel Read Address Valid                                                        |

| s_axi_arready | Out       | 1     | Ready. Indicates DMA is ready to accept the read address.                                                |

| s_axi_araddr  | In        | 9     | AXI4-Lite Read Address Bus                                                                               |

| s_axi_rready  | In        | 1     | AXI4-Lite Read Data Channel Read Data Ready.<br>Indicates target is ready to accept the read data.       |

| s_axi_rdata   | Out       | 32    | AXI4-Lite Read Data Bus                                                                                  |

| s_axi_rresp   | Out       | 2     | AXI4-Lite Read Response Channel Response. Indicates results of the read transfer.                        |

| s_axi_rvalid  | Out       | 1     | AXI4-Lite Read Data Channel Read Data Valid.                                                             |

#### Table 2-8: AXI4-Lite Interface Signals

#### AX4I-Stream Transport Interface.

| Signal Name     | Direction | Width                         | Description                                                                                                   |  |  |  |

|-----------------|-----------|-------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| tx_axis_aresetn | Out       | AXI4-Stream Active-Low reset. |                                                                                                               |  |  |  |

| tx_axis_aclk    | In        | 1                             | AXI-4 Stream clock input.                                                                                     |  |  |  |

| tx_axis_tdata   | Out       | 8                             | Transport stream Data out.                                                                                    |  |  |  |

| tx_axis_tvalid  | Out 1     |                               | Transport stream Data Valid. A transfer takes place when both tx_axis_tvalid and tx_axis_tready are asserted. |  |  |  |

| tx_axis_tlast   | Out       | 1                             | Indicates the boundary of a packet. Fixed at 0.                                                               |  |  |  |

| tx_axis_tuser   | Out       | 1                             | User defined sideband information indicating synchronizing byte, 47h.                                         |  |  |  |

| tx_axis_tready  | In        | 1                             | Indicates that the slave can accept a transfer in the current cycle.                                          |  |  |  |

#### Table 2-9: Transport Stream AXI-Stream Interface Signals

The transport stream data output behavior from the core transport stream interface is shown in Figure 2-3. The tx\_axis\_tuser signal is High when sending the synchronizing byte; tx\_axis\_tvalid is High when output data is valid; tx\_axis\_tdata is updated when tx\_axis\_tready is High; tx\_axis\_tlast is always Low, and there is no idle byte.

| tx_axis_clk        |   |   | Л |   | Л |        | Л    |      | ΓĻ   |      | 1 |   | Ţ |      | บา | Л |     |      | J    | U | บา   |      |

|--------------------|---|---|---|---|---|--------|------|------|------|------|---|---|---|------|----|---|-----|------|------|---|------|------|

| tx_axis_tdata[7:0] |   |   |   |   |   |        | 0x47 | data | data | data | X |   |   | data | 1  |   |     | data | data |   | 0x00 |      |

| tx_axis_tvalid     |   | 1 | 1 | 1 | 1 | 1      | 1    | 1    |      |      |   |   |   |      |    |   |     |      | 1    | 1 |      |      |

| tx_axis_tuser      |   | i | 1 | 1 | i | i<br>I |      |      |      |      |   |   |   | i    | i  | i |     |      | 1    |   |      |      |

| tx_axis_tready     |   | 1 | 1 | 1 | 1 | 1      | 1    |      | 1    |      |   |   | 1 |      |    | 1 |     |      | 1    |   |      | -    |

| tx_axis_tlast      |   | i | 1 |   | 1 | 1      | 1    |      |      |      |   |   |   |      |    | 1 |     |      | 1    |   |      |      |

|                    | 5 |   |   |   | 1 |        | 1    | 8    |      |      |   | 1 |   |      |    |   | 3 S | 1    | 1    | 1 | X13  | 3628 |

Figure 2-3: SMPTE 2022-1/2 Video over IP Receiver Core Transport Stream AXI-Stream Interface

#### **Ethernet Packets Received Interface**

| Table 2-10: E | thernet Packets Received Interface Signa | als |

|---------------|------------------------------------------|-----|

|---------------|------------------------------------------|-----|

| Signal Name         | Direction | Width | Description                                                                                      |  |  |

|---------------------|-----------|-------|--------------------------------------------------------------------------------------------------|--|--|

| rx_pri_rtp_pkt_recv | Out       | 1     | Pulse indicating receiving of media packet from primary link. (Synchronous to pri_eth_clk)       |  |  |

| rx_pri_rtp_seq_num  | Out       | 16    | Sequence number of media packet received from primary link. (Synchronous to pri_eth_clk)         |  |  |

| rx_pri_rtp_ts       | Out       | 32    | Timestamp of the media packet received from primary link. (Synchronous to pri_eth_clk)           |  |  |

| rx_sec_rtp_pkt_recv | Out       | 1     | Pulse indicating receiving of media packets from secondary link. (Synchronous to sec_eth_clk)    |  |  |

| rx_sec_rtp_seq_num  | Out       | 16    | Sequence number of media packet received<br>from secondary link. (Synchronous to<br>sec_eth_clk) |  |  |

| rx_sec_rtp_ts       | Out       | 32    | Timestamp of the media packet received from secondary link. (Synchronous to sec_eth_clk)         |  |  |

| rx_rtp_pkt_buffered | Out       | 16    | Amount of media packets buffered in the DDR for the channel. (Synchronous to sys_clk)            |  |  |

| rx_rtp_pkt_transmit | Out       | I     | Pulse indicating consumption of media packet for TS output. (Synchronous to sys_clk)             |  |  |

| rx_vid_lock         | Out       | 1     | Indication of channel locking to certain payload. (Synchronous to sys_clk)                       |  |  |

| rx_playout_ready    | Out       | 1     | Indication of channel ready for playing out the TS data. (Synchronous to sys_clk)                |  |  |

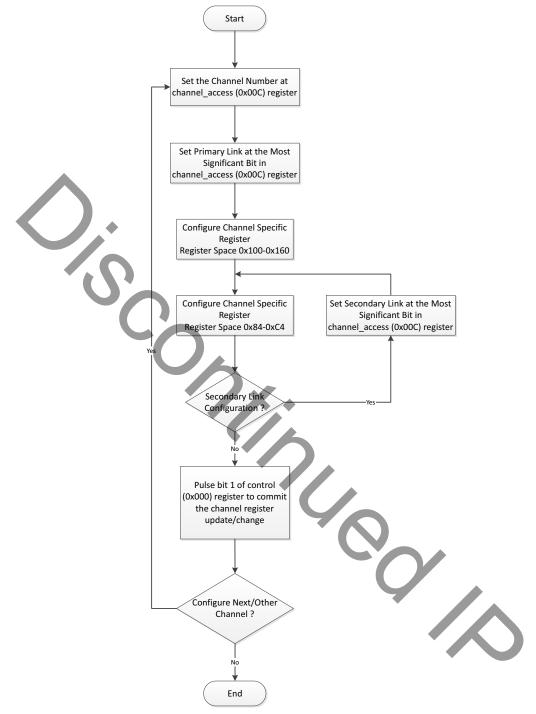

### **Register Space**

The SMPTE 2022-1/2 Video over IP Receiver register space is partitioned into general and channel-specific registers.

| Table 2-11: | AXI4-Lite | Register | Мар |

|-------------|-----------|----------|-----|

|-------------|-----------|----------|-----|

| Address             | Desister News | Access | Default Value | Register Description |       |  |  |  |  |

|---------------------|---------------|--------|---------------|----------------------|-------|--|--|--|--|

| (Hex)<br>BASEADDR + | Register Name | Туре   | (HEX)         | Bit Range            | Value |  |  |  |  |

| General Registers   |               |        |               |                      |       |  |  |  |  |

| Address             |                | Access | Default Value | Register Description |                                                                                                                                      |  |  |

|---------------------|----------------|--------|---------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| (Hex)<br>BASEADDR + | DR +           |        | Bit Range     | Value                |                                                                                                                                      |  |  |

| 0x000               | control        | R/W    | 0x0000000     | Control              |                                                                                                                                      |  |  |

|                     |                |        |               | 31:2                 | Reserved                                                                                                                             |  |  |

|                     |                |        |               | 1                    | Channel Register<br>Update.<br>0 – Host processor<br>actively updating the<br>channel registers<br>1 – Updating process<br>completed |  |  |

|                     |                |        |               | 0                    | Reserved                                                                                                                             |  |  |

| 0x004               | reset          | R/W    | 0x0000000     | Reset                |                                                                                                                                      |  |  |

|                     |                |        |               | 31:1                 | Reserved                                                                                                                             |  |  |

|                     | °O             | 6      |               | 0                    | 1 – Reset the<br>configuration<br>registers and set<br>soft_reset signal<br>High                                                     |  |  |

| 0x00C               | channel_access | R/W    | 0x00000000    | Channel Access       |                                                                                                                                      |  |  |

|                     |                |        |               | 31                   | 0 - primary<br>1 - secondary                                                                                                         |  |  |

|                     |                |        |               | 30:8                 | Reserved                                                                                                                             |  |  |

|                     |                |        | 4             | 7:0                  | The channel number<br>to access the channel<br>space registers                                                                       |  |  |

| 0x020               | sys_cfg        | R      |               | System Confi         | guration                                                                                                                             |  |  |

|                     |                |        |               | 31                   | Hitless switching supported                                                                                                          |  |  |

|                     |                |        |               | 30                   | FEC recovery supported                                                                                                               |  |  |

|                     |                |        |               | 29:8                 | Reserved                                                                                                                             |  |  |

|                     |                |        |               | 7:0                  | Number of channels supported                                                                                                         |  |  |

| 0x024               | version        | R      | 0x02000000    | Version              |                                                                                                                                      |  |  |

|                     |                |        |               | 31:24                | Version major                                                                                                                        |  |  |

|                     |                |        |               | 23:16                | Version minor                                                                                                                        |  |  |

|                     |                |        |               | 15:12                | Version revision                                                                                                                     |  |  |

|                     |                |        |               | 11:8                 | Patch ID                                                                                                                             |  |  |

|                     | 1              |        |               | 7:0                  | Revision number                                                                                                                      |  |  |

| Address             | Register Name                | Access<br>Type | Default Value<br>(HEX) | Register Description      |                                                                                                                                                                                                                        |  |

|---------------------|------------------------------|----------------|------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (Hex)<br>BASEADDR + |                              |                |                        | Bit Range                 | Value                                                                                                                                                                                                                  |  |

| 0x028               | network_path_differe         | R/W            | 0x0000000              | Network Path Differential |                                                                                                                                                                                                                        |  |

|                     | ntial                        |                |                        | 31:9                      | max acceptable<br>delay between 2<br>streams in seamless<br>mode, value based<br>on 90kHz clock ticks                                                                                                                  |  |

|                     |                              |                |                        | 8:0                       | Reserved                                                                                                                                                                                                               |  |

| 0x030               | fec_pkt_processing_d<br>elay | R/W            |                        | FEC Packet P              | rocessing Delay                                                                                                                                                                                                        |  |

|                     |                              | Ď,×            | •                      | 31:9                      | Set time delay for<br>incoming FEC<br>packets before<br>processing for<br>recovery for<br>scenarios when<br>packet arriving out of<br>ordered or delayed<br>packet. Value is<br>counted based on 90<br>kHz clock tick. |  |

| 0x034               | fec_buf_base_addr            | R/W            | 0x0000000              | FEC Buffer Base Address   |                                                                                                                                                                                                                        |  |

|                     |                              |                |                        | 31:0                      | Base address on<br>where the buffer<br>begins in the DDR                                                                                                                                                               |  |

| 0x038               | fec_buf_pool_size            | R/W            | 0x00000000             | FEC Buffer Pool Size      |                                                                                                                                                                                                                        |  |

|                     |                              |                | Č,                     | 31:0                      | No. of Bytes of<br>memory space to<br>cater for FEC buffer                                                                                                                                                             |  |

| 0x03C               | pri_recv_pkt_cnt             | R              |                        | Primary Rece              | ived Packet Count                                                                                                                                                                                                      |  |

|                     |                              |                |                        | 31:0                      | Number of packets<br>received in the<br>primary stream                                                                                                                                                                 |  |

| 0x040               | sec_recv_pkt_cnt             | R              |                        | Secondary Re              | eceived Packet Count                                                                                                                                                                                                   |  |

|                     |                              |                |                        | 31:0                      | Number of packets<br>received in the<br>secondary stream                                                                                                                                                               |  |

| 0x044               | pri_err_pkt_cnt              | R              |                        | Primary Erro              | red Packet Count                                                                                                                                                                                                       |  |

|                     |                              |                |                        | 31:0                      | Number of errored<br>packets received in<br>the primary stream                                                                                                                                                         |  |

| Table 2-11: AXI4-Lite Register Map (Cont | 'd) |

|------------------------------------------|-----|

|------------------------------------------|-----|

| Address             | Register Name       | Access | Default Value | Regist                         | ter Description                                                       |

|---------------------|---------------------|--------|---------------|--------------------------------|-----------------------------------------------------------------------|

| (Hex)<br>BASEADDR + |                     | Туре   | (HEX)         | Bit Range                      | Value                                                                 |

| 0x048               | sec_err_pkt_cnt     | R      |               | Secondary Errored Packet Count |                                                                       |

|                     |                     |        |               | 31:0                           | Number of errored<br>packets received in<br>the secondary<br>stream   |

| 0x04C               | pri_discard_pkt_cnt | R      |               | Primary Disca                  | arded Packet Count                                                    |

|                     |                     |        |               | 31:0                           | Number of not<br>matching pkts<br>received in the<br>primary stream   |

| 0x050               | sec_discard_pkt_cnt | R      |               | Secondary Di                   | scarded Packet Count                                                  |

|                     | °O,                 | 6      |               | 31:0                           | Number of not<br>matching pkts<br>received in the<br>secondary stream |

| 0x054               | gen_stat_reset      | R/W    | 0x00000000    | General Statistics Reset       |                                                                       |

|                     |                     |        |               | 31:6                           | Reserved                                                              |

|                     |                     |        | 5.            | 5                              | Reset<br>sec_discard_pkts_cnt                                         |

|                     |                     |        |               | 4                              | Reset<br>pri_discard_pkts_cnt                                         |

|                     |                     |        | YC            | 3                              | Reset<br>sec_err_pkts_cnt                                             |

|                     |                     |        |               | 2                              | Reset<br>pri_err_pkts_cnt                                             |

|                     |                     |        |               | 1                              | Reset<br>sec_recv_pkts_cnt                                            |

|                     |                     |        |               | 0                              | Reset<br>pri_recv_pkts_cnt                                            |

| Channel Reg         | isters              |        |               |                                |                                                                       |

| 0x084               | ip_hdr_param        | R      |               | IP Header Pa                   | rameter                                                               |

|                     |                     |        |               | 31:16                          | Reserved                                                              |

|                     |                     |        |               | 15:8                           | type of service(TOS)                                                  |

|                     |                     |        |               | 7:0                            | time to live(TTL)                                                     |

| Table 2-11: AXI4-Lite Register Map (Cont | 'd) |

|------------------------------------------|-----|

|------------------------------------------|-----|

| Address             | Register Name      | Access | Default Value<br>(HEX) | Register Description       |                                                                                                                       |  |

|---------------------|--------------------|--------|------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| (Hex)<br>BASEADDR + |                    | Туре   |                        | Bit Range                  | Value                                                                                                                 |  |

| 0x088               | match_vlan         | R/W    | 0x0000000              | Match VLAN                 |                                                                                                                       |  |

|                     |                    |        |                        | 31                         | VLAN filtering<br>0 - Filter stream<br>without VLAN,<br>1 - Filter stream with<br>VLAN having tag<br>info in bit 15:0 |  |

|                     |                    |        |                        | 30:16                      | Reserved                                                                                                              |  |

|                     |                    |        |                        | 15:0                       | 16-bit VLAN tag info                                                                                                  |  |

| 0x08C               | match_dest_ip_addr | R/W    | 0x0000000              | Match Destin               | nation IP Address                                                                                                     |  |

|                     | 00                 |        |                        | 31:0                       | 32-bit destination IP address                                                                                         |  |

| 0x09C               | match_src_ip_addr  | R/W    | 0x0000000              | Match Source IP Address    |                                                                                                                       |  |

|                     |                    |        |                        | 31: 0                      | 32-bit source IP<br>address                                                                                           |  |

| 0x0AC               | match_src_port     | R/W    | 0x0000000              | Match UDP Source Port      |                                                                                                                       |  |

|                     |                    |        |                        | 31:16                      | Reserved                                                                                                              |  |

|                     |                    |        |                        | 15:0                       | 16-bit UDP source port address                                                                                        |  |

| 0x0B0               | match_dest_port    | R/W    | 0x0000000              | Match UDP Destination Port |                                                                                                                       |  |

|                     |                    |        |                        | 31:16                      | Reserved                                                                                                              |  |

|                     |                    |        |                        | 15:0                       | 16-bit UDP<br>destination port<br>address                                                                             |  |

| 0x0B4               | match_sel          | R/W    | 0x0000000              | Matching Selection         |                                                                                                                       |  |

|                     |                    |        |                        | 31:6                       | Reserved                                                                                                              |  |

|                     |                    |        |                        | 5                          | To match SSRC                                                                                                         |  |

|                     |                    |        |                        | 4                          | To match UDP dest port                                                                                                |  |

|                     |                    |        |                        | 3                          | To match UDP src<br>port                                                                                              |  |

|                     |                    |        |                        | 2                          | To match Destination<br>IP                                                                                            |  |

|                     |                    |        |                        | 1                          | To match Source IP                                                                                                    |  |

|                     |                    |        |                        | 0                          | To match VLAN                                                                                                         |  |

| Address             | Register Name                | Access<br>Type | Default Value<br>(HEX) | Register Description          |                                                                                                                                |  |

|---------------------|------------------------------|----------------|------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| (Hex)<br>BASEADDR + |                              |                |                        | Bit Range                     | Value                                                                                                                          |  |

| 0x0B8               | link_reordered_              | R              |                        | Link Reorder                  | ed Packet Count                                                                                                                |  |

|                     | pkt_cnt                      |                |                        | 31:0                          | Number of reordered packets                                                                                                    |  |

| 0x0BC               | link_stat_reset              | R/W            | 0x0000000              | Link Statistic                | s Reset                                                                                                                        |  |

|                     |                              |                |                        | 31:3                          | Reserved                                                                                                                       |  |

|                     |                              |                |                        | 2                             | Reset<br>link_valid_fec_pkt_cn<br>t                                                                                            |  |

|                     | S                            |                |                        | 1                             | Reset<br>link_valid_media_pkt<br>_cnt                                                                                          |  |

|                     |                              |                |                        | 0                             | Reset link<br>reordered_pkt_cnt                                                                                                |  |

| 0x0C0               | link_valid_media_pkt_<br>cnt | R              |                        | Link Valid Media Packet Count |                                                                                                                                |  |

|                     |                              |                |                        | 31:0                          | Number of valid<br>media packets<br>received in the link<br>per channel                                                        |  |

| 0x0C4               | link_valid_fec_pkt_cnt       | R              | 31:0                   | Link Valid Media Packet Count |                                                                                                                                |  |

|                     |                              |                |                        |                               | Number of valid FEC<br>packets received in<br>the channel per link                                                             |  |

| 0x100               | chan_en                      | R/W            | 0x0000000              | Channel Enable                |                                                                                                                                |  |

|                     |                              |                |                        | 31:2                          | Reserved                                                                                                                       |  |

|                     |                              |                |                        | 1                             | RTP timestamp<br>bypass<br>1 - operate on RTP<br>stream with no<br>timestamp<br>0 - operate on RTP<br>stream with<br>timestamp |  |

|                     |                              |                |                        | 0                             | Channel enable<br>0-disablechannel.<br>1 - enable channel                                                                      |  |

| Address             | Register Name   | Access | Default Value | Regist                  | ter Description                                                                                                    |

|---------------------|-----------------|--------|---------------|-------------------------|--------------------------------------------------------------------------------------------------------------------|

| (Hex)<br>BASEADDR + |                 | Туре   | (HEX)         | Bit Range               | Value                                                                                                              |

| 0x10C               | chan_stat_reset | R/W    |               | Channel Stat            | stics Reset                                                                                                        |

|                     |                 |        |               | 31:6                    | Reserved                                                                                                           |

|                     |                 |        |               | 5                       | Reset oor_ pkt_cnt                                                                                                 |

|                     |                 |        |               | 4                       | Reset unrec_pkt_cnt                                                                                                |

|                     |                 |        |               | 3                       | Reset<br>media_buffer_ov                                                                                           |

|                     | <b>J</b> •      |        |               | 2                       | Reset dup_pkt_cnt                                                                                                  |

|                     |                 |        |               | 1                       | Reset corr_ pkt_cnt                                                                                                |

| •                   | S               |        |               | 0                       | Reset<br>chan_valid_media_pk<br>t_cnt                                                                              |

| 0x110               | match_ssrc      | R/W    | 0x0000000     | Match SSRC              |                                                                                                                    |

|                     |                 |        |               | 31:0                    | 32-bit SSRC value<br>used to match<br>between primary and<br>secondary links to<br>the channel                     |

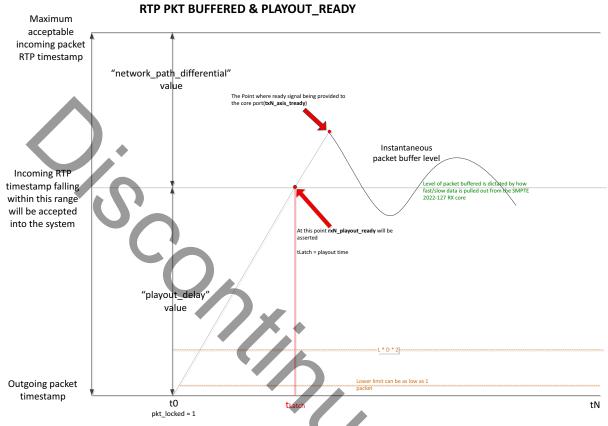

| 0x11C               | playout_delay   | R/W    | 0x00000000    | Playout delay           |                                                                                                                    |

|                     |                 |        |               | 31:9                    | Set wait time to TS<br>playout upon<br>incoming stream<br>packet size lock.<br>Value based on<br>90kHz clock ticks |

|                     |                 |        |               | 8:0                     | Reserved                                                                                                           |

| 0x120               | ts_status       | R      | 0×0000000     | Transport Stream Status |                                                                                                                    |

|                     |                 |        |               | 31:5                    | Reserved                                                                                                           |

|                     |                 |        |               | 4:2                     | TS Packets per IP<br>(17)                                                                                          |

|                     |                 |        |               | 1                       | TS pkt size:<br>0-188bytes; 1-204<br>bytes                                                                         |

|                     |                 |        |               | 0                       | Packet size locked indicator                                                                                       |

| Address             | Register Name                |     | Default Value | Regist                    | ter Description                                                                            |