# Soft Error Mitigation Controller v4.1

# LogiCORE IP Product Guide

**Vivado Design Suite**

PG036 May 4, 2022

Xilinx is creating an environment where employees, customers, and partners feel welcome and included. To that end, we're removing non-inclusive language from our products and related collateral. We've launched an internal initiative to remove language that could exclude people or reinforce historical biases, including terms embedded in our software and IPs. You may still find examples of non-inclusive language in our older products as we work to make these changes and align with evolving industry standards. Follow this link for more information.

# **Table of Contents**

#### **IP Facts**

| Chapter 1: Overview                      |

|------------------------------------------|

| Memory Types                             |

| Mitigation Approaches 6                  |

| Reliability Estimation 7                 |

| Feature Summary 8                        |

| Applications                             |

| Key Considerations for SEM IP Adoption   |

| Encryption and Authentication Support 12 |

| Unsupported Features                     |

| Licensing and Ordering                   |

|                                          |

| Chapter 2: Product Specification         |

| Features 14                              |

| Standards Compliance                     |

| Performance                              |

| Resource Utilization                     |

| Port Descriptions                        |

| Chapter 3: Designing with the Core       |

|                                          |

| Interfaces                               |

| Behaviors                                |

| Systems                                  |

| Customizations                           |

| Data Consistency                         |

| Configuration Memory Masking             |

| Clocking                                 |

| Resets                                   |

| Additional Considerations80              |

| Chapter 4: Design Flow Steps             |

| Customizing and Generating the Core      |

| Constraining the Core 8                                    | 9          |

|------------------------------------------------------------|------------|

| Simulation 9                                               | 16         |

| Synthesis and Implementation                               | 7          |

| Integration and Validation 9                               | 7          |

| Chapter 5: Example Design                                  |            |

| Functions                                                  | 10         |

| Port Descriptions                                          | 13         |

| Demonstration Test Bench                                   | 17         |

| Implementation                                             | 17         |

| External Memory Programming File                           | .0         |

| Appendix A: Verification, Compliance, and Interoperability |            |

| Verification 11                                            | .3         |

| Validation                                                 | .4         |

| Conformance Testing                                        | .4         |

| Appendix B: Upgrading                                      |            |

| Migrating to the Vivado Design Suite 11                    | .5         |

| Upgrading in the Vivado Design Suite                       | .5         |

| Appendix C: Debugging                                      |            |

| Finding Help on Xilinx.com                                 | .6         |

| Debug Tools                                                | .7         |

| Hardware Debug 11                                          | .8         |

| Interface Debug                                            | .9         |

| Clocking                                                   | 20         |

| Appendix D: Additional Resources and Legal Notices         |            |

| Xilinx Resources                                           | <b>1</b>   |

| Documentation Navigator and Design Hubs 12                 | <b>1</b>   |

| References                                                 | 22         |

| Revision History                                           | :3         |

| Please Read: Important Legal Notices 12                    | <u>2</u> 5 |

# Introduction

The LogiCORE™ IP Soft Error Mitigation (SEM) Controller is an automatically configured, pre-verified solution to detect and correct soft errors in Configuration Memory of Xilinx FPGAs. Soft errors are unintended changes to the values stored in state elements caused by ionizing radiation.

The SEM Controller does not prevent soft errors; however, it provides a method to better manage the system-level effects of soft errors. Proper management of these events can increase reliability and availability, and reduce system maintenance and downtime costs.

## **Features**

- Typical detection latency of 25 ms in many devices.

- Integration of built-in silicon primitives to fully leverage and improve upon the inherent error detection capability of the FPGA.

- Optional error correction, using selectable method: repair, enhanced repair, or replace.

- Correction by repair method is ECC algorithm based.

- Correction by enhanced repair method is ECC and CRC algorithm based.

- Correction by replace method is data re-load based.

- Using Xilinx® Essential Bits technology, optional error classification to determine if a soft error has affected the function of the user design.

- Increases uptime by avoiding disruptive recovery approaches for errors that have no real effect on design operation.

- Reduces effective failures-in-time (FIT).

- Optional error injection to support evaluation of SEM Controller applications.

|                                              | LogiCORE IP Facts Table                                                     |  |  |

|----------------------------------------------|-----------------------------------------------------------------------------|--|--|

|                                              | Core Specifics                                                              |  |  |

| Supported<br>Device<br>Family <sup>(1)</sup> | Zynq®-7000 SoC, 7 Series                                                    |  |  |

| Supported<br>User Interfaces                 | RS-232, SPI                                                                 |  |  |

| Resources                                    | See Table 2-9 through Table 2-13                                            |  |  |

|                                              | Provided with Core                                                          |  |  |

| Design Files                                 | Encrypted RTL                                                               |  |  |

| Example<br>Design                            | VHDL and Verilog                                                            |  |  |

| Test Bench                                   | VHDL and Verilog <sup>(2)</sup>                                             |  |  |

| Constraints<br>File                          | XDC                                                                         |  |  |

| Simulation<br>Model                          | Verilog and/or VHDL Behavioral model<br>or source HDL <sup>(2)</sup>        |  |  |

| Supported<br>S/W Driver                      | N/A                                                                         |  |  |

|                                              | Tested Design Flows <sup>(3)</sup>                                          |  |  |

| Design Entry                                 | Vivado® Design Suite                                                        |  |  |

| Simulation                                   | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |  |

| Synthesis                                    | Vivado Synthesis                                                            |  |  |

| Support                                      |                                                                             |  |  |

| Release Notes<br>and Known<br>Issues         | Master Answer Record: 54642                                                 |  |  |

| All Vivado IP<br>Change Logs                 | Master Vivado IP Change Logs: 72775                                         |  |  |

| Xilinx Support web page                      |                                                                             |  |  |

- For a complete list of supported devices, see the Vivado IP catalog.

- Functional and timing simulation of designs that include the SEM Controller is supported. However, it is not possible to observe the SEM Controller behaviors in simulation. Hardware-based evaluation is required.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

lonizing radiation is capable of inducing undesired effects in most silicon devices. Broadly, an undesired effect resulting from a single event is called a Single Event Effect (SEE). In most cases, these events do not permanently damage the silicon device; SEEs that result in no permanent damage to the device are called soft errors. However, soft errors have the potential to reduce reliability.

Xilinx® devices are designed to have an inherently low susceptibility to soft errors. However, Xilinx also recognizes that soft errors are unavoidable within commercial and practical constraints. As a result, Xilinx has integrated soft error detection and correction capability into many device families.

In many applications, soft errors can be ignored. In applications where higher reliability is desired, the integrated soft error detection and correction capability is usually sufficient. In demanding applications, the SEM Controller can ensure an even higher level of reliability.

# **Memory Types**

If a soft error occurs, one or more memory bits are corrupted. The memory bits affected can be in the device configuration memory (which determines the behavior of the design), or might be in design memory elements (which determine the state of the design). The following four memory categories represent a majority of the memory in a device:

- **Configuration Memory**: Storage elements used to configure the function of the design loaded into the device. This includes function block behavior and function block connectivity. This memory is physically distributed across the entire device and represents the largest number of bits. Only a fraction of the bits are essential to the proper operation of any specific design loaded into the device.

- **Block Memory**: High capacity storage elements used to store design state. As the name implies, the bits are clustered into a physical block, with several blocks distributed across the entire device. Block Memory represents the second largest number of bits.

- **Distributed Memory**: Medium capacity storage elements used to store design state. This type of memory is present in certain configurable logic blocks (CLBs) and is distributed across the entire device. Distributed Memory represents the third largest number of bits.

• **Flip-Flops**: Low capacity storage elements used to store design state. This type of memory is present in all configurable logic blocks (CLBs) and is distributed across the entire device. Flip-Flops represent the fourth largest number of bits.

An extremely small number of additional memory bits exist as internal device control registers and state elements. Soft errors occurring in these areas can result in regional or device-wide interference that is referred to as a single-event functional interrupt (SEFI). Due to the small number of these memory bits, the frequency of SEFI events is considered negligible in this discussion, and these infrequent events are not addressed by the SEM Controller.

# **Mitigation Approaches**

Soft error mitigation for design state in Block Memory, Distributed Memory, and Flip-Flops can be performed in the design itself, by applying standard techniques such as error detection and correction codes or redundancy. Soft errors in unused design state resources (those physically present in the device, but unused by the design) are ignored. Designers concerned about reliability must assess risk areas in the design and incorporate mitigation techniques for the design state as warranted.

Soft error mitigation for the design function in Configuration Memory is performed using error detection and correction codes.

Configuration Memory is organized as an array of frames, much like a wide static RAM. In many device families, each frame is protected by ECC, with the entire array of frames protected by CRC in all device families. The two techniques are complementary; CRC is incredibly robust for error detection, while ECC provides high resolution of error location.

The SEM Controller builds upon the robust capability of the integrated logic by adding optional capability to classify Configuration Memory errors as either "essential" or "non-essential." This leverages the fact that only a fraction of the Configuration Memory bits are essential to the proper operation of any specific design.

Without error classification, all Configuration Memory errors must be considered "essential." With error classification, most errors will be assessed "non-essential" which eliminates false alarms and reduces the frequency of errors that require a potentially disruptive system-level mitigation response.

Additionally, the SEM Controller extends the built-in correction capability to accelerate error detection and provides the optional capability to handle multi-bit errors.

If the features offered by the SEM Controller are not required, the integrated soft error detection and correction capability in the silicon should be sufficient for SEU mitigation. See the *7 Series FPGAs Configuration User Guide* (UG470) [Ref 1] for information on how to

use the built-in error detection and correction capability for 7 series FPGAs and Zyng®-7000 SoCs.

# **Reliability Estimation**

As a starting point, your specification for system reliability should highlight critical sections of the system design and provide a value for the required reliability of each sub-section. Reliability requirements are typically expressed as failures in time (FIT), which is the number of design failures that can be expected in  $10^9$  hours (approximately 114,155 years).

When more than one instance of a design is deployed, the probability of a soft error affecting any one of them increases proportionately. For example, if the design is shipped in 1,000 units of product, the nominal FIT across all deployed units is 1,000 times greater. This is an important consideration because the nominal FIT of the total deployment can grow large and can represent a service or maintenance burden.

The nominal FIT is different from the probability of an individual unit being affected. Also, the probability of a specific unit incurring a second soft error is determined by the FIT of the individual design and not the deployment. This is an important consideration when assessing suitable soft error mitigation strategies for an application.

The FIT associated with soft errors must not be confused with that of product life expectancy, which considers the replacement or physical repair of some part of a system.

Xilinx device FIT data is reported in the *Device Reliability Report* (UG116) [Ref 2]. The data reveals the overall infrequency of soft errors.

**TIP:** The failure rates involved are so small that most designs do not include any form of soft error mitigation.

The contribution to FIT from flip-flops is negligible based on the flip-flop's very low FIT and small quantity. However, this does not discount the importance of protecting the design state stored in flip-flops. If any state stored in flip-flops is highly important to design operation, the design must contain logic to detect, correct, and recover from soft errors in a manner appropriate to the application.

The contribution to FIT from Distributed Memory and Block Memory can be large in designs where these resources are highly utilized. As previously noted, the FIT contribution can be substantially decreased by using soft error mitigation techniques in the design. For example, Block Memory resources include built-in error detection and correction circuits that can be used in certain Block Memory configurations. For all Block Memory and Distributed Memory configurations, soft error mitigation techniques can be applied using programmable logic resources.

The contribution to FIT from Configuration Memory is large. Without using an error classification technique, all soft errors in Configuration Memory must be considered "essential," and the resulting contribution to FIT eclipses all other sources combined. Use of error classification reduces the contribution to FIT by no longer considering most soft errors as failures; if a soft error has no effect, it can be corrected without any disruption.

In designs requiring the highest level of reliability, classification of soft errors in Configuration Memory is essential. This capability is provided by the SEM Controller.

# **Feature Summary**

The SEM Controller implements five main functions: initialization, error injection, error detection, error correction, and error classification. All functions, except initialization and detection, are optional; desired functions are selected during the IP core configuration and generation process.

The SEM Controller initializes by bringing the integrated soft error detection capability of the FPGA into a known state after the FPGA enters user mode. After this initialization, the SEM Controller observes the integrated soft error detection status. When an ECC or CRC error is detected, the SEM Controller evaluates the situation to identify the Configuration Memory location involved.

If the location can be identified, the SEM Controller optionally corrects the soft error by repairing it or by replacing the affected bits. The repair methods use active partial reconfiguration to perform a localized correction of Configuration Memory using a read-modify-write scheme. These methods use algorithms to identify the error in need of correction. The replace method also uses active partial reconfiguration with the same goal, but this method uses a write-only scheme to replace Configuration Memory with original data. This data is provided by the implementation tools and stored outside the SEM Controller.

The SEM Controller optionally classifies the soft error as essential or non-essential using a lookup table. Information is fetched as needed during execution of error classification. This data is also provided by the implementation tools and stored outside the SEM Controller.

When the SEM Controller is idle, it optionally accepts input from the user to inject errors into Configuration Memory. This feature is useful for testing the integration of the SEM Controller into a larger system design. Using the error injection feature, system verification and validation engineers can construct test cases to ensure the complete system responds to soft error events as expected.

# **Applications**

Although the SEM Controller can operate autonomously, most applications use the solution in conjunction with an application-level supervisory function. This supervisory function monitors the event reporting from the SEM Controller and determines if additional actions are necessary (for example, reconfigure the device or reset the application).

System designers are encouraged to carefully consider each design's reliability requirements and system-level supervisory functions to make informed decisions.

Is an error mitigation solution even required? Is the solution built into the target device sufficient for the application requirements, or is the SEM Controller required? If the SEM Controller is required, what features should be used?

When the SEM Controller is the best choice for the application, Xilinx recommends that the SEM Controller is used as provided, including the system-level design example components for interfacing with external devices. However, these interfaces can be modified if required for the application.

**RECOMMENDED:** Xilinx recommends integrating the SEM IP core as early as possible, ideally at the start of the project. For more information, see Integration and Validation, page 97.

# **Key Considerations for SEM IP Adoption**

This section is designed to assess whether the SEM IP helps meet the soft error mitigation goals of your product's deployment and what mitigation approach should be chosen. The concepts used in this section were covered in prior sections.

There are two main considerations:

- Understanding the soft error mitigation requirement for your design

- What actions need to be taken if a soft error occurs

# **Understanding the Soft Error Mitigation Requirement**

If the effects of soft errors are a concern for your product's deployment, each component in the system design will usually need a FIT budget. To calculate the FIT for a Xilinx FPGA, use the SEU FIT rate estimator available in the SEU lounge and see the XAPP472 SEU Estimator on how to use the FIT rate estimator.

To calculate FIT for a deployment, at the minimum you need:

- Target device

- Estimated number of the device to be deployed

Besides providing the estimated FIT for the device, the estimator also predicts the number of soft errors expected for a given time frame.

By using an implemented design, a more accurate estimation of the FIT is achieved. This is possible by entering the number of block RAM used, whether the block RAM ECC feature is employed to detect and correct soft errors, as well as the percentage of essential bits in the design. Essential bits are defined as configuration RAM bits that are used to define the function on the FPGA. If an essential bit is changed unintentionally by a soft error, it is possible that the function in the FPGA does not behave as intended.

On the other hand, if a non-essential bit is changed, there is no impact to the function. The following steps determine the percentage of essential bits in a design:

1. Set the following property in Vivado®:

```

set_property bitstream.seu.essentialbits yes [current_design]

```

- 2. Regenerate the bitstream for your design.

- 3. The essential bits percentage is printed in the Vivado Tcl console and consequently the Vivado log while the bitstream and essential bits data are being generated. Here is an example:

```

Writing bitstream ./sem_ultrap_v3_1_example.bit...

Creating bitstream...

Writing bitstream ./sem_ultrap_v3_1_example.ebc...

Creating essential bits data...

This design has 707717 essential bits out of 143015456 total (0.49%).

```

After a FIT estimation has been completed, it must be checked to determine if the FIT requirement for the deployment is met. Other design approaches might need to be implemented to reduce the FIT.

If there is not a FIT target, then it is unclear what design changes (and trade-offs that come with them) need to be made to mitigate the soft error effects, including whether a deployment benefits from using the SEM IP. If that is the case, it is important to identify the benefits obtained using SEM IP before integrating it.

#### Actions to Consider When a Soft Error Occurs

The SEM IP can be configured to detect or detect and correct soft errors. Therefore, consideration must be given to the system-level actions, if any, that must be taken in reaction to soft errors. If no action is taken when a soft error is detected in a design, the benefits of having the SEM IP in the design should be assessed and understood. While this is a valid use case, the effects of soft errors on the design should be known and this mitigation approach should be well understood to ensure it meets the soft error mitigation goals.

**RECOMMENDED:** When using the SEM IP in a design, it is strongly recommended to log the output of the Monitor interface.

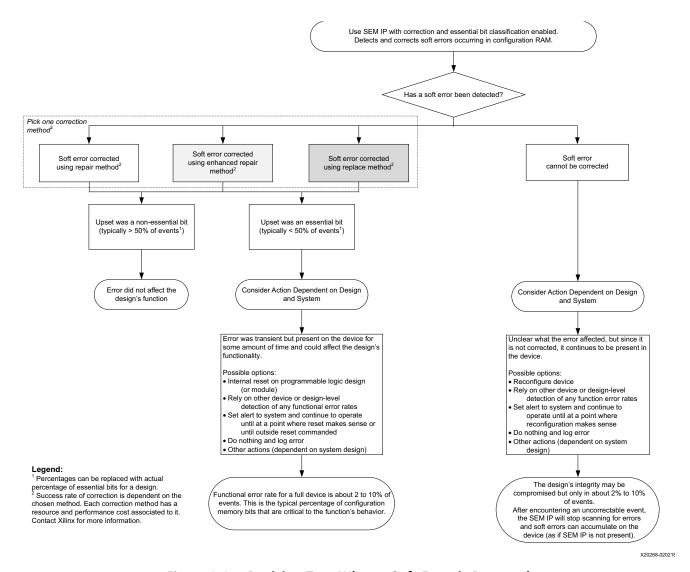

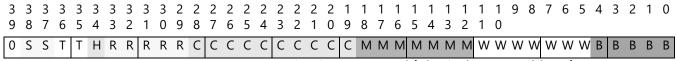

Figure 1-1 shows an example of a decision tree that iterates what a system could do when a soft error occurs. By understanding the possibilities and the system-level considerations, a decision can be made to determine whether or not to use the SEM IP in a design.

**Note:** This diagram is provided as an example and it does not list all the possible considerations.

Figure 1-1: Decision Tree When a Soft Error is Detected

# **Encryption and Authentication Support**

In 7 series devices, private key encryption and authentication of the bitstream is supported with the SEM IP. Bitstream encryption using AES-256 along with SHA2-256 HMAC for authentication has been verified to be compatible with SEM IP in hardware.

In Zynq®-7000 SoC devices, the same private key encryption and authentication of the bitstream is also supported with SEM IP.

Public key authentication using RSA-2048 has not been verified, and as a result, is not supported by the SEM IP.

# **Unsupported Features**

The SEM Controller does not operate on soft errors in block memory, distributed memory, or flip-flops. Soft error mitigation in these memory resources must be addressed by the user logic through preventive measures such as redundancy or error detection and correction codes.

The SEM Controller does not operate on soft errors in state elements contained within embedded processor systems, such as those found in Xilinx Zynq-7000 devices. Soft error mitigation in these memory resources must be addressed through software running on the processor system.

Unsupported features and specific limitations include functional, implementation, and use considerations. For more details, see Additional Considerations in Chapter 3.

# **Licensing and Ordering**

This Xilinx LogiCORE™ IP module is provided at no additional cost with the Xilinx Vivado® Design Suite under the terms of the Xilinx End User License.

Information about other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

### **License Checkers**

If the IP requires a license key, the key must be verified. The Vivado design tools have several license checkpoints for gating licensed IP through the flow. If the license check succeeds, the IP can continue generation. Otherwise, generation halts with error. License checkpoints are enforced by the following tools:

- Vivado synthesis

- Vivado implementation

- write\_bitstream (Tcl command)

**IMPORTANT:** IP license level is ignored at checkpoints. The test confirms a valid license exists. It does not check IP license level.

# **Product Specification**

This chapter contains the specification of the LogiCORE™ IP Soft Error Mitigation (SEM) Controller. This configurable controller for mitigation of soft errors in configuration memory also comes with a system-level example design showing use of the controller in a system.

# **Features**

The SEM controller includes:

- Integration of silicon features to leverage built-in error detection capability.

- Implementation of error correction capability to support correction of soft errors. The error correction method can be defined as:

- Repair: ECC algorithm-based correction. This method supports correction of configuration memory frames with single-bit errors. This covers correction of all single-bit upset events. It also covers correction of multi-bit upset events when errors are distributed one per frame as a result of configuration memory interleaving.

- **Enhanced Repair**: ECC and CRC algorithm-based correction. This method supports correction of configuration memory frames with single-bit errors or double-bit adjacent errors. This covers correction of all single-bit upset events and all double-bit adjacent upset events. This also covers correction of multi-bit upset events when errors are distributed one or two adjacent per frame as a result of configuration memory interleaving.

- Replace: Data reload based correction. This method supports correction of configuration memory frames with arbitrary errors. This covers correction of any upset event that can be resolved to specific configuration memory frames, even if the exact bit locations in the frames cannot be determined.

- Implementation of error classification capability to determine if corrected errors have affected configuration memory in locations essential to the function of the design.

- Provision for error injection to support verification of the controller and evaluation of applications of the controller.

The example design includes:

- Instantiation of the user-configured controller.

- An interface between the controller and external storage. This is required when the controller is configured to perform error classification or error correction by replace.

- An interface between the controller and an external processor for ease of use when the controller is configured to perform error injection.

# **Standards Compliance**

No standards compliance or certification testing is defined. The SEM Controller is exposed to a beam of accelerated particles as part of an extensive hardware validation process.

# **Performance**

Performance metrics for the SEM Controller are derived from silicon specifications and direct measurement, and are for budgetary purposes only. Actual performance might vary.

# **Solution Reliability**

Table 2-1 captures the estimated FIT for the SEM controller. This estimation includes the contribution of configuration RAM and block RAM used by the SEM controller and its system-level example design. Because this estimation is for a design that has all features enabled and all signals brought to I/O pins, it presents an upper bound value.

Table 2-1: Estimated FIT Rate

| Device                      | FIT |

|-----------------------------|-----|

| Monolithic solution         | ~7  |

| SSI solution <sup>(1)</sup> | ~26 |

#### Notes:

1. Estimated for XC7VX1140T with four SLRs and four SEM controllers.

# **Maximum Frequencies**

The maximum frequency of operation of the SEM Controller is not guaranteed. In no case can the maximum frequency of operation exceed the internal configuration access port (ICAP)  $F_{Max}$  specified in the relevant FPGA data sheet as configuration interface AC timing parameter Frbcck. Table 2-2 provides a summary of ICAP  $F_{Max}$  values.

Table 2-2: ICAP Maximum Frequencies

| Device                | ICAP F <sub>Max</sub> |

|-----------------------|-----------------------|

| Zynq-7000             | 100 MHz               |

| Zynq-7000A            | 100 MHz               |

| Zynq-7000Q            | 100 MHz               |

| Kintex-7              | 100 MHz               |

| Kintex-7 Low Voltage  | 70 MHz                |

| Kintex-7Q             | 100 MHz               |

| Kintex-7Q Low Voltage | 70 MHz                |

| Virtex-7 (Non-SSI)    | 100 MHz               |

| Virtex-7Q (Non-SSI)   | 100 MHz               |

| Virtex-7 (SSI)        | 70 MHz                |

| Artix-7               | 100 MHz               |

| Artix-7 Low Voltage   | 70 MHz                |

| Artix-7Q              | 100 MHz               |

| Artix-7A              | 100 MHz               |

| Spartan-7             | 100 MHz               |

Other maximum frequency limitations might apply. For more details on determining the maximum frequency of operation for the SEM Controller, see Interfaces in Chapter 3.

## **Solution Latency**

The error mitigation latency of the solution is defined as the total time that elapses between the creation of an error condition and the conclusion of the mitigation process. The mitigation process consists of detection, correction, and classification.

#### **Estimation Data**

The solution behaviors are based on processing of FPGA configuration memory frames. Single-bit errors always reside in a single frame. Generally, an *N*-bit error can present in several ways, ranging from one frame containing all bit errors, to *N* frames each containing one bit error. When multiple frames are affected by an error, the sequence of detection, correction, and classification is repeated for each affected frame.

The solution properly mitigates an arbitrary workload of errors. The error mitigation latency estimation of an arbitrary workload is complex. This section focuses on the common case involving a single frame, but provides insight into the controller behavior to aid in understanding other scenarios.

#### Start-Up Latency

Start-up latency is the delay between the end of FPGA configuration and the completion of the controller initialization, as marked by entry into the observation state. This latency is a function of the FPGA size (frame count) and the solution clock frequency. It is also a function of the selected correction mode.

The start-up latency is incurred only once. It is not part of the mitigation process. Table 2-3 illustrates start-up latency, decomposed into sub-steps of boot and initialization. The boot time is independent of the selected correction mode, while the initialization time is dependent on the selected correction mode.

Table 2-3: Maximum Start-Up Latency at ICAP F<sub>Max</sub>

| Device           | Boot Time at ICAP F <sub>Max</sub> | Initialization Time at ICAP<br>F <sub>Max</sub> (Repair/Replace) | Initialization Time at ICAP F <sub>Max</sub> (Enhanced Repair) |

|------------------|------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|

| XC7A12T          | 110 ms                             | 8.5 ms                                                           | 1.0 s                                                          |

| XC7A15T          | 110 ms                             | 13.8 ms                                                          | 1.7 s                                                          |

| XC7A25T          | 110 ms                             | 8.5 ms                                                           | 1.0 s                                                          |

| XC7A35T          | 110 ms                             | 13.8 ms                                                          | 1.7 s                                                          |

| XC7A50T          | 110 ms                             | 13.8 ms                                                          | 1.7 s                                                          |

| XC7A75T          | 110 ms                             | 24.1 ms                                                          | 2.9 s                                                          |

| XC7A100T         | 110 ms                             | 24.1 ms                                                          | 2.9 s                                                          |

| XC7A200T         | 110 ms                             | 55.4 ms                                                          | 6.6 s                                                          |

| XC7K70T          | 110 ms                             | 17.8 ms                                                          | 2.1 s                                                          |

| XC7K160T         | 110 ms                             | 38.8 ms                                                          | 4.6 s                                                          |

| XC7K325T         | 110 ms                             | 71.0 ms                                                          | 9.3 s                                                          |

| XC7K355T         | 110 ms                             | 79.9 ms                                                          | 11.9 s                                                         |

| XC7K410T         | 110 ms                             | 91.5 ms                                                          | 15.4 s                                                         |

| XC7K420T         | 110 ms                             | 106.6 ms                                                         | 21.1 s                                                         |

| XC7K480T         | 110 ms                             | 106.6 ms                                                         | 21.1 s                                                         |

| XC7VX330T        | 110 ms                             | 77.3 ms                                                          | 11.1 s                                                         |

| XC7VX415T        | 110 ms                             | 98.1 ms                                                          | 17.7 s                                                         |

| XC7VX485T        | 110 ms                             | 115.7 ms                                                         | 24.5 s                                                         |

| XC7VX550T        | 110 ms                             | 163.5 ms                                                         | 48.7 s                                                         |

| XC7VH580T (SSI)  | 110 ms                             | 74.3 ms                                                          | 10.2 s                                                         |

| XC7V585T         | 110 ms                             | 124.4 ms                                                         | 28.3 s                                                         |

| XC7VX690T        | 110 ms                             | 163.5 ms                                                         | 48.7 s                                                         |

| XC7VH870T (SSI)  | 110 ms                             | 74.3 ms                                                          | 10.2 s                                                         |

| XC7VX980T        | 110 ms                             | 213.3 ms                                                         | 82.6 s                                                         |

| XC7VX1140T (SSI) | 110 ms                             | 74.3 ms                                                          | 10.2 s                                                         |

Table 2-3: Maximum Start-Up Latency at ICAP F<sub>Max</sub> (Cont'd)

| Device          | Boot Time at<br>ICAP F <sub>Max</sub> | Initialization Time at ICAP<br>F <sub>Max</sub> (Repair/Replace) | Initialization Time at ICAP F <sub>Max</sub> (Enhanced Repair) |

|-----------------|---------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|

| XC7V2000T (SSI) | 110 ms                                | 95.4 ms                                                          | 16.7 s                                                         |

| XC7Z007S        | 110 ms                                | 12.2 ms                                                          | 1.5 s                                                          |

| XC7Z012S        | 110 ms                                | 21.7 ms                                                          | 2.6 s                                                          |

| XC7Z014S        | 110 ms                                | 24.2 ms                                                          | 2.9 s                                                          |

| XC7Z010         | 110 ms                                | 12.2 ms                                                          | 1.5 s                                                          |

| XC7Z015         | 110 ms                                | 21.7 ms                                                          | 2.6 s                                                          |

| XC7Z020         | 110 ms                                | 24.2 ms                                                          | 2.9 s                                                          |

| XC7Z030         | 110 ms                                | 34.1 ms                                                          | 4.1 s                                                          |

| XC7Z035         | 110 ms                                | 82.0 ms                                                          | 11.8 s                                                         |

| XC7Z045         | 110 ms                                | 82.0 ms                                                          | 11.8 s                                                         |

| XC7Z100         | 110 ms                                | 103.4 ms                                                         | 19.6 s                                                         |

| XC7S6           | 110 ms                                | 3.8 ms                                                           | 1.0 s                                                          |

| XC7S15          | 110 ms                                | 3.8 ms                                                           | 1.0 s                                                          |

| XC7S25          | 110 ms                                | 8.5 ms                                                           | 1.0 s                                                          |

| XC7S50          | 110 ms                                | 13.8 ms                                                          | 1.7 s                                                          |

| XC7S75          | 110 ms                                | 23.8 ms                                                          | 2.9 s                                                          |

| XC7S100         | 110 ms                                | 23.8 ms                                                          | 2.9 s                                                          |

The start-up latency is the sum of the boot and initialization latency, using the correct column of initialization latency data for the selected correction mode. The start-up latency at the actual frequency of operation can be estimated using data from Table 2-3 and Equation 2-1.

$$StartUpLatency_{ACTUAL} = StartUpLatency_{ICAP\_F_{Max}} \cdot \left[ \frac{ICAP\_F_{Max}}{Frequency_{ACTUAL}} \right] \qquad \qquad \textit{Equation 2-1}$$

## **Error Detection Latency**

Error detection latency is the major component of the total error mitigation latency. Error detection latency is a function of the FPGA size (frame count) and the solution clock frequency. It is also a function of the type of error and the relative position of the error with respect to the position of the silicon readback process. Table 2-4 illustrates full device scan times.

Table 2-4: Maximum Device Scan Times at ICAP F<sub>Max</sub>

| Device  | Scan Time at ICAP F <sub>Max</sub> |

|---------|------------------------------------|

| XC7A12T | 2.6 ms                             |

| XC7A15T | 4.6 ms                             |

| XC7A25T | 2.6 ms                             |

Table 2-4: Maximum Device Scan Times at ICAP F<sub>Max</sub> (Cont'd)

| Device           | Scan Time at ICAP F <sub>Max</sub> |

|------------------|------------------------------------|

| XC7A35T          | 4.6 ms                             |

| XC7A50T          | 4.6 ms                             |

| XC7A75T          | 8.0 ms                             |

| XC7A100T         | 8.0 ms                             |

| XC7A200T         | 18.3 ms                            |

| XC7K70T          | 5.9 ms                             |

| XC7K160T         | 12.9 ms                            |

| XC7K325T         | 23.5 ms                            |

| XC7K355T         | 26.5 ms                            |

| XC7K410T         | 30.3 ms                            |

| XC7K420T         | 35.3 ms                            |

| XC7K480T         | 35.3 ms                            |

| XC7VX330T        | 25.6 ms                            |

| XC7VX415T        | 32.5 ms                            |

| XC7VX485T        | 38.3 ms                            |

| XC7VX550T        | 54.1 ms                            |

| XC7VH580T (SSI)  | 24.6 ms                            |

| XC7V585T         | 41.2 ms                            |

| XC7VX690T        | 54.1 ms                            |

| XC7VH870T (SSI)  | 24.6 ms                            |

| XC7VX980T        | 70.7 ms                            |

| XC7VX1140T (SSI) | 24.6 ms                            |

| XC7V2000T (SSI)  | 31.6 ms                            |

| XC7Z007S         | 4.0 ms                             |

| XC7Z012S         | 7.2 ms                             |

| XC7Z014S         | 8.0 ms                             |

| XC7Z010          | 4.0 ms                             |

| XC7Z015          | 7.2 ms                             |

| XC7Z020          | 8.0 ms                             |

| XC7Z030          | 11.3 ms                            |

| XC7Z035          | 27.2 ms                            |

| XC7Z045          | 27.2 ms                            |

| XC7Z100          | 34.3 ms                            |

| XC7S6            | 1.3 ms                             |

| XC7S15           | 1.3 ms                             |

Table 2-4: Maximum Device Scan Times at ICAP F<sub>Max</sub> (Cont'd)

| Device  | Scan Time at ICAP F <sub>Max</sub> |

|---------|------------------------------------|

| XC7S25  | 2.6 ms                             |

| XC7S50  | 4.6 ms                             |

| XC7S75  | 8.0 ms                             |

| XC7S100 | 8.0 ms                             |

The device scan time for the target device, at the actual frequency of operation, can be estimated using data from Table 2-4 and Equation 2-2.

$$ScanTime_{ACTUAL} = ScanTime_{ICAP\_F_{Max}} \cdot \left[ \frac{ICAP\_F_{Max}}{Frequency_{ACTUAL}} \right]$$

Equation 2-2

The error detection latency can be bounded as follows:

- Absolute minimum error detection latency is effectively zero.

- Average error detection latency for detection by ECC is 0.5 × Scan Time<sub>ACTUAL</sub>

- Maximum error detection latency for detection by ECC is Scan Time<sub>ACTUAL</sub>

- Absolute maximum error detection latency for detection by CRC alone is  $2.0 \times Scan$   $Time_{ACTUAL}$

The frame-based ECC method used always detects single, double, triple, and all odd-count bit errors in a frame. The remaining error types are usually detected by the frame-based ECC method as well. It is rare to encounter an error that defeats the ECC and is detected by CRC alone.

#### **Error Correction Latency**

After detecting an error, the solution attempts correction. Errors are correctable depending on the selected correction mode and error type. Table 2-5 and Table 2-6 provide error correction latency for a configuration frame upset, assuming no throttling on the Monitor Interface.

Table 2-5: Non-SSI: Max Error Correction Latency (100 MHz) No Throttling on Monitor Interface

| Correction<br>Mode | Errors in Frame (Correctability)         | Error Correction State at ICAP_F <sub>Max</sub> |

|--------------------|------------------------------------------|-------------------------------------------------|

| Popair             | 1-bit (Correctable)                      | 610 μs                                          |

| Repair             | 2-bit (Uncorrectable)                    | 25 μs                                           |

|                    | 1-bit (Correctable)                      | 610 µs                                          |

| Enhanced Repair    | 2-bit (Correctable)                      | 18,790 μs                                       |

|                    | 2-bit (Uncorrectable)                    | 9,110 μs                                        |

|                    | BFR <sup>(1)</sup> -only (Uncorrectable) | 10 μs                                           |

| Replace            | Any (Correctable)                        | 830 µs                                          |

| Any                | CRC-only (Uncorrectable)                 | 10 μs                                           |

#### **Notes:**

Table 2-6: SSI: Max Error Correction Latency (70 MHz) No Throttling on Monitor Interface

| Correction<br>Mode | Errors in Frame (Correctability)         | Error Correction State at ICAP_F <sub>Max</sub> |

|--------------------|------------------------------------------|-------------------------------------------------|

| Repair             | 1-bit (Correctable)                      | 915 μs                                          |

| Керап              | 2-bit (Uncorrectable)                    | 70 µs                                           |

|                    | 1-bit (Correctable)                      | 910 μs                                          |

| Enhanced Penair    | 2-bit (Correctable)                      | 26,900 μs                                       |

| Enhanced Repair    | 2-bit (Uncorrectable)                    | 13,010 μs                                       |

|                    | BFR <sup>(1)</sup> -only (Uncorrectable) | 10 μs                                           |

| Replace            | Any (Correctable)                        | 1,220 µs                                        |

| Any                | CRC-only (Uncorrectable)                 | 10 μs                                           |

#### Notes:

The error correction latency at the actual frequency of operation can be estimated using data from Table 2-5 and Equation 2-3.

$$CorrectionLatency_{ACTUAL} = CorrectionLatency_{ICAP\_F_{Max}} \cdot \left[ \frac{ICAP\_F_{Max}}{Frequency_{ACTUAL}} \right] \quad \textit{Equation 2-3}$$

<sup>1.</sup> BFR is an error condition due to a multi-bit upset in an enhanced repair checksum stored in block RAM.

<sup>1.</sup> BFR is an error condition due to a multi-bit upset in an enhanced repair checksum stored in block RAM.

#### **Error Classification Latency**

After attempting correction of an error, the solution classifies the error. The classification result depends on the correction mode, error type, error location, and selected classification mode. Table 2-7 and Table 2-8 provide error classification latency for a configuration frame upset, assuming no throttling on the Monitor Interface.

Table 2-7: Non-SSI: Max Error Classification Latency (100 MHz) No Throttling on Monitor Interface

| Correction<br>Mode | Errors in Frame (Correctability) | Classification<br>Mode | Error Classification State at ICAP_F <sub>Max</sub> |

|--------------------|----------------------------------|------------------------|-----------------------------------------------------|

| Any                | Correctable                      | Enabled                | 750 μs                                              |

| Any                | Uncorrectable                    | Disabled               | 10 μs                                               |

| Any                | Uncorrectable                    | Any                    | 10 μs                                               |

Table 2-8: SSI: Max Error Classification Latency (70 MHz) No Throttling on Monitor Interface

| Correction<br>Mode | Errors in Frame<br>(Correctability) | Classification<br>Mode | Error Classification State at ICAP_F <sub>Max</sub> |

|--------------------|-------------------------------------|------------------------|-----------------------------------------------------|

| Any                | Correctable                         | Enabled                | 1,090 μs                                            |

| Any                | Uncorrectable                       | Disabled               | 10 μs                                               |

| Any                | Uncorrectable                       | Any                    | 10 μs                                               |

The error classification latency at the actual frequency of operation can be estimated using data from Table 2-7 and Equation 2-4.

$$ClassificationLatency_{ACTUAL} = ClassificationLatency_{ICAP\_F_{Max}} \cdot \left[ \frac{ICAP\_F_{Max}}{Frequency_{ACTUAL}} \right] \quad \textit{Equation 2-4}$$

# Sources of Additional Latency

It is highly desirable to avoid throttling on the Monitor Interface, because it increases the total error mitigation latency:

- After an attempted error correction, but before exiting the error correction state (at

which time the correctable status flag is updated), the controller issues a detection and

correction report through the Monitor Interface. If the MON Shim transmit FIFO

becomes full during this report generation, the controller dwells in this state until it has

written the entire report into the MON Shim transmit FIFO. When this happens, the

error correction latency increases.

- After classifying an error, but before exiting the error classification state (at which time

the essential status flag is updated), the controller issues a classification report through

the Monitor Interface. If the MON Shim transmit FIFO becomes full during this report

generation, the controller dwells in this state until it has written the entire report into

the MON Shim transmit FIFO. When this happens, the error classification latency

increases.

The approaches to completely eliminate the potential bottleneck are to remove the MON Shim and leave the Monitor Interface unused, or use the Monitor Interface with a peripheral that never signals a buffer full condition. In the event the Monitor Interface is unused, the Status Interface remains available for monitoring activity.

For peripherals where the potential bottleneck is a concern, it can be mitigated. This is accomplished by adjusting the transmit FIFO size to accommodate the longest burst of status messages that are anticipated so that the transmit FIFO never goes full during error mitigation.

If a transmit FIFO full condition does occur, the increase in the total error mitigation latency is roughly estimated as shown in Equation 2-5.

$$Additional Latency = \frac{Message Length - Buffer Depth}{Transmission Rate}$$

Equation 2-5

In Equation 2-5, MessageLength-BufferDepth is in message bytes, and the Transmission Rate is in bytes per unit of time.

# Sample Latency Estimation

The first sample estimation illustrates the calculation of error mitigation latency for a single-bit error by the solution implemented in an XC7K325T device with a 66 MHz clock. The solution is configured for error correction by repair, with error classification disabled. The initial assumption is that no throttling occurs on the Monitor Interface.

$$DetectionLatency = 0.5 \cdot ScanTime_{ACTUAL} = 0.5 \cdot 23.5ms \cdot \left[\frac{100MHz}{66MHz}\right] = 17.803ms \quad \textit{Equation 2-6}$$

$$CorrectionLatency = 610\mu s \cdot \left[\frac{100MHz}{66MHz}\right] = 0.924ms \quad \textit{Equation 2-7}$$

$$ClassificationLatency = 10\mu s \cdot \left[\frac{100MHz}{66MHz}\right] = 0.015ms \quad \textit{Equation 2-8}$$

$$MitigationLatency = 17.803ms + 0.924ms + 0.015ms = 18.742ms \quad \textit{Equation 2-9}$$

The second sample estimation illustrates the calculation of error mitigation latency for a two-bit error by the solution implemented in an XC7K325T device with a 66 MHz clock. The solution is configured for error correction by replace, with error classification enabled. Again, it is assumed that no throttling occurs on the Monitor Interface.

$$DetectionLatency = 0.5 \cdot ScanTime_{ACTUAL} = 0.5 \cdot 23.5ms \cdot \left[\frac{100MHz}{66MHz}\right] = 17.803ms \; Equation \; 2-10$$

$$CorrectionLatency = 830\mu s \cdot \left[\frac{100MHz}{66MHz}\right] = 1.258ms \qquad Equation \; 2-11$$

$$ClassificationLatency = 750\mu s \cdot \left[\frac{100MHz}{66MHz}\right] = 1.136ms \qquad Equation \; 2-12$$

MitigationLatency = 17.803ms + 1.258ms + 1.136ms = 20.197ms

Equation 2-13

The final sample estimation illustrates an assessment of the additional latency that would result from throttling on the Monitor Interface. Assume the message length in both the first and second samples is approximately 80 bytes, but the buffer depth of the MON Shim is 32 bytes. Further, the MON Shim has been modified to raise the bit rate from 9600 baud to 460800 baud. The standard 8-N-1 protocol used requires 10 bit times on the serial link to transmit a 1-byte payload:

$$Additional Latency = \frac{80 bytes - 32 bytes}{\left[\frac{460800 bittimes}{s} \cdot \frac{byte}{10 bittimes} \cdot \frac{s}{1000 ms}\right]} = 1.042 ms$$

Equation 2-14

This result illustrates that the additional latency resulting from throttling on the Monitor Interface can become significant, especially when the data transmission is serialized and the data rate is low.

# **Throughput**

The throughput metrics of the SEM Controller are not specified.

#### **Power**

The power metrics of the SEM Controller are not specified.

# **Resource Utilization**

Resource utilization metrics for the SEM Controller are derived from post-synthesis reports and are for budgetary purposes only. Actual resource utilization might vary.

Table 2-9: Resource Utilization for Zyng-7000 Devices (1)(2)

| Device                   | IP Core Configuration                        | LUTs | FFs | I/Os | Block RAMs         |

|--------------------------|----------------------------------------------|------|-----|------|--------------------|

| Zynq-7000<br>All Devices | Complete solution with no optional features  | 509  | 361 | 11   | 3 RAMB18           |

| Zynq-7000<br>XC7Z007S    | Complete solution with all optional features | 877  | 673 | 56   | 3 RAMB18, 2 RAMB36 |

| Zynq-7000<br>XC7Z012S    | Complete solution with all optional features | 912  | 674 | 56   | 3 RAMB18, 3 RAMB36 |

| Zynq-7000<br>XC7Z014S    | Complete solution with all optional features | 912  | 674 | 56   | 3 RAMB18, 3 RAMB36 |

| Zynq-7000<br>XC7Z010     | Complete solution with all optional features | 863  | 681 | 56   | 3 RAMB18, 2 RAMB36 |

Table 2-9: Resource Utilization for Zynq-7000 Devices (1)(2) (Cont'd)

| Device               | IP Core Configuration                        | LUTs  | FFs | I/Os | Block RAMs          |

|----------------------|----------------------------------------------|-------|-----|------|---------------------|

| Zynq-7000<br>XC7Z015 | Complete solution with all optional features | 834   | 682 | 58   | 3 RAMB18, 3 RAMB36  |

| Zynq-7000<br>XC7Z020 | Complete solution with all optional features | 838   | 682 | 56   | 3 RAMB18, 3 RAMB36  |

| Zynq-7000<br>XC7Z030 | Complete solution with all optional features | 887   | 683 | 56   | 3 RAMB18, 5 RAMB36  |

| Zynq-7000<br>XC7Z035 | Complete solution with all optional features | 994   | 696 | 56   | 3 RAMB18, 10 RAMB36 |

| Zynq-7000<br>XC7Z045 | Complete solution with all optional features | 994   | 696 | 56   | 3 RAMB18, 10 RAMB36 |

| Zynq-7000<br>XC7Z100 | Complete solution with all optional features | 1,065 | 696 | 56   | 3 RAMB18, 13 RAMB36 |

- 1. The complete solution is the SEM Controller and the example design, which are intended to be used together.

- 2. The Error Injection Interface is connected to I/Os; use of logic debug IP (VIO) increases LUTs/FFs but decreases I/Os.

Table 2-10: Resource Utilization for Kintex-7 Devices<sup>(1)(2)</sup>

| Device                  | IP Core Configuration                        | LUTs  | FFs | I/Os | Block RAMs          |

|-------------------------|----------------------------------------------|-------|-----|------|---------------------|

| Kintex-7<br>All Devices | Complete solution with no optional features  | 511   | 361 | 11   | 3 RAMB18            |

| Kintex-7<br>XC7K70T     | Complete solution with all optional features | 849   | 682 | 56   | 3 RAMB18, 3 RAMB36  |

| Kintex-7<br>XC7K160T    | Complete solution with all optional features | 887   | 683 | 56   | 3 RAMB18, 5 RAMB36  |

| Kintex-7<br>XC7K325T    | Complete solution with all optional features | 991   | 686 | 56   | 3 RAMB18, 9 RAMB36  |

| Kintex-7<br>XC7K355T    | Complete solution with all optional features | 994   | 696 | 56   | 3 RAMB18, 10 RAMB36 |

| Kintex-7<br>XC7K410T    | Complete solution with all optional features | 1,028 | 696 | 56   | 3 RAMB18, 11 RAMB36 |

| Kintex-7<br>XC7K420T    | Complete solution with all optional features | 1,065 | 696 | 56   | 3 RAMB18, 13 RAMB36 |

| Kintex-7<br>XC7K480T    | Complete solution with all optional features | 1,065 | 696 | 56   | 3 RAMB18, 13 RAMB36 |

Table 2-10: Resource Utilization for Kintex-7 Devices (1)(2) (Cont'd)

| Device                    | IP Core Configuration | LUTs             | FFs | I/Os | Block RAMs |  |  |  |

|---------------------------|-----------------------|------------------|-----|------|------------|--|--|--|

| Kintex-7 Low<br>Voltage,  |                       |                  |     |      |            |  |  |  |

| Kintex-7Q,                | Camara a Kintan 7     |                  |     |      |            |  |  |  |

| Kintex-7Q<br>Low Voltage, |                       | Same as Kintex-7 |     |      |            |  |  |  |

| All Devices               |                       |                  |     |      |            |  |  |  |

- 1. The complete solution is the SEM Controller and the example design, which are intended to be used together.

- 2. The Error Injection Interface is connected to I/Os; use of logic debug IP (VIO) increases LUTs/FFs but decreases I/Os.

Table 2-11: Resource Utilization for Virtex-7 Devices (Non-SSI)<sup>(1)(2)</sup>

| Device                   | IP Core Configuration                        | LUTs  | FFs | I/Os | Block RAMs          |  |  |

|--------------------------|----------------------------------------------|-------|-----|------|---------------------|--|--|

| Virtex-7<br>All Devices  | Complete solution with no optional features  | 510   | 361 | 11   | 3 RAMB18            |  |  |

| Virtex-7<br>XC7VX330T    | Complete solution with all optional features | 996   | 696 | 56   | 3 RAMB18, 10 RAMB36 |  |  |

| Virtex-7<br>XC7VX415T    | Complete solution with all optional features | 1,065 | 696 | 56   | 3 RAMB18, 12 RAMB36 |  |  |

| Virtex-7<br>XC7VX485T    | Complete solution with all optional features | 1,101 | 697 | 56   | 3 RAMB18, 14 RAMB36 |  |  |

| Virtex-7<br>XC7VX550T    | Complete solution with all optional features | 1,218 | 691 | 56   | 3 RAMB18, 20 RAMB36 |  |  |

| Virtex-7<br>XC7V585T     | Complete solution with all optional features | 1,073 | 698 | 56   | 3 RAMB18, 15 RAMB36 |  |  |

| Virtex-7<br>XC7VX690T    | Complete solution with all optional features | 1,218 | 691 | 56   | 3 RAMB18, 20 RAMB36 |  |  |

| Virtex-7<br>XC7VX980T    | Complete solution with all optional features | 1,366 | 692 | 56   | 3 RAMB18, 26 RAMB36 |  |  |

| Virtex-7Q<br>All Devices | Same as Virtex-7                             |       |     |      |                     |  |  |

- 1. The complete solution is the SEM Controller and the example design, which are intended to be used together.

- 2. The Error Injection Interface is connected to I/Os; use of logic debug IP (VIO) increases LUTs/FFs but decreases I/Os.

Table 2-12: Resource Utilization for Virtex-7 Devices (SSI)(1)(2)

| Device                | IP Core Configuration                        | LUTs  | FFs   | I/Os | Block RAMs          |

|-----------------------|----------------------------------------------|-------|-------|------|---------------------|

| Virtex-7<br>XC7VH580T | Complete solution with no optional features  | 1,394 | 980   | 19   | 7 RAMB18            |

| Virtex-7<br>XC7VH580T | Complete solution with all optional features | 2,410 | 1,692 | 64   | 7 RAMB18, 18 RAMB36 |

Table 2-12: Resource Utilization for Virtex-7 Devices (SSI)<sup>(1)(2)</sup> (Cont'd)

| Device                    | IP Core Configuration                        | LUTs  | FFs   | I/Os | Block RAMs           |  |

|---------------------------|----------------------------------------------|-------|-------|------|----------------------|--|

| Virtex-7<br>XC7VH870T     | Complete solution with no optional features  | 1,853 | 1,289 | 27   | 10 RAMB18            |  |

| Virtex-7<br>XC7VH870T     | Complete solution with all optional features | 3,245 | 2,230 | 72   | 10 RAMB18, 27 RAMB36 |  |

| Virtex-7<br>XC7VX1140T    | Complete solution with no optional features  | 2,245 | 1,598 | 35   | 13 RAMB18            |  |

| Virtex-7<br>XC7VX1140T    | Complete solution with all optional features | 4,032 | 2,768 | 80   | 13 RAMB18, 36 RAMB36 |  |

| Virtex-7<br>XC7V2000T     | Complete solution with no optional features  | 2,256 | 1,598 | 35   | 13 RAMB18            |  |

| Virtex-7<br>XC7V2000T     | Complete solution with all optional features | 4,342 | 2,808 | 80   | 13 RAMB18, 48 RAMB36 |  |

| Virtex-7Q,<br>All Devices | Same as Virtex-7                             |       |       |      |                      |  |

- 1. The complete solution is the SEM Controller and the example design, which are intended to be used together.

- 2. The Error Injection Interface is connected to I/Os; use of logic debug IP (VIO) increases LUTs/FFs but decreases I/Os.

Table 2-13: Resource Utilization for Artix-7 Devices (1)(2)

| Device                 | IP Core Configuration                        | LUTs | FFs | I/Os | Block RAMs         |

|------------------------|----------------------------------------------|------|-----|------|--------------------|

| Artix-7<br>All Devices | Complete solution with no optional features  | 512  | 361 | 11   | 3 RAMB18           |

| Artix-7<br>XC7A12T     | Complete solution with all optional features | 877  | 673 | 56   | 3 RAMB18, 2 RAMB36 |

| Artix-7<br>XC7A15T     | Complete solution with all optional features | 800  | 681 | 56   | 3 RAMB18, 2 RAMB36 |

| Artix-7<br>XC7A25T     | Complete solution with all optional features | 877  | 673 | 56   | 3 RAMB18, 2 RAMB36 |

| Artix-7<br>XC7A35T     | Complete solution with all optional features | 802  | 681 | 56   | 3 RAMB18, 2 RAMB36 |

| Artix-7<br>XC7A50T     | Complete solution with all optional features | 800  | 681 | 56   | 3 RAMB18, 2 RAMB36 |

| Artix-7<br>XC7A75T     | Complete solution with all optional features | 837  | 682 | 56   | 3 RAMB18, 3 RAMB36 |

| Artix-7<br>XC7A100T    | Complete solution with all optional features | 837  | 682 | 56   | 3 RAMB18, 3 RAMB36 |

| Artix-7<br>XC7A200T    | Complete solution with all optional features | 919  | 681 | 56   | 3 RAMB18, 7 RAMB36 |

Table 2-13: Resource Utilization for Artix-7 Devices (1)(2) (Cont'd)

| Device                  | IP Core Configuration | LUTs | FFs | I/Os | Block RAMs |  |  |

|-------------------------|-----------------------|------|-----|------|------------|--|--|

| Artix-7 Low<br>Voltage, |                       |      |     |      |            |  |  |

| Artix-7A,               | Same as Artix-7       |      |     |      |            |  |  |

| Artix-7Q,               |                       |      |     |      |            |  |  |

| All Devices             |                       |      |     |      |            |  |  |

- 1. The complete solution is the SEM Controller and the example design, which are intended to be used together.

- 2. The Error Injection Interface is connected to I/Os; use of logic debug IP (VIO) increases LUTs/FFs but decreases I/Os.

Table 2-14: Resource Utilization for Spartan-7 Devices (1)(2)

| Device                   | IP Core Configuration                        | LUTs | FFs | I/Os | Block RAMs         |

|--------------------------|----------------------------------------------|------|-----|------|--------------------|

| Spartan-7<br>All Devices | Complete solution with no optional features  | 498  | 406 | 11   | 3 RAMB18           |

| Spartan-7<br>XC7S6       | Complete solution with all optional features | 842  | 673 | 56   | 3 RAMB18, 1 RAMB36 |

| Spartan-7<br>XC7S15      | Complete solution with all optional features | 842  | 673 | 56   | 3 RAMB18, 1 RAMB36 |

| Spartan-7<br>XC725       | Complete solution with no optional features  | 877  | 673 | 56   | 3 RAMB18, 2 RAMB36 |

| Spartan-7<br>XC7S50      | Complete solution with all optional features | 877  | 673 | 56   | 3 RAMB18, 2 RAMB36 |

| Spartan-7<br>XC7S75      | Complete solution with all optional features | 912  | 674 | 56   | 3 RAMB18, 3 RAMB36 |

| Spartan-7<br>XC7S100     | Complete solution with all optional features | 912  | 674 | 56   | 3 RAMB18, 3 RAMB36 |

#### Notes:

- 1. The complete solution is the SEM Controller and the example design, which are intended to be used together.

- 2. The Error Injection Interface is connected to I/Os; use of logic debug IP (VIO) increases LUTs/FFs but decreases I/Os.

# **Port Descriptions**

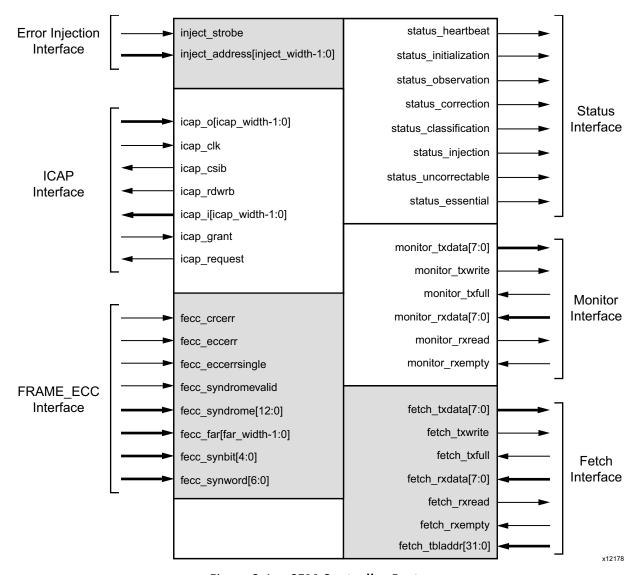

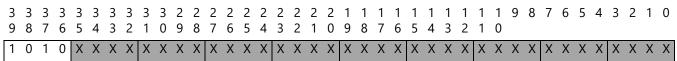

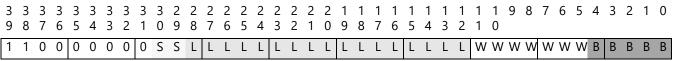

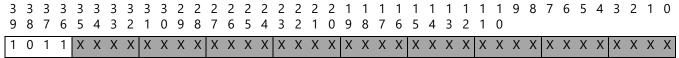

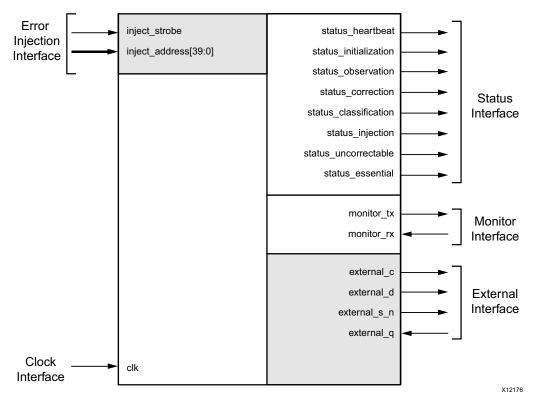

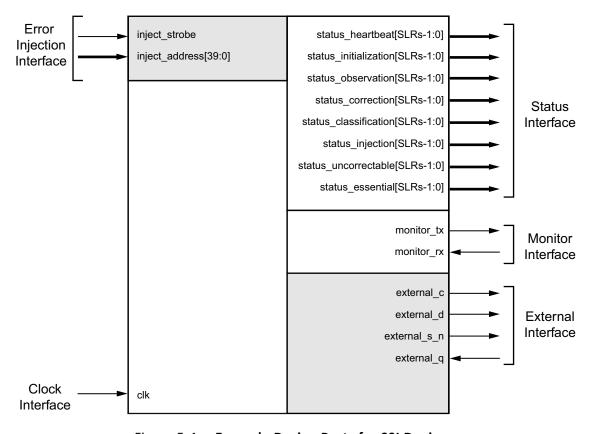

The SEM Controller is the kernel of the soft error mitigation solution. Figure 2-1 shows the SEM Controller ports. The ports are clustered into six groups. Shading indicates port groups that only exist in certain configurations.

Figure 2-1: SEM Controller Ports

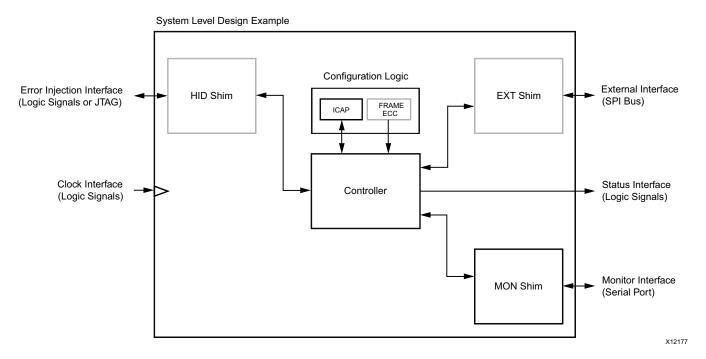

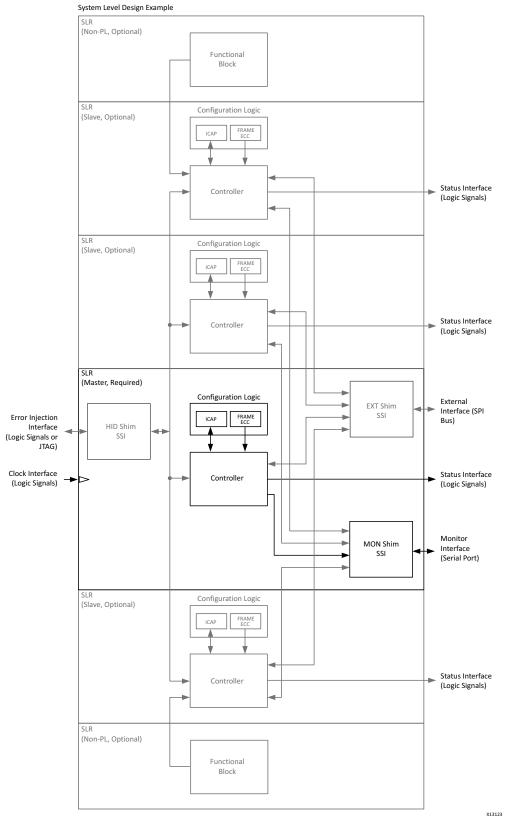

**TIP:** The system-level example design encapsulates the SEM Controller and various shims that serve to interface the Controller to other devices, as shown in Figure 5-1. The example design is not a reference design, but is an integral part of the total soft error mitigation solution. The SEM Controller ports shown in Figure 2-1 connect to the shims delivered in the example design. See Chapter 5, Example Design for more information on the delivered example design. See Port Descriptions in Chapter 5 for the system-level ports for the solution.

The SEM Controller has no reset input or output. It automatically initializes itself with an internal synchronous reset derived from the deassertion of the global GSR signal.

The SEM Controller is a fully synchronous design using <code>icap\_clk</code> as the single clock. All state elements are synchronous to the rising edge of this clock. As a result, all interfaces are also synchronous to the rising edge of this clock.

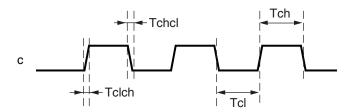

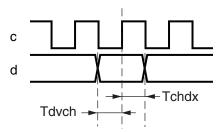

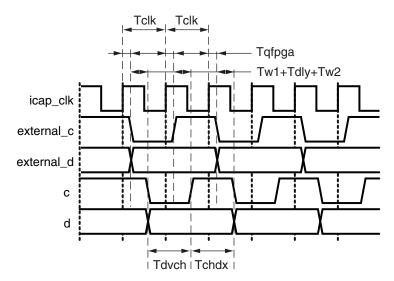

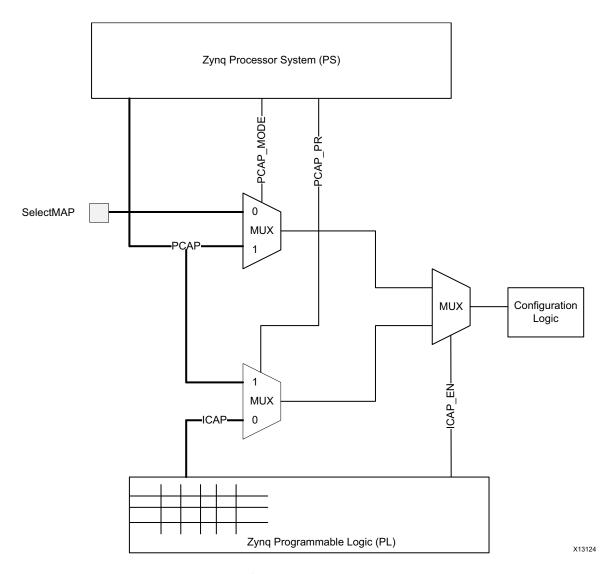

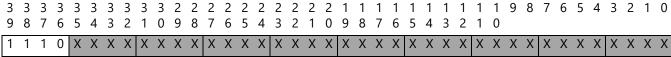

#### **ICAP** Interface

The ICAP Interface is a point-to-point connection between the SEM Controller and the ICAP primitive. The ICAP primitive enables read and write access to the registers inside the FPGA configuration system. The ICAP primitive and the behavior of the signals on this interface are described in the *7 Series FPGAs Configuration User Guide* (UG470) [Ref 1].

Table 2-15: ICAP Interface Signals

| Name                   | Sense | 1/0 | Description                                                                                                                                                                                                            |

|------------------------|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| icap_o[icap_width-1:0] | HIGH  | I   | Receives O output of ICAP. The variable icap_width is equal to 32.                                                                                                                                                     |

| icap_csib              | LOW   | 0   | Drives CSIB input of ICAP.                                                                                                                                                                                             |

| icap_rdwrb             | LOW   | 0   | Drives RDWRB input of ICAP.                                                                                                                                                                                            |

| icap_i[icap_width-1:0] | HIGH  | 0   | Drives I input of ICAP. The variable icap_width is equal to 32.                                                                                                                                                        |

| icap_clk               | EDGE  | I   | Receives the clock for the design. This same clock also must be applied to the CLK input of ICAP. The clock frequency must comply with the ICAP input clock requirements as specified in the target device data sheet. |

| icap_request           | HIGH  | 0   | This signal is reserved for future use. Leave this port OPEN.                                                                                                                                                          |

| icap_grant             | HIGH  | I   | Tie this port to VCC. Receives an ICAP initialization grant signal from the user. icap_grant can be used to hold off the controller initialization state.                                                              |

# **FRAME ECC Interface**

The FRAME\_ECC Interface is a point-to-point connection between the SEM Controller and the FRAME\_ECC primitive. The FRAME\_ECC primitive is an output-only primitive that provides a window into the soft error detection function in the FPGA configuration system. The FRAME\_ECC primitive and the behavior of the signals on this interface are described in Answer Record 54350.

**Table 2-16:** FRAME\_ECC Interface Signals

| Name                | Sense | 1/0 | Description                                  |

|---------------------|-------|-----|----------------------------------------------|

| fecc_crcerr         | HIGH  | I   | Receives CRCERROR output of FRAME_ECC.       |

| fecc_eccerr         | HIGH  | ı   | Receives ECCERROR output of FRAME_ECC.       |

| fecc_eccerrsingle   | HIGH  | I   | Receives ECCERRORSINGLE output of FRAME_ECC. |

| fecc_syndromevalid  | HIGH  | I   | Receives SYNDROMEVALID output of FRAME_ECC.  |

| fecc_syndrome[12:0] | HIGH  | I   | Receives SYNDROME output of FRAME_ECC.       |

| fecc_far[25:0]      | HIGH  | I   | Receives FAR output of FRAME_ECC.            |

Table 2-16: FRAME\_ECC Interface Signals (Cont'd)

| Name              | Sense | I/O | Description                           |

|-------------------|-------|-----|---------------------------------------|

| fecc_synbit[4:0]  | HIGH  | I   | Receives SYNBIT output of FRAME_ECC.  |

| fecc_synword[6:0] | HIGH  | I   | Receives SYNWORD output of FRAME_ECC. |

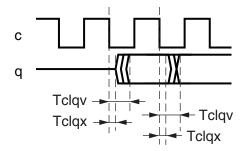

## **Status Interface**

The Status Interface provides a convenient set of decoded outputs that indicate, at a high level, what the controller is doing.

**Table 2-17:** Status Interface Signals

| Name                  | Sense | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

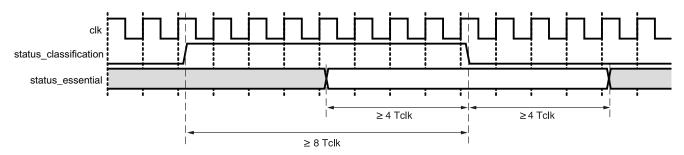

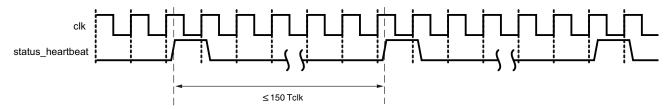

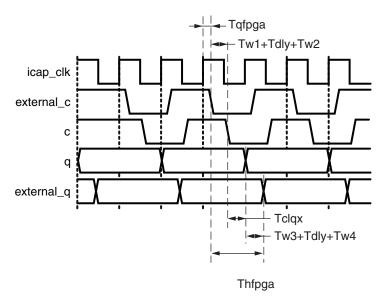

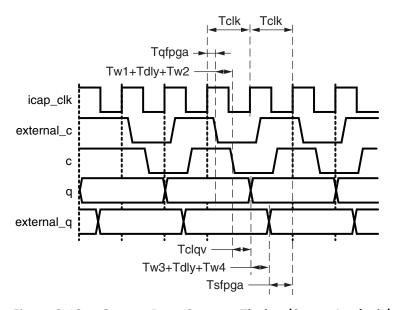

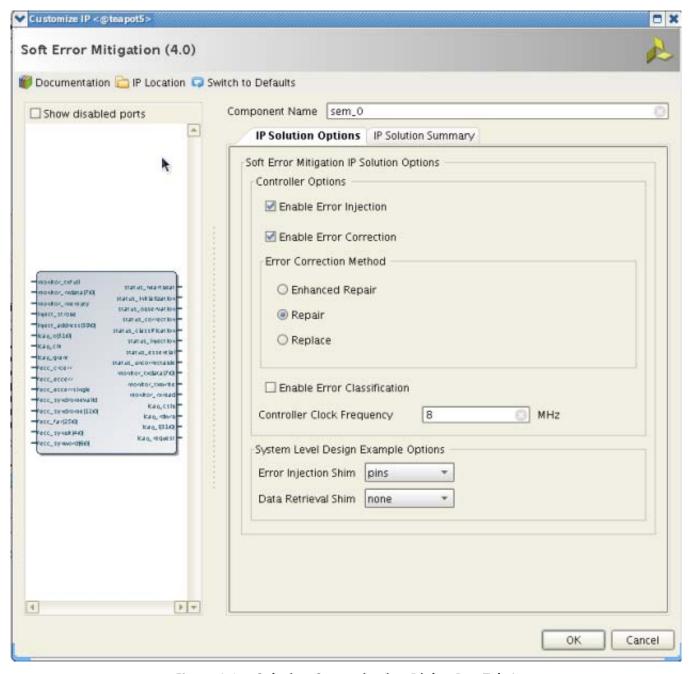

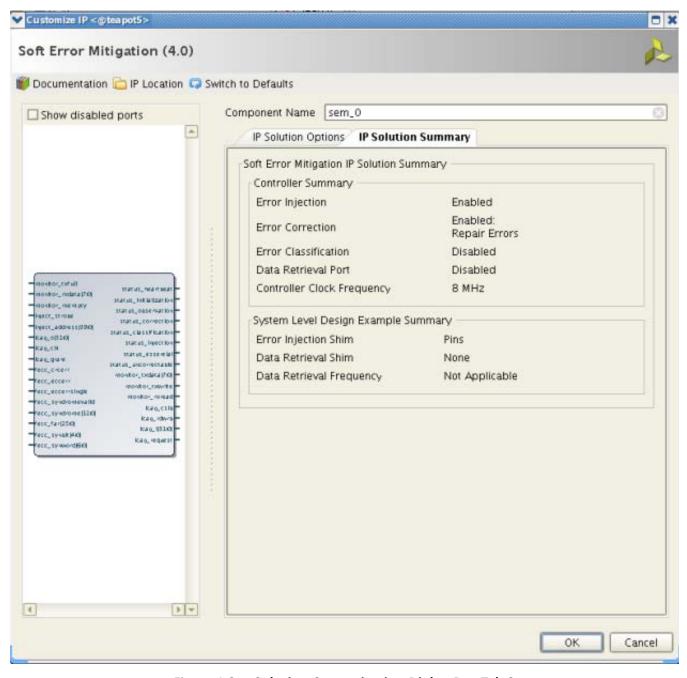

| status_heartbeat      | HIGH  | 0   | The heartbeat signal is active while status_observation is asserted. This output issues a single-cycle high pulse at least once every 150 clock cycles. This signal can be used to implement an external watchdog timer to detect "controller stop" scenarios that can occur if the controller or clock distribution is disabled by soft errors. When status_observation is deasserted, the behavior of the heartbeat signal is unspecified. |