# Quad Serial Gigabit Media Independent v3.3

# LogiCORE IP Product Guide

**Vivado Design Suite**

PG029 October 5, 2016

# **Table of Contents**

### **IP Facts**

| Chapter 1: Overview                                      |

|----------------------------------------------------------|

| System Overview                                          |

| Feature Summary                                          |

| Applications                                             |

| Licensing and Ordering Information 1                     |

| Chapter 2: Product Specification                         |

| Standards                                                |

| Performance                                              |

| Resource Utilization                                     |

| Port Descriptions                                        |

| Transceiver Control and Status Ports                     |

| Register Space 4                                         |

| Chapter 3: Designing with the Core                       |

| Design Guidelines6                                       |

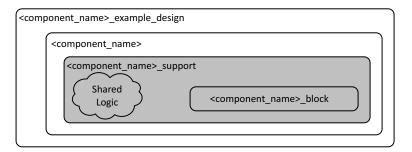

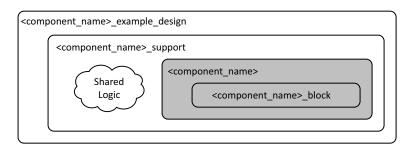

| Shared Logic                                             |

| Clocking 70                                              |

| Resets                                                   |

| Chapter 4: Using the Client Side GMII/MII Datapath       |

| Using the Encrypted Core Level Client-Side GMII/MII      |

| Additional Client-Side QSGMII Adaptation Logic           |

| Chapter 5: Using the Transceiver                         |

| Transceiver Logic                                        |

| Clock Sharing Across Multiple Cores with Transceivers 94 |

| Chapter 6: Design Flow Steps                             |

| Customizing and Generating the Core                      |

| Constraining the Core                                    |

| Simulation                                                                     |     |

|--------------------------------------------------------------------------------|-----|

| Synthesis and Implementation                                                   | 116 |

| Chapter 7: Example Design                                                      |     |

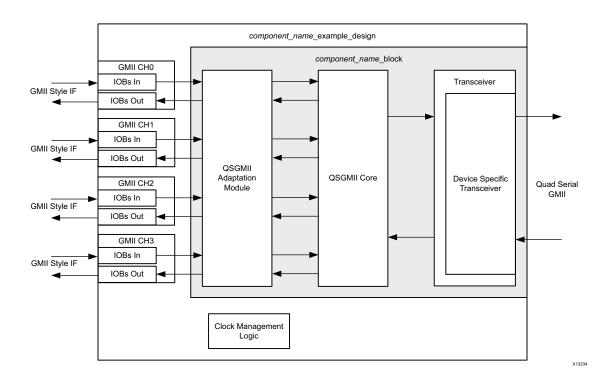

| Top-Level Example Design HDL                                                   | 118 |

| Support Level HDL                                                              | 119 |

| Block Level HDL                                                                | 120 |

| Transceiver Files for Zynq-7000 AP SoC, Virtex-7, Kintex-7, or Artix-7 Devices | 121 |

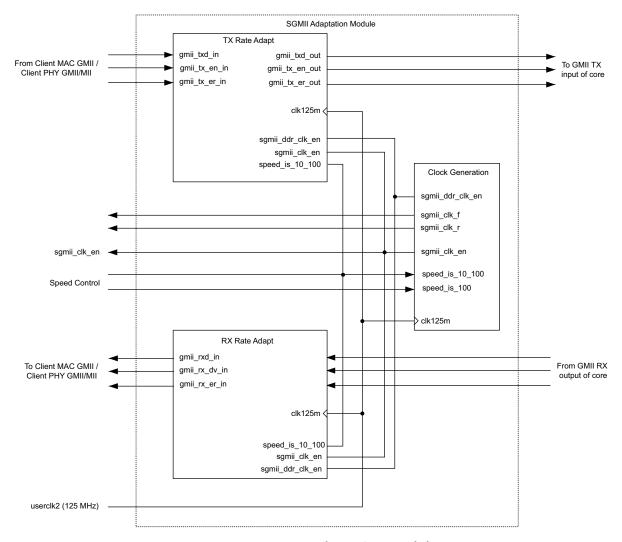

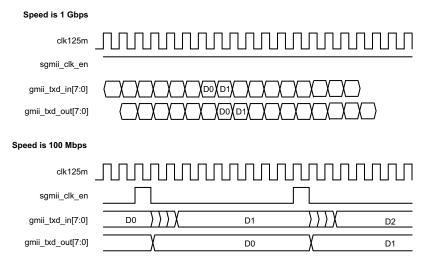

| QSGMII Adaptation Module                                                       | 122 |

| Chapter 8: Test Bench                                                          |     |

| Test Bench Functionality                                                       | 127 |

| Customizing the Test Bench                                                     | 128 |

| Appendix A: Verification, Compliance, and Interoperability                     |     |

| Simulation                                                                     | 130 |

| Hardware Testing                                                               | 130 |

| Compliance Testing                                                             | 130 |

| Appendix B: Migrating and Upgrading                                            |     |

| Migrating                                                                      | 131 |

| Upgrading in the Vivado Design Suite                                           | 132 |

| Appendix C: Implementing External GMII/MII                                     |     |

| External GMII Transmitter Logic                                                | 139 |

| External MII Transmitter Logic                                                 | 140 |

| External GMII/MII Receiver Logic                                               | 141 |

| Appendix D: Debugging                                                          |     |

| Finding Help on Xilinx.com                                                     | 143 |

| Debug Tools                                                                    | 145 |

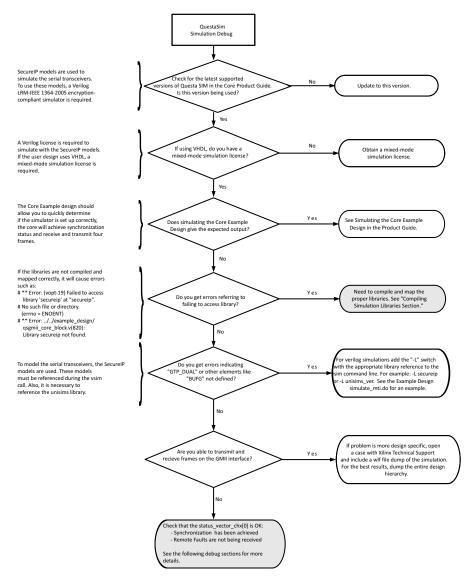

| Simulation Debug                                                               | 146 |

| Hardware Debug                                                                 | 147 |

| Appendix E: Additional Resources and Legal Notices                             |     |

| Xilinx Resources                                                               | 151 |

| References                                                                     | 151 |

| Specifications                                                                 | 152 |

| Revision History                                                               | 152 |

| Please Read: Important Legal Notices                                           | 154 |

# Introduction

The LogiCORE™ Quad Serial Gigabit Media Independent Interface (QSGMII) core provides a flexible solution for combining four Serial Gigabit Media Independent Interfaces (SGMII) into one 5 Gigabits per second (Gb/s) interface, to significantly reduce the number of inputs/ outputs (I/Os). This core supports Cisco QSGMII Specification Version 1.2 (EDCS-540123) [Ref 1].

# **Features**

- Integrated transceiver interface using a Zyng®-7000 All Programmable SoC, Virtex®-7, and Kintex®-7 device GTX transceiver

- Integrated transceiver interface using UltraScale+™ families, UltraScale™ architecture, and Virtex-7 FPGA GTH transceiver

- Integrated transceiver interface using Artix®-7 FPGA GTP transceiver

- Implements SGMII Adaptation to support 10/100/1000 operation for each port

- Transmitters of all ports transmit only /I1/ Idle ordered set

- Lane alignment based on K28.1 character detection

- Implements QSGMII K28.5 swapper on Port 0 transmit path

- Implements QSGMII K28.1 swapper on Port 0 receive path

- Implements receive link synchronization state machine

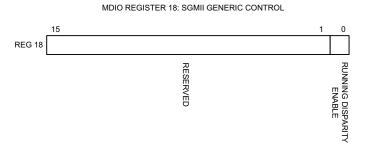

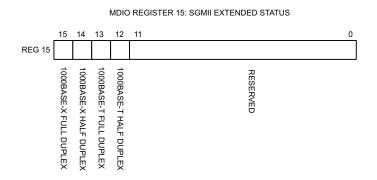

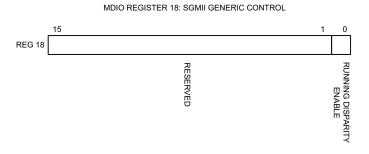

- Programmable Decoder running disparity checking for each port

Supports full duplex mode only

| LogiCORE IP Facts Table                   |                                                                             |  |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|

|                                           | Core Specifics                                                              |  |  |  |  |

| Supported<br>Device Family <sup>(1)</sup> | UltraScale+, UltraScale, Zynq-7000,<br>7 Series, Spartan 7                  |  |  |  |  |

| Supported User<br>Interfaces              | GMII/MII                                                                    |  |  |  |  |

| Resources                                 | See Table 2-1, Table 2-2, Table 2-3, and Table 2-4.                         |  |  |  |  |

|                                           | Provided with Core                                                          |  |  |  |  |

| Design Files Encrypted                    |                                                                             |  |  |  |  |

| Example Design VHDL an                    |                                                                             |  |  |  |  |

| Test Bench                                | Demonstration Test Bench in VHDL and Verilog                                |  |  |  |  |

| Constraints File                          | Xilinx Design Constraints (XDC)                                             |  |  |  |  |

| Simulation<br>Model                       | Verilog and VHDL                                                            |  |  |  |  |

| Supported<br>S/W Drivers                  | N/A                                                                         |  |  |  |  |

|                                           | Tested Design Flows <sup>(2)</sup>                                          |  |  |  |  |

| Design Entry                              | Vivado <sup>®</sup> Design Suite                                            |  |  |  |  |

| Simulation                                | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |  |  |  |

| Synthesis                                 | Vivado Synthesis                                                            |  |  |  |  |

|                                           | Support                                                                     |  |  |  |  |

| Provided b                                | y Xilinx at the <u>Xilinx Support web page</u>                              |  |  |  |  |

- 1. For a complete list of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

The QSGMII IP core is designed to reduce significantly the number of signals that are needed between multi port 10/100/1000 PHYs and Ethernet MAC. QSGMII needs two data signals, each operating at 5 Gb/s, to connect four instances of PHYs and Ethernet MAC.

# System Overview

The QSGMII core provides the functionality to implement the sublayers as specified by the Cisco QSGMII specification.

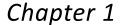

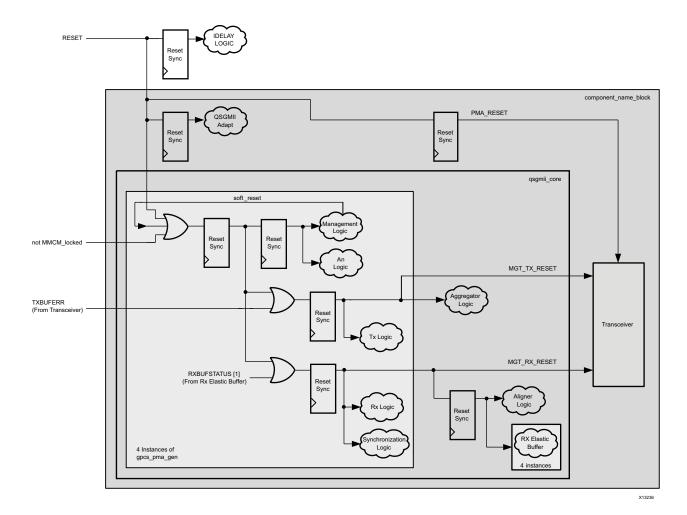

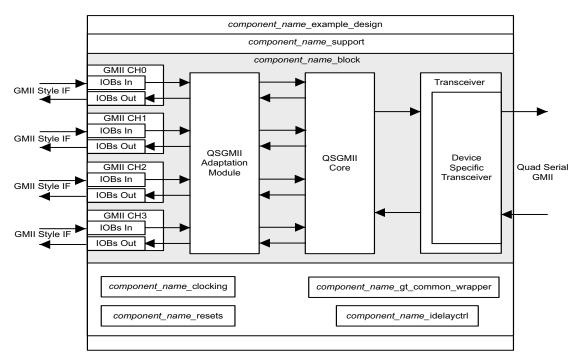

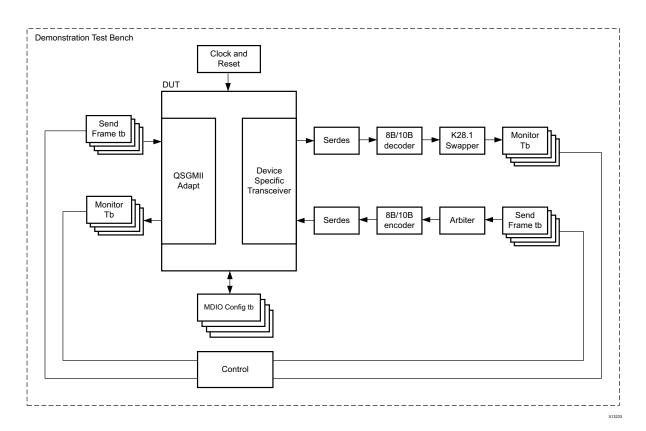

The QSGMII core interfaces to a device-specific transceiver. The transceiver provides some of the PCS functionality, such as 8B/10B encoding/decoding, Physical Medium Attachment (PMA) Serializer/Deserializer (SerDes), and clock recovery. Figure 1-1 illustrates the remaining PCS sublayer functionality and also shows the major functional blocks of the core.

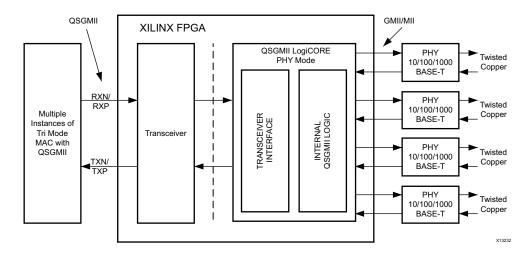

Figure 1-1: QSGMII System Overview

## **SGMII**

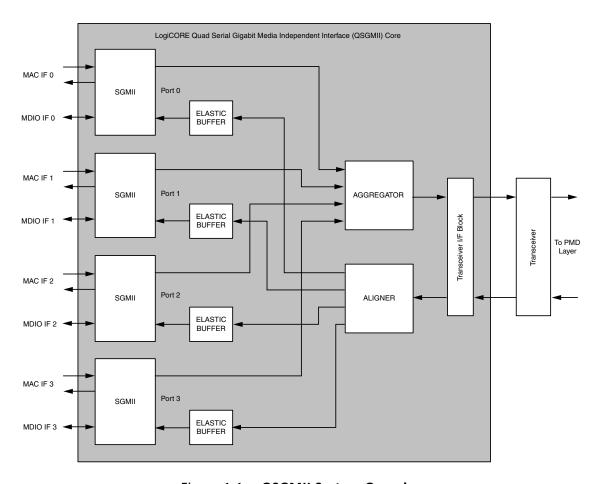

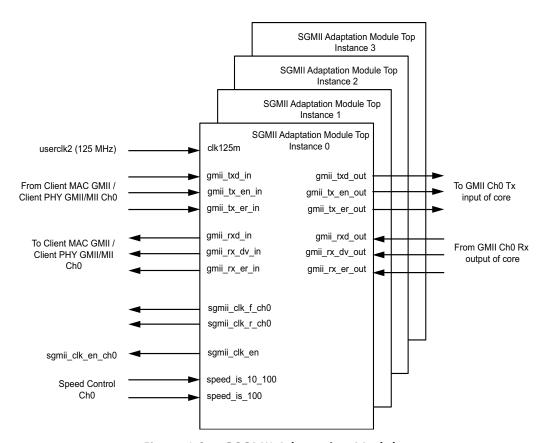

Figure 1-2 illustrates the sub-blocks of the SGMII module.

Figure 1-2: Functional Diagram of SGMII Block

#### GMII/MII Block

A client-side GMII is provided with the core, which can be used as an internal interface for connection to an embedded Media Access Controller (MAC) or other custom logic in MAC mode. In PHY mode, the GMII/MII can be routed to device Input Output Blocks (IOBs) to provide an external (off-device) GMII/MII.

Virtex®-7 devices support GMII at 3.3V or lower only in certain parts and packages. See the <u>Virtex-7 Family home page</u>. Zynq®-7000 All Programmable SoC, Kintex®-7, and Artix®-7 devices support GMII at 3.3V or lower.

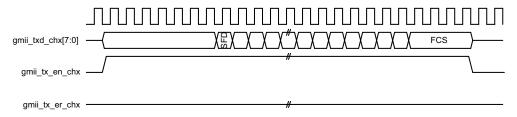

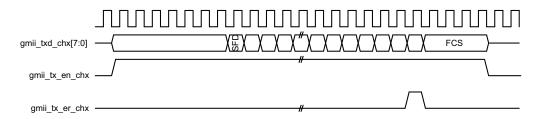

#### **PCS Transmit Engine**

The Physical Coding Sublayer (PCS) transmit engine converts the GMII data octets into a sequence of ordered sets by implementing the state diagrams of *IEEE 802.3-2008 Specification* [Ref 2] (Figures 36-5 and 36-6). The transmit engine transmits only /I1/ characters instead of /I2/, as described in the QSGMII specification.

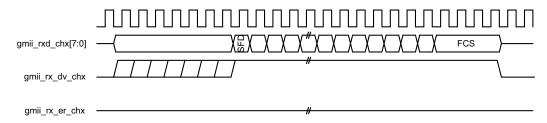

#### **PCS Receive Engine and Synchronization**

The synchronization process implements the state diagram of *IEEE 802.3-2008* (Figure 36-9). The PCS receive engine converts the sequence of ordered sets to GMII data octets by implementing the state diagrams of *IEEE 802.3-2008 Specification* [Ref 2] (Figures 36-7a and 36-7b). This module can be programmed to optionally consider disparity. Disparity checking is disabled by default.

#### **Optional Auto-Negotiation Block**

Clause 37 in the *IEEE 802.3-2008 Specification* [Ref 2] describes the Auto-Negotiation function that allows a device to advertise the modes of operation that it supports to a device at the remote end of a link segment (link partner), and to detect corresponding operational modes that the link partner might be advertising.

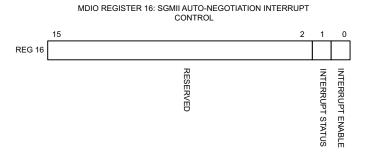

Auto-Negotiation is controlled and monitored through the PCS Management registers.

## **Optional PCS Management Registers**

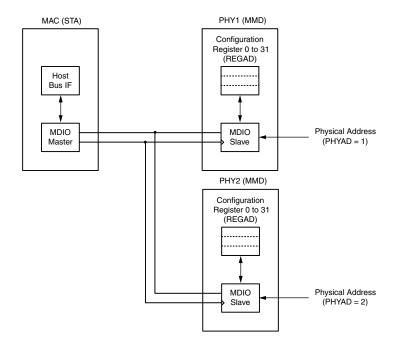

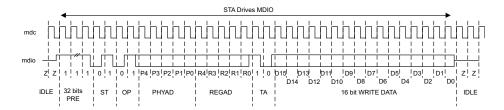

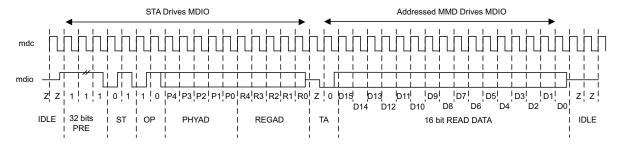

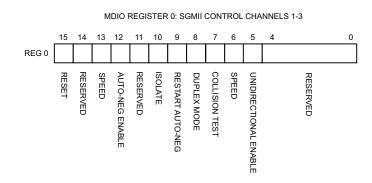

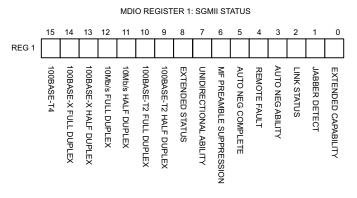

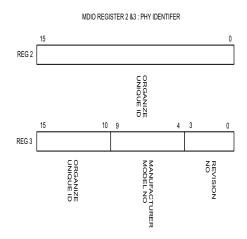

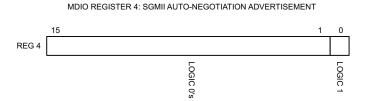

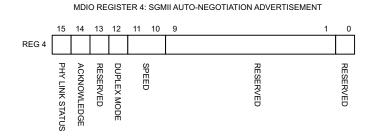

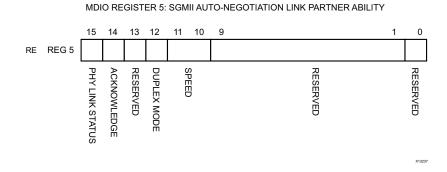

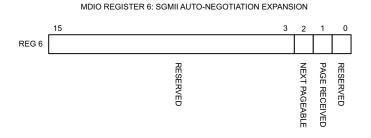

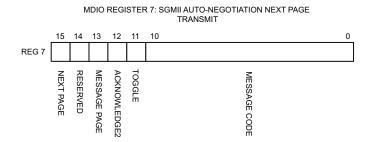

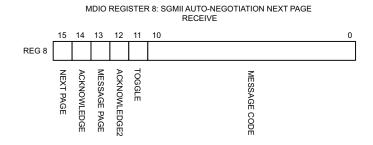

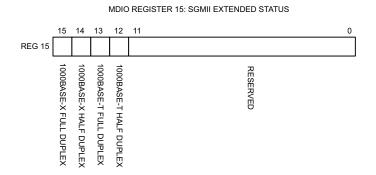

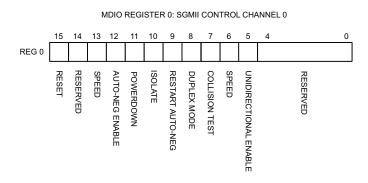

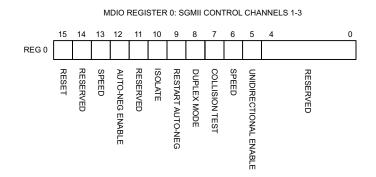

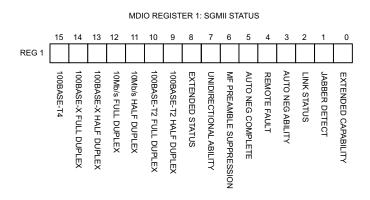

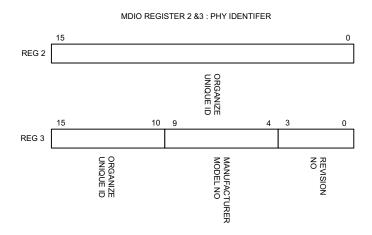

Configuration and status of the core, including access to and from the optional Auto-Negotiation function, uses the Management registers defined in clause 37 of the *IEEE 802.3-2008 Specification* [Ref 2]. These registers are accessed through the serial Management Data Input/Output Interface (MDIO), defined in clause 22 of the *IEEE 802.3-2008 Specification* [Ref 2], as if it were an externally connected PHY.

An additional configuration vector and status signal interface is provided to configure Base Control register (Register 0) and Auto-Negotiation Ability Advertisement register (Register 4).

# Aggregator

The Aggregator implements a portion of a modified transmit path diagram (Figure 1 of the QSGMII v1.2 specification). This module receives data and control from each instance of the SGMII module which is aggregated to 32-bit data and 4-bit control and transferred to Transceiver Interface block. The Aggregator also incorporates the K28.5 swapping function on port 0 that assists in port matching at the peer receiver end.

# **Aligner**

The Aligner receives 32 bits of data from the transceiver interface. Port 0 data can be received on any lane, so a search for the K28.1 character is done on all the lanes to start lane alignment. After a match for K28.1 is found in the octet boundary in the 32-bit data, that octet boundary becomes the start of arbitration and the octet assigned to port 0. The next octet is assigned to port 1 and so on. This module also swaps any K28.1 character received on port 0 with the K28.5 character.

### **Transceiver Interface Block**

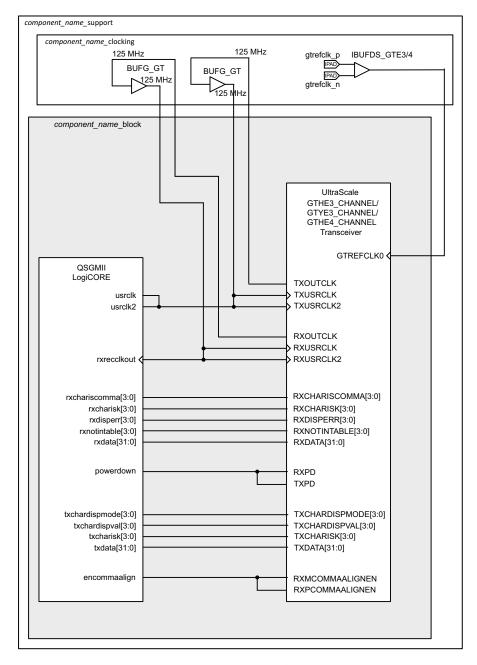

The Transceiver Interface Block enables the core to connect to UltraScale+™ families, UltraScale™ architecture, Zynq-7000 AP SoC, Virtex-7, Kintex-7, or Artix-7 device serial transceiver.

## **Elastic Buffer**

An Elastic Buffer is instantiated on each port to perform clock correction. The clock correction involves additions and removal of /I1/ characters if disparity is ignored or /I2/ if the disparity is considered. This buffer is 128 locations deep.

# **Feature Summary**

- The core has two modes of operation.

- Media Access Controller (MAC) mode to connect to a customized MAC or Xilinx<sup>®</sup>

Tri-Mode Ethernet MAC LogiCORE™ IP operating in Internal Mode. See QSGMII MAC in the Applications section.

- Physical-side interface (PHY) mode to connect to an external PHY through Gigabit Media Independent Interface/Media Independent Interface (GMII/MII). See QSGMII PHY in the Application section.

- Each port configured and monitored through independent a serial MDIO interface, which can optionally be omitted from the core. An additional configuration vector interface is provided that can be used to program registers 0 and 4 over and above the MDIO interface.

- Supports Auto-Negotiation according to IEEE 802.3-2008 Clause 37 on each port for information exchange with a link partner, which can optionally be omitted from the core.

- Integrated transceiver interface using a Zynq-7000 AP SoC, Virtex-7, and Kintex-7 device GTX transceiver.

- Integrated transceiver interface using an UltraScale+ families, UltraScale architecture, and Virtex-7 FPGA GTH transceiver.

- Integrated transceiver interface using Artix-7 FPGA GTP transceiver.

- Implements SGMII Adaptation to support 10/100/1000 operation for each port. Each port can be programmed to operate at a speed independent of other ports.

- Transmitters of all ports transmit only /I1/ Idle ordered set.

- Lane alignment based on K28.1 character detection.

- Implements QSGMII K28.5 swapper on Port 0 transmit path.

- Implements QSGMII K28.1 swapper on Port 0 receive path.

- Implements receive link synchronization state machine.

- Programmable Decoder running disparity checking for each port.

- Supports maximum frame size of 2.8 KB for 10 Mb/s, 28 KB for 100 Mb/s and 280 KB for 1 Gb/s per single lane.

**Note:** By default, the QSGMII core does not support half-duplex mode. To request this functionality, contact your local Xilinx support representative.

# **Applications**

Typical applications for the QSGMII core include the following:

- QSGMII MAC

- QSGMII PHY

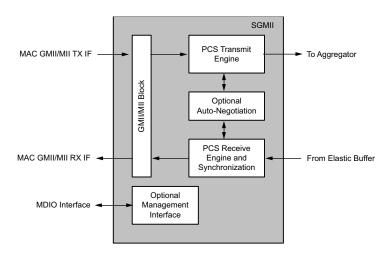

## **QSGMII MAC**

Figure 1-3 illustrates a typical application for the QSGMII core when operating in MAC mode using a device-specific transceiver to provide the serial interface.

- The device-specific transceiver is connected to an external off-the-shelf QSGMII PHY (This can be a device that supports conversion of QSGMII to 10BASE-T, 100BASE-T, or 1000BASE-T.)

- The GMII interfaces of the QGMII core are connected to multiple instances of an embedded Ethernet MAC, for example, the Xilinx Tri-Mode Ethernet MAC core.

Figure 1-3: Typical Application of QSGMII in MAC Mode

# **QSGMII PHY**

Figure 1-4 illustrates a typical application for the QSGMII core when operating in PHY mode, using a device-specific transceiver to provide the serial interface.

- The device-specific transceiver is connected to an external off-the-shelf Ethernet MAC device that also supports QSGMII. (This can be multiple instances of tri-mode MAC providing 10/100/1000 Mb/s operation, for example, the Xilinx Tri-Mode Ethernet MAC core connected to QSGMII core in MAC mode.)

- The GMII/MII interface of QSGMII core is connected to a tri-mode PHY providing 10BASE-T, 100BASE-T, and 1000BASE-T operation.

Figure 1-4: Typical Application of QSGMII in PHY Mode

# **Licensing and Ordering Information**

This Xilinx LogiCORE IP module is provided at no additional cost with the Xilinx Vivado<sup>®</sup> Design Suite under the terms of the Xilinx End User License. Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# **Product Specification**

# **Standards**

- Ethernet Standard 802.3-2008 Clauses 22, 35, 36 and 38 [Ref 2]

- Cisco Serial GMII Specification Revision 1.8 (SGMII) [Ref 3]

- Cisco Quad SGMII Specification Revision 1.2 (QSGMII) [Ref 4]

# **Performance**

# Latency

These measurements are for the core only; they do not include the latency through the UltraScale+™ families, UltraScale™ architecture, Zynq®-7000 All Programmable SoC, Virtex®-7, Kintex®-7, or Artix®-7 device transceiver, or the Transmitter Elastic Buffer added in the QSGMII core.

# Transmit Path Latency

As measured from a data octet input into gmii\_txd[7:0] of the transmitter side GMII of SGMII on port 0 (until that data appears on txdata[7:0] on the serial transceiver interface), the latency through the core in the transmit direction is five clock periods of userc1k2.

# Receive Path Latency

Receive Path Latency is variable because of an elastic buffer on each lane for clock compensation; therefore, the latency is measured from the output of the elastic buffer until the octet appears on the receiver side GMII. As measured from a data octet output from the elastic buffer until that data appears on gmii\_rxd[7:0] of the receiver side GMII of port 0, the latency through the core in the receive direction is six clock periods of userclk2.

# **Throughput**

QSGMII Interface operates at a full line rate of 5 Gb/s.

# **Resource Utilization**

Resources required for this core have been estimated for different devices listed in Table 2-1 through Table 2-4. Utilization figures are obtained by implementing the block-level wrapper for the core. This wrapper is part of the example design and connects the core to the selected physical interface. These values were generated using Xilinx<sup>®</sup> Vivado<sup>®</sup> IP catalog. They are derived from post-synthesis reports, and might change during MAP and PAR.

BUFG usage does not consider multiple instantiations of the core, where clock resources can often be shared. BUFG usage does not include the reference clock required for IDELAYCTRL. This clock source can be shared across the entire device and is not core specific.

**Note:** UltraScale™ architecture results are expected to be similar to 7 series device results.

### Virtex-7 Devices

Table 2-1 provides approximate utilization figures for various core options when a single instance of the core is instantiated in a Virtex-7 device.

Table 2-1: Resource Utilization for Virtex-7

|          | Parameter Val  |                  | De     | vice Res | ources |        |       |

|----------|----------------|------------------|--------|----------|--------|--------|-------|

| Mode     | MDIO Interface | Auto-Negotiation | Slices | FFs      | LUTs   | LUTRAM | BUFGs |

|          | Yes            | Yes              | 1580   | 3353     | 2534   | 442    | 0     |

| MAC MODE | Yes            | No               | 1227   | 2481     | 1684   | 442    | 0     |

| WAC WODE | No             | Yes              | 1321   | 2841     | 2041   | 410    | 0     |

|          | No             | No               | 1076   | 2237     | 1449   | 410    | 0     |

|          | Yes            | Yes              | 1570   | 4049     | 2549   | 442    | 0     |

| PHY GMII | Yes            | No               | 1190   | 3145     | 1684   | 442    | 0     |

| Mode     | No             | Yes              | 1294   | 3513     | 2012   | 410    | 0     |

|          | No             | No               | 1107   | 2885     | 1440   | 410    | 0     |

Table 2-1: Resource Utilization for Virtex-7 (Cont'd)

| Parameter Values |     |     |      | De   | vice Res | ources |   |

|------------------|-----|-----|------|------|----------|--------|---|

|                  | Yes | Yes | 1574 | 3501 | 2657     | 442    | 0 |

| PHY MII          | Yes | No  | 1164 | 2613 | 1795     | 442    | 0 |

| Mode             | No  | Yes | 1306 | 2981 | 2131     | 410    | 0 |

|                  | No  | No  | 1068 | 2369 | 1562     | 410    | 0 |

- 1. The number of BUFGs indicated are at the block level of the core.

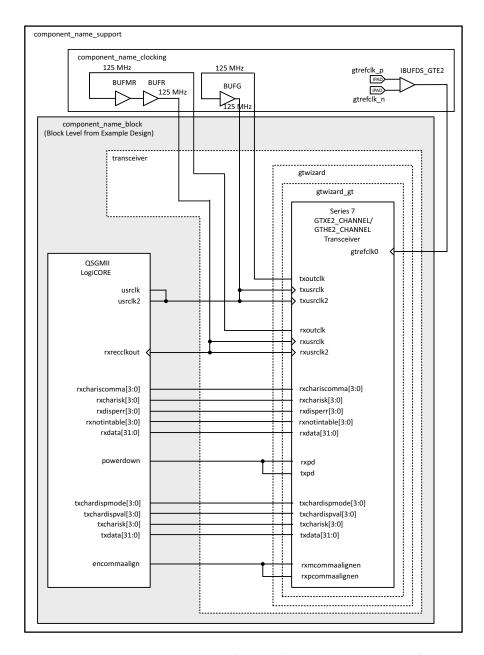

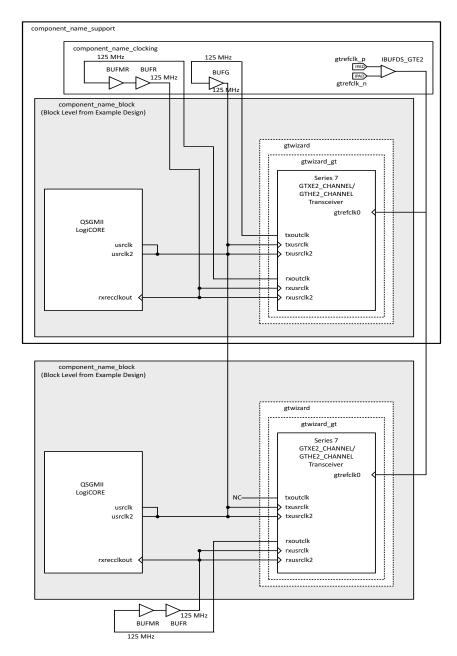

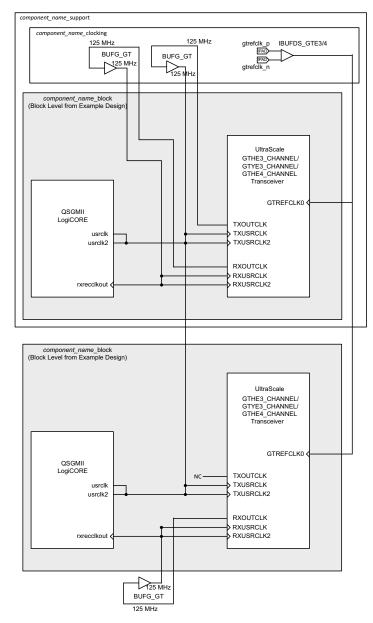

- 2. Additional BUFG is required to drive the txoutclk. See Figure 5-1.

- 3. Additional BUFG is required to drive the free running independent\_clock.

- 4. These two BUFGs can be shared across multiple instances of the core.

- 5. Additional BUFG can be added for rxoutclk. Alternately, a BUFMR and BUFR in series can be used. BUFMR and BUFR are added by default if you selects **Include Shared Logic in Core**; otherwise you can manually instantiate the BUFGs.

#### **Kintex-7 Devices**

Table 2-2 provides approximate utilization figures for various core options when a single instance of the core is instantiated in a Kintex-7 device.

Table 2-2: Resource Utilization for Kintex-7 Devices

| Parameter Values |                |                  |        | Device Resources |      |        |       |  |

|------------------|----------------|------------------|--------|------------------|------|--------|-------|--|

| Mode             | MDIO Interface | Auto-Negotiation | Slices | FFs              | LUTs | LUTRAM | BUFGs |  |

|                  | Yes            | Yes              | 1529   | 3353             | 2550 | 442    | 0     |  |

| MAC MODE         | Yes            | No               | 1131   | 2481             | 1707 | 442    | 0     |  |

| WAC WODE         | No             | Yes              | 1278   | 2841             | 2039 | 410    | 0     |  |

|                  | No             | No               | 1084   | 2237             | 1443 | 410    | 0     |  |

|                  | Yes            | Yes              | 1662   | 4048             | 2547 | 442    | 0     |  |

| PHY GMII Mode    | Yes            | No               | 1275   | 3144             | 1688 | 442    | 0     |  |

| PHY GMII Mode    | No             | Yes              | 1407   | 3512             | 2013 | 410    | 0     |  |

|                  | No             | No               | 1137   | 2884             | 1439 | 410    | 0     |  |

|                  | Yes            | Yes              | 1641   | 3501             | 2675 | 442    | 0     |  |

| PHY MII Mode     | Yes            | No               | 1153   | 2613             | 1821 | 442    | 0     |  |

|                  | No             | Yes              | 1291   | 2981             | 2135 | 410    | 0     |  |

|                  | No             | No               | 1066   | 2369             | 1558 | 410    | 0     |  |

- 1. The number of BUFGs indicated are at the block level of the core.

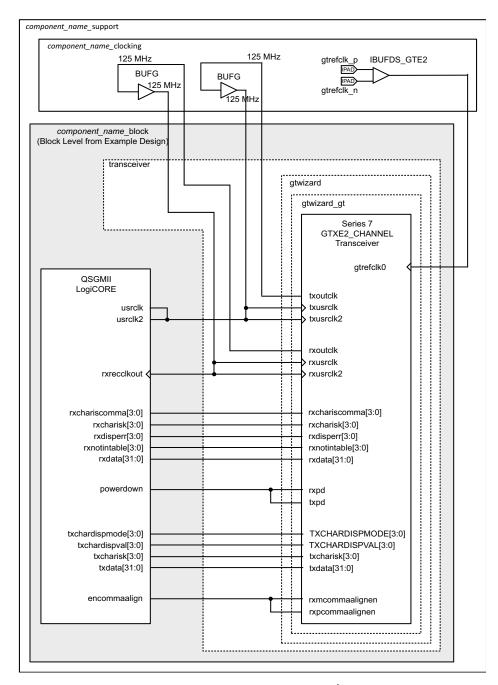

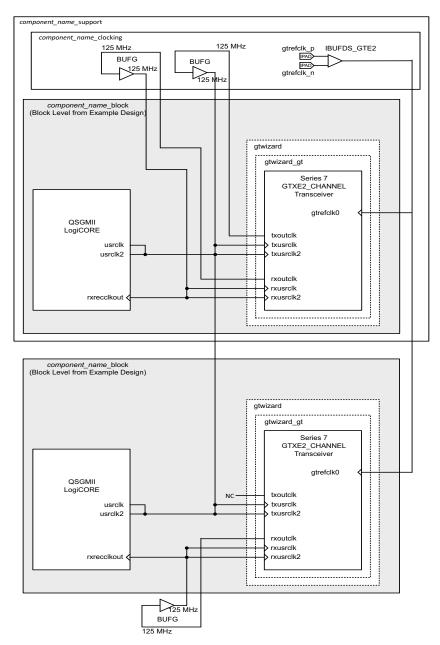

- 2. Additional BUFG is required to drive the txoutclk. See Figure 5-2.

- 3. Additional BUFG is required to drive the free running independent\_clock.

- 4. These 2 BUFGs can be shared across multiple instances of the core.

- 5. Additional BUFG can be added for rxoutclk. BUFG is added by default if you select **Include Shared Logic in Core**; otherwise you can manually instantiate the BUFGs.

#### **Artix-7 Devices**

Table 2-3 provides approximate utilization figures for various core options when a single instance of the core is instantiated in an Artix-7 device.

Table 2-3: Resource Utilization for Artix-7 Devices

|                   | Parameter Values |                  |        |      | vice Res | ources |       |

|-------------------|------------------|------------------|--------|------|----------|--------|-------|

| Mode              | MDIO Interface   | Auto-Negotiation | Slices | FFs  | LUTs     | LUTRAM | BUFGs |

|                   | Yes              | Yes              | 1456   | 3354 | 2525     | 442    | 0     |

| MAC MODE          | Yes              | No               | 1120   | 2482 | 1678     | 442    | 0     |

| WAC WODE          | No               | Yes              | 1212   | 2842 | 2035     | 410    | 0     |

|                   | No               | No               | 951    | 2238 | 1444     | 410    | 0     |

|                   | Yes              | Yes              | 1490   | 4051 | 2536     | 442    | 0     |

| PHY GMII Mode     | Yes              | No               | 1162   | 3147 | 1711     | 442    | 0     |

| FITT GIVIII WIOGE | No               | Yes              | 1339   | 3515 | 2026     | 410    | 0     |

|                   | No               | No               | 1076   | 2887 | 1447     | 410    | 0     |

|                   | Yes              | Yes              | 1498   | 3502 | 2658     | 442    | 0     |

| PHY MII Mode      | Yes              | No               | 1133   | 2614 | 1794     | 442    | 0     |

|                   | No               | Yes              | 1264   | 2982 | 2139     | 410    | 0     |

|                   | No               | No               | 1005   | 2370 | 1562     | 410    | 0     |

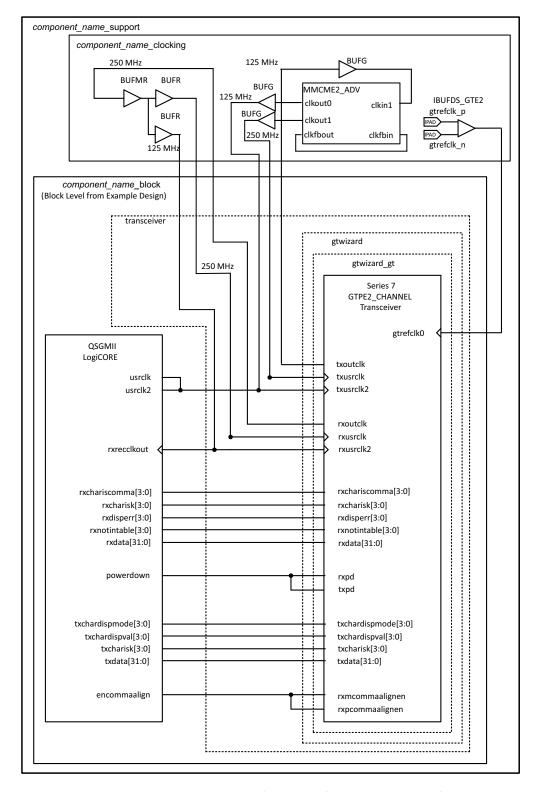

- 1. The number of BUFGs indicated are at the block level of the core.

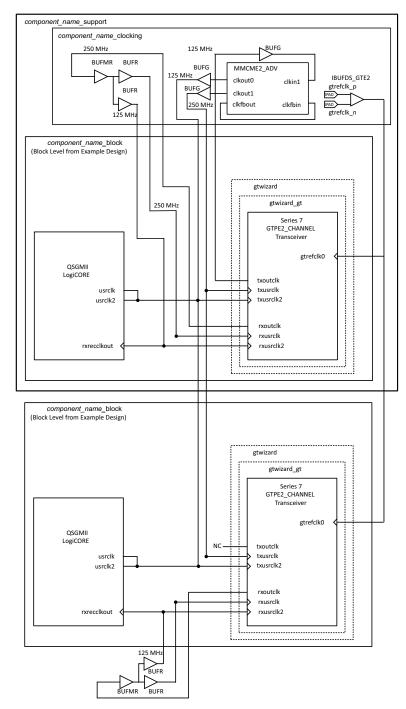

- 2. Additional BUFG is required to feed the input of MMCM. See Figure 5-3.

- 3. Two additional BUFGs are required to drive the outputs of MMCM. See Figure 5-3.

- 4. Additional BUFG is required to drive the free running independent\_clock.

- 5. These four BUFGs can be shared across multiple instances of the core.

- 6. Additional BUFR is used to divide the rxoutclk for driving rxusrclk2.

- 7. Additional BUFR is used to drive the rxusrclk.

- 8. The above BUFRs are added by default if you select **Include Shared Logic in Core**; otherwise you can manually instantiate the BUFRs. Additional BUFGs can be cascaded to the BUFRs if rxoutclk can be shared across multiple instances of the core.

# **Zynq-7000 All Programmable SoCs**

Table 2-4 provides approximate utilization figures for various core options when a single instance of the core is instantiated in a Zynq-7000 AP SoC device.

Table 2-4: Resource Utilization for Zynq-7000

| Parameter Values                  |     |                  |        | Device Resources |      |        |       |  |

|-----------------------------------|-----|------------------|--------|------------------|------|--------|-------|--|

| Mode MDIO Interface Auto-Negotiat |     | Auto-Negotiation | Slices | FFs              | LUTs | LUTRAM | BUFGs |  |

|                                   | Yes | Yes              | 1596   | 3353             | 2536 | 442    | 0     |  |

| MAC MODE                          | Yes | No               | 1248   | 2452             | 1657 | 442    | 0     |  |

| MAC MODE                          | No  | Yes              | 1330   | 2812             | 2005 | 410    | 0     |  |

|                                   | No  | No               | 1147   | 2208             | 1416 | 410    | 0     |  |

|                                   | Yes | Yes              | 1637   | 4048             | 2544 | 442    | 0     |  |

| PHY GMII Mode                     | Yes | No               | 1201   | 3144             | 1683 | 442    | 0     |  |

| PHY GIVIII IVIOGE                 | No  | Yes              | 1351   | 2981             | 2011 | 410    | 0     |  |

|                                   | No  | No               | 1086   | 3512             | 1440 | 410    | 0     |  |

|                                   | Yes | Yes              | 1576   | 2884             | 2659 | 442    | 0     |  |

| PHY MII Mode                      | Yes | No               | 1127   | 2613             | 1802 | 442    | 0     |  |

|                                   | No  | Yes              | 1252   | 2981             | 2128 | 410    | 0     |  |

|                                   | No  | No               | 992    | 2369             | 1561 | 410    | 0     |  |

- 1. The number of BUFGs indicated are at the block level of the core.

- 2. Additional BUFG is required to drive the txoutclk. See Figure 5-2.

- 3. Additional BUFG is required to drive the free running independent\_clock.

- 4. These two BUFGs can be shared across multiple instances of the core.

- 5. Additional BUFG can be added for rxoutclk. BUFG is added by default if you select **Include Shared Logic in Core**; otherwise you can manually instantiate the BUFGs.

# **Port Descriptions**

# **Internal Encrypted Hierarchy of the Core Level Ports**

All ports in the encrypted hierarchy of the core are internal connections in FPGA logic. Un-encrypted HDL in the core and example design (delivered with the core) connect the core, where appropriate, to a device-specific transceiver, and/or add IBUFs, OBUFs, and IOB flip-flops to the external signals of the GMII/MII. IOBs are added to the remaining unconnected ports to take the example design through the Xilinx implementation software. All the ports described here indicate the pins at the in the encrypted hierarchy of the core level. The block level design instantiates the core and transceiver.

All clock management logic is placed in this example design, allowing you more flexibility in implementation (such as designs using multiple cores). This example design is provided in both VHDL and Verilog.

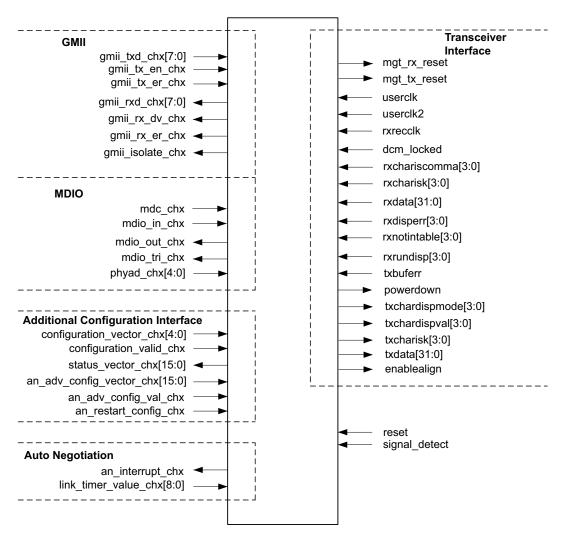

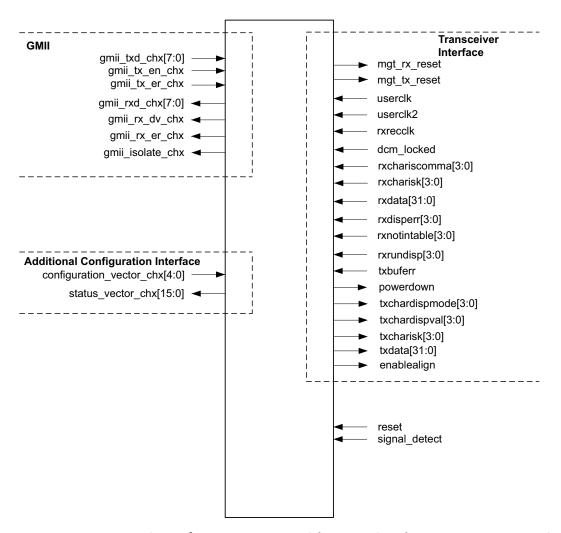

Figure 2-1 shows the pinout for the QSGMII core using a device-specific transceiver with the optional MDIO Management and optional Auto-Negotiation.

The port name for multiple instances of an interface is generalized as "CHx." "CHx" takes the value "CH0," "CH1," "CH2," and "CH3."

Figure 2-1: Component Pinout of QSGMII Core with Optional MDIO and Auto-Negotiation

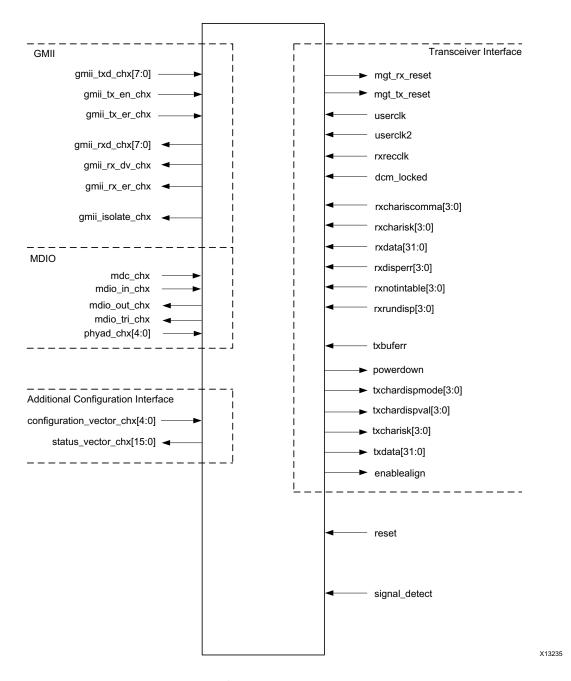

Figure 2-2 shows the pinout for the QSGMII core using a device-specific transceiver with only the optional MDIO Management. The port name for multiple instances of an interface is generalized as "CHx." "CHx" takes the value "CH0," "CH1," "CH2," and "CH3."

Figure 2-2: Component Pinout of QSGMII Core with Only Optional MDIO Management

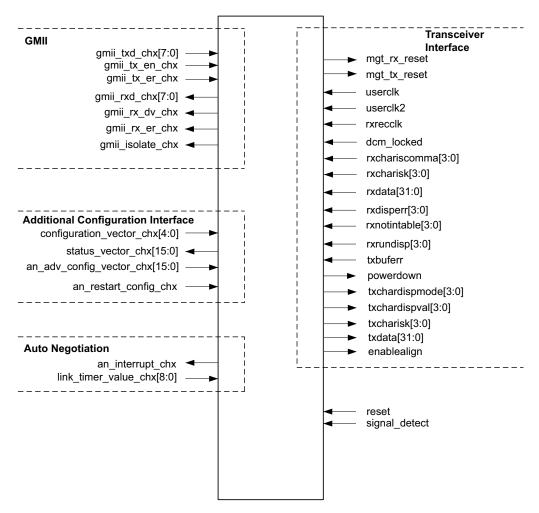

Figure 2-3 shows the pinout for the QSGMII core using a device-specific transceiver with only the optional Auto-Negotiation.

The port name for multiple instances of an interface is generalized as "CHx." "CHx" takes the value "CH0," "CH1," "CH2," and "CH3."

Figure 2-3: Component Pinout of QSGMII Core with Only Optional Auto-Negotiation

Figure 2-4 shows the pinout for the QSGMII core using a device-specific transceiver without optional MDIO or Auto-Negotiation.

The port name for multiple instances of an interface is generalized as "CHx." "CHx" takes the value "CH0," "CH1," "CH2," and "CH3."

Figure 2-4: Component Pinout for QSGMII Core without Optional MDIO or Auto-Negotiation

# **QSGMII Core Client Side Interface**

This interface contains four groups of interfaces, with each group containing a set of the GMII interface, the optional management interface if supported and configuration vectors. MII interface, if present on the QSGMII block, is converted to a GMII type interface. The interfaces end in "chx," taking the values ch0 to ch3, indicating the port connection to the respective GMII interface.

#### **GMII Pinout**

Table 2-5 describes the GMII-side interface signals of the core that are common to all parameterizations of the core. These are typically attached to an Ethernet MAC, either off-chip or internally integrated. The HDL block level in PHY mode of operation for seamless connection to pads in IP Canvas delivered with the core connects these signals to IOBs to provide a place-and-route example.

Table 2-5: GMII Interface Signals Pinout

| Signal                           | Direction | Description                                                                             |

|----------------------------------|-----------|-----------------------------------------------------------------------------------------|

| gmii_txd_chx[7:0] <sup>(1)</sup> | Input     | GMII Transmit data from MAC                                                             |

| gmii_tx_en_chx <sup>(1)</sup>    | Input     | GMII Transmit control signal from MAC                                                   |

| gmii_tx_er_chx <sup>(1)</sup>    | Input     | GMII Transmit control signal from MAC                                                   |

| gmii_rxd_chx[7:0] <sup>(1)</sup> | Output    | GMII Received data to MAC                                                               |

| gmii_rx_dv_chx <sup>(1)</sup>    | Output    | GMII Received control signal to MAC                                                     |

| gmii_rx_er_chx <sup>(1)</sup>    | Output    | GMII Received control signal to MAC                                                     |

| gmii_isolate_chx <sup>(1)</sup>  | Output    | IOB 3-state control for GMII Isolation. Only of use when implementing an external GMII. |

#### **Notes:**

1. These signals are synchronous to the internal 125 MHz reference clock of the core. This is userclk2.

#### **Common Signals**

Table 2-6 describes the remaining signals common to all parameterizations of the core.

Table 2-6: Other Common Signals

| Signal        | Direction | Description                                                                                                                                                                                                                                                                                                                                                               |

|---------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reset         | Input     | Asynchronous reset for the entire core. Active-High. Clock domain is not applicable.                                                                                                                                                                                                                                                                                      |

| signal_detect | Input     | Signal direct from the Physical Medium Dependent (PMD) sublayer indicating the presence of light detected at the optical receiver. If set to 1, indicates that the optical receiver has detected light. If set to 0, this indicates the absence of light. If unused, this signal should be set to 1 to enable correct operation the core. Clock domain is not applicable. |

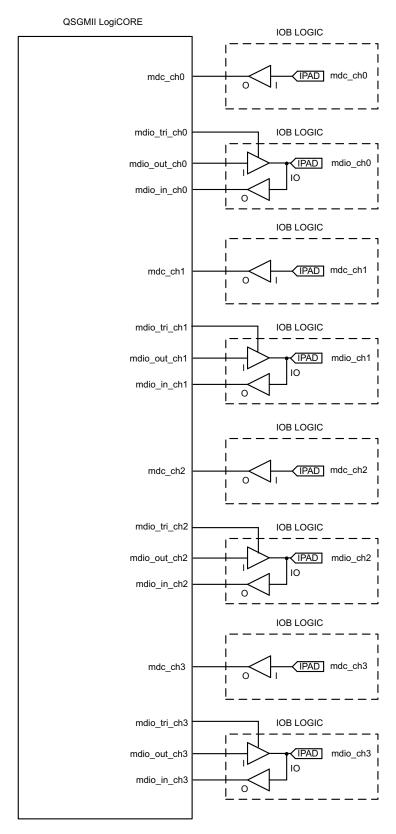

#### **MDIO Management Interface Pinout (Optional)**

The optional MDIO Management Interface is provided for each instance of SGMII. The "chx" suffix denotes a generic nomenclature for describing the interface. Each of the interfaces are identified with "chx" taking values from "ch0" to "ch3."

Table 2-7 describes the optional MDIO interface signals of the core that are used to access the PCS Management registers. Each of these interfaces is typically connected to the MDIO port of a MAC device, either off-chip or to an internally integrated MAC core. For more information, see Management Registers.

Table 2-7: Optional MDIO Interface Pinout

| Signal                      | Direction | Clock<br>Domain | Description                                                                                                                                          |

|-----------------------------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| mdc_chx                     | Input     | NA              | Management clock (<= 2.5 MHz).                                                                                                                       |

| mdio_in_chx <sup>(1)</sup>  | Input     | mdc_chx         | Input data signal for communication with the instance number "x" of the MDIO controller (for example, an Ethernet MAC). Tie High if unused.          |

| mdio_out_chx <sup>(1)</sup> | Output    | mdc_chx         | Output data signal for communication with the instance number "x" of the MDIO controller (for example, an Ethernet MAC).                             |

| mdio_tri_chx <sup>(1)</sup> | Output    | mdc_chx         | 3-state control for MDIO signals. The value 0 signals that the value on mdio_out should be asserted onto the MDIO interface.                         |

| phyad_chx[4:0]              | Input     | NA              | Physical Addresses of the PCS Management register set of each "x" instance of SGMII. It is expected that this signal is tied off to a logical value. |

#### **Auto-Negotiation Interface Pinout (Optional)**

Table 2-8 describes the signals present when the optional Auto-Negotiation functionality is present.

Table 2-8: Optional Auto-Negotiation Interface Signal Pinout

| Signal                          | Direction                                                                                                                                                                                                       | Description                                                                                                                                                                                                                              |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| an_interrupt_chx <sup>(1)</sup> | Output                                                                                                                                                                                                          | When an optional management interface is present, active-High interrupt to signal the completion of an Auto-Negotiation cycle. This interrupt can be enabled/disabled and cleared by writing to the appropriate PCS Management register. |

| January Carput                  | When an optional management interface is not present, this signal just indicates the completion of the Auto-Negotiation cycle. Is reset automatically if Auto-Negotiation restarts. This bit cannot be cleared. |                                                                                                                                                                                                                                          |

#### Notes:

1. These signals are synchronous to the internal 125 MHz reference clock of the core. This is userclk2 when the core is used with the device-specific transceiver.

#### **Additional Configuration Interface**

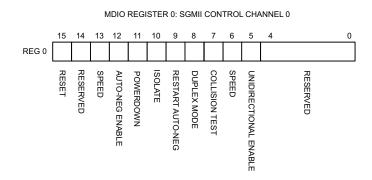

This interface can be used over and above the optional management interface to write into the Control register (Register 0) and the Auto-Negotiation Advertisement register (Register 4).

<sup>1.</sup> These signals can be connected to a 3-state buffer to create a bidirectional mdio signal suitable for connection to an external MDIO controller (for example, an Ethernet MAC).

Table 2-9: Additional Configuration Interface Signal Pinout

| Signal                                            | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|---------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| configuration_vector_<br>chx[5:0] <sup>(1)</sup>  |           | Bit[0]:Unidirectional Enable<br>When set to 1, Enable Transmit irrespective of the state of RX.<br>When set to 0, Normal operation                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                   | Input     | Bit[1]: Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                                   |           | Bit[2]: Power Down When set to 1, the device-specific transceiver is placed in a low-power state. A reset must be applied to clear. MDIO must be present to apply reset. This bit is valid only on configuration_vector_ch0 and is reserved in other instances of configuration_vector.                                                                                                                                                                                                      |  |

|                                                   |           | Bit[3] Isolate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                   |           | When set to 1, the GMII should be electrically isolated. When set to 0, normal operation is enabled                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                                   |           | Bit[4] Auto-Negotiation Enable This signal is valid only if the Auto-Negotiation (AN) module is enabled through the Vivado IP catalog. When set to 1, the signal enables the AN feature. When set to 0, AN is disabled.                                                                                                                                                                                                                                                                      |  |

| configuration_vector_<br>valid_chx <sup>(1)</sup> | Input     | This signal is valid only when the MDIO interface is present. The rising edge of this signal is the enable signal to overwrite the Register 0 contents that were written from the MDIO interface. For triggering a fresh update of Register 0 through configuration_vector_chx, this signal should be deasserted and then reasserted.                                                                                                                                                        |  |

| an_adv_config_vector_<br>chx[15:0] <sup>(1)</sup> | Input     | QSGMII operating in MAC Mode, the AN_ADV register is ha wired internally to "0x0001" and this bus has no effect. Fo QSGMII operating in PHY mode, the AN_ADV register is programmed by this bus as specified for the following bits Bit[0]: Always 1 Bits [9:1]: Reserved Bits [11:10]: Speed 1 1 Reserved 1 0 1000 Mb/s 0 1 100 Mb/s 0 1 100 Mb/s Bits [12]:Duplex Mode 1 Full Duplex 0 Half Duplex Bit[13]: Reserved Bit [14]: Acknowledge Bit [15]: PHY Link Status 1 Link Up 0 Link Down |  |

Table 2-9: Additional Configuration Interface Signal Pinout (Cont'd)

| Signal                                 | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| an_adv_config_valid_chx (1)            | Input     | This signal is valid only when the MDIO interface is present. The rising edge of this signal is the enable signal to overwrite the Register 4 contents that were written from the MDIO interface. For triggering a fresh update of Register 4 through an_adv_config_vector_chx, this signal should be deasserted and then reasserted.                                                                                                                                                     |

| an_restart_config_chx <sup>(1)</sup>   | Input     | This signal is valid only when AN is present. The rising edge of this signal is the enable signal to overwrite Bit 9 of Register 0. For triggering a fresh AN Start, this signal should be deasserted and then reasserted.                                                                                                                                                                                                                                                                |

| status_vector_chx[15:0] <sup>(1)</sup> | Output    | Bit[0]: Link Status This signal indicates the status of the link. When High, the link is valid; synchronization of the link has been obtained and Auto-Negotiation (if present and enabled) has successfully completed. When Low, a valid link has not been established. Either link synchronization has failed or Auto-Negotiation (if present and enabled) has failed to complete.  When auto-negotiation is enabled, this signal is identical to Status register Bit 1.2: Link Status. |

|                                        |           | <ul> <li>When auto-negotiation is disabled, this signal is identical to status_vector_chx Bit[1].</li> <li>Bit[1]: Link Synchronization     This signal indicates the state of the synchronization state machine (<i>IEEE 802.3</i> figure 36-9) which is based on the reception of valid 8B/10B code groups. This signal is similar to Bit[0] (Link Status), but is not qualified with</li> </ul>                                                                                        |

|                                        |           | Auto-Negotiation.  When High, link synchronization has been obtained and in the synchronization state machine, sync_status=OK.  When Low, synchronization has failed.                                                                                                                                                                                                                                                                                                                     |

|                                        |           | Bit[2]: RUDI(/C/)     The core is receiving /C/ ordered sets (Auto-Negotiation Configuration sequences).                                                                                                                                                                                                                                                                                                                                                                                  |

|                                        |           | Bit[3]: RUDI(/I/) The core is receiving /I/ ordered sets (Idles).                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                        |           | Bit[4]: RUDI(INVALID)     The core has received invalid data while receiving/C/ or /I/ ordered set.                                                                                                                                                                                                                                                                                                                                                                                       |

|                                        |           | Bit[5]: RXDISPERR     The core has received a running disparity error during the 8B/10B decoding function.                                                                                                                                                                                                                                                                                                                                                                                |

Table 2-9: Additional Configuration Interface Signal Pinout (Cont'd)

| Signal                                             | Direction | Description                                                                                                                                                                                                                                                                                  |  |

|----------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| status_vector_chx[15:0] <sup>(1)</sup> (continued) | Output    | Bit[6]: RXNOTINTABLE     The core has received a code group that is not recognized from the 8B/10B coding tables.                                                                                                                                                                            |  |

|                                                    |           | Bit[7]: PHY Link Status     This bit represents the link status of the external PHY device     attached to the other end of the QSGMII link (High     indicates that the PHY has obtained a link with its link     partner; Low indicates that is has not linked with its link     partner.) |  |

|                                                    |           | Bit[9:8]: Remote Fault Encoding     This signal indicates the remote fault encoding (IEEE 802.3 table 37-3). This signal is validated by bit 13 of the status_vector_chx and is only valid when Auto-Negotiation is enabled.                                                                 |  |

|                                                    |           | This signal has no significance when the core is in PHY mode and indicates "00."                                                                                                                                                                                                             |  |

|                                                    |           | Bit [11:10]: SPEED     This signal indicates that the speed is negotiated and is only valid when Auto-Negotiation is enabled. The signal encoding follows:                                                                                                                                   |  |

|                                                    |           | Bit[11] Bit[10]<br>1 1 Reserved<br>1 0 1000 Mb/s<br>0 1 100 Mb/s<br>0 0 10 Mb/s                                                                                                                                                                                                              |  |

|                                                    |           | Bit[12]: Duplex Mode     This bit indicates the Duplex mode negotiated with the link partner.                                                                                                                                                                                                |  |

|                                                    |           | 1 = Full Duplex<br>0 = Half Duplex                                                                                                                                                                                                                                                           |  |

|                                                    |           | Bit[13] Remote Fault     When this bit is logic 1, it indicates that a remote fault is detected and the type of remote fault is indicated by status_vector_chx bits[9:8].                                                                                                                    |  |

|                                                    |           | <b>Note:</b> This bit is only deasserted when an MDIO read is made to status register (register 1). This signal has no significance in QSGMII PHY mode.                                                                                                                                      |  |

Table 2-9: Additional Configuration Interface Signal Pinout (Cont'd)

| Bits[15;14]: Pause These bits reflect the bits [8:7] of Register 5 (Link Partn AN register).  Status_vector_chx[15:0](1) (continued)  Output  Bit[15] Bit[14] 0 0 No Pause 0 1 Symmetric Pause 1 0 Asymmetric Pause towards Link partner 1 1 Both Symmetric Pause and Asymmetric Pause to link partner |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

## **QSGMII Core Physical Side Interface**

Table 2-10 describes the interface to the device-specific transceiver. The core is connected to the chosen transceiver in the appropriate HDL example design delivered with the core.

**Table 2-10:** Transceiver Interface Pinout

| Signal                            | Direction | Description                                                                                                                                                                                                                                                                            |  |

|-----------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| mgt_rx_reset <sup>(1)</sup>       | Output    | Reset signal issued by the core to the device-specific transceiver receiver path. Connects to the gtrxreset signal of the device-specific transceiver. This reset is a combination of hard reset, soft reset and reset due to rxbuffer errors.                                         |  |

| mgt_tx_reset <sup>(2)</sup>       | Output    | Reset signal issued by the core to the device-specific transceiver transmitter path. Connects to the gttxreset signal of the device-specific transceiver. This reset is a combination of hard reset, soft reset and reset due to txbuffer errors.                                      |  |

| userclk                           | Input     | Also connected to txusrclk of the device-specific transceiver. Clock domain is not applicable.                                                                                                                                                                                         |  |

| userclk2                          | Input     | Also connected to txusrclk2 of the device-specific transceiver. Clock domain is not applicable.                                                                                                                                                                                        |  |

| rxrecclk                          | Input     | Also connected to rxusrclk2 of the device-specific transceiver. Clock domain is not applicable.                                                                                                                                                                                        |  |

| dcm_locked                        | Input     | A Digital Clock Manager (DCM) can be used to derive userclk and userclk2. This is implemented in the HDL design example delivered with the core. The core uses this input to hold the device-specific transceiver in reset until the DCM obtains lock. Clock domain is not applicable. |  |

| reset_done                        | Input     | Indicates that both transceiver transmit and receive paths have completed reset cycle.                                                                                                                                                                                                 |  |

| rxchariscomma[3:0] <sup>(1)</sup> | Input     | Connects to device-specific transceiver signal of the same name.                                                                                                                                                                                                                       |  |

| rxcharisk[3:0] <sup>(1)</sup>     | Input     | Connects to device-specific transceiver signal of the same name.                                                                                                                                                                                                                       |  |

| rxdata[31:0] <sup>(1)</sup>       | Input     | Connects to device-specific transceiver signal of the same name.                                                                                                                                                                                                                       |  |

Signals are synchronous to the core internal 125 MHz reference clock userclk2 when used with a device-specific transceiver.

Table 2-10: Transceiver Interface Pinout (Cont'd)

| Signal                             | Direction | Description                                                       |

|------------------------------------|-----------|-------------------------------------------------------------------|

| rxdisperr[3:0] <sup>(1)</sup>      | Input     | Connects to device-specific transceiver signal of the same name.  |

| rxnotintable[3:0] <sup>(1)</sup>   | Input     | Connects to device-specific transceiver signal of the same name.  |

| rxrundisp[3:0] <sup>(1)</sup>      | Input     | Connects to device-specific transceiver signal of the same name.  |

| txbuferr <sup>(2)</sup>            | Input     | Connects to device-specific transceiver signal of the sam e name. |

| powerdown <sup>(2)</sup>           | Output    | Connects to device-specific transceiver signal of the same name.  |

| txchardispmode[3:0] <sup>(2)</sup> | Output    | Connects to device-specific transceiver signal of the same name.  |

| txchardispval[3:0] <sup>(2)</sup>  | Output    | Connects to device-specific transceiver signal of the same name.  |

| txcharisk[3:0] <sup>(2)</sup>      | Output    | Connects to device-specific transceiver signal of the same name.  |

| txdata[31:0] <sup>(2)</sup>        | Output    | Connects to device-specific transceiver signal of the same name.  |

| enablealign <sup>(2)</sup>         | Output    | Connects to device-specific transceiver signal of the same name.  |

- 1. When the core is used with a device-specific transceiver, rxrecclk is used as the 125 MHz reference clock for driving these signals.

- 2. When the core is used with a device-specific transceiver, userclk2 is used as the 125 MHz reference clock for driving these signals.

# **Block Hierarchy Level Ports**

All the ports described here indicate the pins at the block level. The block level design instantiates the core and transceiver. The block level design is expected to be pulled from the IP catalog into the IP Canvas.

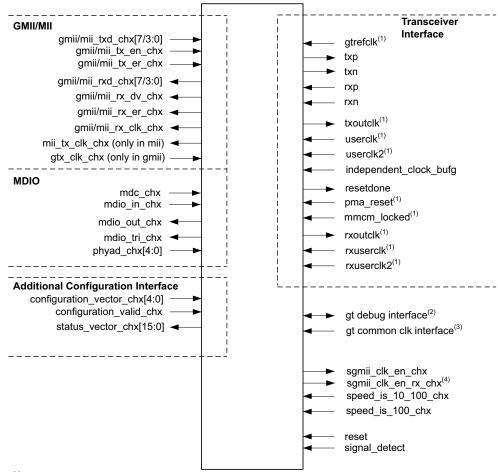

Figure 2-5 shows the pinout for the QSGMII block with the optional MDIO Management and optional Auto-Negotiation. The port name for multiple instances of an interface is generalized as "CHx." "CHx" takes the value "CH0," "CH1," "CH2," and "CH3."

Notes:

X16259-091416

Figure 2-5: Component Pinout of QSGMII Block with Optional MDIO and Auto-Negotiation

These ports are available when Include Shared Logic in Example Design is selected (see Table 2-13).

For ports available for Include Shared Logic in Core, see Table 2-14.

<sup>2.</sup> See Table 2-15 (Transceiver Control and Status Ports).

<sup>3.</sup> For **Include Shared Logic in Example Design** option, see GT Common Clock Interface section in Table 2-13. For **Include Shared Logic in Core**, see Table 2-14.

<sup>4.</sup> These ports are available when the RX path is on rsuserclk2.

Figure 2-6 shows the pinout for the QSGMII block with only optional MDIO Management. The port name for multiple instances of an interface is generalized as "CHx." "CHx" takes the value "CH0," "CH1," "CH2," and "CH3."

#### Notes:

- These ports are available when Include Shared Logic in Example Design is selected (see Table 2-13).

For ports available for Include Shared Logic in Core, see Table 2-14.

- 2. See Table 2-15 (Transceiver Control and Status Ports).

- For Include Shared Logic in Example Design option, see GT Common Clock Interface section in Table 2-13. For Include Shared Logic in Core, see Table 2-14.

- 4. These ports are available when the RX path is on rsuserclk2.

X16260-091416

Figure 2-6: Component Pinout of QSGMII Block with Only Optional MDIO Management

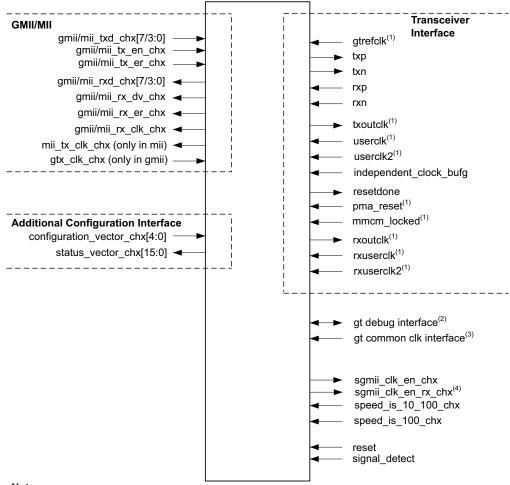

Figure 2-7 shows the pinout for the QSGMII block with only optional Auto-Negotiation. The port name for multiple instances of an interface is generalized as "CHx." "CHx" takes the value "CH0," "CH1," "CH2," and "CH3."

#### Notes:

- These ports are available when Include Shared Logic in Example Design is selected (see Table 2-13).

For ports available for Include Shared Logic in Core, see Table 2-14.

- 2. See Table 2-15 (Transceiver Control and Status Ports).

- For Include Shared Logic in Example Design option, see GT Common Clock Interface section in Table 2-13. For Include Shared Logic in Core, see Table 2-14.

- 4. These ports are available when the RX path is on rsuserclk2.

X16261-091416

Figure 2-7: Component Pinout of QSGMII Block with Only Optional Auto-Negotiation

Figure 2-8 shows the pinout for the QSGMII block without optional MDIO or Auto-Negotiation. The port name for multiple instances of an interface is generalized as "CHx." "CHx" takes the value "CH0," "CH1," "CH2," and "CH3."

- These ports are available when Include Shared Logic in Example Design is selected (see Table 2-13).

For ports available for Include Shared Logic in Core, see Table 2-14.

- 2. See Table 2-15 (Transceiver Control and Status Ports).

- 3. For Include Shared Logic in Example Design option, see GT Common Clock Interface section in Table 2-13. For Include Shared Logic in Core, see Table 2-14.

- 4. These ports are available when the RX path is on rsuserclk2.

X16262-091416

Figure 2-8: Component Pinout of QSGMII Block without Optional MDIO or Auto-Negotiation

#### **QSGMII Block Client Side Interface**

This interface contains four groups of interfaces, with each group containing a set of the GMII/MII interface, the optional management interface if supported and configuration vectors. The interfaces end in "chx," taking the values ch0 to ch3, indicating the port connection to the respective GMII interface.

#### **GMII Pinout**

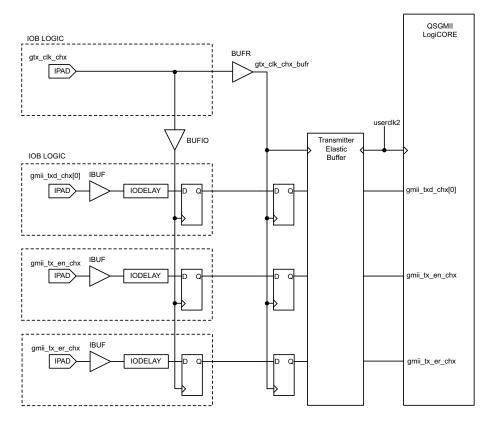

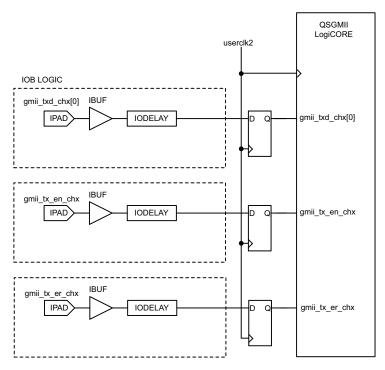

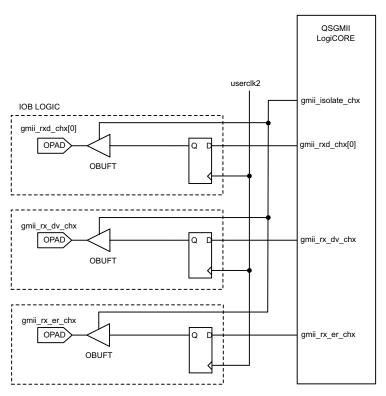

This interface is enabled in the MAC mode or GMII configuration of PHY mode. In the MAC mode this interface is expected to be connected to the GMII interface of Tri-Mode Ethernet MAC core (TEMAC). In the GMII configuration of PHY mode, this interface is brought out onto the pads.

Table 2-11: GMII Interface Signals Pinout

| Signal                           | Direction | Description                                                                   |

|----------------------------------|-----------|-------------------------------------------------------------------------------|

| gmii_txd_chx[7:0] <sup>(1)</sup> | Input     | GMII Transmit data                                                            |

| gmii_txd_en_chx <sup>(1)</sup>   | Input     | GMII Transmit data enable                                                     |

| gmii_tx_er_chx <sup>(1)</sup>    | Input     | GMII Transmit error                                                           |

| gmii_rxd_chx[7:0] <sup>(2)</sup> | Output    | GMII Receive data                                                             |

| gmii_rxd_dv_chx <sup>(2)</sup>   | Output    | GMII Receive data valid                                                       |

| gmii_rx_er_chx <sup>(2)</sup>    | Output    | GMII Receive error                                                            |

| gtx_clk_chx                      | Input     | GMII TX clock. This is valid only in GMII configuration in PHY mode           |

| gmii_rx_clk_chx                  | Output    | GMII RX clock. This is valid only in GMII configuration in PHY mode           |

| sgmii_clk_en_chx                 | Output    | Clock enables. This valid only in MAC mode.                                   |

| sgmii_clk_en_rx_chx              | Output    | Clock enables. This valid only in MAC mode and when RX path is on rxuserclk2. |

- 1. In MAC mode these signals are synchronous to 125 MHz reference clock of the core, that is, userclk2. In GMII configuration of PHY mode these signals are synchronous to gtx\_clk\_chx and these signals are synchronized to userclk2 domain using Transmit Elastic Buffer present in the block

- 2. These signals are synchronous to 125 MHz reference clock of the core. This is userclk2.

Table 2-12: MII Interface Signals Pinout

| Signal                          | Direction | Description                                                                                                                           |

|---------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| mii_txd_chx[7:0] <sup>(1)</sup> | Input     | MII Transmit data                                                                                                                     |

| mii_tx_en_chx <sup>(1)</sup>    | Input     | MII Transmit data enable                                                                                                              |

| mii_tx_er_chx <sup>(1)</sup>    | Input     | MII Transmit error                                                                                                                    |

| mii_rxd_chx[7:0] <sup>(2)</sup> | Output    | MII Receive data                                                                                                                      |

| mii_rx_dv_chx <sup>(2)</sup>    | Output    | MII Receive data valid                                                                                                                |

| mii_rx_er_chx <sup>(2)</sup>    | Output    | MII Receive data error                                                                                                                |

| mii_tx_clk_chx                  | Output    | MII TX clock. This is valid only in MII configuration in MII mode. The clock can be 2.5/25 MHz based on 10/100 Mb/s mode of operation |

Table 2-12: MII Interface Signals Pinout (Cont'd)

| Signal         | Direction | Description                                                                                                                           |  |

|----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| mii_rx_clk_chx | Output    | MII RX clock. This is valid only in MII configuration in MII mode. The clock can be 2.5/25 MHz based on 10/100 Mb/s mode of operation |  |

- 1. These signals should be driven on mii\_tx\_clk\_chx.

- 2. These signals are synchronous to mii\_rx\_clk\_chx.

#### **Common Signals**

See Table 2-6 of Common Signals section for these signals.

#### **MDIO Management Interface Pinout (Optional)**

See Table 2-7 of MDIO Management Interface Pinout section for these signals.

#### **Auto-Negotiation Interface Pinout (Optional)**

See Table 2-8 of Auto-Negotiation Interface Pinout section for these signals.

#### **Additional Configuration Interface**

See Table 2-9 of Additional Configuration Interface Pinout section for these signals.

## QSGMII Block Physical Side Interface

Table 2-13 describes the interface to the device-specific transceiver for the case where shared logic is included in the example design.

Table 2-13: QSGMII Block Physical Side Interface with Shared Logic in the Example Design

| Signal   | Direction | Description                                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------------------|

| gtrefclk | Input     | 125 MHz reference clock from IBUFDS to the transceiver                                          |

| txp      | Output    | Transmit differential                                                                           |

| txn      | Output    | Transmit differential                                                                           |

| rxp      | Input     | Receive differential                                                                            |

| rxn      | Input     | Receive differential                                                                            |

| txoutclk | Output    | txoutclk from transceiver                                                                       |

| userclk  | Input     | Also connected to txusrclk of the device-specific transceiver. Clock domain is not applicable   |

| userclk2 | Input     | Also connected to txusrclk2 of the device-specific transceiver. Clock domain is not applicable. |

| rxoutclk | Output    | rxoutclk from transceiver.                                                                      |

Table 2-13: QSGMII Block Physical Side Interface with Shared Logic in the Example Design

| Signal                     | Direction                 | Description                                                                                                                                                                                        |

|----------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rxuserclk                  | Input                     | Also connected to rxusrclk of the device-specific transceiver. Clock domain is not applicable.                                                                                                     |

| rxuserclk2                 | Input                     | Also connected to rxusrclk2 of the device-specific transceiver. Clock domain is not applicable.                                                                                                    |

| independent_clock_bufg     | Input                     | Stable clock used as stable clock in transceiver and also as control clock for IDELAYCTRL. This clock is 200 MHz for 7 series devices and 300 MHz for UltraScale+ families and UltraScale devices. |

| resetdone                  | Output                    | Indication that reset sequence of the transceiver is complete.                                                                                                                                     |

| pma_reset                  | Input                     | Hard reset synchronized to independent_clock_bufg.                                                                                                                                                 |

| mmcm_locked                | Input                     | Indication from the MMCM that the outputs are stable.                                                                                                                                              |

| independent_clock_bufgdiv4 | Input                     | Independent clock divided by 4. This clock is only present for UltraScale+ families and UltraScale devices when Transceiver Control and Status Ports are disabled.                                 |

|                            | GT Common Clock Interface |                                                                                                                                                                                                    |

| gt0_pll0outclk_in          | Input                     | Valid only for Artix-7 families.<br>Indicates out clock from PLL0 of<br>GT Common.                                                                                                                 |

| gt0_pll0outrefclk_in       | Input                     | Valid only for Artix-7 families.<br>Indicates reference out clock<br>from PLL0 of GT Common.                                                                                                       |

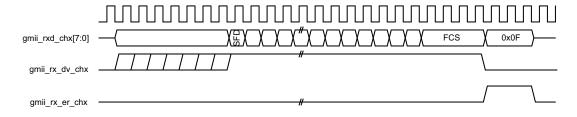

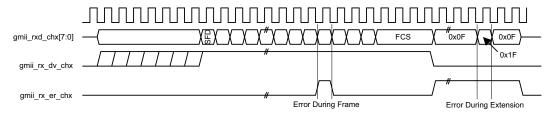

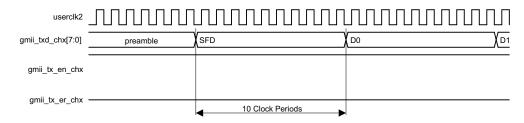

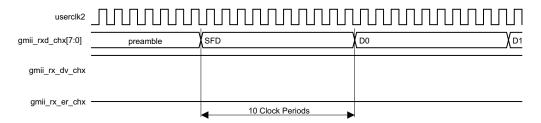

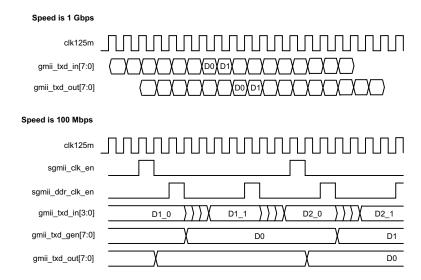

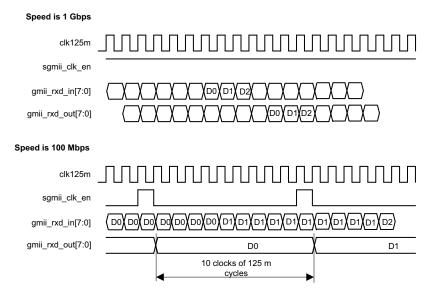

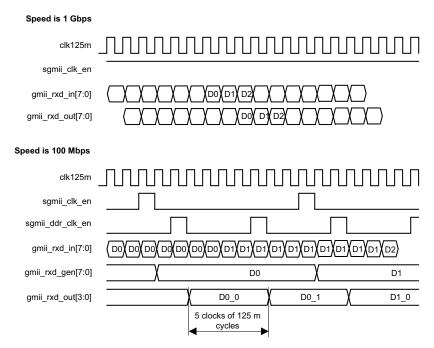

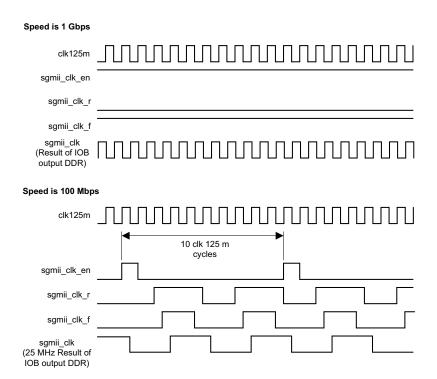

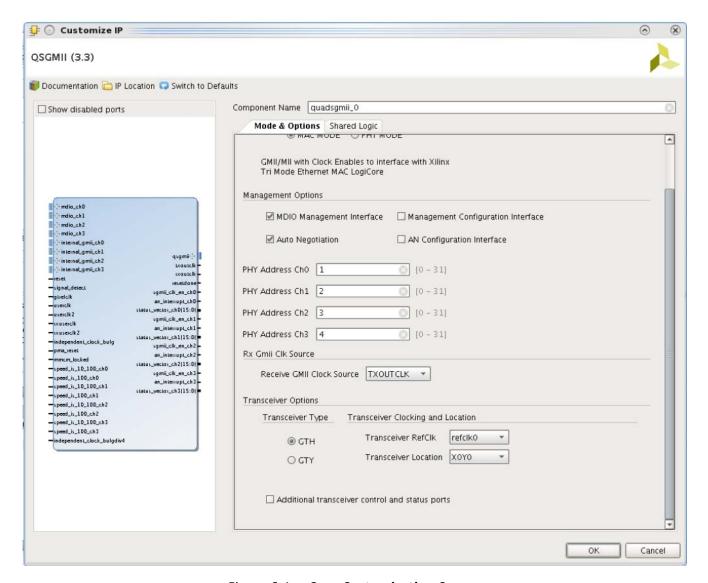

| gt0_pll1outclk_in          | Input                     | Valid only for Artix-7 families.<br>Indicates out clock from PLL1 of<br>GT Common.                                                                                                                 |