# QDMA Subsystem for PCI Express v1.0

# **Product Guide**

Vivado Design Suite

PG302 (v1.0) April 17, 2018

# Table of Contents

| Chapter 1: IP Facts                                      |     |

|----------------------------------------------------------|-----|

| Features                                                 | 4   |

| IP Facts                                                 | 5   |

| Chapter 2: Overview                                      | 7   |

| Glossary                                                 | 8   |

| QDMA Architecture                                        |     |

| QDMA Operations                                          | 17  |

| Applications                                             | 49  |

| Feature Support Roadmap                                  | 49  |

| Licensing and Ordering                                   | 50  |

| Chapter 3: Product Specification                         |     |

| Standards                                                |     |

| Minimum Device Requirements                              | 51  |

| Port Descriptions                                        | 52  |

| Register Space                                           | 67  |

| Context Structure Definition                             |     |

| Queue Entry Structure                                    | 111 |

| Chapter 4: Designing with the Subsystem                  | 114 |

| General Design Guidelines                                | 114 |

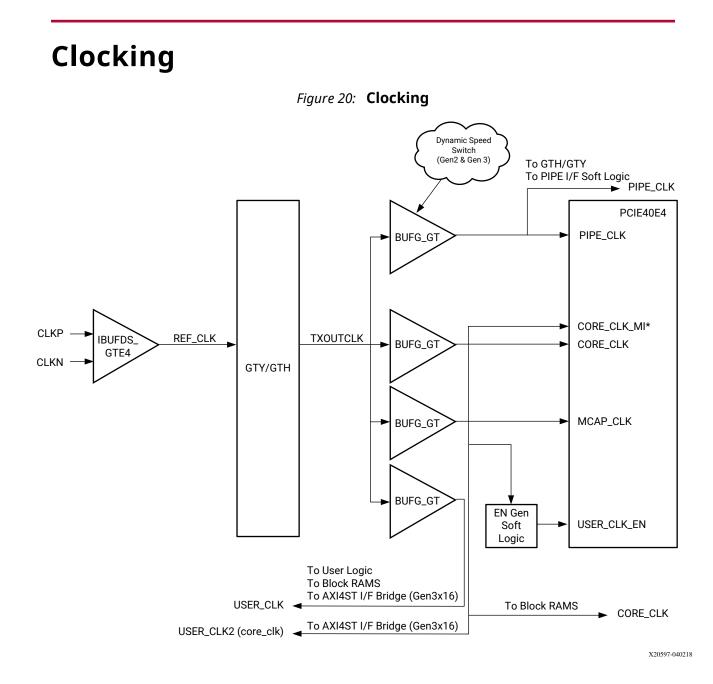

| Clocking                                                 | 115 |

| Chapter 5: Design Flow Steps                             | 117 |

| Customizing and Generating the Subsystem                 |     |

| Constraining the Subsystem                               | 129 |

| Simulation                                               |     |

| Synthesis and Implementation                             | 133 |

| Chapter 6: Example Design                                | 134 |

| AXI4 Memory Mapped and AXI Stream Default Example Design |     |

www.xilinx.com

| Appendix A: Upgrading                               |       |

|-----------------------------------------------------|-------|

| Comparing With DMA/Bridge Subsystem for PCI Express | . 140 |

| Appendix B: Debugging                               | 141   |

| Finding Help on Xilinx.com                          | . 141 |

| Debug Tools                                         | 142   |

| Hardware Debug                                      | 143   |

| Appendix C: Application Software Development        | 144   |

| Device Drivers                                      | 144   |

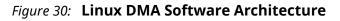

| Linux DMA Software Architecture (PF/VF)             | . 145 |

| Using the Driver                                    | . 145 |

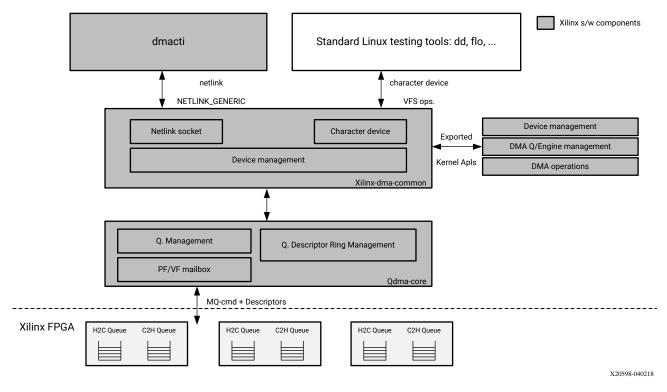

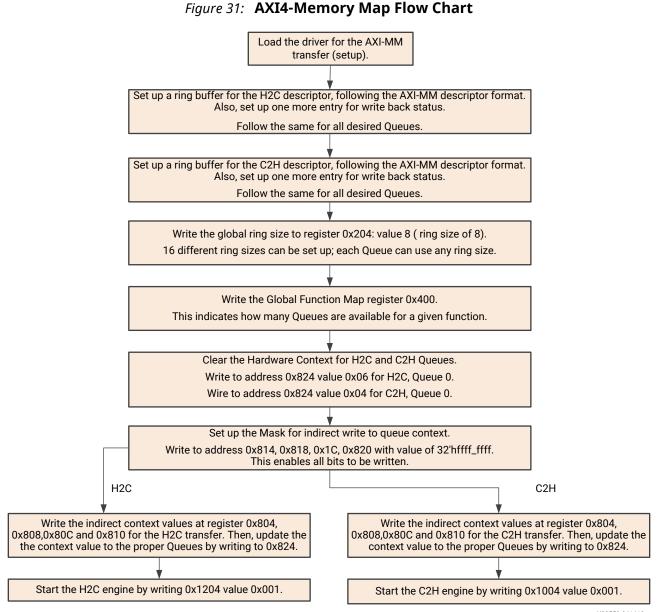

| Reference Software Driver Flow                      | 147   |

| Appendix D: Additional Resources and Legal Notices  | 154   |

| Xilinx Resources                                    | 154   |

| Documentation Navigator and Design Hubs             | . 154 |

| References                                          | 155   |

| Training Resources                                  | 155   |

| Revision History                                    |       |

| Please Read: Important Legal Notices                | . 156 |

# **IP** Facts

The Xilinx QDMA Subsystem for PCI Express<sup>®</sup> (PCIe<sup>®</sup>) implements a high performance DMA for use with the PCI Express<sup>®</sup> 3.x Integrated Block with the concept of multiple queues that is different from the DMA/Bridge Subsystem for PCI Express which uses multiple C2H and H2C channels.

### **Features**

- Supports PCIe Integrated Blocks in UltraScale+<sup>™</sup> devices, including Virtex<sup>®</sup> UltraScale+<sup>™</sup> devices with high bandwidth memory (HBM).

- Supports 64, 128, 256 and 512-bit data path.

- Supports x1, x2, x4, x8, or x16 link widths.

- Supports Gen1, Gen2, and Gen3 link speeds.

- Support for both the AXI4 Memory Mapped and AXI4-Stream interfaces per queue.

- 2K queue sets

- 2K H2C Descriptor rings.

- 。 2K C2H Descriptor rings.

- 。 2K C2H Write back rings.

- Supports Polling Mode (Status Descriptor Write Back).

- Interrupts

- 。 2K MSI-X vectors.

- Up to 8 MSI-X per function.

- Interrupt coalescing.

- C2H Stream interrupt moderation.

- C2H AXI4-Stream Completion (CMPT) interrupt entry coalescence.

- Descriptor and DMA customization through user logic

- Allows custom Descriptor format.

- Traffic Management.

- Supports SR-IOV up to 4 Physical Functions (PF) and 252 Virtual Functions (VF)

- Thin Hypervisor model.

- Allows only privileged/Physical functions to program contexts and registers.

- Function Level Reset (FLR) support.

- 。 Mailbox.

The 2018.1 version of this IP is marked as BETA. Not all features listed above are supported in the current release. For a list of features that are not supported, see Feature Support Roadmap. Some ports and the Descriptor Format will change in 2018.2. For more information, contact Xilinx Support.

### **IP Facts**

| LogiCORE IP Facts Table              |                                                                                |  |  |

|--------------------------------------|--------------------------------------------------------------------------------|--|--|

| Subsystem Specifics                  |                                                                                |  |  |

| Supported Device Family <sup>1</sup> | UltraScale+™                                                                   |  |  |

| Supported User Interfaces            | AXI4 Memory Map, AXI4-Stream, AXI4-Lite                                        |  |  |

| Resources                            | Not Provided                                                                   |  |  |

| Subs                                 | ystem                                                                          |  |  |

| Design Files                         | Encrypted System Verilog                                                       |  |  |

| Example Design                       | Verilog                                                                        |  |  |

| Test Bench                           | Verilog                                                                        |  |  |

| Constraints File                     | Xilinx Constraints File (XDC)                                                  |  |  |

| Simulation Model                     | Verilog                                                                        |  |  |

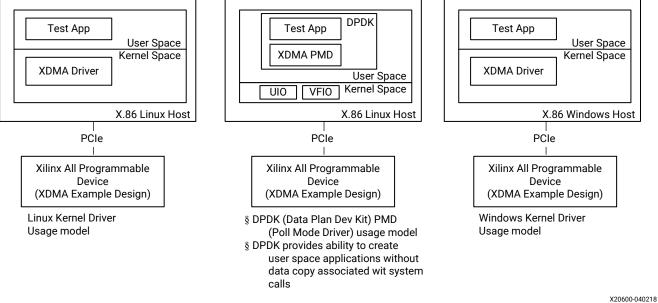

| Supported S/W Driver <sup>2</sup>    | Linux, Windows, DPDK Drivers                                                   |  |  |

| Tested Design Flows <sup>3</sup>     |                                                                                |  |  |

| Design Entry                         | Vivado Design Suite                                                            |  |  |

| Simulation                           | For supported simulators, see the Xilinx Design Tools:<br>Release Notes Guide. |  |  |

| Synthesis                            | Vivado Synthesis                                                               |  |  |

#### LogiCORE IP Facts Table

#### Support

Provided by Xilinx® at the Xilinx Support web page

Notes:

- 1. For a complete list of supported devices, see the Vivado IP catalog.

- 2. Standalone driver details can be found in AR 70928.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

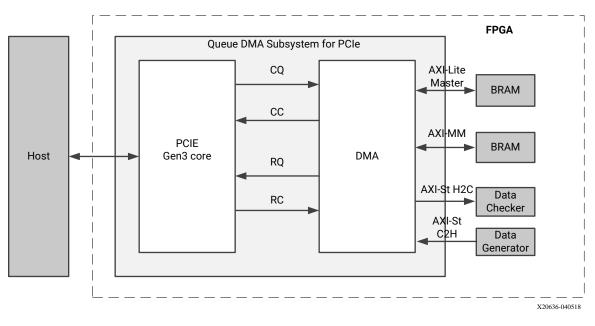

The Queue DMA (QDMA) subsystem provides PCI Express (PCIe) based high bandwidth and high packet rate by using the UltraScale+ Integrated Block for PCI Express in conjunction with an extensive DMA and bridge infrastructure. The primary mechanism for data transfer is bidirectional Endpoint ("Card") initiated transactions from Host to Card (H2C) and Card to Host (C2H). QDMA provides a secondary option of Host initiated memory accesses to AXI space on the card (Target Bridge – Master), and user logic initiated direct access to the Host (Target Bridge – Slave), including PCIe and AXI4 memory mapping. The primary user interfaces to the DMA engines are: AXI4 Memory Mapped (AXI-MM) and AXI4-Stream (AXI-ST); AXI4 Memory Mapped and AXI4-Lite for direct host or user logic initiated access; and several other functional interfaces. The user logic and software interact through the PCIe Base Address Registers (BAR) interfaces and AXI4-Lite Slave (AXI-L) register interfaces to set up and control the subsystem.

The QDMA Subsystem for PCIe offers a wide range of setup and use options, many selectable on a per-queue basis, such as memory mapped DMA or stream DMA, interrupt mode or polling, etc. The subsystem provides many options for customizing the Descriptor and DMA through user logic to provide complex traffic management capabilities.

The main difference between QDMA and other DMA offerings is the concept of Queues. The idea of Queues is derived from the "queue set" concepts of Remote Direct Memory Access (RDMA) from high performance computing (HPC) interconnects. These Queues can be individually configured by interface type, and they function in many different modes. Based on how the DMA descriptors are loaded for a single Queue, each Queue provides a very low overhead option for setup and continuous update functionality. By assigning Queues as resources to multiple PCIe Physical and Virtual Functions, a single QDMA core and PCI Express interface can be used across a wide variety of multi-function and virtualized application spaces.

A common usage example for the QDMA Subsystem for PCIe is to implement Data Center and Telco applications, such as Compute accelerations, Smart NIC, NVMe, RDMA-enabled NIC (RNIC), server virtualization, and NFV in the user logic. Multiple applications can be implemented to share the QDMA by assigning different queue sets and PCIe functions to each application. These Queues can then be scaled in the user logic to implement rate limiting, traffic priority, and custom work queue entry (WQE).

The QDMA Subsystem for PCIe can be used and exercised with a Xilinx provided QDMA reference driver, and then built out to meet a variety of application spaces.

# Glossary

The following table contains frequently used acronyms in this document.

#### Table 1: Glossary of Terms

| Acronym | Full Name                               |

|---------|-----------------------------------------|

| AXI-ST  | AXI4-Stream                             |

| H2C     | Host to Card                            |

| C2H     | Card to Host                            |

| TXQ     | Transfer Queue                          |

| RXQ     | Receive Queue                           |

| ТМ      | Traffic Manager                         |

| СМРТ    | C2H AXI4-Stream Completion              |

| FLR     | Function Level Reset                    |

| CQ      | Completer Request                       |

| сс      | Completer Completion                    |

| RQ      | Requester Request                       |

| RC      | Requester Completion                    |

| SRIOV   | Single root input/output virtualization |

| PF      | Physical function                       |

| VF      | Virtual function                        |

| PIDX    | Producer index pointer                  |

| CIDX    | Consumer index pointer                  |

| СТХТ    | Context                                 |

| HW      | Hardware                                |

| SW      | Software                                |

| QID     | Queue Identification                    |

| CSR     | Control/Status register                 |

| PFCH    | Prefetch Block                          |

## **QDMA** Architecture

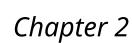

The following figure shows the block diagram of the QDMA Subsystem for PCIe.

Figure 1: QDMA Core

## PCIe CQ/CC

The PCIe CQ/CC modules receive and process TLP requests from the remote PCIe agent. This interface to the UltraScale+<sup>™</sup> Integrated Block for PCIe IP operates in address aligned mode. The module uses the BAR information from theIntegrated Block for PCIe IP to determine where the request should be forwarded. The three destinations for these requests are:

- the internal configuration module

- the AXI4 MM Bridge Master interface

- the AXI4-Lite Bridge Master interface

Non-posted requests are expected to receive completions from the destination, which are forwarded to the remote PCIe agent. For details, see the *UltraScale+ Devices Integrated Block for PCI Express LogiCORE IP Product Guide* (PG213).

## PCIe RQ/RC

The role of the PCIe RQ/RC interface is to generate PCIeTLPs on the RQ bus and process PCIe Completion TLPs from the RC bus. This interfaces to the UltraScale+<sup>™</sup> Integrated Block for PCIe<sup>®</sup> core operates in DWord aligned mode. With a 512-bit interface, straddling must also be enabled. While straddling is supported, all combinations of RQ straddled transactions as defined in the UltraScale+ Devices Integrated Block for PCI Express LogiCORE IP Product Guide (PG213) may not be implemented.

## **PCIe Configuration**

Several factors can throttle outgoing non-posted transactions. Outgoing non-posted transactions are throttled based on flow control information from the Integrated Block for PCIe<sup>®</sup> to prevent head of line blocking of posted requests. If Finite Completion Credits are not supported in the system or not configured in the Integrated Block for PCIe<sup>®</sup>PCIe IP, the DMA will meter non-posted transactions based on the PCIe Receive FIFO space. It is possible that non-posted transactions can be throttled by the number of outstanding PCIe tags.

### **Interrupt Module**

IRQ module aggregates interrupts from various sources into the UltraScale+<sup>™</sup> Integrated Block for PCle<sup>®</sup> core interface. The interrupt sources are queue-based interrupts, user interrupts and error interrupts.

Queue-based interrupts and User interrupts are allowed on the PFs and VF, but Error interrupts are allowed only for PFs. If the SRIOV is not enabled, each PF has the choice of MSI-X or MSI. If the SRIOV is enabled, only MSI-X is supported on all functions.

With support for MSI-X, MSI can be specified by attributes. Host system (Root Complex) will enable one or all of the interrupt types supported in hardware. If MSI-X is enabled, it takes precedence over the MSI.

The UltraScale+<sup>™</sup> Integrated Block for PCIe core offers eight interrupts per functions. The QDMA offers a novel way of aggregating interrupts from multiple queues on a given PCIe function to a single interrupt vector. Theoretically, all 2K queues can be mapped to single vectors. The QDMA offers 256 interrupt aggregation rings that can be flexibly allocated among 256 functions.

### **Descriptor Engine**

H2C and C2H descriptors are fetched by the Descriptor Engine. The descriptor engine maintains per queue context where it tracks the software PIDX, CIDX, BADDR, queue configurations, etc. It uses a round-robin algorithm for fetching the descriptors. The descriptor engine has separate buffers for H2C and C2H, and ensures it never fetches available space. In addition, it has only one descriptor fetch outstanding per queue. It also reorders the out-of-order completions so that descriptors for the queues are always in order.

The descriptor bypass can be enabled on a per queue basis and the fetched descriptors, after buffering, are sent to the respective bypass output interface instead of the H2C or C2H engine. In internal mode, based on context setting, the descriptors are sent to per H2C MM, C2H MM, H2C Stream or C2H Stream engines.

The descriptor engine is also responsible for generating the status descriptor for completion of DMA operations. With the exception of C2H Stream, all modes use this mechanism to convey completion of DMA operations, which allows the software to reclaim the descriptors and free up any associated buffers. This is indicated by the CIDX field of the status descriptor.

RECOMMENDED: If the queue is associated with interrupt aggregation, Xilinx recommends that you turn off this status descriptor, and instead get the DMA status from the interrupt aggregation ring.

To put a limit on the number of fetched descriptors, turn on crediting on a per queue basis. In this mode, the descriptor engine fetches the descriptors for available credit, and the total descriptors fetched per queue is limited to the credit provided. The user logic can return the credit through the dsc\_crdt interface.

To help the traffic manager prioritize the job, the available descriptor to be fetched (incremental PIDX value) of the PIDX update is sent to the user logic on the  $tm_dsc_sts$  interface. This prioritizes and optimizes the descriptor storage, and implements a DMA descriptor pull mode.

## H2C MM Engine

The H2C MM Engine moves data from host memory to card memory through H2C AXI-M interface. The engine generates reads on PCIe, splitting descriptors into multiple requests based on MRRS and 4K boundaries. Once completion data for a read request is received on PCIe, it generates a write on the H2C AXI-M interface. For source and destination addresses that are not aligned, the hardware will shift the data and split writes on AXI-M to prevent 4K alignment crossing. Each completed descriptor is checked to determine whether a writeback and/or interrupt is required.

For Internal mode, the queue descriptor engine delivers memory mapped descriptors straight to H2C MM engine. The user logic can also inject the descriptor to H2C bypass interface to move data from host to card memory. This gives the ability to do interesting things such as mixing the control and DMA commands in the same queue. Control information can be sent to a control processor indicating the completion of DMA operation.

### C2H MM Engine

The C2H MM Engine moves data from card memory to host memory through C2H AXI-M interface. The engine generates reads on the C2H AXI-M, splitting descriptors into multiple requests based on 4K boundaries. Once completion data for a read request is received, it generates a write on the Integrated Block for PCIe<sup>®</sup> interface. For source and destination addresses that are not aligned, the hardware will shift the data and split writes on the PCIe to obey MPS and prevent 4K alignment crossing. Each completed descriptor is checked to determine whether a writeback and/or interrupt is required.

For Internal mode, the queue descriptor engine delivers memory mapped descriptors straight to C2H MM engine. The user logic can also inject the descriptor to C2H bypass in interface to move data from host to card memory. This gives the ability to do interesting things such as mixing the control and DMA commands in the same queue. Control information can be sent to a control processor indicating the completion of DMA operation.

The PCIe Function number information will be provided by the AXI-MM <code>aruser</code> interface bus. A parity bus separate from the data and user bus is also provided for end-to-end parity support.

### **H2C Stream Engine**

H2C engine moves data from host to H2C Stream interface. For internal mode, queue descriptors are delivered straight to the H2C engine. For a queue in bypass, the descriptors can be reformatted and fed to bypass-in interface. The engine is responsible for breaking up DMA reads to MPS size, guarantee the space for completions, and also makes sure completions are reordered to make for correct H2C Stream interface ordering.

It has the buffering for up to 256 DMA reads and up to 32 Kbytes of data. There is an aligner to zero align the PCIe completion data to the AXI-ST interface. This allows every descriptor to be random offset and random length. Total length of all descriptors should be less than 64 KB.

For internal mode queues, each descriptor defines a single packet to be transferred to the H2C AXI-ST interface. A packet straddling multiple descriptors is not allowed, due to the lack of per queue storage. Multi-descriptor packets can be implemented using the descriptor bypass mode, where descriptors are delivered to user logic, to be stored on a per queue basis. When it has enough descriptors to form the packet, the H2C DMA can be initiated by delivering those descriptors, non-interleaved, with other H2C ST packet descriptors, through bypass in interface. Also, in bypass in the interface, the user logic can control the generation of the status descriptor.

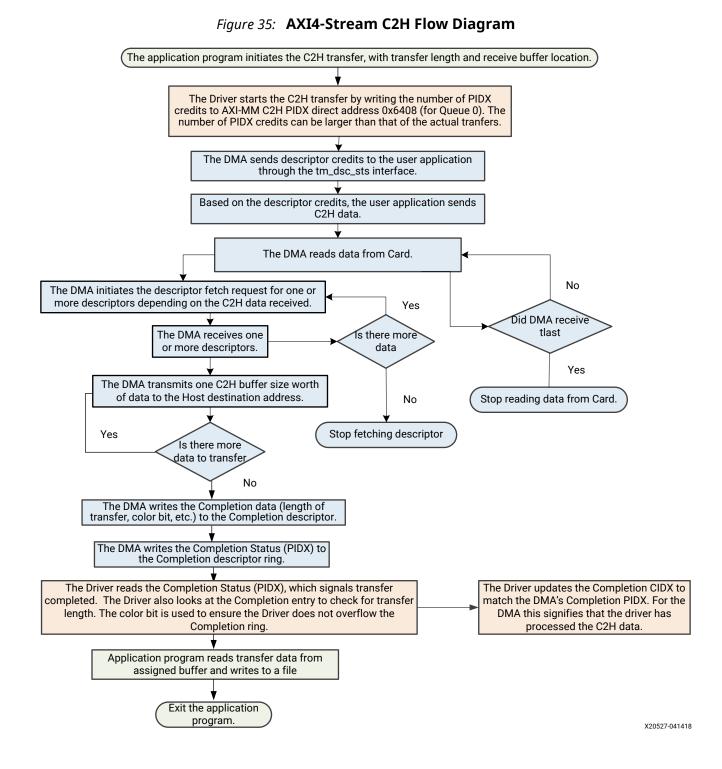

### **C2H Stream Engine**

THe C2H streaming engine is responsible for DMA writing the streaming packet from the user logic to the descriptors in C2H descriptor queue specified by the QID associated with the packet. It allows user logic to send up to 28B of metadata along with packet, which will be placed into C2H AXI-Stream Completion (CMPT) queue entry.

C2H has two major blocks to accomplish C2H streaming DMA, Prefetch Block (PFCH) cache and CMPT. The PFCH and CMPT will have per queue context to performance of its function, which the software is expected to program.

PFCH cache has three main modes, on a per queue basis, called cache mode, simple bypass and cached bypass mode.

- In **simple bypass mode**, a queue fetched descriptor is sent to user logic. User logic is then responsible for delivering the packet and associated descriptor in bypass interface. The ordering of the descriptors in bypass interface and C2H stream interface be maintained across queue among simple bypass mode queues.

- In cache mode and cached bypass mode, the PFCH module offers storage for 512 descriptors, which can be used by up to 64 different queues. In this mode, it controls the descriptors to be fetched by managing the C2H descriptor queue credit on demand based on received packets in the pipeline. One could turn on the pre-fetch mode per queue basis and that causes the descriptors to be opportunistically pre-fetched so that descriptors are available before the packet shows up and reduce the latency. The size of the buffer is fixed for a queue (PFCH context) and it can scatter the packet up to 7 descriptors. In cached bypass mode descriptor is bypassed to user logic for further processing such as address translation and sent back on the bypass in interface. This does not have the same restriction as simple bypass mode.

After the DMA write of the packet from the C2H stream interface is done, the CMPT packet from the CMPT interface is placed into the CMPT queue ID from the C2H stream interface. Queue state and configuration is stored in CMPT context per queue basis. It stores the base address, CIDX, PIDX, configurations in context. The software identifies the new CMPT entry being written based on the color bit or the based status descriptor. It also can be configured to generate the interrupt, status descriptor, or both based on the needs of the software. If the interrupts for multiple queues are aggregated into the interrupt aggregation ring, the status descriptor information is available in the interrupt aggregation ring as well.

CMPT has cache of 32 entries to coalesce the multiple smaller CMPT writes into 64B writes to improve the PCIe efficiency. At any time, it can simultaneously coalesce for 32 queues and any additional queue, needing to write CMPT entry, will cause the eviction of least recently used queue.

### Bridge Master AXI Memory Mapped Interface

The Bridge AXI-MM Master interface is used for high bandwidth access to AXI Memory Mapped space from the Integrated Block for PCIe<sup>®</sup>. The interface supports up to 32 outstanding reads and 32 outstanding writes. One or more PCIe BAR of any PF or VF can be mapped to master AXI-MM interface. This selection needs to be done at the point of configuring the IP. Function ID, bar ID (bar hit), VF group and VF group offset will be made available as part of aruser and awuser of the AXI-MM interface to help the user logic identify the source of memory access. Also, each host initiated access can be uniquely mapped to 64 bit AXI address space through PCIe to AXI BAR translation.

#### **Bridge Master AXI4-Lite Interface**

One or more PCIe BAR of any PF or VF can be mapped to the master AXI4-Lite interface. This selection needs to be done at the point of configuring the IP. Function ID, BAR ID (BAR hit), VF group, and VF group offset will be made available as part of aruser and awuser of the AXI4-Lite interface to help the user logic identify the source of memory access. Also, each of the host initiated access can be uniquely mapped to 64 bit AXI address space. Though the user bits are non-standard, without user bits the user logic may not be able to identify the intended address space. One outstanding read and one outstanding write are supported on this interface.

### **PCIe to AXI BARs**

For requests received in PCIe, a set of six 32-bit BARs for each Physical Function, one 32-bit BAR for EXPROM BAR on physical function, and six 32-bit BARs for Virtual Functions within the same Physical Function when SR-IOV is enabled are available. These BARs provide address translation to the AXI4 memory mapped spaced capability, interface routing, and AXI4 request attribute configuration. Pairs of BARs can be configured as a single 64-bit BAR. Each BAR can be configured to route its requests to the QDMA register space, the Bridge AXI4-Lite Master interface, or the Bridge AXI-MM Master interface.

The configurable AXI request attributes include:

- Address aperture to be translated: attr\_dma\_pciebar2axibar\_[0-5]\_len

- Translated address: attr\_dma\_pciebar2axibar\_[0-5]

A programming example can be found in the Address Translation section (Example 3) of AXI Bridge for PCI Express Gen3 Subsystem Product Guide (PG194).

#### **Request Memory Type**

The memory type can be set for each PCIe BAR through attributes attr\_dma\_pciebar2axibar\_\*\_cache\_pf\*.

- AxCache[0] is set to 1 for Modifiable and 0 for Non-modifiable.

- AxCache[1] is set to 1 for Cacheable and 0 for Non-cacheable.

- Allocate and Other Allocate are not supported.

### **Bridge Slave AXI Memory Mapped Interface**

The Bridge AXI-MM Slave Interface is used for high bandwidth memory transfers between the user logic and the Integrated Block for PCIe<sup>®</sup>. AXI to PCIe translation is supported through the AXI to PCIE BARs. The interface will split requests as necessary to obey PCIe MPS and 4K crossing requirements. Up to 32 outstanding read requests and up to 32 outstanding write requests are supported.

### **Bridge Slave AXI4-Lite Interface**

The AXI4-Lite slave interface is used to access the AXI Bridge and QDMA internal registers. The QDMA registers are virtualized for VFs and PFs. Example VFs and PFs can access different parts of the address space, and each has access to its own queues. To accommodate all modes, this interface provides a non-standard AXI4-Lite slave interface where the user logic can provide function ID, which gives the QDMA proper internal register access. One outstanding read request and one outstanding write request are supported.

### AXI to PCIe BARs

In the Bridge Slave interface, there are six BARs which can be configured as 32 bits or 64 bits. These BARs provide address translation from AXI address space to PCIe address space. The address translation is configured for each AXI BAR through attributes. The attributes include:

- Base address: attr\_dma\_axibar\_base\_[0-5]

- High address: attr\_dma\_axibar\_highaddr\_[0-5]

- Address size (32-bit or 64-bit): attr\_dma\_axibar\_as\_[0-5]

- Translated address: attr\_dma\_axibar\_[0-5]

A programming example can be found in the Address Translation section (Example 4) of AXI Bridge for PCI Express Gen3 Subsystem Product Guide (PG194).

### **SR-IOV Support**

The QDMA Subsystem for PCIe provides an optional feature to support the Single Root I/O Virtualization (SR-IOV). The PCI-SIG<sup>®</sup> Single Root I/O Virtualization and Sharing (SR-IOV) specification standardizes the method for bypassing the VMM involvement in datapath transactions and allows a single PCI Express<sup>®</sup> Endpoint to appear as multiple separate PCI Express Endpoints. SR-IOV classifies the functions as:

- **Physical Functions (PF)**: Full featured PCIe<sup>®</sup> functions which include SR-IOV capabilities among others.

- Virtual Functions (VF): PCIe functions featuring configuration space with Base Address Registers (BARs) but lacking the full configuration resources and controlled by the PF configuration. The main role of the VF is data transfer.

Apart from PCIe defined configuration space, QDMA Subsystem for PCI Express virtualizes data path operations, such as pointer updates for queues, and interrupts. The rest of the management and configuration functionality (slow path) is deferred to the physical function driver. The driver that does not have sufficient privileges needs to communicate with the privileged driver through mailbox provided in part of the QDMA Subsystem for PCI Express.

The security is an important aspect of virtualization. The QDMA Subsystem for PCI Express offers the following security functionality:

- QDMA allows only privileged PF to configure the context and registers.

- Drivers are allowed to do pointer updates only for the queue allocated to them.

- IOMMU can be turned on to check that the DMA is done by PFs and VFs. The ARID comes from queue context programmed by privileged function.

Any PF or VF can communicate to a PF (not itself) through mailbox. Each function implements one 64B inbox and 64B outbox. These mailboxes will be visible to the driver in the DMA BAR (typically BAR0) of its own function. At any given time any function can have one outgoing mailbox and incoming mailbox message outstanding.

The QDMA Subsystem for PCI Express supports all the PCIe defined resets, such as link down reset, hot reset and FLR (supports only Quiesce mode).

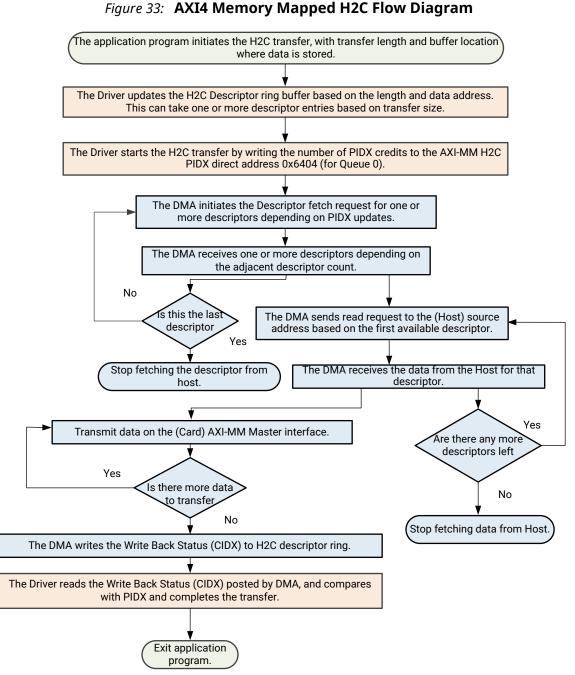

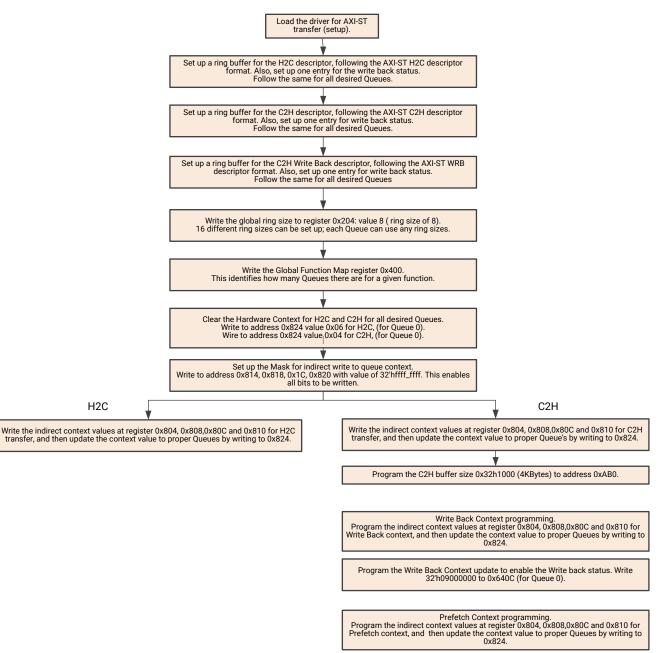

# **QDMA Operations**

### **Theory of Rings**

Multi-queue DMA uses RDMA model queue pairs to allow RNIC implementation in the user logic. Each queue set consists of Host to Card (H2C) Ring, Card to Host (C2H) Ring, and a C2H Stream Completion (CMPT) Ring.

H2C and C2H rings are always written by the driver/software. The hardware is always read from the Queue set (QSet0 - QSet2047). H2C carries the descriptors for the DMA read operations. C2H carries the descriptors for the DMA write operations.

In all internal modes, H2C descriptors carry address and length, which is also called scatter gather descriptor. It supports 32 bits of metadata that can be passed from software to hardware along with every packet. The descriptor can be of memory mapped (carries host address and card address) or streaming (only host address). Through descriptor bypass, you can define the complex descriptor format where software is permitted the concept of immediate data and more metadata along with packet.

Memory Mapped descriptors for C2H queue consist of card address, host address and the length of transfer. In streaming mode except for simple bypass mode, descriptors carry only the host address and the buffer size of the descriptor passed by the driver, which is expected to be of fixed size for the whole queue.

The software advertises valid descriptors to H2C queue and C2H queue by writing its producer index (PIDX) to the hardware. H2C and C2H descriptors can be reclaimed upon completion of DMA operation through the status descriptor. The status descriptor is the last entry of the descriptor ring in a queue set. The status descriptor carries the consumer index (CIDX) of the hardware so that the driver knows when to reclaim the descriptor and deallocate the buffers in the host.

For C2H stream mode, C2H descriptors will be reclaimed based on the queue entry. Typically it carries one entry per C2H packet, indicating of one or more C2H descriptors consumed. The CMPT queue entry carries enough information for software to claim all the descriptors consumed. Through external logic it can be extended to carry other kinds of completions or information to host.

CMPT entry written to the ring can be detected by the driver using color bit in the descriptor or the status descriptor at the end of the CMPT queue ring. This CMPT descriptor can carry meta data for C2H stream packet and also it can be custom completion or immediate for user application. The CMPT queue can be detected by the driver using a color bit in the descriptor or last descriptor of the CMPT queue reserved as status descriptor. The CMPT queue supports two formats, internal or user. In internal format, it conveys metadata, color bit, descriptor format, error and packet length. In the user format, the length is the responsibility of the user logic.

|             | Driver Obje | ects     |

|-------------|-------------|----------|

| H2C/<br>TXQ | C2H/<br>RXQ | Qset0    |

|             |             |          |

|             | CMPT/CQ     |          |

|             |             |          |

| H2C/<br>TXQ | C2H/<br>RXQ | Qset2047 |

|             | CMPT/CQ     |          |

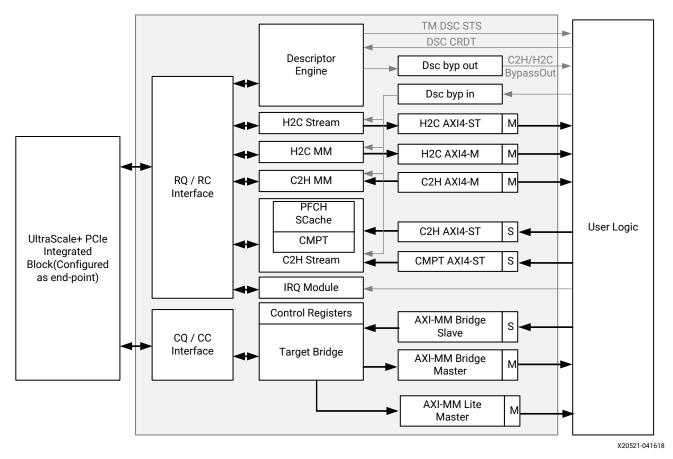

#### H2C and C2H Circular Buffer Queues

#### Figure 3: H2C and C2H Circular Buffer Queues

The above figures shows the H2C and C2H fetch operation.

- For H2C, the application data gets written to a buffer, the software forms the descriptor and posts it to the copy of the Producer Index (PIDX) location in the descriptor ring. (For C2H, the driver forms the descriptor with the buffer for the hardware to the DMA packet.)

- The software sends the posted write for the associated Queue ID (QID) with its current PIDX value.

- Upon reception of PIDX, updates the hardware, which issues DMA read to address BASE +CIDX.

- The read completion from the host memory is delivered to the H2C Engine or C2H Engine. In case of bypass, it will be sent out.

- Whenever the descriptor processing is complete, only for the H2C Status Descriptor with CIDX will be written to allow the driver to reuse the descriptors and deallocate buffers.

For C2H, the fetch operation is implicit through the write back ring.

*Note*: C2H operates in pull mode of the descriptor, and H2C can be either pull or push mode.

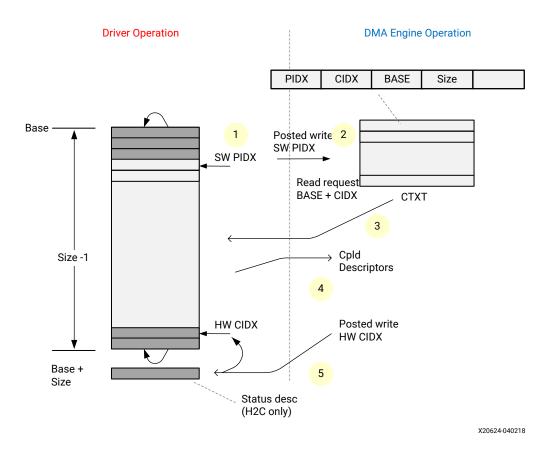

#### **C2H DMA Write Back**

#### Figure 4: C2H DMA Write Back

When C2H receives a packet from the user logic, it gets the DMA buffer from the Fetch Engine and the DMA writes the payload to one or more buffers. After that, write back operation begins.

Simple flow of DMA Write back queue operation.

- The DMA write completion descriptor will be written to address BASE+PIDX.

- Posted write to status descriptor with PIDX.

- If in interrupt mode, generate the interrupt.

- The software identifies the new descriptor being written, updates the SW CIDX, and reads any buffers associated with the descriptor.

- Sends posted write back to queue DMA with SW CIDX. This allows the hardware to reuse the descriptors again.

### **Descriptor Bypass**

The Descriptor bypass mode provides immediate data with efficient traffic management. It also provides address translation of descriptors. The C2H Descriptor bypass mode allows for custom write back format. The Descriptor bypass mode can be used with RoCE/iWARP Send queues. In Descriptor bypass mode, descriptors are pushed in from the soft logic and stored in-order in the descriptor buffer based on the channel to which the descriptor belongs. The descriptor bypass can be enabled on a per channel basis. The descriptor bypass is controllable through registers.

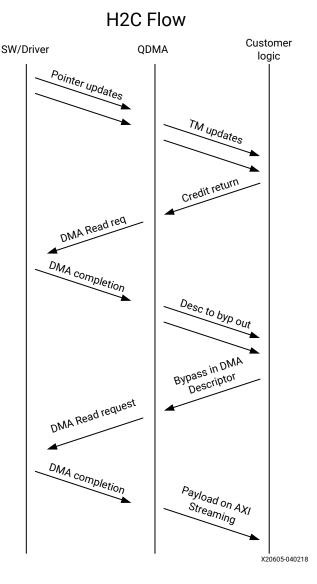

#### H2C Descriptor Bypass

Figure 5: H2C Descriptor Bypass Flow

When Descriptor Bypass for Read (H2C) is enabled, these descriptor bypass ports are present. For port descriptions, seeQDMA Descriptor Bypass Input Ports and QDMA Descriptor Bypass Output Ports.

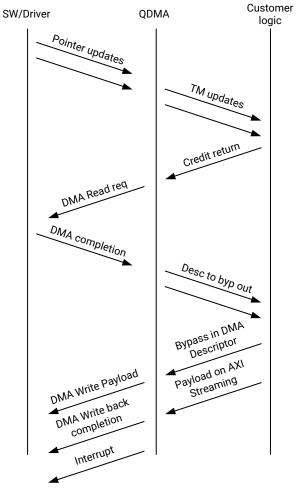

#### **C2H Descriptor Bypass**

The C2H Bypass mode supports two bypass input modes:

- **Simple mode**: Customer logic takes full responsibility of returning descriptor in sync with incoming packet.

- Cache mode: This mode makes use of cache in QDMA where up to 512 C2H descriptors can be cached for 64 queues.

The C2H descriptor bypass flow is as shown below.

C2H Flow

X20604-040218

For port descriptions, see QDMA Descriptor Bypass Input Ports and QDMA Descriptor Bypass Output Ports.

### C2H Stream

#### C2H Descriptor

The C2H descriptors can be from the Fetch Engine or C2H Bypass Input interfaces. The descriptors from the Fetch Engine are in cache mode. The PFCH block keeps the order of the descriptors. The descriptors from the C2H Bypass Input interfaces have one interface for the simple mode, and another interface for the cache mode. For the simple mode, the user application keeps the order of the descriptors. For the cache mode, the PFCH block keeps the order of the descriptors.

The Prefetch Context has a bypass bit. When it is 1'b1, the user application sends the credits for the descriptors. When it is 1'b0, the PFCH block sends the credits for the descriptors.

The Descriptor Context has a desc\_byp bit. When it is 1'b1, the Fetch Engine sends out the descriptors on the C2H Bypass Output interface. The user application convert it and loops it back to the QDMA Subsystem for PCIe on the C2H Bypass Input interface. When it is 1'b0, the Fetch Engine sends the descriptors to the PFCH block directly.

|        | c2h_byp_in  | desc_ctxt.desc_byp | pfch_ctxt.bypass |

|--------|-------------|--------------------|------------------|

| Case 1 | simple mode | 1                  | 1                |

| Case 2 | cache mode  | 1                  | 0                |

| Case 3 | cache mode  | 0                  | 0                |

Three cases per queue basis are supported.

For Case 1, the Fetch Engine sends the descriptors out on the C2H Bypass Out interface. The user application converts the descriptor and loops it back to the QDMA on the simple mode C2H Bypass Input interface. The user application sends the credits for the descriptors, and it also keeps the order of the descriptors.

For Case 2, the Fetch Engine sends the descriptors out on the C2H Bypass Output interface. The user application converts the descriptor and loops it back to the QDMA on the cache mode C2H Bypass Input interface. The PFCH block sends the credits for the descriptors, and it keeps the order of the descriptors.

For Case 3, the Fetch Engine sends the descriptors to the PFCH block. The PFCH block sends out the credits for the descriptors and keeps the order of the descriptors. In this case, the descriptors do not go out on the C2H Bypass Output and do not come back on the C2H Bypass Input interfaces.

#### C2H DMA Write Engine

The C2H DMA Write Engine block gets the C2H streaming data packet from the user application. It breaks the data packet into smaller TLP packets and sends them to the integrated block for PCIe.

#### **C2H** Completion

When the user application sends the C2H data packet to the DMA, it also sends the CMPT packet. The CMPT packet has two formats: Standard Format and User Format.

The following is the CMPT packet from the user application in the Standard Format when the data format bit is 1'b0.

| Name         | Size             | Index    |

|--------------|------------------|----------|

| User defined | 44 bits-236 bits | [255:20] |

| rsvd         | 8                | [19:12]  |

| Qid          | 11               | [11:1]   |

| Data format  | 1                | [0:0]    |

The following is the CMPT packet from the user application in the User Format when the data format bit is 1'b1.

| Name         | Size             | Index   |

|--------------|------------------|---------|

| User defined | 61 bits-253 bits | [255:3] |

| rsvd         | [2:1]            | [2:1]   |

| Data format  | [0:0]            | [0:0]   |

The CMPT packet has three types: 8B, 16B, or 32B. When it is 8B or 16B, it only needs one pump of the data. When it is 32B, it needs two pumps of data. Each data pump is 128bits.

When the DMA write of the data packet is done, the QDMA writes the CMPT packet into the CMPT queue. Besides the user defined data, it also includes some other information, such as error, color, and the length onto the CMPT packet.

The following is the CMPT packet inside the CMPT queue in the User Format when the data format bit is 1'b1.

| Name         | Size             | Index   |

|--------------|------------------|---------|

| User defined | 61 bits-253 bits | [255:3] |

| err          | 1                | [2:2]   |

| color        | 1                | [1:1]   |

| Name        | Size | Index |

|-------------|------|-------|

| Data format | 1    | [0:0] |

The following is the CMPT packet inside the CMPT queue in the Standard Format when the data format bit is 1'b0.

| Name         | Size             | Index    |

|--------------|------------------|----------|

| User defined | 44 bits-236 bits | [255:20] |

| Len          | 16               | [19:4]   |

| rsvd         | 1                | [3:3]    |

| err          | 1                | [2:2]    |

| color        | 1                | [1:1]    |

| Data format  | 1                | [0:0]    |

#### **C2H Interrupt Moderation**

The QDMA Subsystem for PCIe provides a means to moderate the C2H completion interrupts. You can choose from one of the 7 modes to regulate the C2H completion interrupts. The selected mode for a queue is stored in the QDMA Subsystem for PCIe in the C2H completion ring context for that queue. After a mode has been selected for a queue, the driver can always select another mode when it sends the completion ring CIDX update to QDMA.

The C2H completion interrupt moderation is handled by the completion engine inside the C2H engine. The completion engine stores the C2H completion ring contexts of all the queues. It is possible to individually enable or disable the sending of interrupts and C2H completion status descriptors for every queue and this information is present in the completion ring context.

The QDMA Subsystem for PCIe keeps only one interrupt outstanding per queue. This policy is enforced by QDMA even if all other conditions to send an interrupt have been met for the mode. The way the QDMA Subsystem for PCIe considers an interrupt serviced is by receiving a CIDX update for that queue from the driver.

The basic policy followed in all the interrupt moderation modes is that when there is no interrupt outstanding for a queue, the QDMA Subsystem for PCIe keeps monitoring the trigger conditions to be met for that mode. Once the conditions are met, an interrupt is sent out. While the QDMA subsystem is waiting for the interrupt to be served, it remains sensitive to interrupt conditions being met and remembers them. When the CIDX update is received, the QDMA subsystem evaluates whether the conditions are still being met. If they are still being met, another interrupt is sent out. If they are not met, no interrupt is sent out and QDMA resumes monitoring for the conditions to be met again.

Note that the interrupt moderation modes that the QDMA subsystem provides are not necessarily precise. Thus, if the user application sends two C2H packets with an indication to send an interrupt, it is not necessary that two interrupts will be generated. The main reason for this behavior is that when the driver is interrupted to read the completion ring, and it is under no obligation to read exactly up to the completion for which the interrupt was generated. Thus, the driver may not read up to the interrupting completion descriptor, or it may even read beyond the interrupting completion descriptor if there are valid descriptors to be read there. This behavior requires the QDMA Subsystem for PCIe to re-evaluate the trigger conditions every time it receives the CIDX update from the driver.

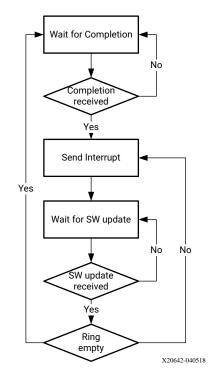

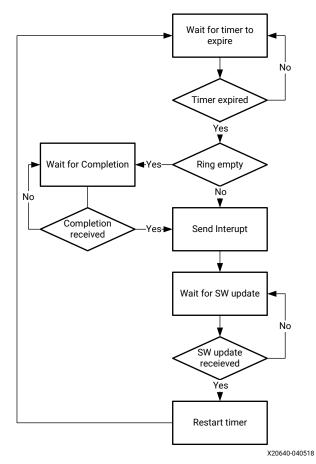

The detailed description of each mode is given below:

- **TRIGGER\_EVERY:** This mode is the most aggressive in terms of interruption frequency. The idea behind this mode is to send an interrupt whenever the completion engine determines that an unread completion descriptor is present in the completion ring.

- **TRIGGER\_TIMER:** The QDMA Subsystem for PCIe maintains a timer for each QID running with this mode. The idea behind this mode is to interrupt the driver after a specific interval of time. These intervals of time can be configured by the driver. Every QID can be configured to use one of 16 programmable timer values.

- **TRIGGER\_USER:** The QDMA Subsystem for PCIe provides the User a way to send a C2H packet to the subsystem with an indication to send out an interrupt when the subsystem is done sending the packet to the host. This allows the user application to perform interrupt moderation when the TRIGGER\_USER mode is set.

- **TRIGGER\_USER\_COUNT:** This mode allows the QDMA Subsystem for PCIe to generate an interrupt when the number of unread completion descriptors in the completion ring exceeds a certain threshold. This threshold is driver programmable on a per-queue basis. When this mode is set, the QDMA Subsystem for PCIe sends an interrupt whenever it determines that the number of unread completion descriptors in the completion queue has exceeded the threshold value. In this mode, the subsystem remains sensitive to any requests for interrupts sent by the user application along with the C2H packet.

- **TRIGGER\_TIMER\_COUNT:** This mode makes The QDMA Subsystem for PCIe generate interrupts when either sufficient time has passed or when the number of unread completion descriptors in the completion queue has exceeded the threshold value.

- **TRIGGER\_USER\_TIMER:** In this mode, the QDMA Subsystem for PCIe remains sensitive to any requests for interrupts sent by the user application along with the C2H packet in addition to interrupting the host if a certain amount of time has passed.

- **TRIGGER\_DIS:** In this mode, the QDMA Subsystem for PCIe does not send C2H completion interrupts in spite of them being enabled for a given queue. The only way that the driver can read the completion ring in this case is when it regularly polls the ring. The driver will have to make use of the color bit feature provided in the completion ring when this mode is set as this mode also disables the sending of any completion status descriptors to the completion ring.

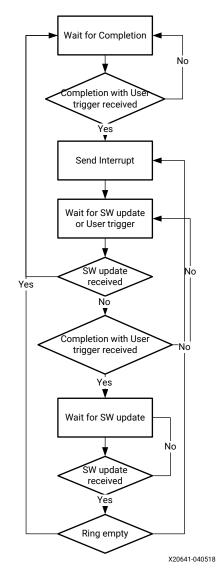

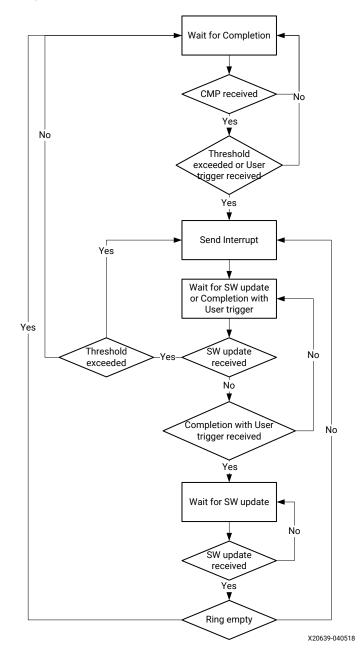

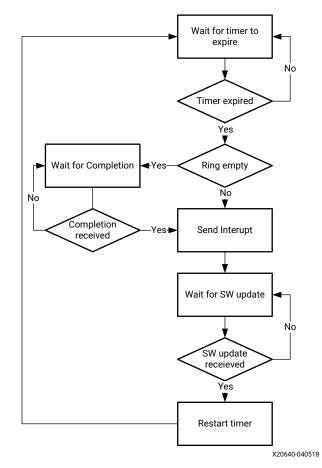

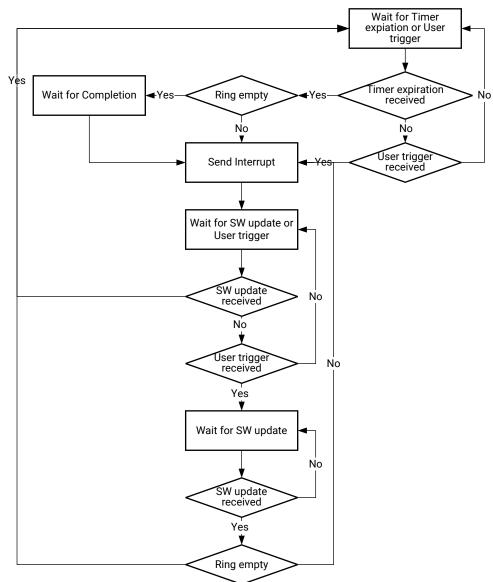

The followings are the flow charts of different modes.

#### Figure 7: Flowchart for EVERY Mode

#### Figure 8: Flowchart for TIMER Mode

#### Figure 9: Flowchart for USER Mode

Figure 10: Flowchart for USER\_COUNT Mode

#### Figure 11: Flowchart for TIMER\_COUNT Mode

Figure 12: Flowchart for USER\_TIMER Mode

X20637-040518

#### **C2H** Timer

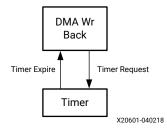

Figure 13: C2H Timer

The C2H timer is a trigger mode in the WRB context . It supports 2048 queues, and each queue has its own timer. When the timer expires, a timer expire signal is sent to the write back module. If multiple timers expire at the same time, then they are sent out in a round robin manner.

#### Reference Timer

The reference timer is based on the timer tick. The register QDMA\_C2H\_INT\_TIMER\_TICK defines the value for a timer tick. 16 QDMA\_C2H\_TIMER\_CNT [7:0] registers have the timer counts based on the timer tick. The timer\_ix is the index to the QDMA\_C2H\_TIMER\_CNT registers.

#### Timer Quadrant

The Timer Quadrant allocates the timer injections into four quadrants. It stalls the reference timer when the previous quadrant still has active injections that are not yet expire. This guarantees the new timer injection do not conflict with the old timer injections.

| C2H Registers           | Access Type | Description                                                               |

|-------------------------|-------------|---------------------------------------------------------------------------|

| QDMA_C2H_INT_TIMER_TICK | RW          | The value of a timer tick.                                                |

| QDMA_C2H_TIMER_CNT      | RW          | 16 registers. The bit [7:0] has the timer counts based on the timer tick. |

#### SRIOV Support

The QDMA Subsystem for PCIe provides an optional feature to support the Single Root I/O Virtualization and Sharing (SR-IOV) based Virtualization.

The PCI-SIG<sup>®</sup> Single Root I/O Virtualization and Sharing (SR-IOV) specification (available from *PCI-SIG Specifications*(www.pcisig.com/specifications) standardizes the method for bypassing the VMM involvement in datapath transactions and allows a single PCI Express<sup>®</sup> endpoint to appear as multiple, separate PCI Express endpoints. SR-IOV classifies the functions as:

- **Physical Functions (PF):** Full featured PCIe<sup>®</sup> functions which include SR-IOV capabilities among others.

- Virtual Functions (VF): PCIe functions featuring the configuration space with Base Address Registers (BARs) but lacking the full configuration resources and controlled by the PF configuration. The main role of the VF is data transfer.

When the SR-IOV capability is enabled during the QDMA Subsystem for PCIe configuration, the subsystem allocates dedicated hardware resource which provides each VF independent DMA (optional), memory space and interrupts. The VF configuration space can be mapped to the virtual systems memory which enables direct access to the VF physical address including allowing the DMA access to the virtual system using Intel<sup>®</sup> Virtualization Technology for Directed I/O (VT-d). VT-d is responsible for I/O device assignments, the DMA, and Interrupt remapping. Moreover, in order to protect VMs from bad memory accesses, IOMMU must be enabled at the Host.

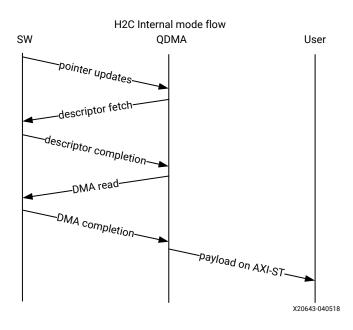

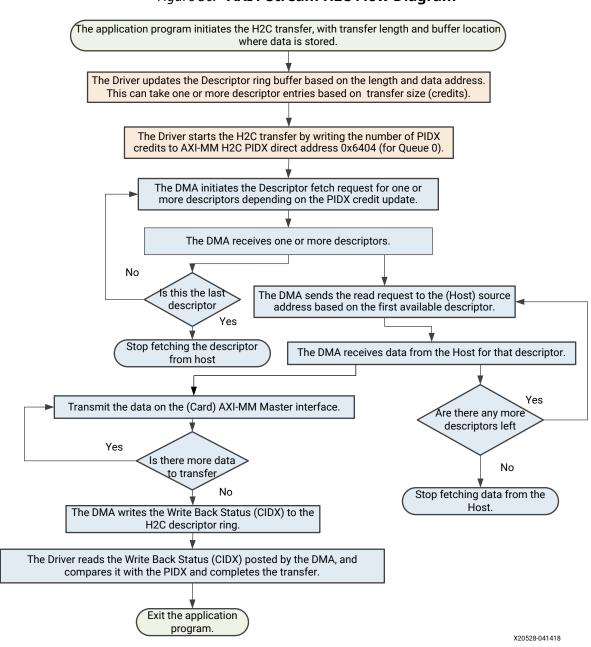

### H2C Stream

The H2C engine is responsible for transferring data from the host and deliver it to the user logic. The H2C engine operates on the H2C descriptors. Each descriptor specifies the start address and the length of the data to be transferred to the user logic. The H2C engine parses the descriptor and issues read requests to the host over PCIe, splitting the read requests at MRRS boundary. There can be up to 256 requests outstanding to hide the host read latency. The H2C engine implements a buffer of 32 KB to re-order the TLPs as they come back. Data is issued to the user logic in order of the requests sent to PCIe.

Based on the context that the H2C engine receives along with the descriptor, it could additionally be asked to send a status write back to the host once it is done issuing data to the user logic.

The H2C engine can be operated in two modes:

- Internal mode: In internal mode, after the descriptor is fetched from the host, it is fed straight to the H2C engine for processing. In internal mode, each descriptor transfers exactly one packet of data.

- **Bypass mode**: In bypass mode, after the descriptors are fetched from the host, they are sent to the user logic. The bypass logic stores these descriptors and then sends them back to the QDMA Subsystem for PCIe through the descriptor bypass-in interface. The descriptors are then fed to the H2C engine for processing.

The following are the advantages of using the bypass mode:

- The user logic can have a custom descriptor format.

- Immediate data can be passed from the software to the user logic without DMA operation.

- The user logic can do traffic management by sending the descriptors to the QDMA Subsystem for PCIe when ready to sink all the data.

- Performs address translation.

The following figures show the internal mode and bypass mode flows.

#### Figure 14: H2C Internal Mode Flow

H2C bypass mode flow

When using the H2C engine in internal mode, each descriptor transfers exactly one packet of data. The maximum length of the packet can be 64K-1 bytes. The descriptor format in internal mode is shown below:

| Name   | Size (b) | Index    | Description                   |

|--------|----------|----------|-------------------------------|

| addr_h | 32       | [127:96] | Upper 32 bits of the address. |

| addr_l | 32       | [95:64]  | Lower 32 bits of the address. |

| rsv1   | 16       | [63:48]  | Reserved                      |

| len    | 16       | [47:32]  | Length of data to the DMA.    |

| rsv2   | 32       | [31:0]   | Reserved                      |

When using the H2C engine in bypass mode, each packet can span over multiple descriptors. The maximum total length of the packet still needs to be 64K-1 bytes. In this mode, it is required that the user will send the batch of descriptors defining a packet to QDMA without interleaving with descriptors from other queues. The descriptor format used in this mode has two additional bits to specify whether a descriptor is the Start-Of-Packet or End-Of-Packet descriptor. The middle descriptors must have SOP=EOP=0. It is legal to have a descriptor with SOP=EOP=1. Shown below is the descriptor format in the bypass mode:

| Name   | Size (b) | Index    | Description                       |

|--------|----------|----------|-----------------------------------|

| addr_h | 32       | [127:96] | Upper 32 bits of the address.     |

| addr_l | 32       | [95:64]  | Lower 32 bits of the address.     |

| rsv1   | 14       | [63:50]  | Reserved                          |

| еор    | 1        | [49]     | Descriptor marks end of packet.   |

| sop    | 1        | [48]     | Descriptor marks start of packet. |

| len    | 16       | [47:32]  | Length of data to the DMA.        |

| rsv2   | 32       | [31:0]   | Reserved                          |

When feeding in the descriptor on the bypass in interface, the user logic can request that the QDMA Subsystem for PCIe sends a status write back to the host when it is done fetching the data from the host. The user logic can also request that a status be issued when the DMA is done. These behaviors can be controlled by using the sdi and mrkr\_req bits in the bypass in interface. Refer to the QDMA Descriptor Bypass Input Ports description for details.

An alternative H2C descriptor format can be used. This is done by resetting the use\_stm\_dsc\_format attribute. This alternative descriptor format has the same information as the ones described above except the fields are in different locations. The table below describe this other descriptor format.

| Name | Ssize (b) | Index    | Description |

|------|-----------|----------|-------------|

| rsv2 | 34        | [127:94] | Reserved    |

| Name | Ssize (b) | Index   | Description                       |

|------|-----------|---------|-----------------------------------|

| еор  | 1         | [94]    | Descriptor marks end of packet.   |

| sop  | 1         | [93]    | Descriptor marks start of packet. |

| rsv1 | 13        | [92:80] | Reserved                          |

| len  | 16        | [79:64] | Length of data to the DMA.        |

| addr | 64        | [63:0]  | 64b address.                      |

The H2C engine has a data aligner that aligns the data to OB boundary before issuing it to the user logic. When in bypass mode, each descriptor defining the packet can have an arbitrarily aligned address and an arbitrarily aligned length. The aligner aligns and packs the data so that a continuous stream of data starting a OB boundary is issued to the user logic.

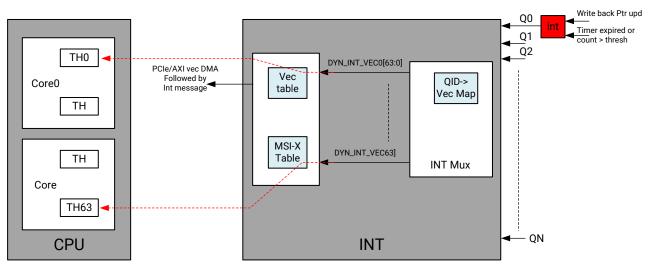

# **QDMA Interrupts**

The QDMA Subsystem for PCIe supports up to 256 MSI-X vectors, with up to 8 MSI-X vectors per function. Legacy interrupts are not supported in the subsystem. A single MSI-X vector can be used to support multiple queues. Each vector has an associated Interrupt Ring. The QID and status of queues requiring service are written into the Interrupt Ring. There can be at most one entry for each QID in the ring. When a PCIe MSI-X interrupt is received by the Host, the software reads the Interrupt Ring to determine which queues need service. Mapping of queues to vectors is programmable. It has independent table programming per PF. It supports all interrupt modes for non-SR-IOV, and MSI/MSI-X for SRIOV.

### Queue-Based Interrupt Visualization

Figure 16: Queue-Based Interrupt Visualization

X20599-041318

### Interrupt Flow

When the H2C or C2H interrupt occur, the QID to vector RAM is read. The RAM has 2K entries to support up to 2K queues. It also includes two portions: one for H2C, and one for C2H. It maps the QID to the vector and indicates if it is direct interrupt mode or indirect interrupt mode. If it is direct interrupt mode, the vector is used to generate the PCIe MSI-X message. If it is indirect interrupt mode, the vector is used as the index of the Interrupt Context RAM.

The following is the data in the QID to vector RAM.

| Signals     | Bits | Owner  | Description                                                                      |

|-------------|------|--------|----------------------------------------------------------------------------------|

| H2c_en_coal | 1    | Driver | 1'b1: indirect interrupt mode.<br>1'b0: direct interrupt mode for H2C interrupt. |

| H2c_vector  | 8    | Driver | Interrupt vector for the H2C interrupt.                                          |

| C2h_en_coal | 1    | Driver | 1'b1: indirect interrupt mode.<br>1'b0: direct interrupt mode for C2H interrupt. |

| C2h_vector  | 8    | Driver | Interrupt vector for the C2H interrupt.                                          |

**Direct Interrupt mode**: For direct interrupt mode, the PCIe MSI-X message is out directly.

**Indirect Interrupt mode**: For indirect interrupt mode, it supports up to 256 Interrupt Rings and up to 256 functions. Each function can use one Interrupt Ring or multiple Interrupt Rings.

In the indirect interrupt mode, the QDMA processes the interrupt with the following steps.

- Look up the QID to vector RAM.

- Look up the Interrupt Context RAM.

- Writes to the Interrupt Ring.

- Send out the PCIe MSI-X message.

The Interrupt Context RAM includes the information of the Interrupt Ring. It has 256 entries to support up to 256 Interrupt Rings.

Each entry of the Interrupt Context RAM has the following information for the associated Interrupt Ring.

| Signals | Bits | Owner | Description                                             |

|---------|------|-------|---------------------------------------------------------|

| Pidx    | 12   | DMA   | Cumulative pointer of the Interrupt Ring entry written. |

| Signals             | Bits | Owner  | Description                                                                                                                                     |

|---------------------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Page_Size           | 3    | Driver | Size of the Interrupt Ring.<br>0: 4KB<br>1: 8KB<br>2: 12KB<br>3: 16KB<br>4: 20KB<br>5: 24KB<br>6: 28KB<br>7: 32KB                               |

| Baddr_4k            | 52   | Driver | Base Addr[63:12]. The Interrupt Ring in memory is 4K aligned.                                                                                   |

| Color               | 1    | DMA    | This bit inverts every time PIDX wraps around.                                                                                                  |

| Int_st              | 1    | DMA    | Interrupt state.<br>0: WAIT_TRIGGER<br>1: ISR_RUNNING                                                                                           |

| Dbg_small_page_size | 1    | Driver | For debug purposes, supports some smaller ring<br>sizes.<br>{Dbg_small_page_size, Page_Size}:<br>4'b1000: 128B<br>4'b1001: 512B<br>4'b1010: 1KB |

| Vec                 | 5    | Driver | Interrupt Vector                                                                                                                                |

| Vld                 | 1    | Driver | Valid                                                                                                                                           |

After looking up the Interrupt Context RAM, it then writes to the Interrupt Ring. It also updates the Interrupt Context RAM with the new PIDX, color, and the interrupt state.

Each entry of the Interrupt Ring has 8B data with the following information.

| Signals   | Bits | Owner  | Description                                                                                                       |

|-----------|------|--------|-------------------------------------------------------------------------------------------------------------------|

| Pidx      | 12   | DMA    | Cumulative pointer of the Interrupt Ring entry written.                                                           |

| Page_Size | 3    | Driver | Size of the Interrupt Ring.<br>0: 4KB<br>1: 8KB<br>2: 12KB<br>3: 16KB<br>4: 20KB<br>5: 24KB<br>6: 28KB<br>7: 32KB |

| Baddr_4k  | 52   | Driver | Base Addr[63:12]. The Interrupt Ring in memory is 4K aligned.                                                     |

| Color     | 1    | DMA    | This bit inverts every time PIDX wraps around.                                                                    |

| Signals | Bits | Owner  | Description                                           |

|---------|------|--------|-------------------------------------------------------|

| Int_st  | 1    | DMA    | Interrupt state.<br>0: WAIT_TRIGGER<br>1: ISR_RUNNING |

| Vec     | 6    | Driver | Interrupt Vector                                      |

| Vld     | 1    | Driver | Valid                                                 |

Finally, the QDMA Subsystem for PCIe sends out the PCIe MSI-X message using the interrupt vector from the Interrupt Context RAM.

When the PCIe MSI-X interrupt is received by the Host, the software reads the Interrupt Ring to determine which queues need service. After the software reads the Interrupt Ring, it will do a dynamic pointer update for the software CIDX to indicate the cumulative pointer that the software reads to. If the software CIDX is equal to the PIDX, this triggers a write to the Interrupt Ring on the interrupt state of that queue. If the software CIDX is not equal to the PIDX, it sends out another PCIe MSI-X message. Therefore, the software can read the Interrupt Ring again.

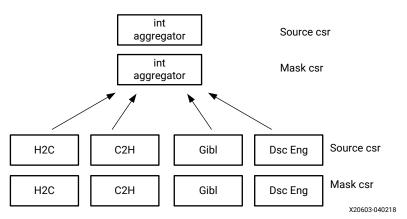

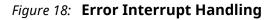

### Asynchronous Internal Interrupts

The asynchronous interrupts are used for capturing events that are not synchronous to any DMA operations, namely errors, status, and debug conditions. There is one asynchronous interrupt per PF. Every interrupt is configurable to any one of the PF.

In a Queue based scheme, interrupts are broadcast to all PFs and maintain status for each PF while in the async internal scheme. All async interrupts are configured to any one of the PFs.

The Source CSR registers are write 1 to clear type. Reset does not clear the status. They operate independent of the mask. The Mask CSR registers enables the associated source to participate in the interrupt.

### Error Interrupt Handling

The Error Aggregator module aggregates all of the errors together. When the error occurs, it generates an Error Interrupt if the ARM bit is set. The ARM bit is set by the software and cleared by the hardware when the Error Interrupt is taken. The Interrupt Arbiter arbitrates the Error Interrupt with the other interrupts.

The Error Interrupt supports the direct interrupt mode and indirect interrupt mode. For the direct interrupt mode, it sends out the PCIe MSI-X message directly. For the indirect interrupt mode, it processes the interrupt with the following steps.

- 1. Reads the Error Interrupt register to get the vector.

- 2. Looks up the Interrupt Context RAM.

- 3. Writes to the Interrupt Ring.

- 4. Sends out the PCIe MSI-X message.

The following is the data in the error interrupt register.

| Signals     | Bits | Owner  | Description                                                  |

|-------------|------|--------|--------------------------------------------------------------|

| Err_int_arm | 1    | Driver | ARM bit; set by software and clear by hardware.              |

| En_coal     | 1    | Driver | 1'b1: indirect interrupt mode<br>1'b0: direct interrupt mode |

| Vec         | 8    | Driver | Interrupt Vector                                             |

| Func        | 8    | Driver | Function                                                     |

The following shows how Error Interrupt handling.

# **Function Level Reset**

The FLR mechanism enables software to quiesce and reset Endpoint hardware with functionlevel granularity.

## Errors

### Linkdown

If the PCIe link goes down during DMA operations, transactions may be lost and the DMA may not be able to complete. In such cases, the AXI4 interfaces will continue to operate. Outstanding read requests on the C2H Bridge AXI4 MM interface receive correct completions or completions with a slave error response. The DMA will log a link down error in the status register. It is the responsibility of the driver to have a timeout and handle recovery of a link down situation.

### Parity

Pass through parity is supported on the primary data paths. Parity error can occur on C2H streaming, H2C streaming, Memory Mapped, Bridge Master and Bridge Slave interfaces. Parity error on Write payload can occur on C2H streaming, Memory Mapped and Bridge Slave. Double bit error on write payload and read completions for Bridge Slave interface causes parity error. Parity errors on requests to the PCIe are dropped by the UltraScale+<sup>™</sup> Devices Integrated Block for PCIe core, and a fatal error is logged by the PCIe. Parity errors are not recoverable and can result in unexpected behavior. Any DMA during and after the parity error should be considered invalid.

### Error Aggregator

There are Leaf Error Aggregators in different places. They log the errors and propagate them to a central place. The Central Error Aggregator aggregates the errors from all of the Leaf Error Aggregators.

The QDMA\_GLBL\_ERR\_STAT register is the error status register of the Central Error Aggregator. The bit fields indicate the locations of Leaf Error Aggregators. We can then look for the error status register of the individual Leaf Error Aggregator to find the exact error. For details, see QDMA\_GLBL\_ERR\_STAT (0X248).

The register QDMA\_GLBL\_ERR\_MASK is the error mask register of the Central Error Aggregator. It has the mask bits for the corresponding errors. When the mask bit is set, it will enable the corresponding error to be propagated to the next level to generate an Interrupt. The detail information of the error generated interrupt is described in the interrupt section. For details, see QDMA\_GLBL\_ERR\_MASK (0X24C).

Each Leaf Error Aggregator has an error status register and an error mask register. The error status register logs the error. The hardware sets the bit when the error happens, and the software can write 1'b1 to clear the bit if needed. The error mask register has the mask bits for the corresponding errors. When the mask bit is set, it enables the propagation of the corresponding error to the Central Error Aggregator. The error mask register does not affect the error logging to the error status register.

Links to the error status registers and the error mask registers information of the Leaf Error Aggregators follows.

#### C2H Streaming Error

QDMA\_C2H\_ERR\_STAT (0xAF0): The error status register of the C2H streaming errors.

QDMA\_C2H\_ERR\_MASK (0xAF4): The error mask register. The software can set the bit to enable the corresponding C2H streaming error to be propagated to the Central Error Aggregator.

QDMA\_C2H\_FIRST\_ERR\_QID (0xB30): The QID of the first C2H streaming error.

QDMA\_C2H MM Status (0x1040)

| Bit     | Default | Access<br>Type | Field      | Description                                                                                                                                                                                                  |

|---------|---------|----------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:17] |         |                |            | Reserved                                                                                                                                                                                                     |

| [16]    |         |                | rdwr       | Read or Write Error.<br>0: Read error<br>1: Write error                                                                                                                                                      |

| [15:0]  |         |                | error_code | If Write Error, bit position:<br>2: RAM uncorrectable error<br>1: Unsupported request<br>0: Function level reset<br>Other bits reserved<br>If Read Error, bit position:<br>1: Slave error<br>0: Decode error |

#### Table 2: C2H MM Error Code (0x1058)

#### Table 3: C2H0 MM Error Info (0x105C)

| Bit     | Default | Access<br>Type | Field | Description                       |

|---------|---------|----------------|-------|-----------------------------------|

| [31:29] |         |                |       | Reserved                          |

| [28:17] |         |                | qid   | Queue ID of the descriptor.       |

| [16]    |         |                | dir   | Direction of descriptor.          |

| [15:0]  |         |                | cidx  | Consumer index of the descriptor. |

#### **QDMA H2C0 MM Error**

H2C0 MM Status (0x1240)

| Bit     | Default | Access<br>Type | Field      | Description                                                                                                                                                                                                                                                                                                                                                         |

|---------|---------|----------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:17] |         |                |            | Reserved                                                                                                                                                                                                                                                                                                                                                            |

| [16]    |         |                | rdwr       | Read or Write Error.<br>0: Read error<br>1: Write error                                                                                                                                                                                                                                                                                                             |

| [15:0]  |         |                | error_code | If Read Error, bit position:<br>1: Header poisoned<br>2: Unsupported request or Completer Abort<br>3: Header byte count mismatch<br>4: Header param mismatch<br>5: Header address mismatch<br>8: Function level reset<br>16 : Data poisoned<br>22: PCIe reads disabled<br>Other bits reserved<br>If Write Error, bit position:<br>1: Slave error<br>0: Decode error |

#### Table 4: H2C0 MM Error Code (0x1258)

#### Table 5: H2C0 MM Error Info (0x1258)

| Bit     | Default | Access<br>Type | Field | Description                      |

|---------|---------|----------------|-------|----------------------------------|

| [31:29] |         |                |       | Reserved                         |

| [28:17] |         |                | qid   | Queue ID of the descriptor.      |

| [16]    |         |                | dir   | Direction of descriptor.         |

| [15:0]  |         |                | cidx  | Consumer index of the descriptor |

#### **TRQ Error**

QDMA\_GLBL\_TRQ\_ERR\_STS (0x260): The error status register of the TRQ errors.

QDMA\_GLBL\_TRQ\_ERR\_MSK (0x264): The error mask register.

QDMA\_GLBL\_TRQ\_ERR\_LOG\_A (0x268): The error logging register. It shows the select, function, and address of the access when the error happens.

#### **Descriptor Error**

QDMA\_GLBL\_TRQ\_ERR\_STS (0x260): The error status register of the TRQ errors.

QDMA\_GLBL\_TRQ\_ERR\_MSK (0x264): The error mask register.

QDMA\_GLBL\_TRQ\_ERR\_LOG\_A (0x268): The error logging register. It shows the select, function, and address of the access when the error happens.

#### **RAM Double Bit Error**

#### Table 6: **QDMA\_RAM\_DBE\_STS\_A(0xfc)**

| Bit   | Default | Access<br>Type | Field             | Description                                                              |

|-------|---------|----------------|-------------------|--------------------------------------------------------------------------|

| [31]  |         |                | reserved          |                                                                          |

| [30]  |         |                | pfch_ll_ram       | C2H ST prefetch list RAM double bit ECC error.                           |

| [29]  |         |                | wrb_ctxt_ram      | C2H ST writeback context RAM double bit ECC error.                       |

| [28]  |         |                | pfch_ctxt_ram     | C2H ST prefetch RAM double bit ECC error.                                |

| [27]  |         |                | desc_req_fifo_ram | C2H ST descriptor request RAM double bit ECC error.                      |

| [26]  |         |                | int_ctxt_ram      | Interrupt context RAM double bit ECC error.                              |

| [25]  |         |                | int_qid2vec_ram   | Interrupt QID2VEC RAM double bit ECC error.                              |

| [24]  |         |                | wrb_coal_data_ram | Writeback Coalescing RAM double bit ECC error.                           |

| [23]  |         |                | tuser_fifo_ram    | C2H ST TUSER RAM double bit ECC error.                                   |

| [22]  |         |                | qid_fifo_ram      | C2H ST QID FIFO RAM double bit ECC error.                                |

| [21]  |         |                | payload_fifo_ram  | C2H ST payload RAM double bit ECC error.                                 |

| [20]  |         |                | timer_fifo_ram    | Timer fifo RAM double bit ECC error.                                     |

| [19]  |         |                | pasid_ctxt_ram    | PASID configuration RAM double bit ECC error.                            |

| [18]  |         |                | dsc_cpld          | Descriptor engine fetch completion data RAM double bit ECC error.        |

| [17]  |         |                | dsc_cpli          | Descriptor engine fetch completion information RAM double bit ECC error. |

| [16]  |         |                | dsc_sw_ctxt       | Descriptor engine software context RAM double bit ECC error.             |

| [15]  |         |                | dsc_crd_rcv       | Descriptor engine receive credit context RAM double bit ECC error.       |

| [14]  |         |                | dsc_hw_ctxt       | Descriptor engine hardware context RAM double bit ECC error.             |

| [13]  |         |                | func_map          | Function map RAM double bit ECC error.                                   |

| [12]  |         |                | c2h_wr_brg_dat    | Bridge slave write data buffer double bit ECC error.                     |

| [11]  |         |                | c2h_rd_brg_dat    | Bridge slave read data buffer double bit ECC error.                      |

| [10]  |         |                | h2c_wr_brg_dat    | Bridge master write double bit ECC error.                                |

| [9]   |         |                | h2c_rd_brg_dat    | Bridge master read double bit ECC error.                                 |

| [8:5] |         |                | reserved          |                                                                          |

| [4]   |         |                | mi_c2h0_dat       | C2H MM data buffer double bit ECC error.                                 |

| [3:1] |         |                | reserved          |                                                                          |

| [0]   |         |                | mi_h2c0_dat       | H2C MM data buffer double bit ECC error.                                 |

#### Table 7: QDMA\_RAM\_DBE\_MSK\_A(0xf8)

| Bit    | Default | Access<br>Type | Field | Description                                                     |

|--------|---------|----------------|-------|-----------------------------------------------------------------|

| [31:0] |         |                | mask  | Error logging enable masks. See QMD_RAM_DBE_STS for definitions |