# Modular Media over IP Infrastructure

**Vivado Design Suite**

PG241 June 7, 2017

# **Table of Contents**

| Chapter 1: Overview                  |    |

|--------------------------------------|----|

| Feature Summary                      | 6  |

| Applications                         | 7  |

| Licensing and Ordering Information   | 7  |

|                                      |    |

| Chapter 2: Product Specification     |    |

| Media over IP Infrastructure Modules | 9  |

| Performance (Maximum Frequencies) 2  | 24 |

| Latency                              | 25 |

| Resource Utilization                 |    |

| Port Descriptions                    |    |

| Register Space                       | 34 |

|                                      |    |

| Chapter 3: Designing with the Core   |    |

| General Design Guidelines            | 70 |

| Clocking                             | 71 |

| Resets                               |    |

| Protocol Description                 | 71 |

|                                      |    |

| Chapter 4: Design Flow Steps         |    |

| Customizing and Generating the Core  |    |

| Constraining the Core                |    |

| Simulation                           |    |

| Synthesis and Implementation         | 30 |

| Chapter 5: Example Design            |    |

### Chapter 6: Test Bench

| Using the Demonstration Test Bench                              | 82 |

|-----------------------------------------------------------------|----|

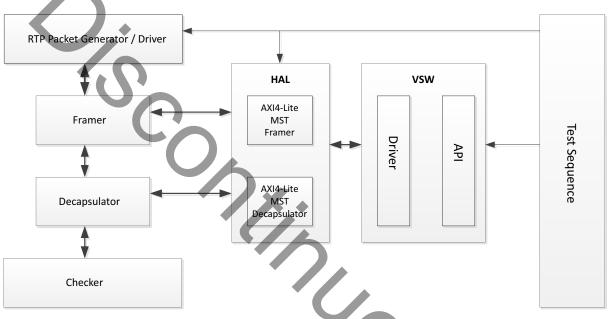

| Demonstration Test Bench Architecture for both Framer and Decap | 83 |

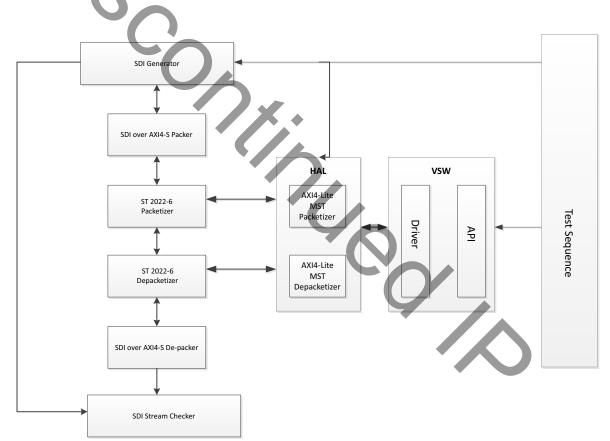

| Demonstration Test Bench Architecture for both                  |    |

| ST 2022-6 Packetizer and ST 2022-6 Depacketizer                 | 84 |

#### Appendix A: Verification, Compliance, and Interoperability

### Appendix B: Migrating and Upgrading

#### **Appendix C: Debugging**

| Finding Help on Xilinx.com     | 88 |

|--------------------------------|----|

| Debug Tools (Reference Boards) | 89 |

| Interface Debug                | 90 |

| Core Debug                     | 91 |

### Appendix D: Additional Resources and Legal Notices

| Xilinx Resources                     |

|--------------------------------------|

| References                           |

| Revision History                     |

| Please Read: Important Legal Notices |

|                                      |

|                                      |

## **IP Facts**

# Introduction

The Modular Media over IP Infrastructure is a collection of cores that can be integrated together to support a variety of protocols for video, audio, and data over IP-based networks. Primarily developed to support the SMPTE ST 2022 [Ref 4] [Ref 5] [Ref 6] standards for video over IP initially, the modules and their associated reference designs can be used as a starting point framework for many types of media over IP implementations, both standardized and proprietary. Offering superior flexibility and scalability, modules can be added to or replaced by existing and future cores from Xilinx, our Alliance Program Members or customer's own IP. Access to intermediate signaling is inherently available.

# **Features**

- Video stream conversion modules

- ST 2022-6 Packetizer Module: Converts Serial Digital Interface (SDI) video stream (SDI over AXI4-Stream) into a media datagram stream in accordance with the SMPTE ST 2022-6 protocol.

- ST 2022-6 Depacketizer Module: Converts received Real-time Transport Protocol (RTP) encapsulated SMPTE ST 2022-6 Media packets into SDI video stream (SDI over AXI4-Stream)

- Ethernet packet processing modules

- Framer Module: Framing Ethernet Packets by adding the Ethernet, Internet Protocol (IP) and User Datagram Protocol (UDP) headers to incoming Real-time Transport Protocol (RTP) packets.

- Decapsulator Module: Accepts Ethernet Packets and perform header stripping (output RTP packets), channel matching and filtering, video stream detection and video frame boundary alignment.

| LogiCORE <sup>™</sup> IP Facts Table      |                                                                                                  |  |  |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|

| Core Specifics                            |                                                                                                  |  |  |  |

| Supported<br>Device Family <sup>(1)</sup> | UltraScale+™ Families,<br>Kintex® UltraScale™, Zynq®-7000,<br>Virtex®-7, Kintex®-7               |  |  |  |

| Supported User<br>Interfaces              | AXI4-Lite, AXI4-Stream, AXI4                                                                     |  |  |  |

| Resources                                 | See Resource Utilization in Chapter 2                                                            |  |  |  |

|                                           | Provided with Core                                                                               |  |  |  |

| Design Files                              | Encrypted RTL                                                                                    |  |  |  |

| Example Design                            | Modular SMPTE ST 2022-567 on Kintex-7<br>Evaluation Board Application Note (XAPP1272)<br>[Ref 3] |  |  |  |

| Test Bench                                | Verilog and VHDL                                                                                 |  |  |  |

| Constraints File                          | XDC                                                                                              |  |  |  |

| Simulation<br>Model                       | Encrypted RTL, VHDL Behavioral,<br>VHDL or Verilog source HDL                                    |  |  |  |

| Supported<br>S/W Driver <sup>(2)</sup>    | Standalone                                                                                       |  |  |  |

| Tested Design Flows <sup>(3)</sup>        |                                                                                                  |  |  |  |

| Design Entry                              | Vivado® Design Suite                                                                             |  |  |  |

| Simulation                                | For supported simulators, see the<br>Xilinx Design Tools: Belease Notes Guide                    |  |  |  |

| 2 1        | 0                                                                              |

|------------|--------------------------------------------------------------------------------|

| Simulation | For supported simulators, see the<br>Xilinx Design Tools: Release Notes Guide. |

| Synthesis  | Vivado Synthesis                                                               |

| Yc         | Support                                                                        |

|            | Willow at the Willow Comment with more                                         |

Provided by Xilinx at the Xilinx Support web page

#### Notes:

1;

- 1. For a complete list of supported devices, see the Vivado IP catalog.

- 2. Standalone driver details can be found in the SDK directory (*<install\_directory>/*doc/usenglish/xilinx\_drivers.htm). Linux OS and driver support information is available from the Xilinx Wiki page.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

In broadcast and professional audio/video markets, vendors and end users are pushing for the widespread adoption of IP-based networking to transport video, audio and data either between locations, or between equipment. This can reduce costs, enable seamless workflows, and offer expanded capabilities to handle all kinds of traffic in novel and more efficient ways. Up until now, the main way this has been done in broadcast is using standards such as SMPTE ST 2022, which can encapsulate multiple uncompressed SDI video channels, or multiple compressed transport streams into an Ethernet stream.

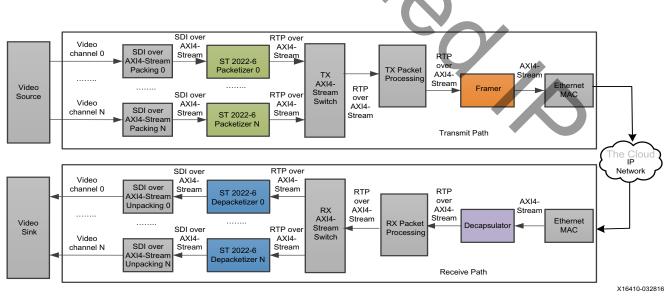

The modular media over IP infrastructure focuses initially on SMPTE ST 2022-6, with ST 2022-6 Packetizers and ST 2022-6 Depacketizers supporting the SMPTE ST 2022-6 standard and converting between SDI video and (Real Time Protocol) RTP packet streams (see IETF RFC 3550 [Ref 2]). Framer and Decapsulator modules are used to do conversion between RTP and Ethernet packets. The infrastructure can be configured to enable SMPTE ST 2022-7 which adds further robustness by adding a second redundant network link and being able to switch seamlessly between them should one link lose packets.

The SMPTE ST 2022 modules integrate easily with the Xilinx SMPTE SD/HD/3G-SDI or SMPTE UHD-SDI (up to 3G rate) LogiCORE IP cores, the 10 Gigabit Ethernet subsystem and other cores to provide a fully inter-operable system-level design for high-bit rate Video over IP.

Over time this modular approach provides a framework to support protocols and standards beyond SMPTE ST 2022 and to accelerate overall time-to-market.

## **Feature Summary**

The Modular Media over IP Infrastructure supports the ST 2022 Media over IP system design. The core supports all SD/HD3G-SDI modes, except the following:

- HD: 1035i, 59.94/60

- 3G-levelA: 1080P, 47.95/48.

- 3G-levelB: 1080P, 47.95/48/50/59.94/60

The ST 2022-6 Packetizer and ST 2022-6 Depacketizer are based on SMPTE ST 2022-6 standards. Framer and Decapsulator can be used for SMPTE ST 2022-5/6 standards.

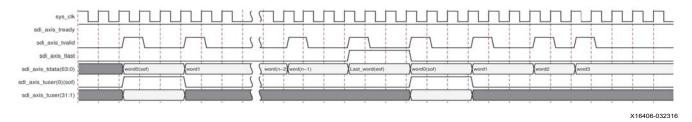

- AXI4-Stream compliant

- Supports these AXI4-Stream defined signals: TVALID, TREADY, TDATA, TKEEP, TLAST, TUSER.

- Supports SDI over AXI4-Stream (customized AXI4-Stream for video frame stream transmitting/receiving) (see Chapter 3, Designing with the Core).

- Supports RTP over AXI4-Stream (customized AXI4-Stream for RTP packet stream transmitting/receiving) (see Chapter 3, Designing with the Core).

- ST 2022-6 Packetizer Converts an SDI video stream (SDI over AXI4-Stream) into a media datagram stream in accordance with the SMPTE ST 2022-6 protocol.

- ST 2022-6 Depacketizer Converts received RTP Encapsulated SMPTE ST 2022-6 Media Packets into SDI video stream (SDI over AXI4-Stream).

- Framer Framing Ethernet Packets by adding the Ethernet, Internet Protocol and User Datagram Protocol (UDP) headers to incoming RTP Encapsulated SMPTE ST 2022, RFC4175, or RFC3190 packets.

- Decapsulator

Accepts Ethernet packets that encapsulate SMPTE ST 2022 5/6, RFC4175, or RFC3190 media data and performs header stripping (transmit RTP Encapsulated SMPTE ST 2022-5/6, RFC4175, or RFC3190 packets), channel matching and filtering, video stream detection and video frame boundary alignment.

# Applications

- Transport high bandwidth RTP Encapsulated ST 2022, RFC4175, or RFC3190 packets over IP Network

- Support real-time ST 2022, RFC4175, or RFC3190 applications such as contribution, primary distribution and digital cinema.

- SMPTE ST 2022-56 Example Application: See *Modular SMPTE ST 2022-567 on Kintex-7 Evaluation Board Application Note* (XAPP1272) [Ref 3].

# Licensing and Ordering Information

This Xilinx LogiCORE<sup>™</sup> IP module is provided under the terms of the <u>Xilinx Core License</u> <u>Agreement</u>. The module is shipped as part of the Vivado® Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your <u>local Xilinx sales representative</u> for information about pricing and availability.

For more information, visit the Modular Media over IP Infrastructure product page.

Information about other Xilinx LogiCORE IP modules is available at the <u>Xilinx Intellectual</u> <u>Property</u> page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your <u>local Xilinx sales representative</u>.

### **License Checkers**

If the IP requires a license key, the key must be verified. The Vivado design tools have several license checkpoints for gating licensed IP through the flow. If the license check succeeds, the IP can continue generation. Otherwise, generation halts with an error. License checkpoints are enforced by the following tools:

- Vivado synthesis

- Vivado implementation

- write\_bitstream (Tcl command)

**IMPORTANT:** *IP license level is ignored at checkpoints. The test confirms a valid license exists. It does not check IP license level.*

### Hardware Evaluation License

If a Hardware Evaluation License is being used, the core will stop transmitting video after timeout.

Chapter 2

# **Product Specification**

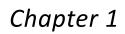

Figure 2-1: ST 2022-6 Packetizer Block Diagram

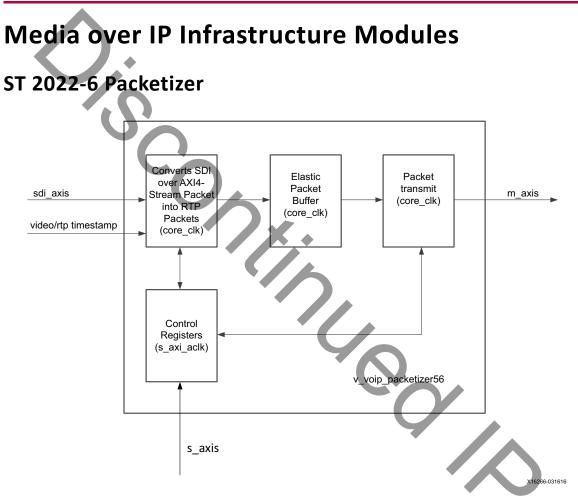

Figure 2-2: ST 2022-6 Packetizer Operation Flow

The ST 2022-6 Packetizer module accepts SDI over AXI4-Streams and transmits out SMPTE ST 2022-6 RTP packets to a downstream module. The packet information is defined in the TUSER bus of the m\_axis interface (see "RTP over AXI4-Stream Protocol" in Chapter 4, Design Flow Steps.)

The module has an AXI4-Lite interface that allows dynamic control of the register settings. See Table 2-3.

The ST 2022-6 media payload length by default is set to 1,376 bytes. You have the flexibility to configure the media payload length by configuring bit [10:0] of the media payload length register (offset 0x20).

The video format information is required by the module for correct operation. The video format information can be either from an upstream module by using the SDI over AXI4-Stream interface TUSER sideband signal or by direct register programming on the module. The decision is made through the video\_format (offset 0x14) register bit 31.

The module must be enabled before accepting SDI over AXI4-Stream data by setting bit 0 to 1 of the module control register (offset 0x10). The channel number must be configured before enabling the module and the configured channel number is reflected in the RTP over AXI4-Stream master interface TUSER bus.

The RTP time stamp and Video time stamp is provided via the RTP Time Stamp input port and the Video Time Stamp input port respectively.

The media payload length register (offset 0x20) and register bit[27:16] of the module control register (offset 0x10) should be configured first before enabling the module.

Whenever the video format changes, a reset or clear action must be done on the module, which is done by programing the module enable to 0.

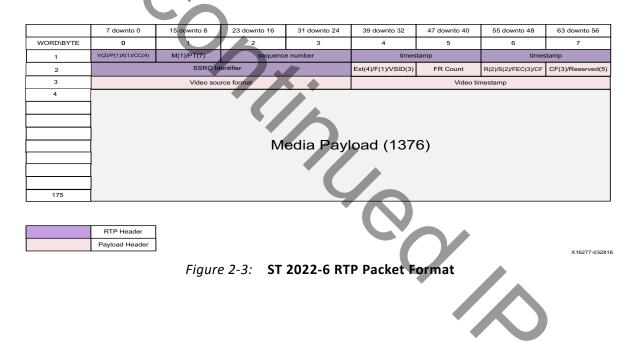

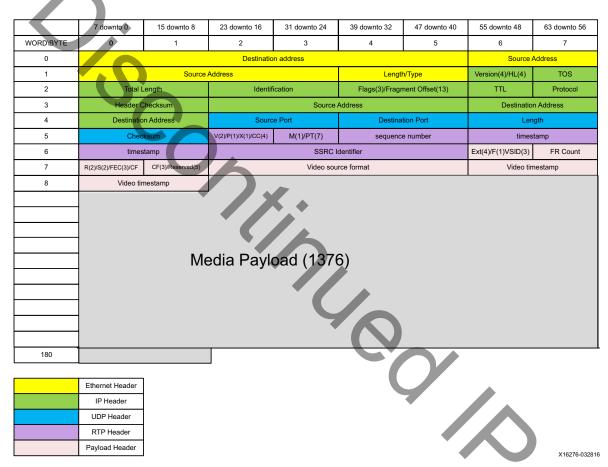

Figure 2-3 shows the packet format that comes out from the RTP over AXI4-Stream master interface of the module. This packet format strictly follows the SMPTE ST 2022-6 standard. Note that the Ext[3:0] field in the media payload header are fixed to zero which means the header extension is not supported.

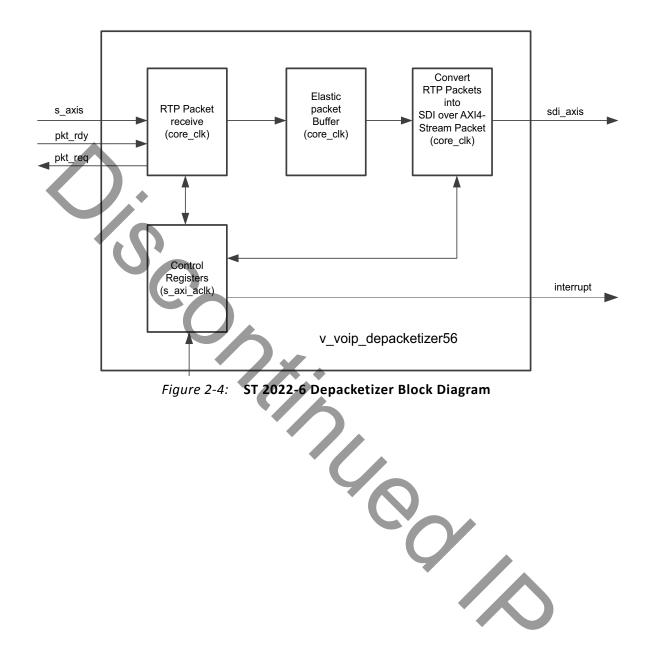

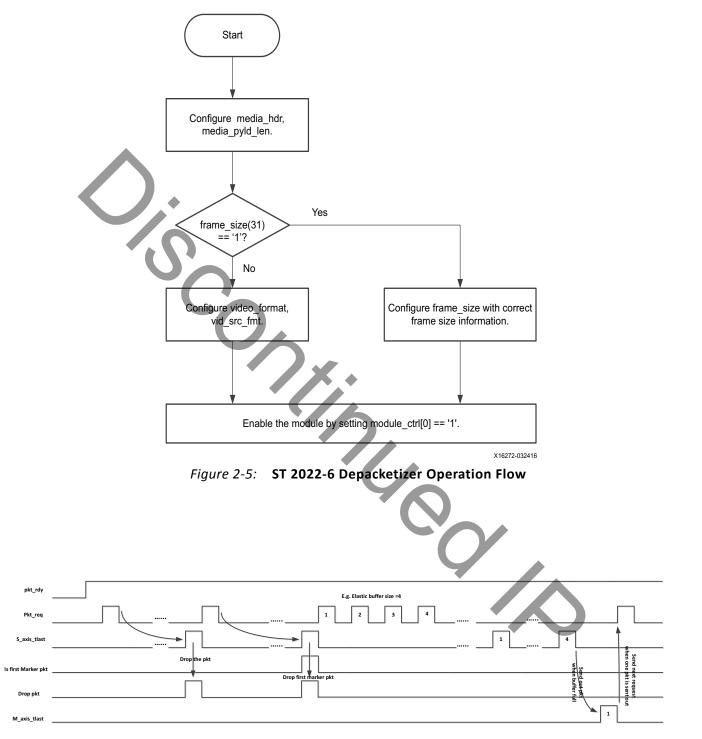

### ST 2022-6 Depacketizer

Figure 2-6: ST 2022-6 Depacketizer Packet Request Protocol

The ST 2022-6 Depacketizer module converts RTP packets back to SDI over the AXI4-Stream video stream. The incoming stream packet type must be an SMPTE ST 2022-6 RTP packet. The RTP header and media payload header are stripped off. The input interface to the ST 2022-6 Depacketizer module must comply with "RTP over AXI4-Stream" (customized AXI4-Stream for RTP packet stream transmitting/receiving.) See Chapter 3, Designing with the Core.

The frame size information is required by the module for correct operation. The frame size consists of two important pieces of information: datagram per frame and last datagram length. You are required to program the video\_format (offset 0x14) and vid\_src\_fmt (offset 0x18). The module can decode the frame size from these two video format registers.

If you need to use a non-standard video frame size, you can program the frame\_size (offset 0x24) register bit 31 to 1 and give the correct frame size information on the remaining bits of the register.

The media payload length is configured by the media\_pyld\_len (offset 0x20) register, which has a default value of 1,376 (decimal). It is the size in bytes for the video data carried in the incoming packet.

Because the incoming packet might not have a video timestamp inserted in the media payload header, you need to explicitly tell the module about video timestamp information by programming the media\_hdr (offset 0x1C) register bit 0. This is important because it determines whether the module can succeed extracting the correct media payload data from the packet.

The pkt\_req output port of the ST 2022-6 Depacketizer module is connected to the upstream module for the packet request process. If the upstream module does not have this handshaking protocol but only the AXI4-Stream master interface, you can tie the pkt\_rdy to High and ignore the pkt\_req output. This is illustrated in Figure 2-6. When the pkt\_rdy input is High, the module sends out one request pulse and waits for the packet to arrive at the RTP over AXI4-Stream slave interface. When the packet arrives, it checks whether it is the last packet of a video frame or not by checking on the marker bit ("M" bit) in the packet RTP header. If it is not the marker packet, the packet is detected (will be dropped), the module will send out a number of packet request pulses in every other cycle (the number of pulses sent in this burst equal to the elastic buffer size). This is to fill the internal buffer until full. Packets will be processed and data will be sent out on the SDI over AXI4-Stream master interface only when the buffer becomes full. This feature can help to avoid video data starvation at the module output that can be caused by upstream modules.

Disabling the module causes the internal buffer and state machine to be cleared and reset, which is needed when you want to reset the module or during stream changes.

Currently, there is only one interrupt source from the module which is "buffer become empty interrupt." In normal operation, when the data stream is flowing through the module, the buffer level of the module should maintain approximately the same buffer size. Due to upstream module error/instability, the buffer level might go down.

If the buffer becomes empty because of this, it will cause video stream interruption. In this case this interrupt is fired to notify the system of the error condition.

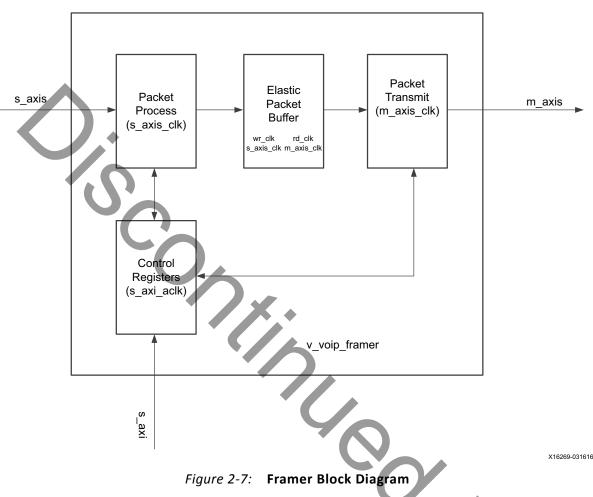

### Framer

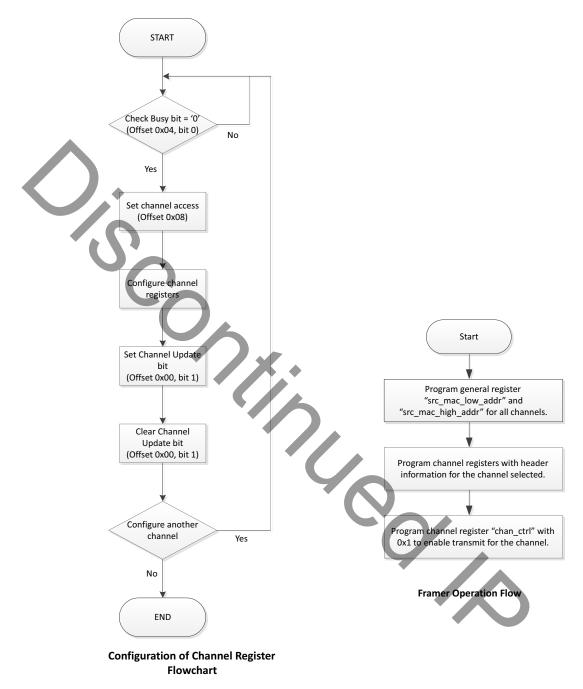

The Figure 2-8 left flow chart shows the operation of the configuration channel space registers; this operation is common for multi-channel register modules, for example, the Decapsulator and Framer modules.

The main steps to access a channel space register are:

- 1. Read the general space register "status" bit0 to check whether the hardware is busy or not.

- 2. If not busy, program the channel number into the general space register "channel\_access".

- 3. Access the channel space registers.

- 4. If the channel registers get new programmed values, program the general space register "control" bit1 to 1.

5. Program the general space register "control" bit1 to 0. Note that the preceding steps are used to access one or more channel space registers for one channel.

The module accepts RTP Encapsulated SMPTE ST 2022-5/6, RFC4175, or RFC3190 packets from the upstream module and adds user-programmed UDP/IP/Ethernet headers. The generated Ethernet packets can be sent to the Ethernet Media Access Control (MAC).

If the generic "Overflow Handling Strategy" is set to 1, when the internal elastic buffer becomes full, packets will be dropped at the RTP over AXI4-Stream slave interface and will not be pushed back to the upstream module. If this generic is set to 0, if the buffer becomes full, packets will be pushed back to the upstream module by deassertion of TREADY of the RTP over AXI4-Stream slave interface.

The module is configured through the  $s_{axi}$  (AXI4-Lite) interface which is usually connected to the processor subsystem.

The s\_axis input interface comply with "RTP over AXI4-Stream". The m\_axis output interface is the simple AXI4-Stream interface without tuser.

As shown in Figure 2-8, the module is a multi-channel module that can support multiple channels.

The generic "Max Channels" should be properly set because it determines how many channels that the module can support. If it is set too large, FPGA resource utilization can be high.

The input packet types are RTP Encapsulated SMPTE ST 2022-5/6, RFC4175, or RFC3190 packets driven on the RTP over AXI4-Stream slave interface of the module. The output packet types are Ethernet packet types driven on the AXI4-Stream master interface of the module. The Ethernet/IP/UDP headers are user configurable. Some header field values are shared among all channels (general register space) and most of the header field values are per channel programmable.

Figure 2-9 and Figure 2-10 show a typical Ethernet packet format without a VLAN field (for the RTP Encapsulated SMPTE ST 2022-6 Media packet and RTP Encapsulated SMPTE ST 2022-5 Media FEC packet). Framer will not change the content of the RTP header and Payload Data. Framer only adds the Ethernet header, IP header, and UDP header to the RTP packet according to user-configured parameters.

As for RTP Encapsulated SMPTE ST 2022-5 FEC packets, the UDP Destination Port will be added by 2 for column SMPTE ST 2022-5 FEC packets and by 4 for row SMPTE ST 2022-5 FEC packets from the user-configured UDP Destination Port.

The IP header checksum is calculated by the module but the UDP header checksum will be zeros.

Figure 2-9 and Figure 2-10 show packet format for the RTP and FEC packet.

As for the payload header, Figure 2-9 shows the case that the field **CF[3:0] /= 0** (including timestamp). The design also supports the packet format without timestamp (CF[3:0]=0). The Payload header field **Ext[3:0**] should always be zero; an extension is not supported. For the payload header, refer to the SMPTE ST 2022-6 standard.

As for the Internet IP header, the **IHL[3:0]** field is hard coded to zeros which means the Internet IP header length is fixed as shown in the figure. The **Identification[15:0]** field is set to zeros. The **Flags[3:0]** field is set to 010 to mean "no fragmentation" and "no more fragments". The **Fragment Offset** field is set to zero as well.

Note that for the Internet IP header field **TTL[7:0**], it must be programmed with a big enough value that guarantees the packet can survive before reaching its destination. The default value from the design is zero.

The Internet IP header field **Protocol[7:0]** is hard coded to be 0x11 to force the packet to be a User Datagram according to the Internet Protocol Numbers (refer to RFC762 [Ref 15]).

Figure 2-9: Ethernet Packet Format for ST 2022-6 RTP Packet Type (without VLAN)

|           | 7 downto 0                         | 15 downto 8 | 23 downto 16         | 31 downto 24          | 39 downto 32   | 47 downto 40    | 55 downto 48     | 63 downto 56 |

|-----------|------------------------------------|-------------|----------------------|-----------------------|----------------|-----------------|------------------|--------------|

| WORD\BYTE | 0                                  | 1           | 2                    | 3                     | 4              | 5               | 6                | 7            |

| 0         | Destination address Source Address |             |                      |                       |                | Address         |                  |              |

| 1         |                                    | Source      | Address              |                       | Lengt          | п/Туре          | Version(4)/HL(4) | TOS          |

| 2         | Total L                            | .ength      | Identif              | ication               | Flags(3)/Fragr | nent Offset(13) | TTL              | Protocol     |

| 3         | Header C                           | hecksum     |                      | Source A              | Address        |                 | Destination      | n Address    |

| 4         | Destinatio                         | n Address   | Sourc                | e Port                | Destina        | tion Port       | Length           |              |

| 5         | Chec                               | ksum        | V(2)/P(1)/X(1)/CC(4) | M(1)/PT(7)            | sequence       | e number        | timestamp        |              |

| 6         | times                              | tamp        |                      | SSRC I                | dentifier      |                 | E/R/P/X/CC(4)/M  | PT Recovery  |

| 7         | SN E                               | Base        |                      | TS Red                | covery         |                 | Length R         | lecovery     |

| 8         | Rese                               | erved       | Offset               | Offset(2)/Reserved(6) | NA             | Reserved        |                  |              |

|           |                                    | Ме          | dia heade            | er (12) + I           | Media Pa       | yload (13       | 376)             |              |

| <         | ).<br>'S                           | Me          | dia heade            | er (12) + I           | Media Pa       | yload (13       | 376)             |              |

| 182       |                                    | Me          | dia heade            | er (12) + I           | Media Pa       | yload (13       | 376)             |              |

| 182       | Ethernet Header                    | 2           |                      |                       | Media Pa       | yload (13       | 376)             |              |

| 182       | Ethernet Header<br>IP Header       | 2           |                      |                       | Media Pa       | yload (13       | 376)             |              |

| 182       |                                    | 2           |                      |                       | Media Pa       | yload (13       | 376)             |              |

| 182       | IP Header                          | 2           | dia heade            |                       | Vedia Pa       | yload (13       | 376)             |              |

Figure 2-10: Ethernet Packet Format for ST 2022-5 FEC Packet Type (without VLAN)

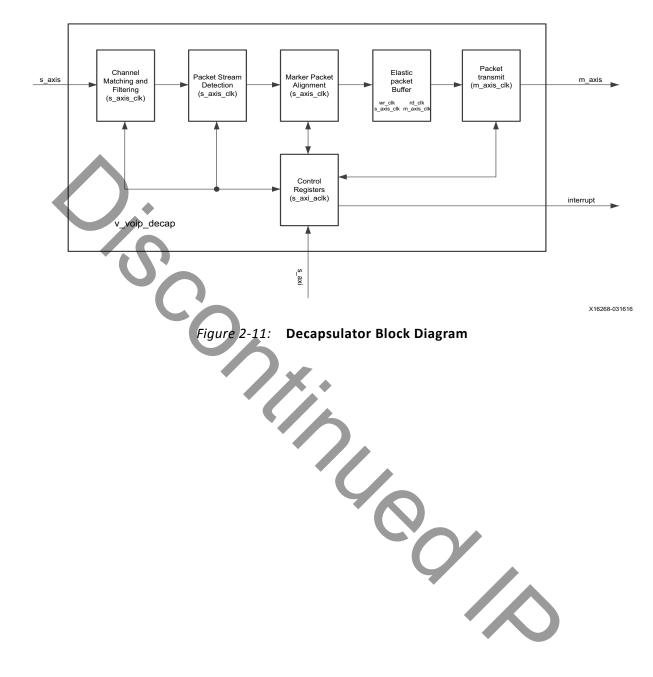

### Decapsulator

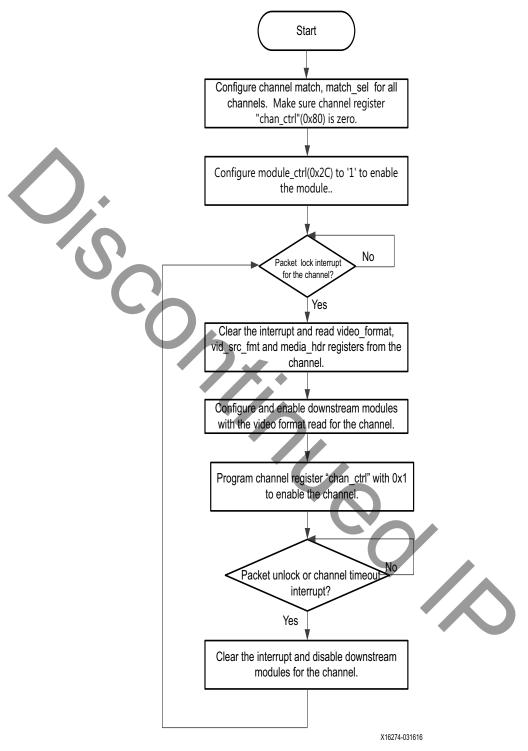

Figure 2-12: Decapsulator Operation Flow

*Note:* To see how to access the channel register, refer to the "Configuration of Channel Registers Flowchart" in Figure 2-8 because the concept is the same.

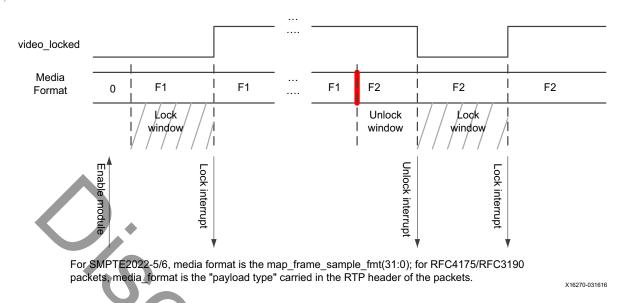

*Figure 2-13:* **Decapsulator Video Format Lock/Unlock Interrupt**

The Decapsulator module receives Ethernet datagrams and transmits RTP datagrams to the downstream module via the RTP over AXI4-Stream master interface. The Decapsulator module performs these operations:

- Channel mapping or filtering based on per channel filtering settings.

- Stripping off the Ethernet, IP and UDP headers to form an RTP packet.

- Media stream detection based on the media payload header from incoming packets. A few video stream detection interrupts are generated to notify the system about the packet stream change.

Note that the s\_axis\_tuser input port is a single-bit signal to indicate that the current packet is a good (1) or bad (0) packet. It is sampled when s\_axis\_tlast is valid. If you do not want to connect this signal, tie it to High.

The module has a s\_axi (AXI4-Lite) interface that allows dynamic control of register settings. See Decapsulator.

The module is activated by programming the module enable to 1; otherwise, it will be in sleep or mute mode in which the module will not accept packets.

When the module is enabled, the incoming packets pass through these processing stages before it can be accepted by the module and sent out to downstream modules:

- **Channel Matching**: The Ethernet header (or sometimes the RTP header's payload type) information is used to match incoming packets into a different channel based on per channel programmed matching header information. If packets get mismatched, the packet will be dropped. Only the matched packets on the channel will be passed down to the next processing stage: video detection.

- Stream detection (only for SMPTE ST 2022-6 and RFC4175): For SMPTE2022-5/6, ٠ the media format is the map frame sample fmt(31:0); for RFC4175/RFC3190 packets, media\_format is the "payload type" carried in the RTP header of the packets. By default, the media stream is unlocked in a channel and the channel is disabled. When a continuous number of received packets (lock window) are matched on the channel and have the same ST 2022-6 media format in the packet header, the channel is locked. A packet lock interrupt is fired. When the channel is in the media stream locked state, if a continuous number of received packets (unlock window) are matched on the channel and they have a different media format from the locked media format, the channel is unlocked. The channel is disabled by hardware and a packet unlock interrupt is fired. When the channel is locked and suddenly no packets get matched on the channel for a certain amount of time (user configured channel timeout: in number of core clocks), the channel is disabled by hardware and a channel timeout interrupt is fired. Note that all packets will be dropped on the channel if the channel is disabled or the channel is enabled but the first marker packet is not detected excepting RFC3190 which doesn't have Marker packet detection. Also note that media stream detection is activated only when the module is enabled.

- Marker packet alignment: For RFC3190, there is not marker packet concept and then there is not marker packet alignment for RFC3190 packet stream. For SMPTE2022-5/6 and RFC4175, the marker bit of RTP header is set for last packet of the video frame. When the channel gets enabled, all packets will be dropped until the very first marker packet is detected. All packets after the first marker packet are processed by the module and sent out to the downstream module. Note that marker pkt alignment is activated only when the channel is enabled.

There are two register fields in the channel\_control register that can be programmed to decide whether marker packet detection should be enabled or not. Another register bit is defined in the channel\_control register to let you decide whether the first marker packet should be sent downstream or dropped inside the Decapsulator module.

*Note:* Packet process means stripping off the Ethernet/IP/UDP headers.

Register configuration is required for normal Decapsulator module operation.

Decapsulator decodes the current packet type based on the PT field extracted from the RTP header. (Note: for RFC4175/RFC3190, the PT field is also used as media format and channel matching parameters). Note that the module can only accept RTP version 2. The decoded packet type and other packet information is output on the m\_axis\_tuser(31:0) bus (see

Port Descriptions). The Protocol field of the IP header of the packet must be 0x11; otherwise, the packet cannot be matched.

For SMPTE2022-5/6 packets processing, the RTP header "PT(6:0)" payload type field are fixed. However, the RFC4175/RFC3190 encapsulated packets won't have fixed payload type. The payload type is dynamic and programmed at the sender and passed to the receiver through SDP. At the receiver, for RFC4175/RFC3190, you must program the payload type for channel matching. After an incoming packet is matched on the channel, the packet processing continues.

| РТ             | m_axis_tuser<br>(31:28) | Packet type                                      | Comments                                                      |

|----------------|-------------------------|--------------------------------------------------|---------------------------------------------------------------|

| N.A            | "0000"                  | Non-RTP                                          |                                                               |

| "0100001" (33) | "0001"                  | RTP Encapsulated SMPTE ST<br>2022-2 Media Packet |                                                               |

| "1100000" (96) | "0001" or "0010"        | RTP Encapsulated SMPTE ST 2022-1 FEC Packet      | Further decoded as Column or<br>Row FEC packet by FEC header. |

| "1100010" (98) | "0101"                  | RTP Encapsulated SMPTE ST<br>2022-6 Media Packet |                                                               |

| "1100011" (99) | "0110" or "0111"        | RTP Encapsulated SMPTE ST<br>2022-5 FEC Packet   | Further decoded as Column or<br>Row FEC packet by FEC header. |

| (100~127)      | "1000"                  | RTP Encapsulated RFC4175<br>Media Packet         | Dynamic payload type.                                         |

| (100~127)      | "1001"                  | RTP Encapsulated RFC3190<br>Media Packet         | Dynamic payload type.                                         |

Table 2-1: Decapsulator: Decode Incoming Packet Type

# **Performance (Maximum Frequencies)**

The performance of the Modular Media over IP Infrastructure is limited only by the FPGA logic speed. Each core utilizes only block RAMs, LUTs, and registers and contains no I/O elements.

The maximum achievable clock frequency can vary. The maximum achievable clock frequency and all resource counts can be affected by other tool options, additional logic in the FPGA, using a different version of Xilinx tools and other factors. See the resource utilization section for device family specific information.

# Latency

For the ST 2022-6 Packetizer, different video formats (SD/HD/3G) causes different latencies on the module. The latency relies on the clock frequency and video format.

For the ST 2022-6 Depacketizer, SDI data is output only when the Elastic Buffer becomes full. The latency relies on both the clock frequency and Elastic Buffer size.

For the Framer, latency relies on the clock frequency.

For the Decapsulator, the latency is measured after marker packet alignment. In other words, the time spent performing video detection and frame boundary alignment do not contribute to the latency. Its latency relies on the clock frequency.

Table 2-2 shows the latency for all IP cores (based on simulation).

| IP Name                   | Clock Frequency                                                   | Latency<br>(clock cycles)                                 | Comments                                                                           |

|---------------------------|-------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------|

| ST 2022-6<br>Packetizer   | core_clk=200 MHz<br>s_axi_aclk=100 MHz                            | SD: 8171@core_clk<br>HD:1493@core_clk<br>3G: 754@core_clk | Media_payload_length=1376Bytes.<br>Include video timestamp.                        |

| ST 2022-6<br>Depacketizer | core_clk=200 MHz<br>s_axi_aclk=100 MHz                            | 910@core_clk                                              | Elastic Buffer = 4.<br>Media_payload_length=1376Bytes.<br>Include video timestamp. |

| Framer                    | s_axis_clk=200 MHz<br>m_axis_clk=156.25 MHz<br>s_axi_aclk=100 MHz | 192@s_axis_clk                                            | SMPTE ST 2022 5/6 packets.                                                         |

| Decapsulator              | s_axis_clk=156.25 MHz<br>m_axis_clk=200 MHz<br>s_axi_aclk=100 MHz | 245@m_axis_clk                                            | SMPTE ST 2022 5/6 packets.                                                         |

Table 2-2: Latency

# **Resource Utilization**

For resource utilization for the ST 2022-6 Packetizer, ST 2022-6 Depacketizer, Decapsulator. and Framer, see the following links.

- ST 2022-Packetizer

- ST 2022-6 Depacketizer

- <u>Framer</u>

- <u>Decapsulator</u>

# **Port Descriptions**

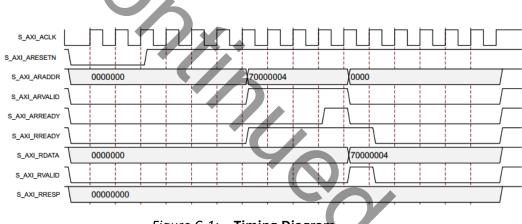

### **AXI4-Lite Interface**

| Table 2-3: | AXI-Lite | Interface |

|------------|----------|-----------|

|------------|----------|-----------|

| Signal Name   | Direction | Width | Description                                                                                                         |

|---------------|-----------|-------|---------------------------------------------------------------------------------------------------------------------|

| s_axi_aclk    | In        | 1     | AXI4-Lite clock.                                                                                                    |

| s_axi_aresetn | In        | 1     | AXI4-Lite active-Low reset.                                                                                         |

| s axi awaddr  | In        | 32    | AXI4-Lite Write Address Bus.                                                                                        |

|               |           |       |                                                                                                                     |

| s_axi_awvalid | In        | 1     | AXI4-Lite Write Address Channel Write Address Valid.                                                                |

| s_axi_wdata   | In        | 32    | AXI4-Lite Write Data Bus.                                                                                           |

| s_axi_wstrb   | In        | 4     | AXI4-Lite Write Data Channel Data Byte Strobes.                                                                     |

| s_axi_wvalid  | In        | 1     | AXI4-Lite Write Data Channel Write Data Valid.                                                                      |

| s_axi_awready | Out       | 1     | AXI4-Lite Write Address Channel Write Address<br>Ready. Indicates that DMA is ready to accept the<br>write address. |

| s_axi_wready  | Out       | 1     | AXI4-Lite Write Data Channel Write Data Ready.<br>Indicates DMA is ready to accept the write data.                  |

| s_axi_bresp   | Out       | 2     | AXI4-Lite Write Response Channel. Indicates results of the write transfer.                                          |

| s_axi_bvalid  | Out       | 1     | AXI4-Lite Write Response Channel Response Valid.<br>Indicates response is valid.                                    |

| s_axi_bready  | In        | 1     | AXI4-Lite Write Response Channel Ready. Indicates target is ready to receive a response.                            |

| s_axi_arvalid | In        | 1     | AXI4-Lite Read Address Channel Read Address Valid.                                                                  |

| s_axi_arready | Out       | 1     | Ready. Indicates DMA is ready to accept the read address.                                                           |

| s_axi_araddr  | In        | 32    | AXI4-Lite Read Address Bus.                                                                                         |

| Signal Name  | Direction | Width | Description                                                                                        |

|--------------|-----------|-------|----------------------------------------------------------------------------------------------------|

| s_axi_rready | In        | 1     | AXI4-Lite Read Data Channel Read Data Ready.<br>Indicates target is ready to accept the read data. |

| s_axi_rdata  | Out       | 32    | AXI4-Lite Read Data Bus.                                                                           |

| s_axi_rresp  | Out       | 2     | AXI4-Lite Read Response Channel Response.<br>Indicates results of the read transfer.               |

| s_axi_rvalid | Out       | 1     | AXI4-Lite Read Data Channel Read Data Valid.                                                       |

#### Notes:

he Vivado . 1. Refer to the Vivado Design Suite: AXI Reference Guide (UG1037) [Ref 14] on the AXI4-Lite interface and its protocol.

### **RTP over AXI4-Stream Interface Protocol**

#### Table 2-4: RTP over AXI4-Stream Interface Protocol

| Signals<br>(Master/Slave) | Direction<br>(Master/<br>Slave) | Description                                                                 |

|---------------------------|---------------------------------|-----------------------------------------------------------------------------|

| m/s_axis_tvalid           | Out/In                          | Valid indicator for m/s_axis_tdata, m/s_axis_tlast, m/s_axis_tuser signals. |

| m/s_axis_tdata[63:0]      | Out/In                          | Data                                                                        |

| m/s_axis_tlast            | Out/In                          | High at the last word of the output packet                                  |

|                           |                                 |                                                                             |

| Signals<br>(Master/Slave) | Direction<br>(Master/<br>Slave) | Description     |                                                                             |                     |                                                                 |  |  |  |

|---------------------------|---------------------------------|-----------------|-----------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------|--|--|--|

|                           |                                 | Bit             | Abbreviation                                                                | Descript            | ion                                                             |  |  |  |

|                           |                                 | 0               | Packet Start                                                                | High on<br>output p | ly at the first valid word of the<br>backet.                    |  |  |  |

|                           |                                 | 2:1             | Protocol Version                                                            | version ("00")      |                                                                 |  |  |  |

|                           |                                 | 14:3            | Channel Number                                                              | Shall be            | valid at packet start                                           |  |  |  |

|                           |                                 | 15              | Reserved                                                                    |                     |                                                                 |  |  |  |

|                           |                                 | 26:16           | Packet Length                                                               |                     | valid at payload start. It is the<br>backet length in bytes.    |  |  |  |

| Ť ()                      |                                 | 27              | Reserved                                                                    |                     |                                                                 |  |  |  |

|                           |                                 |                 |                                                                             | 0000                | UDP encapsulated                                                |  |  |  |

| m/s_axis_tuser[31:0]      | Out/In                          |                 |                                                                             | 0001                | RTP encapsulated SMPTE ST<br>2022-2 compliant media<br>packet   |  |  |  |

|                           |                                 | 2               | ×.+                                                                         | 0010                | RTP encapsulated SMPTE ST<br>2022-1 compliant Column<br>FEC     |  |  |  |

|                           |                                 | 31:28           | つ,                                                                          | 0011                | RTP encapsulated SMPTE ST<br>2022-1 compliant Row FEC<br>packet |  |  |  |

|                           |                                 |                 | Packet Type                                                                 | 0101                | RTP encapsulated SMPTE ST<br>2022-6 compliant media<br>packet   |  |  |  |

|                           |                                 |                 |                                                                             | 0110                | RTP encapsulated SMPTE ST<br>2022-5 compliant Column<br>packet  |  |  |  |

|                           |                                 |                 |                                                                             | 0111                | RTP encapsulated SMPTE ST<br>2022-5 compliant Row FEC<br>packet |  |  |  |

|                           |                                 |                 |                                                                             | 1000                | RTP encapsulated RFC4175<br>compliant media packet              |  |  |  |

|                           |                                 |                 |                                                                             | 1001                | RTP encapsulated RFC3190 compliant media packet                 |  |  |  |

| m/s_axis_tready           | In/Out                          | TREAD<br>cycle. | TREADY indicates that the slave can accept a transfer in the current cycle. |                     |                                                                 |  |  |  |

#### Table 2-4: RTP over AXI4-Stream Interface Protocol (Cont'd)

# SDI over AXI4-Stream Interface Protocol (Master or Slave Interfaces)

#### Table 2-5: SDI over AXI4-Stream Interface Protocol (Master or Slave Interfaces)

| Signals         | Direction<br>(Master/Slave) | Descrip                                                                     | Description           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|-----------------|-----------------------------|-----------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| sdi_axis_tready | In/Out                      | TREADY indicates that the slave can accept a transfer in the current cycle. |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| sdi_axis_tvalid | Out/In                      | Valid ir<br>signals.                                                        |                       | _axis_tdata, sdi_axis_tlast, and sdi_axis_tuser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| sdi_axis_tlast  | Out/In                      | Togeth                                                                      | er with sdi_axis      | _tdata to indicate the last word of the frame.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                 | •                           | Bit                                                                         | Native SDI<br>Mapping | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| sdi_axis_tdata  | Out/In                      | 9:0                                                                         | ds1a<br>ds2a          | <ul> <li>Video data stream 1 which is dependent on the SDI mode:</li> <li>SD-SDI: Multiplexed Y/C data stream</li> <li>HD-SDI: Y data stream</li> <li>3G-SDI level A: Data stream 1</li> <li>3G-SDI level B-DL: Data stream 1 of link A</li> <li>3G-SDI level B-DS: Y data stream of HD-SDI signal 1</li> <li>Video data stream 2 which is dependent on the SDI mode:</li> <li>SD-SDI: Not used</li> <li>HD-SDI: C data stream</li> <li>3G-SDI level B-DL: Data stream 2 of link A</li> <li>3G-SDI level B-DL: Cata stream 2 of link A</li> <li>3G-SDI level B-DL: C data stream 2 of link A</li> <li>3G-SDI level B-DL: C data stream 1 of link A</li> </ul> |  |  |  |  |

|                 |                             | 29:20                                                                       | ds1b                  | <ul> <li>This is only used in 3G-SDI level B mode.</li> <li>The data stream on this port is:</li> <li>3G-SDI level B-DL: Data stream 1 of link B</li> <li>3G-SDI level B-DS: Y data stream of<br/>HD-SDI signal 2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                 |                             | 39:30                                                                       | ds2b                  | <ul> <li>This is only used in 3G-SDI level B mode.</li> <li>The data stream on this port is:</li> <li>3G-SDI level B-DL: Data stream 2 of link B</li> <li>3G-SDI level B-DS: C data stream of<br/>HD-SDI signal 2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                 |                             | 63:40                                                                       |                       | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Signals               | Direction<br>(Master/Slave) | Descrip     | Description                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                |  |  |

|-----------------------|-----------------------------|-------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|

|                       |                             | Bit         | Abbreviatio<br>n                                                                                              | Descri                                                                                                                                                                                                                                                                                                                                                                       | ption                                                                          |  |  |

|                       |                             | 0           | sof                                                                                                           | Indicat                                                                                                                                                                                                                                                                                                                                                                      | tes Start of Frame                                                             |  |  |

|                       |                             | 1           | Reserved                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                |  |  |

|                       |                             |             |                                                                                                               | 00                                                                                                                                                                                                                                                                                                                                                                           | HD-SDI                                                                         |  |  |

|                       |                             | 3:2         | sdi_mode                                                                                                      | 01                                                                                                                                                                                                                                                                                                                                                                           | SD-SDI                                                                         |  |  |

|                       |                             | 5.2         | sul_mode                                                                                                      | 10                                                                                                                                                                                                                                                                                                                                                                           | 3G-SDI                                                                         |  |  |

|                       | •                           |             |                                                                                                               | 11                                                                                                                                                                                                                                                                                                                                                                           | Invalid Video Format                                                           |  |  |

| sdi_axis_tuser Out/In | S                           | 4           |                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                              | vhen the input signal is level B and<br>hen it is level A. This output is only |  |  |

|                       | 5                           | rx_bit_rate | being<br>modes<br>When<br>FPGAs<br>contro<br>that go<br>to the<br>HD-SD<br>• rx_b<br>Gb/s<br>• rx_b<br>• rx_b | using the transceivers in Xilinx<br>, the device-specific transceiver<br>Il module contains a bit rate detector<br>enerates the signal to be connected<br>rx_bit_rate input port.<br>DI mode:<br>it_rate = 0: Bit rate = 1.485 Gb/s<br>it_rate = 1: Bit rate = 1.485/1.001<br>s 3G-SDI mode:<br>it_rate = 0: Bit rate = 2.97 Gb/s<br>it_rate = 1: Bit rate = 2.97/1.001 Gb/s |                                                                                |  |  |

|                       |                             | 29:6        | vid_src_fmt                                                                                                   | Bit<br>29:26<br>25:18<br>17:10<br>9:6                                                                                                                                                                                                                                                                                                                                        | Description<br>MAP<br>FRAME<br>FRATE<br>SAMPLE                                 |  |  |

|                       |                             | 31:30       | Reserved                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                              |  |  |

#### Table 2-5: SDI over AXI4-Stream Interface Protocol (Master or Slave Interfaces) (Cont'd)

### ST 2022-6 Packetizer Port Descriptions

| Signal                | Direction | Description                                       |

|-----------------------|-----------|---------------------------------------------------|

| core_clk              | input     | Main clock for the core.                          |

| core_reset            | input     | Main reset for the core, high active.             |

| rtp_timestamp[31:0]   | input     | Used inside RTP header.                           |

| video_timestamp[31:0] | input     | Used inside SMPTE ST 2022-6 media payload header. |

#### Table 2-6: ST 2022-6 Packetizer Port Description

#### Notes:

1. For sdi\_axis interface refer to SDI over AXI4-Stream Interface Protocol (Master or Slave Interfaces).

2. For m\_axis interface refer to

## ST 2022-6 Depacketizer Port Descriptions

| Signal     | Direction | Description                                                                                                                                                 |  |  |  |

|------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| core_clk   | input     | Main clock for the core.                                                                                                                                    |  |  |  |

| core_reset | input     | Main reset for the core, active-High.                                                                                                                       |  |  |  |

| pkt_rdy    | input     | Used to indicate ST 2022-6 Depacketizer to request packet.                                                                                                  |  |  |  |

| pkt_req    | output    | Single cycle pulse to request for a packet, generated only when pkt_rdy is High.                                                                            |  |  |  |

| interrupt  | output    | Active-High interrupt, which is asserted when any interrupt source<br>in the module is triggered. It will go down when all interrupt source<br>are cleared. |  |  |  |

#### Table 2-7: ST 2022-6 Depacketizer Port Descriptions

#### Notes:

1. For sdi\_axis interface refer to SDI over AXI4-Stream Interface Protocol (Master or Slave Interfaces).

2. For s\_axis interface refer to RTP over AXI4-Stream Interface Protocol

### **Framer Port Descriptions**

| Table 2-8: | Framer F | ort D | escriptions |

|------------|----------|-------|-------------|

|            |          |       |             |

| Signal        | Direction | Description                                                                 |

|---------------|-----------|-----------------------------------------------------------------------------|

| s_axis_clk    | input     | Clock for s_axis interface logic.                                           |

| s_axis_rst    | input     | Active-High reset for s_axis interface logic.                               |

| m_axis_clk    | input     | Clock for m_axis interface logic.                                           |

| m_axis_rst    | input     | Active-High reset for m_axis interface logic.                               |

| m_axis_tready | input     | TREADY indicates that the slave can accept a transfer in the current cycle. |

| m_axis_tvalid | output    | Valid indicator for m_axis_tdata, m_axis_tlast, and m_axis_tuser signals.   |

| Signal             | Direction | Description                                 |  |  |  |

|--------------------|-----------|---------------------------------------------|--|--|--|

| m_axis_tlast       | output    | High at the last word of the output packet. |  |  |  |

| m_axis_tdata(63:0) | output    | Data                                        |  |  |  |

| m_axis_tkeep(7:0)  | output    | Byte enable for each byte in m_axis_tdata.  |  |  |  |

#### Table 2-8: Framer Port Descriptions (Cont'd)

#### Notes:

1. For  $s_{axis}$  interface refer to RTP over AXI4-Stream Interface Protocol.

# **Decapsulator Port Descriptions**

### Table 2-9: Decapsulator Port Descriptions

| Signal             | Direction | Description                                                                                                                                                                                    |  |  |

|--------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| s_axis_clk         | input     | Clock for s_axis interface logic.                                                                                                                                                              |  |  |

| s_axis_rst         | input     | Active-High reset for s_axis interface logic.                                                                                                                                                  |  |  |

| m_axis_clk         | input     | Clock for m_axis interface logic.                                                                                                                                                              |  |  |

| m_axis_rst         | input     | Active-High reset for m_axis interface logic.                                                                                                                                                  |  |  |

| s_axis_tready      | output    | TREADY indicates that the slave can accept a transfer in the current cycle.                                                                                                                    |  |  |

| s_axis_tvalid      | input     | Valid indicator for m_axis_tdata, m_axis_tlast, and m_axis_tuser signals.                                                                                                                      |  |  |

| s_axis_tlast       | input     | High at the last word of the output packet                                                                                                                                                     |  |  |

| s_axis_tdata[63:0] | input     | Data                                                                                                                                                                                           |  |  |

| s_axis_tkeep[7:0]  | input     | Byte enable for each byte in s_axis_tdata.<br><i>Note:</i> Currently this port is not used inside the design.                                                                                  |  |  |

| s_axis_tuser       | input     | Single bit signal to indicate that the current packet is a good or bad packet. And it is sampled when s_axis_tlast is valid. If you do not want to connect this signal, please tie it to High. |  |  |

| interrupt          | output    | Active-High interrupt, which is asserted when any interrupt sour<br>in the module is triggered. It will go down when all interrupt sour<br>are cleared.                                        |  |  |

| Notes:             |           |                                                                                                                                                                                                |  |  |

#### Notes:

1. For m\_axis interface refer to

# **Register Space**

### ST 2022-6 Packetizer Module Register Space

| Address         |                | Access                             | Cleared               | Default        |                  | Description                                                             |                             |  |

|-----------------|----------------|------------------------------------|-----------------------|----------------|------------------|-------------------------------------------------------------------------|-----------------------------|--|

| Offset<br>(HEX) | Register Name  | Type (HW:<br>hardware<br>writable) | with<br>SOFT<br>reset | Value<br>(HEX) | Bit<br>Range     | Value                                                                   |                             |  |

|                 |                | •                                  |                       |                |                  |                                                                         | Control                     |  |

|                 |                |                                    |                       |                | 31:1             | 31:1 Reserved                                                           |                             |  |

| 0x0000          | control        | R/W                                | N                     | 0x00000000     |                  |                                                                         | Soft reset                  |  |

|                 |                |                                    |                       |                | 0                | 1                                                                       | Reset all pcore registers   |  |

|                 |                | 6                                  |                       |                |                  | 0                                                                       | Unreset the pcore registers |  |

|                 |                |                                    | 6                     |                |                  | Peak P                                                                  | acket Buffer Level          |  |

| 0x0008          | peak_buf_level | R                                  | Y                     | 0x00000000     | 31:6             | Reserve                                                                 | ed                          |  |

| 0,0000          | peak_bal_level | IX                                 |                       |                | 5:0              | Peak packet buffer level, in numbe of packets.                          |                             |  |

|                 |                | R                                  |                       | 0x01000000     | Hardware version |                                                                         |                             |  |

|                 |                |                                    |                       |                | 31:24            | 4 Version major                                                         |                             |  |

| 0x000C          | version        |                                    | N                     |                | 23:16            | 3:16 Version minor                                                      |                             |  |

| 0,0000          | version        |                                    |                       |                | 15:12            | Version                                                                 | revision                    |  |

|                 |                |                                    |                       |                | 11:8             | Patch II                                                                | D                           |  |

|                 |                |                                    |                       |                | 7:0              | Revisio                                                                 | n number                    |  |

|                 |                |                                    |                       |                |                  | M                                                                       | odule Control               |  |

|                 |                |                                    |                       |                | 31:28            | Reserved                                                                |                             |  |

|                 |                |                                    |                       |                | 27:16            | Channel number, which is reflected in the tuser output bit 14 to bit 3. |                             |  |

|                 |                |                                    |                       |                | 15:2             | Reserve                                                                 | ed                          |  |

| 0x0010          | module_ctrl    | R/W                                | Y                     | 0x00000000     |                  | Lossles                                                                 | s mode configuration        |  |

|                 |                |                                    |                       |                | 1                | 0                                                                       | Normal mode                 |  |

|                 |                |                                    |                       |                | -                | 1                                                                       | Lossless mode               |  |

|                 |                |                                    |                       |                |                  | Module                                                                  | e Enable                    |  |

|                 |                |                                    |                       |                | 0                | 0                                                                       | Module is disabled.         |  |

|                 |                |                                    |                       |                |                  | 1                                                                       | Module is enabled.          |  |

Table 2-10: ST 2022-6 Packetizer Module Register Map

|                            | Register Name | Access<br>Type (HW:<br>hardware<br>writable) | Cleared<br>with<br>SOFT<br>reset | Default<br>Value<br>(HEX) | Description  |                                                          |                                                                                                                 |

|----------------------------|---------------|----------------------------------------------|----------------------------------|---------------------------|--------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Address<br>Offset<br>(HEX) |               |                                              |                                  |                           | Bit<br>Range | Value                                                    |                                                                                                                 |