PB019 (v4.0) May 22, 2019

LogiCORE IP Product Brief

# Introduction

The Xilinx® LogiCORE™ IP LTE DL Channel Encoder core provides designers with an LTE Downlink Channel Encoding block for the 3GPP TS 36.212 v9.0.0 Multiplexing and Channel Coding specification.

# **Additional Documentation**

A full product guide is available for this core. Access to this material can be requested by clicking on this registration link: www.xilinx.com/member/ Ite\_dl\_channel\_enc\_eval/index.html.

# Features

- Channel coding for 3GPP TS 36.212 supports:

- Downlink shared channel (DL-SCH)

- Paging channel (PCH)

- Multicast channel (MCH)

- Broadcast channel (BCH)

- Control format indicator (CFI)

- HARQ indicator (HI)

- Downlink control information (DCI)

- 8, 16, and 32 bit operation for DL-SCH, PCH, and MCH

- Bit-accurate C model available

- Fully optimized for speed and area

- Fully synchronous design using a single clock

| LogiCORE IP Facts Table<br>Core Specifics         |                                                                             |  |

|---------------------------------------------------|-----------------------------------------------------------------------------|--|

|                                                   |                                                                             |  |

| Supported User<br>Interfaces                      | Can be interfaced to AXI4-Stream <sup>(2)</sup>                             |  |

|                                                   | Provided with Core                                                          |  |

| Design Files                                      | Netlist                                                                     |  |

| Example Design                                    | Not Provided                                                                |  |

| Test Bench                                        | VHDL                                                                        |  |

| Constraints File                                  | Not Provided                                                                |  |

| Simulation<br>Model                               | VHDL or Verilog Structural<br>C Model                                       |  |

| Supported S/W<br>Driver                           | N/A                                                                         |  |

| Tested Design Tools                               |                                                                             |  |

| Design Entry<br>Tools                             | Vivado® Design Suite                                                        |  |

| Simulation                                        | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |

| Synthesis Tools                                   | Vivado Synthesis                                                            |  |

| Support                                           |                                                                             |  |

| Provided by Xilinx at the Xilinx Support web page |                                                                             |  |

| Provided by                                       | Vivado Synthes Support                                                      |  |

- For a complete list of supported devices, see the Vivado IP catalog.

- 2. Interface similar to AXI and can be connected to an AXI4-Stream interface.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

<sup>©</sup> Copyright 2014–2019 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

## Overview

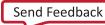

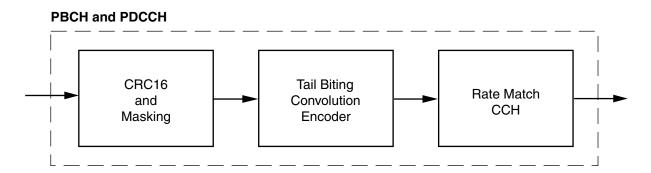

The LTE DL Channel Encoder core provides a channel encoding solution for the 3GPP 36.212 specification. Figure 1 and Figure 2 respectively illustrate the main blocks in the LTE encoding chain for the two main channel types that are supported by the core. The architecture has been designed to provide efficient use of the FPGA while also offering a low bandwidth processor interface to reduce system-level overhead. Timing-critical operations are performed by the FPGA.

The interface to the core can be attached to any AXI4-Stream system. The memory-mapped interface allows for simple integration and validation within the system.

Data is processed sequentially on a transport block basis for each of the two main channel types, where the term "transport block" is used to describe a block of data originating from the MAC layer. Specific processing is applied depending on the type of input block, which is indicated as part of the control signaling provided by the MAC layer.

The following functions are supported by the core:

- CRC

- 24-bit CRC applied to DL-SCH, PCH, and MCH transport blocks

- 16-bit CRC applied to BCH and DCI code blocks (with additional scrambling on parity bits)

- Segmentation

- Code block segmentation applied to DL-SCH, PCH, and MCH transport blocks (that is, data which is subjected to turbo encoding), with an additional 24-bit CRC computed on each code block (in cases where segmentation produces more than one code block)

- Encoding

- Turbo code applied to DL-SCH, PCH, and MCH data

- Convolutional code applied to BCH and DCI data (single code block)

- Rate Matching

- Applied on a code block basis to DL-SCH, PCH, MCH, BCH, and DCI data. This function performs appropriate puncturing according to the AMC parameters and redundancy version.

- Data output on a code block basis for the DL-SCH, PCH, and MCH channels.

- Control Format Indicator Generation

- The HI or CFI coded outputs are generated according to the type indicated from the control signaling from the MAC layer.

#### **Control and Broadcast Channel Processing**

Figure 1: Downlink Channel Processing for BCH and DCI -CCH Channel Stream

#### Shared, Paging, and Multicast Channel Processing

Figure 2: Downlink Channel Processing for DL-SCH, PCH and MCH -SCH Channel Stream

## **Technical Support**

Xilinx provides technical support at the Xilinx Support web page for this LogiCORE<sup>™</sup> IP product when used as described in the product documentation. Xilinx cannot guarantee timing, functionality, or support if you do any of the following:

- Implement the solution in devices that are not defined in the documentation.

- Customize the solution beyond that allowed in the product documentation.

- Change any section of the design labeled DO NOT MODIFY.

To contact Xilinx Technical Support, navigate to the Xilinx Support web page.

### **Licensing and Ordering Information**

This Xilinx LogiCORE IP module is provided under the terms of the Xilinx Turbo Code LogiCORE IP License Terms. The module is shipped as part of the Vivado Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your local Xilinx sales representative for information about pricing and availability.

For more information, visit the LTE DL Channel Encoder product web page.

Information about other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

*Disclaimer:* France Telecom, for itself and certain other parties, claims certain intellectual property rights covering Turbo Codes technology, and has decided to license these rights under a licensing program called the Turbo Codes Licensing Program. Supply of this IP core does not convey a license nor imply any right to use any Turbo Codes patents owned by France Telecom, TDF or GET. Contact France Telecom for information about its Turbo Codes Licensing Program at the following address:

France Telecom R&D, VAT/TURBOCODES, 38, rue du Général Leclerc, 92794 Issy Moulineaux, Cedex 9, France.

#### **Revision History**

The following table shows the revision history for this document:

| Date       | Version | Revision                                               |

|------------|---------|--------------------------------------------------------|

| 05/22/2019 | 4.0     | Updated to align with Product Guide (PG069) updates.   |

| 04/05/2017 | 3.0     | Corrected lower limit of CCH size in PG069.            |

| 11/18/2015 | 3.0     | Added support for UltraScale+ families.                |

| 06/04/2014 | 3.0     | Initial Xilinx release. This document replaces XMP023. |

### **Please Read: Important Legal Notices**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials without prior written consent. Certain products are subject to the terms and conditions of Xilinx's limited warranty, please refer to Xilinx's Terms of Sale which can be viewed at http://www.xilinx.com/legal.htm#tos; IP cores may be subject to warranty and support terms of Sale which can be viewed at http://www.xilinx.com/legal.htm#tos.

#### AUTOMOTIVE APPLICATIONS DISCLAIMER

AUTOMOTIVE PRODUCTS (IDENTIFIED AS "XA" IN THE PART NUMBER) ARE NOT WARRANTED FOR USE IN THE DEPLOYMENT OF AIRBAGS OR FOR USE IN APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE ("SAFETY APPLICATION") UNLESS THERE IS A SAFETY CONCEPT OR REDUNDANCY FEATURE CONSISTENT WITH THE ISO 26262 AUTOMOTIVE SAFETY STANDARD ("SAFETY DESIGN"). CUSTOMER SHALL, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE PRODUCTS, THOROUGHLY TEST SUCH SYSTEMS FOR SAFETY PURPOSES. USE OF PRODUCTS IN A SAFETY APPLICATION WITHOUT A SAFETY DESIGN IS FULLY AT THE RISK OF CUSTOMER, SUBJECT ONLY TO APPLICABLE LAWS AND REGULATIONS GOVERNING LIMITATIONS ON PRODUCT LIABILITY.