# JESD204C v1.0

# LogiCORE IP Product Guide

Vivado Design Suite

PG242 June 7, 2017

# **Table of Contents**

#### **IP Facts**

###

### **Chapter 3: Designing with the Core**

| Clocking | 18 |

|----------|----|

| Resets   | 22 |

### **Chapter 4: Design Flow Steps**

| Customizing and Generating the Core | 23 |

|-------------------------------------|----|

| Configuring the JESD204 PHY in IPI  | 27 |

| Constraining the Core               | 28 |

| Simulation                          | 30 |

| Synthesis and Implementation        | 30 |

#### **Chapter 5: Example Design**

#### Chapter 6: Test Bench

#### Appendix A: Verification, Compliance, and Interoperability

Appendix B: Upgrading

#### Appendix C: Debugging

| Debug Tools      | 39 |

|------------------|----|

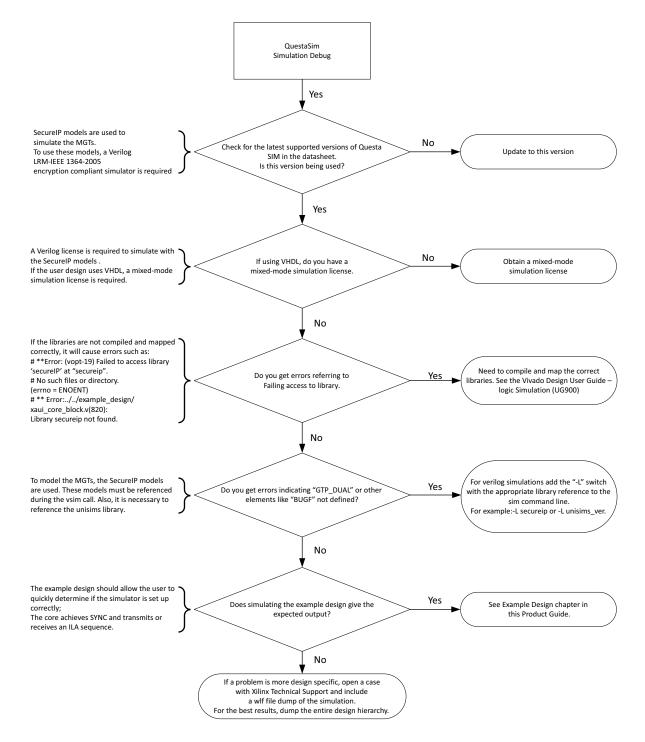

| Simulation Debug | 40 |

| Hardware Debug   | 41 |

| Interface Debug  | 41 |

## Appendix D: Additional Resources and Legal Notices

| Xilinx Resources                        | 43 |

|-----------------------------------------|----|

| Documentation Navigator and Design Hubs | 43 |

| References                              | 43 |

| Revision History                        | 44 |

| Please Read: Important Legal Notices    | 45 |

## **IP Facts**

# Introduction

The Xilinx® LogiCORE<sup>™</sup> IP JESD204C core implements a JESD204C (Draft standard [9]) compatible interface supporting line rates from 1 Gb/s to 32 Gb/s. The JESD204C core can be configured as a transmitter or receiver.<sup>(1)</sup>

## Features

- Designed to JEDEC® JESD204C-100 and JESD204C-300 Draft Standard

- Supports up to eight lanes per core and greater number of lanes using multiple cores

- Supports 64b66b link layer

- Supports CRC and CMD meta data modes

- Supports subclass 0 and 1

- Provides physical and data link layer functions when used in conjunction with the JESD204\_PHY core

- AXI4-Lite configuration interface

- AXI4-Stream Data and Command interfaces

- Supports Transceiver sharing between TX and RX cores using the JESD204\_PHY core

| LogiCORE IP Facts Table                           |                                                                             |  |  |

|---------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| Core Specifics                                    |                                                                             |  |  |

| Supported<br>Device Family <sup>(1)</sup>         | UltraScale+™, UltraScale™                                                   |  |  |

| Supported User<br>Interfaces                      | AXI4-Lite, AXI4-Stream                                                      |  |  |

| Resources                                         | Performance and Resource Utilization web page                               |  |  |

|                                                   | Provided with Core                                                          |  |  |

| Design Files                                      | Encrypted RTL                                                               |  |  |

| Example Design                                    | Verilog                                                                     |  |  |

| Test Bench                                        | Verilog                                                                     |  |  |

| Constraints File                                  | XDC                                                                         |  |  |

| Simulation<br>Model                               | Verilog                                                                     |  |  |

| Supported<br>S/W Driver                           | N/A                                                                         |  |  |

|                                                   | Tested Design Flows <sup>(2)</sup>                                          |  |  |

| Design Entry                                      | Vivado® Design Suite                                                        |  |  |

| Simulation                                        | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |  |

| Synthesis                                         | Vivado Synthesis                                                            |  |  |

| Support                                           |                                                                             |  |  |

| Provided by Xilinx at the Xilinx Support web page |                                                                             |  |  |

#### Notes:

- 1. For a complete listing of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

1. The maximum line rate supported is dependent on the transceiver type and speed grade of the selected device.

# Chapter 1

# Overview

The LogiCORE<sup>™</sup> IP JESD204C core implements a JESD204C-300 link layer. When used in conjunction with the LogiCORE<sup>™</sup> IP JESD204\_PHY core (to provide the physical layer), a JESD204C system can be created supporting line rates between 1 and 32 Gb/s on 1 to 8 lanes using GTYE4 and GTYE3 (UltraScale+ and UltraScale) transceivers. See the device data sheets for maximum line rates supported by each device and family. The JESD204C core can be configured as transmit or receive and multiple cores can be used to realize links requiring more than eight lanes.

The JESD204C core is delivered by using the Xilinx® Vivado® Design Suite. In addition, an example design is provided in Verilog.

## **Unsupported Features**

Sample data mapping/demapping is not provided by the core, because of the requirement that it be customized for different converter devices. For more information see applicable converter datasheets.

# **Licensing and Ordering**

## **License Checkers**

If the IP requires a license key, the key must be verified. The Vivado design tools have several license checkpoints for gating licensed IP through the flow. If the license check succeeds, the IP can continue generation. Otherwise, generation halts with error. License checkpoints are enforced by the following tools:

- Vivado synthesis

- Vivado implementation

- write\_bitstream (Tcl command)

**IMPORTANT:** *IP license level is ignored at checkpoints. The test confirms a valid license exists. It does not check IP license level.*

## License Type

This Xilinx LogiCORE IP module is provided under the terms of the Xilinx Core License Agreement. The module is shipped as part of the Vivado Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your local Xilinx sales representative for information about pricing and availability.

For more information, visit the JESD204C product web page.

Information about other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

A free evaluation version of the core is provided with the Xilinx Vivado Design Suite which lets you assess the core functionality and demonstrates the various interfaces of the core in simulation. To access the evaluation version visit the JESD204 IP Evaluation page.

## **License Options**

The JESD204C core provides three licensing options. After installing the Vivado Design Suite and the required IP Service Packs, choose a license option.

### Simulation Only

The Simulation Only Evaluation license key is provided with the Xilinx Vivado Design Suite. This key lets you assess core functionality with either the example design provided with the JESD204C core, or alongside your own design and demonstrates the various interfaces to the core in simulation. (Functional simulation is supported by a dynamically generated HDL structural model.)

#### Full System Hardware Evaluation

The Full System Hardware Evaluation license is available at no cost and lets you fully integrate the core into an FPGA design, place-and-route the design, evaluate timing, and perform functional simulation of the JESD204C core using the example design and demonstration test bench provided with the core.

In addition, the license key lets you generate a bitstream from the placed and routed design, which can then be downloaded to a supported device and tested in hardware. The core can be tested in the target device for a limited time before timing out (ceasing to function), at which time it can be reactivated by reconfiguring the device.

### Full

The Full license key is available when you purchase the core and provides full access to all core functionality both in simulation and in hardware, including:

- Gate-level functional simulation support

- Back annotated gate-level simulation support

- Functional simulation support

- Full-implementation support including place and route and bitstream generation

- Full functionality in the programmed device with no time-outs

## **Obtaining Your License Key**

This section contains information about obtaining a simulation, full system hardware, and full license keys.

#### Simulation License

No action is required to obtain the Simulation Only Evaluation license key; it is provided by default with the Xilinx Vivado Design Suite.

#### Full System Hardware Evaluation License

To obtain a Full System Hardware Evaluation license, perform these steps:

- 1. Navigate to the JESD204 product page for this core.

- 2. Click Evaluate.

- 3. Follow the instructions on the page.

#### **Obtaining a Full License**

To obtain a Full license key, you must purchase a license for the core. After doing so, click the **Access Core** link on the xilinx.com IP core product page for further instructions.

## **Installing Your License File**

The Simulation only Evaluation license key is provided with the Vivado Design Suite and does not require installation of an additional license file. For the Full System Hardware Evaluation license and the Full license, an email will be sent to you containing instructions for installing your license file. Additional details about IP license key installation can be found in the Vivado Design Suite Installation, Licensing and Release Notes document.

Chapter 2

# **Product Specification**

The JESD204C core is used in conjunction with the JESD204\_PHY core to support the draft JESD204C-100 physical layer and JESD204C-300 link layer specification.

# Standards

JEDEC® Serial interface for Data Converters JESD204C draft [Ref 9].

# Performance

For details about performance, visit the Performance and Resource Utilization web page.

## **Resource Utilization**

For details about resource utilization, visit the Performance and Resource Utilization web page.

# **Port Descriptions**

The port descriptions for the JESD204C core are described in the following sections.

## **TX** Core

| Signal Name                 | Interface                            | Direction | Description                                                                                                                                                                                                                                                                                                                                         |  |

|-----------------------------|--------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| System Signals              |                                      |           |                                                                                                                                                                                                                                                                                                                                                     |  |

| tx_core_clk                 | System<br>s_axis_tx<br>s_axis_tx_cmd | I         | Core logic clock input.<br>Frequency = serial line rate/66                                                                                                                                                                                                                                                                                          |  |

| tx_core_reset               | System                               | Ι         | Core asynchronous logic reset active high.                                                                                                                                                                                                                                                                                                          |  |

| tx_aresetn                  | s_axis_tx<br>s_axis_tx_cmd           | 0         | AXI4-Stream interface reset. Active low.<br>Associated with both data and command<br>interfaces.                                                                                                                                                                                                                                                    |  |

| tx_reset_gt                 | System                               | 0         | JESD204_PHY TX datapath reset. Core output to<br>reset the transmit datapath in a connected<br>JESD204_PHY. This must be connected to a<br>JESD204_PHY.                                                                                                                                                                                             |  |

| tx_reset_done               | System                               | Ι         | JESD204_PHY TX reset done input. Indicates the JESD204_PHY has completed the transmit reset process.                                                                                                                                                                                                                                                |  |

| s_axi_aclk                  | s_axi                                | Ι         | AXI4-Lite clock input.                                                                                                                                                                                                                                                                                                                              |  |

| s_axi_aresetn               | s_axi                                | Ι         | AXI4-Lite reset input. Active low.                                                                                                                                                                                                                                                                                                                  |  |

| s_axi*                      | s_axi                                | Ι         | See Appendix A of the Vivado AXI Reference<br>Guide (UG1037) [Ref 10] for a description of<br>AXI4 signals.                                                                                                                                                                                                                                         |  |

| irq                         | System                               | 0         | System interrupt output.                                                                                                                                                                                                                                                                                                                            |  |

| tx_sysref                   | System                               | Ι         | SYSREF input.<br>When Subclass 1 mode is selected, this signal is<br>required and used by the core to set the phase<br>of the local extended multi-block clock. This<br>SYSREF signal must be generated synchronous<br>to the core clock. This input should be driven<br>from an external device generating SYSREF for<br>both TX and RX on a link. |  |

| JESD204_PHY Interface Ports |                                      |           |                                                                                                                                                                                                                                                                                                                                                     |  |

| gtN_txdata[63:0]            | РНҮ                                  | 0         | TX data to JESD204 PHY. N = Lanes - 1                                                                                                                                                                                                                                                                                                               |  |

| gtN_txheader[1:0]           | РНҮ                                  | 0         | TX header to JESD204 PHY. N = Lanes - 1                                                                                                                                                                                                                                                                                                             |  |

| Transmit Interface          |                                      |           |                                                                                                                                                                                                                                                                                                                                                     |  |

| tx_tdata [(64*N)-1:0        | s_axis_tx                            | Ι         | Transmit data input. N = Lanes - 1                                                                                                                                                                                                                                                                                                                  |  |

| Signal Name             | Interface     | Direction | Description                                                                                                                                                           |  |

|-------------------------|---------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| tx_tready               | s_axis_tx     | 0         | AXI4-Stream tready.                                                                                                                                                   |  |

| tx_tuser                | s_axis_tx     | 0         | AXI4-Stream tuser. Set to 1 on the cycle that marks the start of an extended multi-block. 0 otherwise.                                                                |  |

| tx_cmd_tdata[(19*N)-1:0 | s_axis_tx_cmd | Ι         | Transmit Cmd interface N = Lanes - 1<br>For Meta mode = CRC, Cmd payload is bits [6:0]<br>with bits [18:7] set to Zero.<br>For Meta mode = Cmd, Cmd payload is [18:0] |  |

| tx_cmd_tvalid           | s_axis_tx_cmd | Ι         | AXI4-Stream tvalid.                                                                                                                                                   |  |

| tx_cmd_tready           | s_axis_tx_cmd | 0         | AXI4-Stream tready. tx_cmd_tready will be set<br>for 1 cycle every multi-block to control the Cmc<br>word flow.                                                       |  |

#### Table 2-1: TX Core: Port Descriptions

## **RX Core**

| Signal Name    | Interface                            | Direction | Description                                                                                                                                            |  |  |

|----------------|--------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| System Signals |                                      |           |                                                                                                                                                        |  |  |

| rx_core_clk    | System<br>s_axis_rx<br>s_axis_rx_cmd | Ι         | Core logic clock input.<br>Frequency = serial line rate/66                                                                                             |  |  |

| rx_core_reset  | System                               | Ι         | Core asynchronous logic reset active high.                                                                                                             |  |  |

| rx_aresetn     | s_axis_rx<br>s_axis_rx_cmd           | 0         | AXI4-Stream interface reset. Active low.<br>Associated with both data and command<br>interfaces.                                                       |  |  |

| rx_reset_gt    | System                               | 0         | JESD204_PHY RX datapath reset. Core output to<br>reset the receive datapath in a connected<br>JESD204_PHY. This must be connected to a<br>JESD204_PHY. |  |  |

| rx_reset_done  | System                               | Ι         | JESD204_PHY RX reset done input. Indicates the JESD204_PHY has completed the receive reset process.                                                    |  |  |

| s_axi_aclk     | s_axi                                | Ι         | AXI4-Lite clock input.                                                                                                                                 |  |  |

| s_axi_aresetn  | s_axi                                | Ι         | AXI4-Lite reset input. Active Low.                                                                                                                     |  |  |

| s_axi*         | s_axi                                | I         | See Appendix A of the Vivado AXI Reference<br>Guide (UG1037) [Ref 10] for a description of<br>AXI4 signals.                                            |  |  |

| Irq            | System                               | 0         | System interrupt output.                                                                                                                               |  |  |

#### Table 2-2: TX Core: Port Descriptions

| Signal Name             | Interface     | Direction   | Description                                                                                                                                                                                                                                                                                                                                      |  |

|-------------------------|---------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| rx_sysref               | System        | Ι           | SYSREF input. When Subclass 1 mode is<br>selected, this signal is required and used by the<br>core to set the phase of the local extended<br>multi-block clock. This SYSREF signal must be<br>generated synchronous to the core clock. This<br>input should be driven from an external device<br>generating SYSREF for both TX and RX on a link. |  |

|                         | JESD2         | 04_PHY Int  | terface Ports                                                                                                                                                                                                                                                                                                                                    |  |

| gtN_rxdata[63:0]        | РНҮ           | Ι           | RX data from JESD204 PHY. N = Lanes - 1                                                                                                                                                                                                                                                                                                          |  |

| gtN_rxheader[1:0]       | РНҮ           | Ι           | RX header from JESD204 PHY. N = Lanes - 1                                                                                                                                                                                                                                                                                                        |  |

| gtN_misalign            | РНҮ           | Ι           | Signal from JESD204 PHY to indicate a misaligned sync header was detected.                                                                                                                                                                                                                                                                       |  |

| gtN_block_sync          | РНҮ           | Ι           | Signal from JESD204 PHY to indicate block sync status.                                                                                                                                                                                                                                                                                           |  |

|                         |               | Receive Int | terface                                                                                                                                                                                                                                                                                                                                          |  |

| rx_tdata [(64*N)-1:0    | s_axis_rx     | 0           | Receive data output. N = Lanes - 1                                                                                                                                                                                                                                                                                                               |  |

| rx_tready               | s_axis_rx     | 0           | AXI4-Stream tready.                                                                                                                                                                                                                                                                                                                              |  |

| rx_tuser[2:0]           | s_axis_rx     | 0           | <ul><li>Axi4-Stream tuser.</li><li>Bit 0 set to 1 on the cycle that marks the start of an extended multi-block. 0 otherwise.</li><li>Bit 1 set to 1 if a multi-block alignment error was detected in the preceding multi-block. 0 otherwise.</li><li>Bit 2 set to 1 if a CRC error was detected in the preceding multi-block.</li></ul>          |  |

| rx_cmd_tdata[(19*N)-1:0 | s_axis_rx_cmd | 0           | Transmit Cmd interface N = Lanes - 1<br>For Meta mode = CRC, Cmd payload is bits [6:0]<br>with bits [18:7] set to Zero.<br>For Meta mode = Cmd, Cmd payload is [18:0]                                                                                                                                                                            |  |

| rx_cmd_tvalid           | s_axis_rx_cmd | 0           | AXI4-Stream tvalid. rx_cmd_tvalid will be set for<br>1 cycle every multiblock to control the Cmd<br>word flow.                                                                                                                                                                                                                                   |  |

| rx_cmd_tready           | s_axis_rx_cmd | Ι           | AXI4-Stream tready.                                                                                                                                                                                                                                                                                                                              |  |

# **Register Space**

The JESD204C core is configured using an AXI4-Lite Register Interface. The register map is shown in Table 2-3.

The RX and TX cores share a common address map and register definitions where possible, exceptions are highlighted.

$\bigcirc$

**RECOMMENDED:** Xilinx recommends that if significant configuration changes are made using the control registers (in particular, changes to framing parameters), the core should be reset to ensure that the link is resynchronized using the updated parameters.

| AXI4-Lite<br>Address | Register Name            | TX Access Type | RX Access Type |

|----------------------|--------------------------|----------------|----------------|

| 0x000                | IP_VERSION               | R              | R              |

| 0x004                | IP_CONFIG                | R              | R              |

| 0x020                | RESET                    | RW             | RW             |

| 0x024                | CTRL_ENABLE              | RW             | RW             |

| 0x030                | CTRL_MB_IN_EMB           | RW             | RW             |

| 0x034                | CTRL_SUB_CLASS           | RW             | RW             |

| 0x038                | CTRL_META_MODE           | RW             | RW             |

| 0x040                | CTRL_LANE_ENA            | RW             | RW             |

| 0x044                | CTRL_RX_BUF_ADV          | N/A            | RW             |

| 0x048                | CTRL_TEST_MODE           | N/A            | N/A            |

| 0x04C                | CTRL_RX_MBLOCK_TH        | N/A            | RW             |

| 0x050                | CTRL_SYSREF              | RW             | RW             |

| 0x054                | STAT_LOCK_DEBUG          | N/A            | R              |

| 0x060                | STAT_STATUS              | R              | R              |

| 0x064                | CTRL_IRQ                 | RW             | RW             |

| 0x068                | STAT_IRQ                 | R              | R              |

| 0x400                | (Lane 0) STAT_RX_BUF_LVL | N/A            | R              |

| 0x410                | (Lane 0) STAT_RX_ERROR   | N/A            | R              |

| 0x480                | (Lane 1) STAT_RX_BUF_LVL | N/A            | R              |

| 0x490                | (Lane 1) STAT_RX_ERROR   | N/A            | R              |

| 0x500                | (Lane 2) STAT_RX_BUF_LVL | N/A            | R              |

| 0x510                | (Lane 2) STAT_RX_ERROR   | N/A            | R              |

| 0x580                | (Lane 3) STAT_RX_BUF_LVL | N/A            | R              |

| 0x590                | (Lane 3) STAT_RX_ERROR   | N/A            | R              |

| 0x600                | (Lane 4) STAT_RX_BUF_LVL | N/A            | R              |

| 0x610                | (Lane 4) STAT_RX_ERROR   | N/A            | R              |

#### Table 2-3: Register Address Map

| AXI4-Lite<br>Address | Register Name            | TX Access Type | RX Access Type |

|----------------------|--------------------------|----------------|----------------|

| 0x680                | (Lane 5) STAT_RX_BUF_LVL | N/A            | R              |

| 0x690                | (Lane 5) STAT_RX_ERROR   | N/A            | R              |

| 0x700                | (Lane 6) STAT_RX_BUF_LVL | N/A            | R              |

| 0x710                | (Lane 6) STAT_RX_ERROR   | N/A            | R              |

| 0x780                | (Lane 7) STAT_RX_BUF_LVL | N/A            | R              |

| 0x790                | (Lane 7) STAT_RX_ERROR   | N/A            | R              |

#### Table 2-3: Register Address Map (Cont'd)

#### Table 2-4: IP\_VERSION

| Bits  | Default<br>Value | Description          |

|-------|------------------|----------------------|

| 31:24 | -                | Version: Major       |

| 23:16 | _                | Version: Minor       |

| 15:8  | -                | Version: Revision    |

| 7:0   | —                | Reserved (read 0x00) |

#### Register Address Map

#### Table 2-5: IP\_CONFIG

| Bits | Default<br>Value | Description                      |  |

|------|------------------|----------------------------------|--|

| 3:0  | -                | Number of lanes in core.         |  |

| 16   | -                | 1 = Core is TX<br>0 = Core is RX |  |

#### Register Address Map

#### Table 2-6: RESET

| Bits | Default<br>Value | Description                                                                                                                                                            |  |

|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0    | 0                | Reset. (not self-clearing)<br>1 = put core into reset<br>0 = Release core from reset<br>Once set to 0. This bit will read back 1 until the reset process is completed. |  |

#### Table 2-7:CTRL\_ENABLE

| Bits | Default<br>Value | Description                                                                                                                                                               |  |

|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0    | 0                | Enable Cmd interface.<br>1 = Enables the AXI4-Stream Cmd interface and the associated processing of the sync<br>header meta data.<br>0 = Cmd words will be zeroed.        |  |

| 1    | 0                | Enable Data Interface.<br>1 = Enables the AXI4-Stream Data interface and transmits/receives data on the link.<br>0 = The link will be transmitting/receiving scrambled 0s |  |

#### Register Address Map

#### Table 2-8: CTRL\_MB\_IN\_EMB

| Bits | Default<br>Value | Description                                                                                                              |  |

|------|------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| 7:0  | 1                | Number of multi-blocks in an extended multi-block. Program this register with the actual value.<br>Note: 0 is Not valid. |  |

#### Register Address Map

#### Table 2-9: CTRL\_SUB\_CLASS

| Bits | Default<br>Value | Description                                    |

|------|------------------|------------------------------------------------|

| 0    | 1                | Sub Class:<br>0 = Subclass 0<br>1 = Subclass 1 |

Register Address Map

#### Table 2-10: CTRL\_META\_MODE

| Bits | Default<br>Value | Description                                       |

|------|------------------|---------------------------------------------------|

| 1:0  | 0                | Meta Mode:<br>0 = Cmd<br>1 = CRC<br>2 = FEC (TBD) |

Register Address Map

#### Table 2-11: CTRL\_LANE\_ENA

| Bits | Default<br>Value | Description                                                                                                        |  |

|------|------------------|--------------------------------------------------------------------------------------------------------------------|--|

| 7:0  | -                | Lane enable register.<br>Default is all lanes enabled.<br>Set 1 bit per lane (bit 0 = lane 0, bit 1 = lane 1 etc.) |  |

#### Register Address Map

#### Table 2-12: CTRL\_RX\_BUF\_ADV

| Bits | Default<br>Value | Description                                                   |  |

|------|------------------|---------------------------------------------------------------|--|

| 5:0  | 0                | Advance the release of the receiver buffer by N 64-bit words. |  |

Register Address Map

#### Table 2-13: CTRL\_TEST\_MODE

| Bits | Default<br>Value | Description |

|------|------------------|-------------|

| N/A  | 0                | TBD         |

Register Address Map

#### Table 2-14: CTRL\_RX\_MBLOCK\_TH

| Bits | Default<br>Value | Description                                                                                                                                                                                      |

|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0  | 0                | MB lock threshold.<br>How many correct/incorrect multi-block alignment markers are<br>required to achieve/lose multi-block lock. The actual value<br>used is 1 plus the number in this register. |

Register Address Map

#### Table 2-15: CTRL\_SYSREF

| Bits    | Default<br>Value | Description                                                                                                                                                               |  |  |

|---------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 19:16 0 |                  | SYSREF Delay:<br>Add additional delay to SYSREF alignment of local extended multi-block counter.<br>1111 = 15 core_clk cycles delay<br><br>0000 = 0 core_clk cycles delay |  |  |

|         |                  | This register is used to retard the phase of the local extended multi-block clock.                                                                                        |  |  |

Register Address Map

#### Table 2-16: **STAT\_LOCK\_DEBUG**

| Bits  | Default<br>Value | Description                                                                                                        |  |  |

|-------|------------------|--------------------------------------------------------------------------------------------------------------------|--|--|

| 7:0   | -                | Lane indicator 64b66b sync header aligned.<br>1 bit per lane.<br>Set to 1 when alignment is achieved. 0 otherwise. |  |  |

| 23:16 | -                | Lane indicator multi-block aligned.<br>1 bit per lane.<br>Set to 1 when alignment is achieved. 0 otherwise.        |  |  |

#### Register Address Map

#### Table 2-17: STAT\_STATUS

| Bits | Default<br>Value | Description                                                                                                                               |  |  |

|------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0    | -                | Interrupt pending.                                                                                                                        |  |  |

| 1    | -                | SYSREF captured.                                                                                                                          |  |  |

| 2    | -                | REF error. A sysref was detected out of phase with the local extended multi-block ck.                                                     |  |  |

| 4    | -                | 4b66b Sync Header Lock Status:<br>= Sync Header lock achieved on all lanes.<br>his bit is a logical OR of the individual lane status bits |  |  |

| 5    | -                | Multi-block Lock Status:<br>1 = Multi-block lock achieved on all lanes<br>This bit is a logical OR of the individual lane status bits.    |  |  |

| 10   | -                | Buffer overflow error.<br>1 = The receiver buffer has overflowed.                                                                         |  |  |

#### Table 2-18: CTRL\_IRQ

| Bits | Default<br>Value | Description                                              |  |  |

|------|------------------|----------------------------------------------------------|--|--|

| 0    | 0                | Global Interrupt Enable:                                 |  |  |

| 0    | 0                | Must be set for any interrupt to function.               |  |  |

| 1    | 0                | 1 = Enable Interrupt on SYSREF Received.                 |  |  |

| 2    | 0                | . = Enable Interrupt on SYSREF Error.                    |  |  |

| 4    | 0                | 1 = Enable Interrupt on Loss of 64b66b Sync Header Lock. |  |  |

| 5    | 0                | 1 = Enable Interrupt on Loss of Multi-block Lock.        |  |  |

| 6    | 0                | 1 = Enable Interrupt on Block Sync Error.                |  |  |

| 7    | 0                | 1 = Enable Interrupt on Multi-block Error.               |  |  |

| 8    | 0                | 1 = Enable Interrupt on CRC Error.                       |  |  |

| 9    | 0                | 1 = Enable Interrupt on FEC Error (TBD).                 |  |  |

| 10   | 0                | 1 = Enable Interrupt on overflow Error.                  |  |  |

#### Register Address Map

Table 2-19: STAT\_IRQ

| Bits | Default<br>Value | Description                                           |  |  |

|------|------------------|-------------------------------------------------------|--|--|

| 1    | -                | 1 = SYSREF Received Interrupt triggered.              |  |  |

| 2    | -                | 1 = SYSREF Error Interrupt triggered.                 |  |  |

| 4    | -                | = 64b66b Sync Header Lock Status Interrupt triggered. |  |  |

| 5    | -                | 1 = Multi-block Lock Status Interrupt triggered.      |  |  |

| 6    | -                | 1 = Block Sync Error detected Interrupt triggered.    |  |  |

| 7    | -                | 1 = Multi-block Error detected Interrupt triggered    |  |  |

| 8    | -                | 1 = Multi-block Error detected Interrupt triggered.   |  |  |

| 9    | -                | 1 = TBD FEC Error detected Interrupt triggered.       |  |  |

| 10   | -                | 1 = Overflow Error Interrupt triggered.               |  |  |

#### Register Address Map

#### Table 2-20: **STAT\_RX\_BUF\_LVL**

Note: This is a Per Lane Register

| Bits        | Default<br>Value | Description                                                                                                              |  |

|-------------|------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| <b>F</b> .0 |                  | Buffer fill level.                                                                                                       |  |

| 5:0         | -                | The amount of data in the receiver buffer for lane 0.<br>The value returned is the number of 64-bit words in the buffer. |  |

Register Address Map

#### Table 2-21: **STAT\_RX\_ERROR**

**Note:** This is a *Per Lane* Register

| Bits | Default<br>Value | Description                                                                               |  |

|------|------------------|-------------------------------------------------------------------------------------------|--|

| 31:0 | -                | Count of error seen on lane 0<br>The count is cumulative and is cleared on read or reset. |  |

# Chapter 3

# Designing with the Core

This chapter provides a general description of how to use the JESD204C core in your designs and should be used in conjunction with Chapter 2, Product Specification, which describes specific core interfaces.

# Clocking

The JESD204C specification [Ref 9] does not define specific serial line rates for any JESD204C link, but a valid range of line rates from 312.5 Mb/s to 32 Gb/s. The JESD204C core supports line rates from 1 Gb/s to 32 Gb/s (depending on the part and speed grade selection). In most instances, the serial line rate selection is governed by the specifications of the ADC/DAC Converter device(s) to which the core is interfaced. The required operating serial line rate directly relates to the clock rate at which the core logic operates (core clock); the serial line rate also governs the selection of the reference clock required by the transceiver(s).

## **Core Clock**

The JESD204C core operates using a 64-bit (8-byte) datapath. The core clock frequency is always the line rate divided by 66. For example, for a serial line rate of 16.5 Gb/s, the core clock frequency is 250 MHz.

The AXI4-streaming RX / TX Data and Cmd interfaces operate at this core clock frequency. TX and RX core\_clock should be used as the clock source for these interfaces.

## **Reference Clock**

The GTY serial transceivers in the JESD204\_PHY require a stable, low-jitter reference clock which has a device and speed grade-dependent range. In some circumstances, it can be advantageous to use the same clock frequency for both core clock and reference clock. However this might not always be practical. It is important to understand the limitations imposed on the reference clock and core clock, together with system-level implications such as the synchronous capture of SYSREF for Subclass 1.

## AXI4-Lite Interface Clock

The JESD204C core is configured and monitored through an AXI4-Lite processor interface. The clock for this interface is separate and independent from the core and reference clocks.

## **DRP Clock**

JESD204C system implementation requires the use of a JESD204 PHY core. The JESD204\_PHY core must be supplied with a DRP clock (see JESD204 PHY LogiCORE IP Product Guide PG198 [Ref 11]).

## Separate Transceiver Reference and Core Clocks (subclass 1)

For JESD204C, the most generic and flexible clocking scheme uses separate transceiver reference and JESD204C core clocks supplied to the FPGA. In this configuration, the reference and core clocks are physically separate and can be run at independent, but related, frequencies, without additional constraints.

The reference clock can be run at any frequency within the limitations of the transceiver for the selected line rate. The core clock always runs at the required rate (1/66th of the serial line rate).

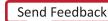

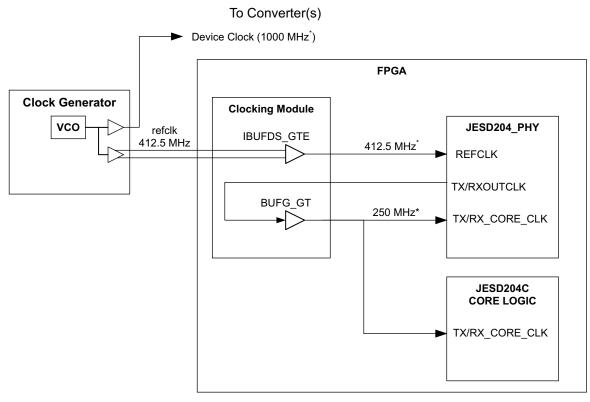

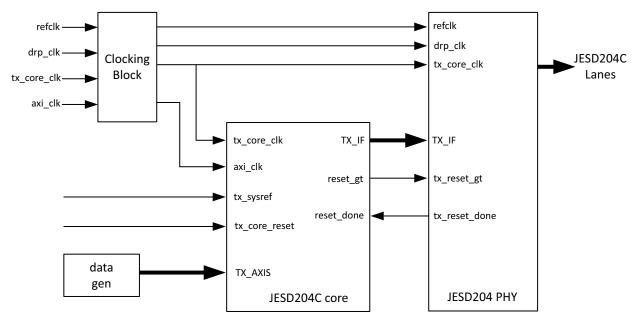

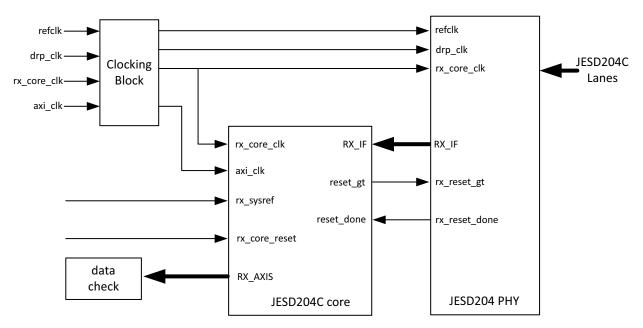

This configuration is shown in Figure 3-1.

example frequencies. Line Rate = 16.5Gb/s

Figure 3-1: Separate Transceiver Reference and Core Clocks

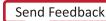

## Transceiver Reference Clock used as Core Clock (Subclass 1)

For some systems it is possible to run a single clock input which acts as both the transceiver reference clock and the JESD204C core clock. While this configuration can simplify a system design, the required clock frequency is not compatible with the CPLL input (therefore QPLL 0 or 1 must be used). In this configuration, the input transceiver reference clock must always be the required rate (1/66th of the serial line rate).

*Note:* When using this clocking scheme, the signal GT\_POWERGOOD output from the JESD204\_PHY must be connected to the CE pin on the BUFG\_GT.

This configuration is shown in Figure 3-2.

\* Example Frequencies. Line Rate = 16.5 Gb/s

*Figure 3-2:* Transceiver Reference Clock used as Core Clock (Subclass 1)

## Transceiver Output Clock used as Core Clock (Subclass 0)

For Subclass 0 only operation, the timing limitations imposed to support deterministic latency are removed, and a simplified clocking arrangement can be used which requires only a reference clock input. In this case the transceiver PLL is used to generate the core clock signal. In this configuration any clock frequency that is suitable to use as the transceiver reference cock is acceptable.

This configuration is shown in Figure 3-3.

*Note:* This configuration is not suitable for subclass 1 operation because the output phase of the transceiver PLL is unknown and therefore this clock cannot be used to reliably sample SYSREF.

\* example frequencies. Line Rate = 16.5Gb/s

*Figure 3-3:* Transceiver Output Clock used as Core Clock (Subclass 0)

## **Clocking Considerations**

- Always refer to the device data sheet for the chosen part and speed grade to confirm which PLLs are available for a required line rate PLL selection for a particular rate may not be arbitrary.

- The CPLL supports a maximum line rate in any device of 12.5 Gb/s.

- If the CPLL is required, the transceiver reference clock cannot be used as the core clk because the acceptable reference clock input frequencies to the CPLL do not cover the required Line Rate/66 ratio.

- For Line rates above 16.375G, ensure only port MGTREFCLK0 is used to drive QPLL0, and MGTREFCLK1 to drive QPLL1.

## Resets

The reset inputs and outputs on the JESD204C core are as shown in Table 3-1.

| Reset            | Description                                                                                                                                                                                                                                                          |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| tx/rx_core_reset | This reset input is asynchronous and active high.<br>This reset input will reset the JESD204C core logic but does not reset the AXI4-Lite<br>register interface - so all programmed values will be maintained.                                                       |  |  |  |  |

| s_axi_aresetn    | This reset input must be synchronized with the AXI4-Lite interface clock.<br>This reset input will reset the AXI4-Lite register interface.                                                                                                                           |  |  |  |  |

| tx/rx_reset_gt   | This reset output must be connected to the JESD204_PHY core. This signal is used to initiate a JESD204_PHY GT reset sequence.                                                                                                                                        |  |  |  |  |

| tx/rx_reset_done | This input must be connected to the JESD204_PHY core.<br>This signal is used to hold the JESD204C core in reset until completion of the<br>JESD204_PHY GT reset sequence.<br><b>Note</b> : A low input on this port will force the JESD204C core into a reset state. |  |  |  |  |

| tx/rx_aresetn    | This reset output is synchronous to tx/rx_core_clk.<br>This output is an AXI4-Streaming interface reset signal to be used with the<br>AXI4-streaming RX / TX Data and Cmd interfaces.                                                                                |  |  |  |  |

Table 3-1: JESD204C Resets

# **Design Flow Steps**

This chapter describes customizing and generating the JESD204C core, constraining the core, and the simulation, synthesis and implementation steps that are specific to this IP core. More detailed information about the standard Vivado® design flows and the Vivado IP integrator can be found in the following Vivado Design Suite user guides:

- Vivado Design Suite User Guide: Designing IP Subsystems using IP Integrator (UG994) [Ref 1]

- Vivado Design Suite User Guide: Designing with IP (UG896) [Ref 2]

- Vivado Design Suite User Guide: Getting Started (UG910) [Ref 3]

- Vivado Design Suite User Guide: Logic Simulation (UG900) [Ref 4]

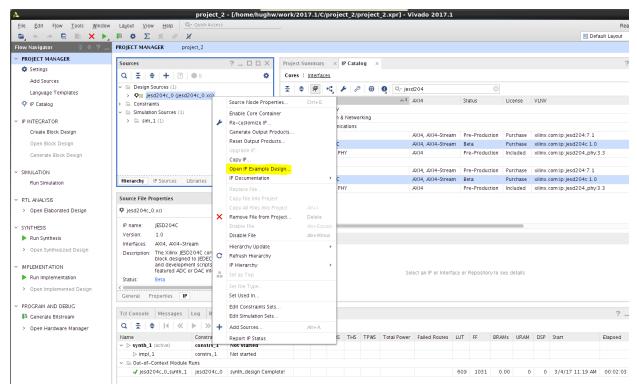

# **Customizing and Generating the Core**

This section includes information on using Xilinx tools to customize and generate the core in the Vivado Design Suite.

If you are customizing and generating the core in the IP integrator, see the *Vivado Design Suite User Guide: Designing IP Subsystems using IP Integrator* (UG994) [Ref 1] for detailed information. IP integrator might auto-compute certain configuration values when validating or generating the design. To check whether the values do change, see the description of the parameter in this chapter. To view the parameter value you can run the validate\_bd\_design command in the Tcl console.

You can customize the IP for use in your design by specifying values for the various parameters associated with the IP core using the following steps:

- 1. Select the IP from the Vivado IP catalog.

- 2. Double-click the selected IP or select the **Customize IP** command from the toolbar or right-click menu.

For details, see the Vivado Design Suite User Guide: Designing with IP (UG896) [Ref 2] and the Vivado Design Suite User Guide: Getting Started (UG910) [Ref 3].

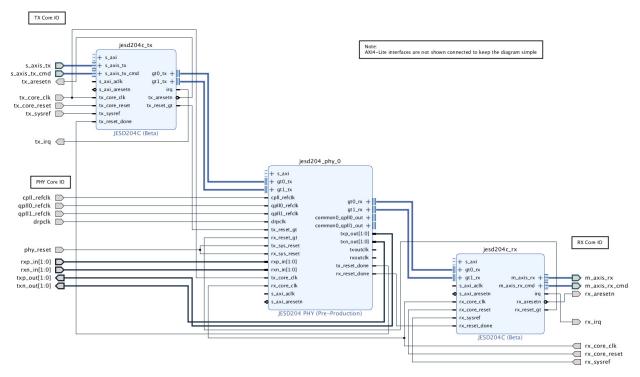

*Note:* Figures in this chapter are illustrations of the JESD204C GUI in the Vivado Integrated Design Environment (IDE). This layout might vary from the current version.

## **Configuration Tab**

| <b>.</b>                                                                                                                                                                                            | Re-                                                | customize IP ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JESD204C (1.0)                                                                                                                                                                                      |                                                    | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 💕 Documentation 🛛 IP Location                                                                                                                                                                       |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Show disabled ports                                                                                                                                                                                 | Component Name                                     | jesd204c_tx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                     | Configuration                                      | JESD204 PHY Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <pre>+ s_axis_tx<br/>+ s_axis_tx_crmd gt0_tx +   <br/>s_axi_aclk gt1_tx +   <br/>s_axi_aresetn irq<br/>tx_core_clk tx_aresetn +<br/>tx_core_reset tx_reset_gt<br/>tx_systef<br/>tx_reset_done</pre> | Number of Lane<br>Lanes per Lir<br>Clocking Option | Transmit       Image: Signal and the second sec |

| Bought IP license available                                                                                                                                                                         |                                                    | OK Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

*Figure 4-1:* **Configuration Tab**

- **Component Name** The component name is used as the base name of the output files generated for the core. Names must begin with a letter and must be composed from these characters: a through z, 0 through 9 and "\_" (underscore).

- **Transmit or Receive** The core can be configured as a transmitter, for connection to DAC devices, or receiver, for connection to ADC devices.

- **Number of Lanes** The core supports 1 to 8 lanes. For interfaces requiring more than 8 lanes, multiple core must be used.

- **AXI4-Lite Clock Frequency** The frequency of the clock connected to the AXI4-Lite Management Interface.

## **JESD204 PHY Configuration Tab**

| -                                                                                                                                                                                            | Re-customize IP                                                                                                                                                                                                                                                                                            | >                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| JESD204C (1.0)                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                            | 4                                 |

| 🖗 Documentation 🛛 🔚 IP Location                                                                                                                                                              |                                                                                                                                                                                                                                                                                                            |                                   |

| Show disabled ports                                                                                                                                                                          | Component Name jesd204c_tx                                                                                                                                                                                                                                                                                 |                                   |

|                                                                                                                                                                                              | Configuration         JESD204 PHY Configuration           The JESD204C does not include a JESD204 PHY. A JESD204 PHY can be generated from the IP catalogue                                                                                                                                                | e and wired up to the JESD204C IP |

| + s_axi<br>+ s_axis_tx<br>+ s_axis_tx_crnd gt0_tx +   <br>s_axi_aclk gt1_tx +   <br>s_axi_aresetn irq<br>tx_core_clk tx_aresetn •<br>tx_core_reset tx_reset_gt<br>tx_sysref<br>tx_reset_done | Transceiver Parameters         Transceiver Type         GTYE4         Line Rate (Gbps)         B.00         Reference Clock (MHz)         200         PLL Type         CPLL         DRP Clock Frequency (MHz)         121.2121212         Valid Range of values for DRP Clock Frequency: [10.0121.2121212] |                                   |

• **Transceiver Parameters** – For any selected Line Rate and PLL Type, valid Reference Clock frequencies can be selected from a drop-down list. A free-running DRP clock must be supplied, and the frequency (within the displayed valid range) must be entered in the DRP Clock Frequency box.

## **User Parameters**

Table 4-1 shows the relationship between the GUI fields in the Vivado IDE and the User Parameters (which can be viewed in the Tcl console).

Table 4-1: Vivado IDE Parameter to User Parameter Relationship

| Vivado IDE Parameter/Value <sup>(1)</sup> | User Parameter/Value <sup>(1)</sup> | Default Value  |  |

|-------------------------------------------|-------------------------------------|----------------|--|

| Transmit or Receive                       | C_NODE_IS_TRANSMIT                  | 0 (= Transmit) |  |

| Lanes per Link                            | C_LANES                             | 2              |  |

| AXI4-Lite Clock Frequency                 | AXICLK_FREQ                         | 100.00         |  |

| Transceiver Parameters                    |                                     |                |  |

| Line Rate <sup>(2)</sup>                  | GT_Line_Rate                        | 8.0            |  |

| Ref Clock Frequency <sup>(2)</sup>        | GT_REFCLK_FREQ                      | 200.0          |  |

| DRP Clock Frequency                       | DRPCLK_FREQ                         | 200.0          |  |

| PLL Type                                  | C_PLL_SELECTION                     | 0 (=CPLL)      |  |

Notes:

1. Parameter values are listed in the table where the Vivado IDE parameter value differs from the user parameter value. Such values are shown in this table as indented below the associated parameter.

2. Varies depending on device.

## **Output Generation**

For details, see the Vivado Design Suite User Guide: Designing with IP (UG896) [Ref 2].

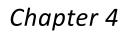

## **Transceiver Sharing**

The JESD204\_PHY core (see *JESD204 PHY LogiCORE IP Product Guide* (PG198) [Ref 11]) provides a simple way to share transceivers between JESD204(B or C) cores. Any number of JESD204\_PHY cores can be connected to any number of JESD204 cores to cater for any combination of ADCs and DACs using different line rates and lane counts.

An example of a two lane TX and two lane RX sharing a JESD204 PHY is shown in Figure 4-3. The transmitter and the receiver are configured for different line rates. Separate refclk inputs are provided for each PLL and separate core clocks are provided for TX and RX to support subclass 1 (see Figure 3-1).

Figure 4-3: Transceiver Sharing

# **Configuring the JESD204 PHY in IPI**

The RTL example design that can be generated for the JESD204C core in Vivado (see Chapter 5) delivers a JESD204 PHY core with the settings used in the JESD204C GUI. When configuring a JESD204 PHY core for use in IPI with a JESD204C core, the following values must be set:

- The transceiver type must be set to GTYE3 or GTYE4.

- The data path width must be set to 64 bits.

As highlighted in Figure 4-4.