# UltraScale + Devices Integrated 100G Ethernet Subsystem v1.0

## **Product Guide**

**Vivado Design Suite**

PG203 April 6, 2016

# **Table of Contents**

| Chapter 1: Overview                    |

|----------------------------------------|

| Feature Summary 5                      |

| Licensing and Ordering Information 7   |

| Chapter 2: Product Specification       |

| Typical Operation                      |

| Statistics Gathering                   |

| Testability Functions                  |

| Pause Operation                        |

| Standards                              |

| Performance and Resource Utilization   |

| Port Descriptions                      |

| Attribute Descriptions                 |

| Chapter 3: Designing with the Core     |

| Clocking                               |

| Resets                                 |

| Protocol Description                   |

| PCS 51                                 |

| Ethernet MAC 55                        |

| 1588v2 Timestamping                    |

| Transceiver Selection Rules 80         |

| Dynamic Reconfiguration Port           |

| Chapter 4: Design Flow Steps           |

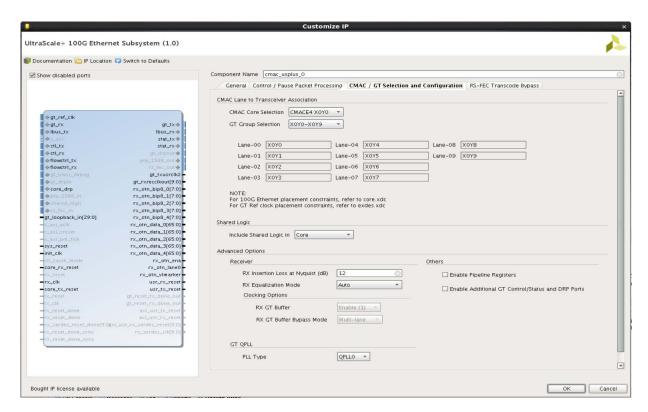

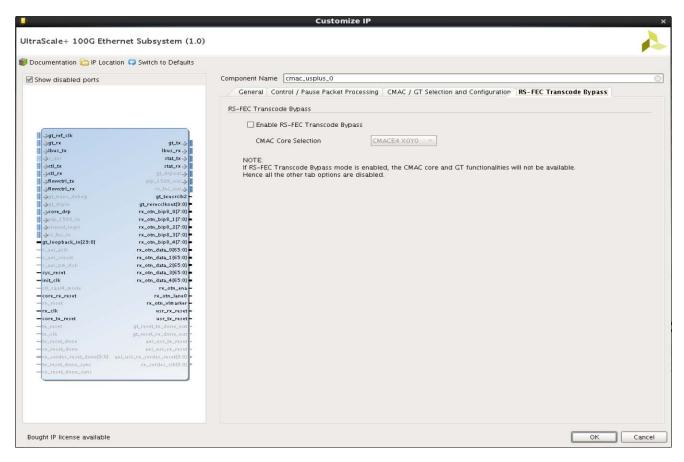

| Customizing and Generating the Core 90 |

| Constraining the Core                  |

| Simulation                             |

| Synthesis and Implementation           |

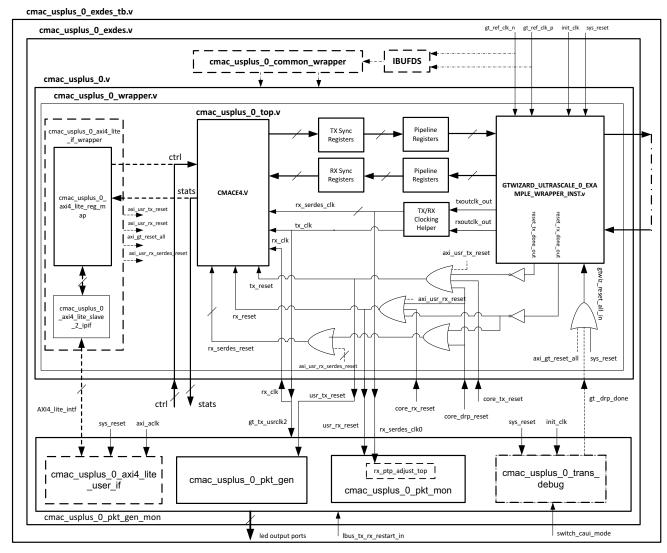

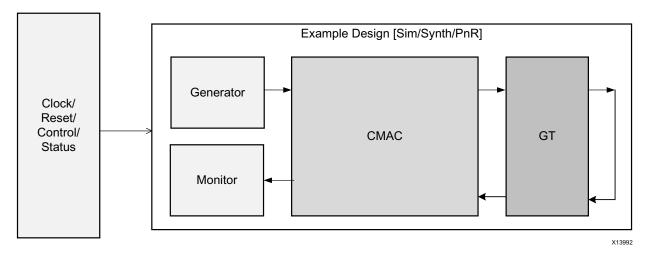

| Chapter 5: Example Design              |

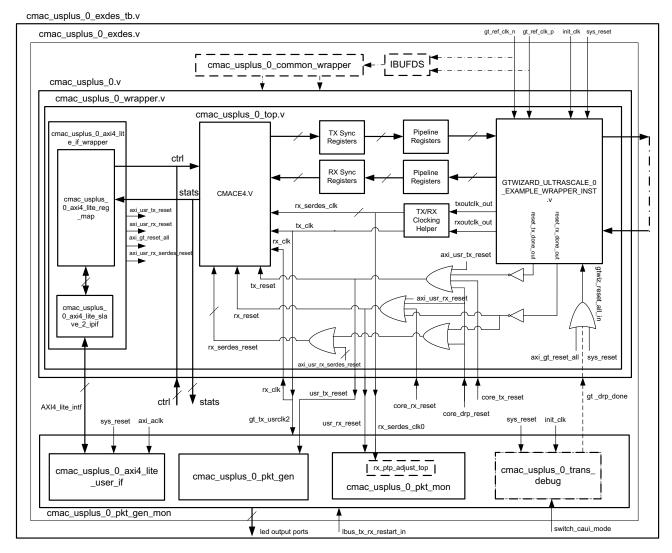

| Overview                               |

| User Interface 107                     |

| CORE XCI Top Level Port List                                       | 109 |

|--------------------------------------------------------------------|-----|

| Modes of Operation                                                 | 152 |

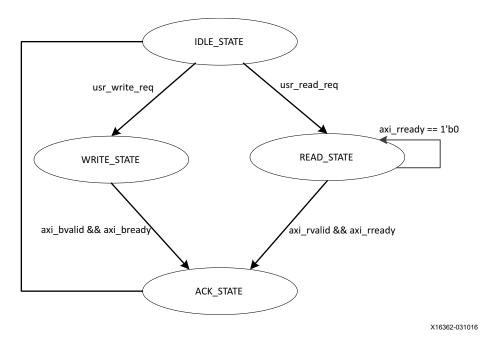

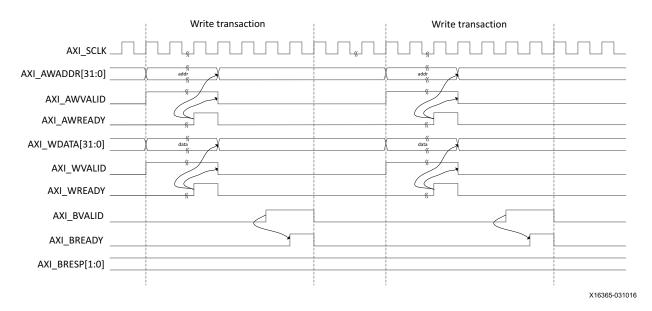

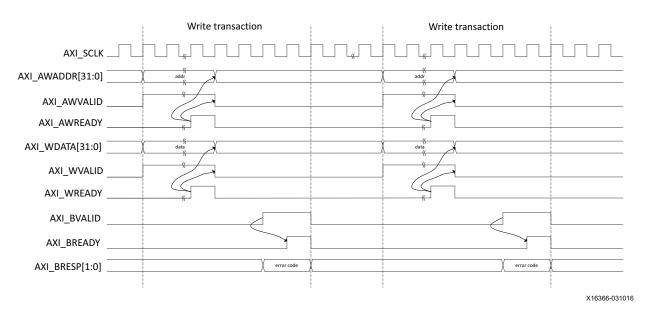

| Transaction Flow                                                   | 156 |

| CORE DRP Operation                                                 | 163 |

| AXI4-Lite Interface Implementation                                 | 164 |

| RS-FEC Transcode Bypass                                            | 187 |

| Use Case for Different Modes                                       | 188 |

| Simulating the Example Design                                      | 195 |

| Synthesizing and Implementing the Example Design                   | 196 |

| Appendix A: Debugging                                              |     |

| Finding Help on Xilinx.com                                         |     |

| Debug Tools                                                        | 198 |

| Simulation Debug                                                   | 199 |

| Hardware Debug                                                     | 200 |

| Interface Debug                                                    | 202 |

| Protocol Debug                                                     | 203 |

| Appendix B: UltraScale+ Device OTN Interface                       |     |

| Overview                                                           | 205 |

| Implementation                                                     | 206 |

| Appendix C: UltraScale+ Device RS-FEC for Integrated 100G Ethernet |     |

| Operating Modes                                                    | 209 |

| Ports                                                              | 210 |

| Clocks and Resets                                                  | 212 |

| RS-FEC Sub-Modes                                                   | 213 |

| Using the RS-FEC Engine                                            | 216 |

| Appendix D: Additional Resources and Legal Notices                 |     |

|                                                                    |     |

| Xilinx Resources                                                   | 220 |

| Xilinx Resources       References                                  |     |

|                                                                    | 220 |

## Introduction

The Xilinx® UltraScale+™ Devices Integrated 100G Ethernet IP subsystem provides a high performance, low latency 100 Gb/s Ethernet port that allows for a wide range of user customization and statistics gathering. The dedicated block provides both the 100G Ethernet MAC, and RS-FEC logic with support for *IEEE 1588-2008* [Ref 1] hardware timestamping.

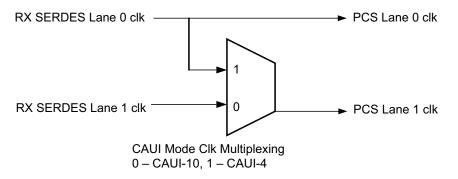

The 100G Ethernet IP core provides three configurations: (CAUI-10) 10x10.3125G, (CAUI-4) 4x25.78125G, and switchable CAUI-4 and CAUI-10 mode. The 100G Ethernet IP core is designed to the *IEEE std 802.3-2012* [Ref 2] specification.

#### **Features**

- Supports CAUI-10, CAUI-4, and switchable CAUI-4 and CAUI-10 modes

- 512-bit segmented local bus (LBUS) user interface at ~322 MHz

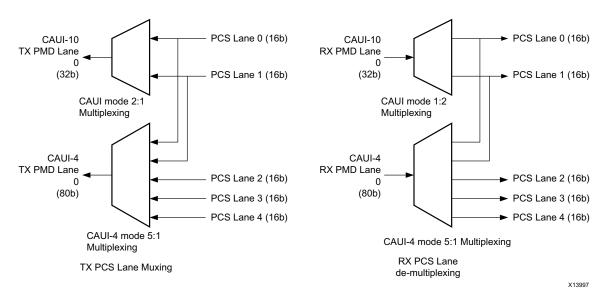

- 32-bit interface to the serial transceiver for CAUI-10 lanes and 80-bit interface to the serial transceiver for CAUI-4 lanes

- IEEE 1588-2008 [Ref 1] one-step and two-step hardware timestamping at ingress and egress at full 80-bits

- Pause frame processing including priority based flow control per IEEE std 802.3-2012 Annex 31 [Ref 2]

- IEEE Dynamic and static deskew support

- Optional built-in 802.3bj-2014 Clause 91 RS-FEC block in CAUI-4 mode

- Receive side OTN interface

See Feature Summary in Chapter 1 for a list of more features.

| LogiCORE IP Facts Table                     |                                                                             |  |  |  |

|---------------------------------------------|-----------------------------------------------------------------------------|--|--|--|

| Core Specifics                              |                                                                             |  |  |  |

| Supported<br>Device Family <sup>(1)</sup>   | UltraScale+                                                                 |  |  |  |

| Supported User<br>Interfaces                | Segmented LBUS                                                              |  |  |  |

| Resources                                   | Performance and Resource Utilization web page                               |  |  |  |

|                                             | Provided with Core                                                          |  |  |  |

| Design Files                                | Verilog                                                                     |  |  |  |

| Example Design                              | Verilog                                                                     |  |  |  |

| Test Bench                                  | Verilog                                                                     |  |  |  |

| Constraints File                            | Xilinx Design Constraints (XDC)                                             |  |  |  |

| Simulation<br>Model                         | Verilog                                                                     |  |  |  |

| Supported<br>S/W Driver                     | N/A                                                                         |  |  |  |

|                                             | Tested Design Flows <sup>(2)</sup>                                          |  |  |  |

| Design Entry                                | Vivado® Design Suite                                                        |  |  |  |

| Simulation                                  | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |  |  |

| Synthesis                                   | Vivado synthesis                                                            |  |  |  |

|                                             | Support                                                                     |  |  |  |

| Provided by Xilinx @ www.xilinx.com/support |                                                                             |  |  |  |

#### **Notes:**

- For a complete list of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

## Overview

This product guide describes the function and operation of the Xilinx® UltraScale+™ Devices Integrated 100G Ethernet subsystem, including how to design, customize, and implement it.

The core is designed to the *IEEE std 802.3-2012* [Ref 2] specification with an option for *IEEE 1588-2008* [Ref 1] hardware timestamping. The core instantiates the UltraScale+ devices integrated block for 100G Ethernet. This core simplifies the design process and reduces time to market.

Although the core is a fully-verified solution, implementing a complete design varies depending on the configuration and functionality of the application. See Chapter 2, Product Specification for details about the core.

**RECOMMENDED:** For best results, previous experience building high performance, pipelined FPGA designs using Xilinx implementation design tools and constraint files is recommended.

**IMPORTANT:** CAUI-4 and switchable CAUI-10/CAUI-4 require GTY transceivers that are available only in Virtex® UltraScale+ devices.

## **Feature Summary**

Following is summary of the features

- IEEE 1588-2008 [Ref 1] one-step and two-step hardware timestamping with transparent clock support

- 20 PCS lanes (PCSLs) for the 100G Ethernet IP core

- GTY or GTH transceivers used for UltraScale+ devices

- PCS Lane marker framing and de-framing including reordering of each PCS lane

- · Link status and alignment monitoring reporting

- 64B/66B decoding and encoding as defined in IEEE std 802.3-2012 Clause 82 [Ref 2]

- Scrambling and descrambling using  $x^{58} + x^{39} + 1$  polynomial

- Inter-Packet gap (IPG) insertion and deletion as required by IEEE std 802.3-2012 Clause 82 [Ref 2]

- Optional frame check sequence (FCS) calculation and addition in the transmit direction

- FCS checking and optional FCS removal in the receive direction

- Support for 802.3x and priority-based pause operation

- DRP interface for dynamic reconfiguration of the core

- Detailed statistics gathering

- Total bytes

- Total packets

- Good bytes

- Good packets

- Unicast packets

- Multicast packets

- Broadcast packets

- Pause packets

- Virtual local area network (VLAN) tagged packets

- 64B/66B code violations

- Bad preambles

- Bad FCS

- Packet histogram for packets sized between:

- 64

- 65-127

- 128-255

- 256-511

- 512-1023

- 1024-1518

- 1519-1522

- 1523-1548

- 1549-2047

- 2048-4095

- 4096-8191

- 8192-9215

## **Licensing and Ordering Information**

This Xilinx LogiCORE™ IP module is provided at no additional cost with the Xilinx Vivado Design Suite under the terms of the Xilinx End User License.

Information about this and other Xilinx LogiCORE™ IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

For more information and to generate a no charge license key, visit the <u>UltraScale+</u> <u>Integrated 100G Ethernet Subsystem</u> product web page.

For more information on generating a hardware evaluation license and ordering for the IEEE 802.3 RS-FEC, visit the IEEE 802.3bj Reed-Solomon Forward Error Correction page.

## **Product Specification**

Table 2-1 defines the integrated CMAC block for the 100 Gb/s Ethernet solution.

Table 2-1: Integrated CMAC Block for the 100 Gb/s Ethernet Solution

| Protocol                                    | Lane Width                 | Line Rate                                      | SerDes             | SerDes Width                |

|---------------------------------------------|----------------------------|------------------------------------------------|--------------------|-----------------------------|

| CAUI-10                                     | x10                        | 10.3125 Gb/s                                   | GTH<br>GTY         | 32b                         |

| CAUI-4                                      | x4                         | 25.78125 Gb/s <sup>(2)</sup>                   | GTY <sup>(1)</sup> | 80b                         |

| Runtime<br>Switchable<br>CAUI-4/<br>CAUI-10 | CAUI-10: x10<br>CAUI-4: x4 | CAUI-10: 10.3125 Gb/s<br>CAUI-4: 25.78125 Gb/s | GTY <sup>(1)</sup> | CAUI-10: 32b<br>CAUI-4: 80b |

#### Notes:

- CAUI-4 and switchable CAUI-10/CAUI-4 require GTY transceivers that are available only in Virtex® UltraScale+™ devices.

- 2. The line rate of 25.78125 Gb/s is available on select devices, Virtex UltraScale+ devices in typical speed grades.

The core instantiates the CMAC block along with the necessary GTH or GTY transceivers. The core provides an example of how the two blocks are connected together, along with the reset and clocking for those blocks.

The integrated block is designed to IEEE std 802.3-2012 [Ref 2].

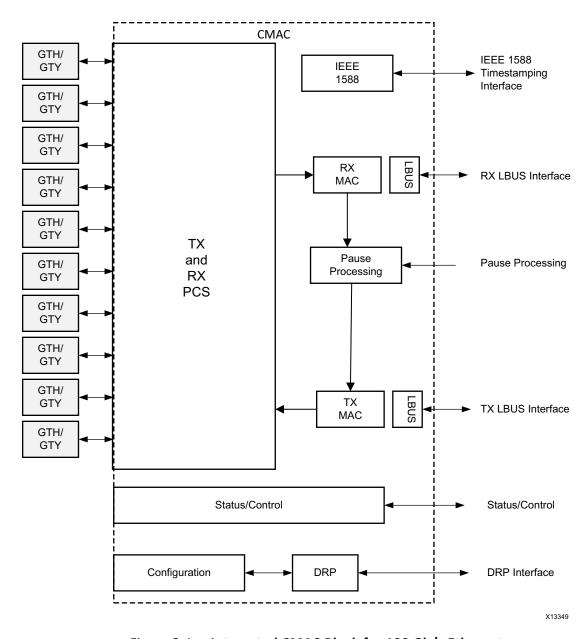

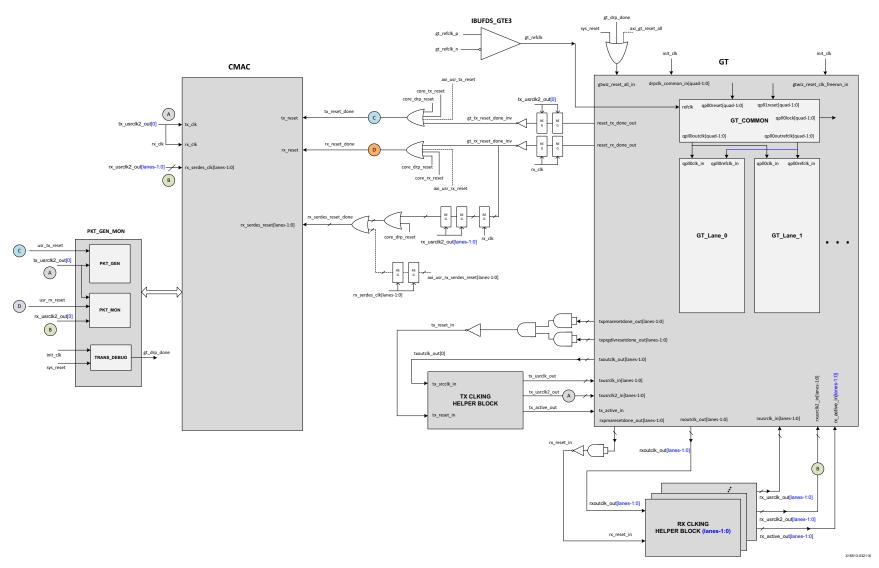

Figure 2-1 illustrates the following interfaces to the integrated CMAC block.

- Serial transceiver interface

- User-side transmit and receive LBUS interface

- Pause processing

- IEEE 1588-2008 [Ref 1] timestamping interface

- Status/Control interface

- DRP interface used for configuration

Figure 2-1: Integrated CMAC Block for 100 Gb/s Ethernet

## **Typical Operation**

The 100G Ethernet IP core handles all protocol related functions to communicate to the other devices PCS and Ethernet MAC interface. This includes handshaking, synchronizing and error checking. You provide packet data through the Local Bus (LBUS) TX interface and receive packet data from the LBUS RX interface. The LBUS is designed to match commonly used packet bus protocols made common by the SPI4.2 and Interlaken protocols. A detailed description is given in User Side LBUS Interface in Chapter 3.

The core is designed to be flexible and used in many different applications. The RX path does not perform any buffering other than the pipelining required to perform the required operations. Received data is passed directly to the user interface in a cut-through manner, allowing you the flexibility to implement any required buffering scheme. Also, the core TX path consists of a single pipeline with minimal buffering to provide reliable cut-through operation.

## **Statistics Gathering**

The 100G Ethernet IP core provides a flexible and user-friendly mechanism for gathering statistics. For all the supported statistics, the core has an output signal (or bus if needed) that indicates an increment value for the statistic in a given clock cycle. This allows the increment value to build the required counter mechanism. This mechanism allows you to select which statistics are required in the system without having the cost overhead of a full set of counters. Additionally, and more importantly, you can implement any counter and statistics gathering mechanism required by the system. For example, you can build 32-bit or 64-bit counters as needed, or implement clear-on-read or saturated counters, as required.

For the purposes of TX statistics, good packets are defined as packets without FCS or other errors; bad packets are defined as packets with FCS or any other error.

For the purposes of RX statistics, good packets are defined as packets without FCS or other errors including length error. Bad packets are defined as packets with FCS or any other error. The length field error includes length field error, oversize and undersize packets.

## **Testability Functions**

The 100G Ethernet example design implements the test pattern generation and checking as defined in Clause 82.2.10 (Test-pattern generators) and Clause 82.2.17 (Test-pattern checker). See the IEEE 802.3 documents for details.

## **Pause Operation**

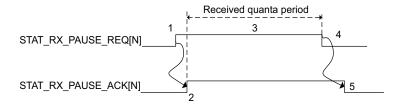

The 100G Ethernet IP core is capable of handling 802.3x and priority-based pause operation. The RX path parses pause packets and presents the extracted quanta on the status interface; the TX path can accept pause packet requests from the control interface and will inject the requested packets into the data stream. Both global pause packets and priority-based pause packets are handled. Details are described in Pause Processing Interface in Chapter 3.

**Note:** "802.3x" and "global pause" are used interchangeably throughout the document.

#### **Standards**

The 100G Ethernet IP core is designed to be compliant with the *IEEE std 802.3-2012* [Ref 2] specification. The timestamping feature is designed to be compliant with *IEEE 1588-2008* [Ref 1].

### **Performance and Resource Utilization**

For full details about performance and resource utilization, visit <u>Performance and Resource Utilization</u>.

## **Port Descriptions**

Table 2-2 provides a detailed description of the 100G Ethernet IP core ports.

**IMPORTANT:** CAUI-4 and switchable CAUI-10/CAUI-4 require GTY transceivers that are available only in Virtex UltraScale+ devices.

Table 2-2: Transceiver I/O

| Name                      | Direction | Domain           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------|-----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ctl_tx_ipg_value[3:0]     | Input     |                  | This signal may be optionally present. The ctl_tx_ipg_value defines the target average minimum Inter Packet Gap (IPG, in bytes) inserted between LBUS packets. Valid values are 8 to 12. The ctl_tx_ipg_value can also be programmed to a value in the 0 to 7 range, but in that case, it is interpreted as meaning <i>minimal IPG</i> , so only Terminate code word IPG is inserted; no Idles are ever added in that case - and that produces an average IPG of around 4 bytes when random-size packets are transmitted.                                        |

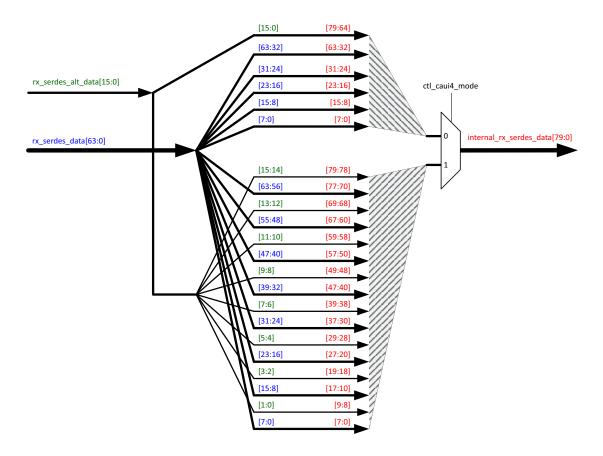

| RX_SERDES_ALT_DATA0[15:0] | Input     | RX_SERDES_CLK[0] | 16-bit group of the Receive data bus from SerDes0. There are 10 RX_SERDES_DATA buses; one bus for each SerDes lane, and each bus has either 80 or 32 bits depending on whether operation is in CAUI-4 or CAUI-10 mode respectively. The first four SerDes lanes can operate at 80 bits or 32 bits, and the remaining six lanes operate at 32 bits. The 32 LSBs of the first four lanes are used in CAUI-10 mode. The mapping of the 80 bits, comprised of a 16-bit group and a 64-bit group, is not obvious. See PCS Lane Multiplexing in Chapter 3 for details. |

| RX_SERDES_ALT_DATA1[15:0] | Input     | RX_SERDES_CLK[1] | 16-bit group of the Receive data bus from SerDes1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RX_SERDES_ALT_DATA2[15:0] | Input     | RX_SERDES_CLK[2] | 16-bit group of the Receive data bus from SerDes2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RX_SERDES_ALT_DATA3[15:0] | Input     | RX_SERDES_CLK[3] | 16-bit group of the Receive data bus from SerDes3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RX_SERDES_DATA0[63:0]     | Input     | RX_SERDES_CLK[0] | 64-bit group of the Receive data bus from SerDes0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RX_SERDES_DATA1[63:0]     | Input     | RX_SERDES_CLK[1] | 64-bit group of the Receive data bus from SerDes1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RX_SERDES_DATA2[63:0]     | Input     | RX_SERDES_CLK[2] | 64-bit group of the Receive data bus from SerDes2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RX_SERDES_DATA3[63:0]     | Input     | RX_SERDES_CLK[3] | 64-bit group of the Receive data bus from SerDes3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RX_SERDES_DATA4[31:0]     | Input     | RX_SERDES_CLK[4] | Data bus from SerDes4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RX_SERDES_DATA5[31:0]     | Input     | RX_SERDES_CLK[5] | Data bus from SerDes5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Table 2-2: Transceiver I/O (Cont'd)

| Name                      | Direction | Domain           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------|-----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX_SERDES_DATA6[31:0]     | Input     | RX_SERDES_CLK[6] | Data bus from SerDes6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RX_SERDES_DATA7[31:0]     | Input     | RX_SERDES_CLK[7] | Data bus from SerDes7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RX_SERDES_DATA8[31:0]     | Input     | RX_SERDES_CLK[8] | Data bus from SerDes8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RX_SERDES_DATA9[31:0]     | Input     | RX_SERDES_CLK[9] | Data bus from SerDes9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

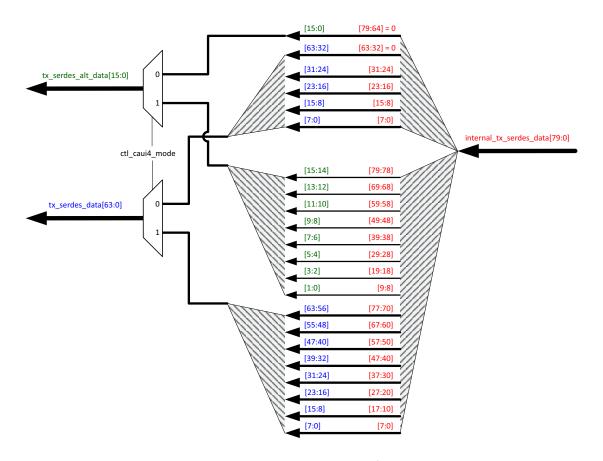

| TX_SERDES_ALT_DATA0[15:0] | Output    | TX_SERDES_CLK[0] | 16-bit group of the Transmit data bus to SerDes0. There are 10 TX_SERDES_DATA buses; one bus for each SerDes lane, and each bus has either 80 or 32 bits depending on whether operation is in CAUI-4 or CAUI-10 mode respectively. The first four SerDes lanes can operate at 80 bits or 32 bits, and the remaining six lanes operate at 32 bits. The 32 LSBs of the first four lanes are used in CAUI-10 mode. The mapping of the 80 bits, comprised of a 16-bit group and a 64-bit group, is not obvious. See PCS Lane Multiplexing in Chapter 3 for details. |

| TX_SERDES_ALT_DATA1[15:0] | Output    | TX_SERDES_CLK[1] | 16-bit group of the Transmit data bus to SerDes1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TX_SERDES_ALT_DATA2[15:0] | Output    | TX_SERDES_CLK[2] | 16-bit group of the Transmit data bus to SerDes2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TX_SERDES_ALT_DATA3[15:0] | Output    | TX_SERDES_CLK[3] | 16-bit group of the Transmit data bus to SerDes3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TX_SERDES_DATA0[63:0]     | Output    | TX_SERDES_CLK[0] | 64-bit group of the Transmit data bus to SerDes0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TX_SERDES_DATA1[63:0]     | Output    | TX_SERDES_CLK[1] | 64-bit group of the Transmit data bus to SerDes1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TX_SERDES_DATA2[63:0]     | Output    | TX_SERDES_CLK[2] | 64-bit group of the Transmit data bus to SerDes2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TX_SERDES_DATA3[63:0]     | Output    | TX_SERDES_CLK[3] | 64-bit group of the Transmit data bus to SerDes3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TX_SERDES_DATA4[31:0]     | Output    | TX_SERDES_CLK[4] | Data bus to SerDes4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TX_SERDES_DATA5[31:0]     | Output    | TX_SERDES_CLK[5] | Data bus to SerDes5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TX_SERDES_DATA6[31:0]     | Output    | TX_SERDES_CLK[6] | Data bus to SerDes6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TX_SERDES_DATA7[31:0]     | Output    | TX_SERDES_CLK[7] | Data bus to SerDes7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TX_SERDES_DATA8[31:0]     | Output    | TX_SERDES_CLK[8] | Data bus to SerDes8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TX_SERDES_DATA9[31:0]     | Output    | TX_SERDES_CLK[9] | Data bus to SerDes9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Table 2-2: Transceiver I/O (Cont'd)

| Name                 | Direction | Domain             | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|-----------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX_SERDES_CLK[9:0]   | Input     |                    | Recovered clock of each SerDes lane. The RX_SERDES_DATA bus for each lane is synchronized to the positive edge of the corresponding bit of this bus.                                                                                                                                                                                                                                                            |

| RX_SERDES_RESET[9:0] | Input     | RX_SERDES_CLK[9:0] | Reset for each RX SerDes lane. The recovered clock for each SerDes lane has associated with it an active-High reset. This signal should be 1 whenever the associated recovered clock is not operating at the correct frequency. Generally this signal is derived from a PLL lock signal. This reset signal should be held in reset until the GT is finished its initialization and the RX_SERDES_CLK is stable. |

Table 2-3: LBUS Interface – Clock/Reset Signals

| Name     | Direction | Domain           | Description                                                                                                                                                                                                                                                     |

|----------|-----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_CLK   | Input     |                  | TX clock. All TX signals between the 100G Ethernet IP core and the user-side logic are synchronized to the positive edge of this signal. The clock frequency is equal to the line rate divided by the SerDes width. This frequency is nominally 322.265625 MHz. |

| RX_CLK   | Input     |                  | RX clock. All RX signals between the 100G Ethernet IP core and the user-side logic are synchronized to the positive edge of this signal. The frequency of this clock should be the same as the TX clock.                                                        |

| RX_RESET | Input     | async (5 ns min) | Reset for the RX circuits. This signal is active-High (1 = reset) and must be held High until RX_CLK is stable. The 100G Ethernet IP core handles synchronizing the RX_RESET input to the appropriate clock domains within the 100G Ethernet IP core.           |

| TX_RESET | Input     | async (5 ns min) | Reset for the TX circuits. This signal is active-High (1 = reset) and must be held High until TX_CLK is stable. The 100G Ethernet IP core handles synchronizing the TX_RESET input to the appropriate clock domains within the 100G Ethernet IP core.           |

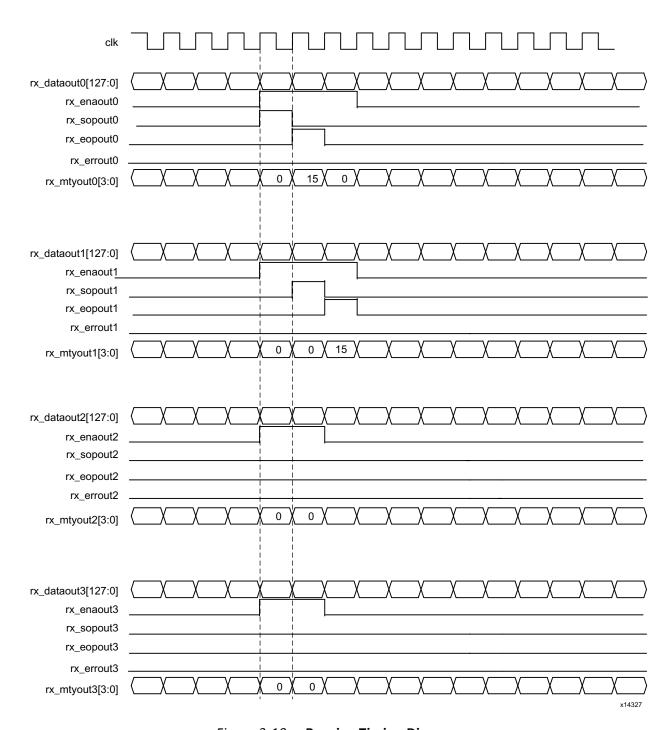

Table 2-4: LBUS Interface – RX Path Signals

| Name               | Direction | Domain | Description                                                                                                                                                                                                                                                                                                                         |

|--------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX_DATAOUT0[127:0] | Output    | RX_CLK | Receive segmented LBUS Data for segment 0. The value of this bus is only valid in cycles that RX_ENAOUT0 is sampled as 1.                                                                                                                                                                                                           |

| RX_DATAOUT1[127:0] | Output    | RX_CLK | Receive segmented LBUS Data for segment1.                                                                                                                                                                                                                                                                                           |

| RX_DATAOUT2[127:0] | Output    | RX_CLK | Receive segmented LBUS Data for segment2.                                                                                                                                                                                                                                                                                           |

| RX_DATAOUT3[127:0] | Output    | RX_CLK | Receive segmented LBUS Data for segment3.                                                                                                                                                                                                                                                                                           |

| RX_ENAOUT0         | Output    | RX_CLK | Receive LBUS Enable for segment0. This signal qualifies the other signals of the RX segmented LBUS Interface. Signals of the RX LBUS Interface are only valid in cycles in which RX_ENAOUT is sampled as a 1.                                                                                                                       |

| RX_ENAOUT1         | Output    | RX_CLK | Receive LBUS Enable for segment1.                                                                                                                                                                                                                                                                                                   |

| RX_ENAOUT2         | Output    | RX_CLK | Receive LBUS Enable for segment2.                                                                                                                                                                                                                                                                                                   |

| RX_ENAOUT3         | Output    | RX_CLK | Receive LBUS Enable for segment3.                                                                                                                                                                                                                                                                                                   |

| RX_SOPOUT0         | Output    | RX_CLK | Receive LBUS Start-Of-Packet for segment0. This signal indicates the Start Of Packet (SOP) when it is sampled as a 1 and is only valid in cycles in which RX_ENAOUT is sampled as a 1.                                                                                                                                              |

| RX_SOPOUT1         | Output    | RX_CLK | Receive LBUS Start-Of-Packet for segment1.                                                                                                                                                                                                                                                                                          |

| RX_SOPOUT2         | Output    | RX_CLK | Receive LBUS Start-Of-Packet for segment2.                                                                                                                                                                                                                                                                                          |

| RX_SOPOUT3         | Output    | RX_CLK | Receive LBUS Start-Of-Packet for segment3.                                                                                                                                                                                                                                                                                          |

| RX_EOPOUT0         | Output    | RX_CLK | Receive LBUS End-Of-Packet for segment0. This signal indicates the End Of Packet (EOP) when it is sampled as a 1 and is only valid in cycles in which RX_ENAOUT is sampled as a 1.                                                                                                                                                  |

| RX_EOPOUT1         | Output    | RX_CLK | Receive LBUS End-Of-Packet for segment1.                                                                                                                                                                                                                                                                                            |

| RX_EOPOUT2         | Output    | RX_CLK | Receive LBUS End-Of-Packet for segment2.                                                                                                                                                                                                                                                                                            |

| RX_EOPOUT3         | Output    | RX_CLK | Receive LBUS End-Of-Packet for segment3.                                                                                                                                                                                                                                                                                            |

| RX_ERROUT0         | Output    | RX_CLK | Receive LBUS Error for segment0. This signal indicates that the current packet being received has an error when it is sampled as a 1. This signal is only valid in cycles when both RX_ENAOUT and RX_EOPOUT are sampled as a 1. When this signal is a value of 0, it indicates that there is no error in the packet being received. |

| RX_ERROUT1         | Output    | RX_CLK | Receive LBUS Error for segment1.                                                                                                                                                                                                                                                                                                    |

| RX_ERROUT2         | Output    | RX_CLK | Receive LBUS Error for segment2.                                                                                                                                                                                                                                                                                                    |

| RX_ERROUT3         | Output    | RX_CLK | Receive LBUS Error for segment3.                                                                                                                                                                                                                                                                                                    |

|                    |           |        |                                                                                                                                                                                                                                                                                                                                     |

Table 2-4: LBUS Interface - RX Path Signals (Cont'd)

| Name            | Direction | Domain | Description                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX_MTYOUT0[3:0] | Output    | RX_CLK | Receive LBUS Empty for segment0. This bus indicates how many bytes of the RX_DATAOUT bus are empty or invalid for the last transfer of the current packet. This bus is only valid in cycles when both RX_ENAOUT and RX_EOPOUT are sampled as 1. When RX_ERROUT and RX_ENAOUT are sampled as 1, the value of RX_MTYOUT[2:0] is always 000. Other bits of RX_MTYOUT are as usual. |

| RX_MTYOUT1[3:0] | Output    | RX_CLK | Receive LBUS Empty for segment1.                                                                                                                                                                                                                                                                                                                                                |

| RX_MTYOUT2[3:0] | Output    | RX_CLK | Receive LBUS Empty for segment2.                                                                                                                                                                                                                                                                                                                                                |

| RX_MTYOUT3[3:0] | Output    | RX_CLK | Receive LBUS Empty for segment3.                                                                                                                                                                                                                                                                                                                                                |

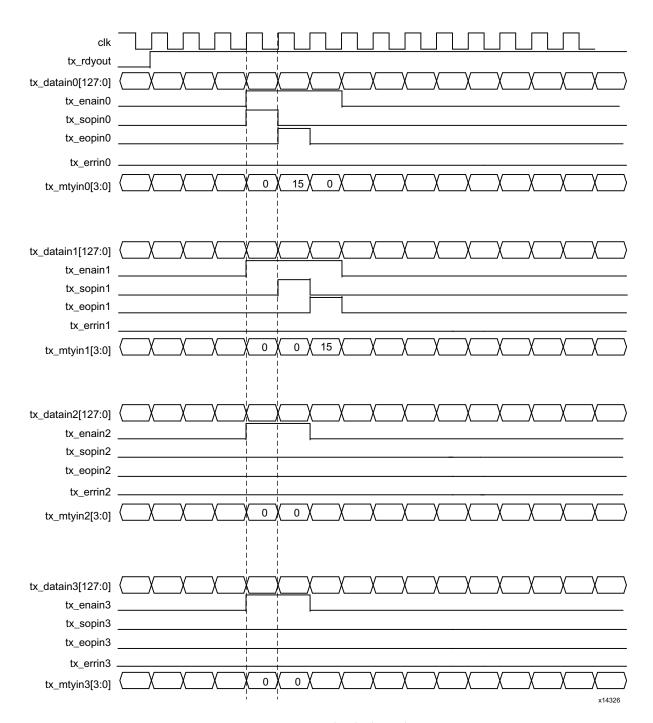

Table 2-5: LBUS Interface – TX Path Signals

| Name              | Direction | Domain | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_RDYOUT         | Output    | TX_CLK | Transmit LBUS Ready. This signal indicates whether the dedicated 100G Ethernet IP core TX path is ready to accept data and provides back-pressure to the user logic. A value of 1 means the user logic can pass data to the 100G Ethernet IP core. A value of 0 means the user logic must stop transferring data to the 100G Ethernet IP core within four cycles or there will be an overflow.        |

| TX_OVFOUT         | Output    | TX_CLK | Transmit LBUS Overflow. This signal indicates whether you have violated the back pressure mechanism provided by the TX_RDYOUT signal. If TX_OVFOUT is sampled as a 1, a violation has occurred. It is up to you to design the rest of the user logic to not overflow the TX interface. In the event of an overflow condition, the TX path must be reset.                                              |

| TX_UNFOUT         | Output    | TX_CLK | Transmit LBUS Underflow. This signal indicates whether you have under-run the LBUS interface. If TX_UNFOUT is sampled as 1, a violation has occurred meaning the current packet is corrupted. Error control blocks are transmitted as long as the underflow condition persists. It is up to the user logic to ensure a complete packet is input to the core without under-running the LBUS interface. |

| TX_DATAIN0[127:0] | Input     | TX_CLK | Transmit segmented LBUS Data for segment0. This bus receives input data from the user logic. The value of the bus is captured in every cycle that TX_ENAIN is sampled as 1.                                                                                                                                                                                                                           |

| TX_DATAIN1[127:0] | Input     | TX_CLK | Transmit segmented LBUS Data for segment1.                                                                                                                                                                                                                                                                                                                                                            |

| TX_DATAIN2[127:0] | Input     | TX_CLK | Transmit segmented LBUS Data for segment2.                                                                                                                                                                                                                                                                                                                                                            |

| TX_DATAIN3[127:0] | Input     | TX_CLK | Transmit segmented LBUS Data for segment3.                                                                                                                                                                                                                                                                                                                                                            |

Table 2-5: LBUS Interface – TX Path Signals (Cont'd)

| Name           | Direction | Domain | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_ENAIN0      | Input     | TX_CLK | Transmit LBUS Enable for segment0. This signal is used to enable the TX LBUS Interface. All signals on the transmit segmented LBUS interface are sampled only in cycles in which TX_ENAIN is sampled as a 1.                                                                                                                                                                                                                                                                                                                                                                          |

| TX_ENAIN1      | Input     | TX_CLK | Transmit LBUS Enable for segment1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TX_ENAIN2      | Input     | TX_CLK | Transmit LBUS Enable for segment2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TX_ENAIN3      | Input     | TX_CLK | Transmit LBUS Enable for segment3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TX_SOPIN0      | Input     | TX_CLK | Transmit LBUS Start Of Packet for segment0. This signal is used to indicate the Start Of Packet (SOP) when it is sampled as a 1 and is 0 for all other transfers of the packet. This signal is sampled only in cycles in which TX_ENAIN is sampled as a 1.                                                                                                                                                                                                                                                                                                                            |

| TX_SOPIN1      | Input     | TX_CLK | Transmit LBUS Start Of Packet for segment1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TX_SOPIN2      | Input     | TX_CLK | Transmit LBUS Start Of Packet for segment2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TX_SOPIN3      | Input     | TX_CLK | Transmit LBUS Start Of Packet for segment3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TX_EOPIN0      | Input     | TX_CLK | Transmit LBUS End Of Packet for segment0. This signal is used to indicate the End Of Packet (EOP) when it is sampled as a 1 and is 0 for all other transfers of the packet. This signal is sampled only in cycles in which TX_ENAIN is sampled as a 1.                                                                                                                                                                                                                                                                                                                                |

| TX_EOPIN1      | Input     | TX_CLK | Transmit LBUS End Of Packet for segment1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TX_EOPIN2      | Input     | TX_CLK | Transmit LBUS End Of Packet for segment2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TX_EOPIN3      | Input     | TX_CLK | Transmit LBUS End Of Packet for segment3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TX_ERRIN0      | Input     | TX_CLK | Transmit LBUS Error for segment0. This signal is used to indicate that a packet contains an error when it is sampled as a 1 and is 0 for all other transfers of the packet. This signal is sampled only in cycles in which TX_ENAIN and TX_EOPIN are sampled as 1. When this signal is sampled as a 1, the last data word is replaced with the IEEE standard 802.3-2012 Error Code control word that guarantees the partner device receives the packet in error. If a packet is input with this signal set to a 1, the FCS checking and reporting is disabled (only for that packet). |

| TX_ERRIN1      | Input     | TX_CLK | Transmit LBUS Error for segment1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TX_ERRIN2      | Input     | TX_CLK | Transmit LBUS Error for segment2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TX_ERRIN3      | Input     | TX_CLK | Transmit LBUS Error for segment3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TX_MTYIN0[3:0] | Input     | TX_CLK | Transmit LBUS Empty for segment0. This bus is used to indicate how many bytes of the TX_DATAIN bus are empty or invalid for the last transfer of the current packet. This bus is sampled only in cycles that TX_ENAIN and TX_EOPIN are sampled as 1. When TX_EOPIN and TX_ERRIN are sampled as 1, the value of TX_MTYIN[2:0] is ignored and treated as if it was 000. The other bits of TX_MTYIN are used as usual.                                                                                                                                                                   |

| TX_MTYIN1[3:0] | Input     | TX_CLK | Transmit LBUS Empty for segment1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Table 2-5: LBUS Interface – TX Path Signals (Cont'd)

| Name           | Direction | Domain | Description                       |

|----------------|-----------|--------|-----------------------------------|

| TX_MTYIN2[3:0] | Input     | TX_CLK | Transmit LBUS Empty for segment2. |

| TX_MTYIN3[3:0] | Input     | TX_CLK | Transmit LBUS Empty for segment3. |

Table 2-6: LBUS Interface – TX Path Control/Status Signals

| Name                | Direction | Domain | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTL_TX_ENABLE       | Input     | TX_CLK | TX Enable. This signal is used to enable the transmission of data when it is sampled as a 1. When sampled as a 0, only idles are transmitted by the 100G Ethernet IP core. This input should not be set to 1 until the receiver it is sending data to (that is, the receiver in the other device) is fully aligned and ready to receive data (that is, the other device is not sending a remote fault condition). Otherwise, loss of data can occur. If this signal is set to 0 while a packet is being transmitted, the current packet transmission is completed and then the 100G Ethernet IP core stops transmitting any more packets. |

| CTL_TX_SEND_LFI     | Input     | TX_CLK | Transmit Local Fault Indication (LFI) code word. If this input is sampled as a 1, the TX path only transmits Local Fault code words.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CTL_TX_SEND_RFI     | Input     | TX_CLK | Transmit Remote Fault Indication (RFI) code word. If this input is sampled as a 1, the TX path only transmits Remote Fault code words. This input should be set to 1 until the RX path is fully aligned and is ready to accept data from the link partner.                                                                                                                                                                                                                                                                                                                                                                                |

| CTL_TX_SEND_IDLE    | Input     | TX_CLK | Transmit Idle code words. If this input is sampled as a 1, the TX path only transmits Idle code words. This input should be set to 1 when the partner device is sending Remote Fault Indication (RFI) code words.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| STAT_TX_LOCAL_FAULT | Output    | TX_CLK | A value of 1 indicates the transmit encoder state machine is in the TX_INIT state. This output is level sensitive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 2-7: LBUS Interface - RX Path Control/Status Signals

| Name                        | Direction | Domain              | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------|-----------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTL_RX_ENABLE               | Input     | RX_CLK              | RX Enable. For normal operation, this input must be set to 1. When this input is set the to 0, after the RX completes the reception of the current packet (if any), it stops receiving packets by keeping the PCS from decoding incoming data. In this mode, there are no statistics reported and the LBUS interface is idle.                                                                      |

| CTL_RX_FORCE_RESYNC         | Input     | async<br>(5 ns min) | RX force resynchronization input. This signal is used to force the RX path to reset, re-synchronize, and realign. A value of 1 forces the reset operation. A value of 0 allows normal operation.  Note: This input should normally be Low and should only be pulsed (one cycle minimum pulse) to force realignment.                                                                                |

| STAT_RX_FRAMING_ERR_0[3:0]  | Output    | RX_CLK              | RX sync header bits framing error for lane 0. Each PCS Lane has a four-bit bus that indicates how many sync header errors were received for that PCS Lane. The value of the bus is only valid when the corresponding STAT_RX_FRAMING_ERR_VALID_[19:0] is a 1. The values on these buses can be updated at any time and are intended to be used as increment values for sync header error counters. |

| STAT_RX_FRAMING_ERR_1[3:0]  | Output    | RX_CLK              | RX sync header bits framing error for lane 1.                                                                                                                                                                                                                                                                                                                                                      |

| STAT_RX_FRAMING_ERR_2[3:0]  | Output    | RX_CLK              | RX sync header bits framing error for lane 2.                                                                                                                                                                                                                                                                                                                                                      |

| STAT_RX_FRAMING_ERR_3[3:0]  | Output    | RX_CLK              | RX sync header bits framing error for lane 3.                                                                                                                                                                                                                                                                                                                                                      |

| STAT_RX_FRAMING_ERR_4[3:0]  | Output    | RX_CLK              | RX sync header bits framing error for lane 4.                                                                                                                                                                                                                                                                                                                                                      |

| STAT_RX_FRAMING_ERR_5[3:0]  | Output    | RX_CLK              | RX sync header bits framing error for lane 5.                                                                                                                                                                                                                                                                                                                                                      |

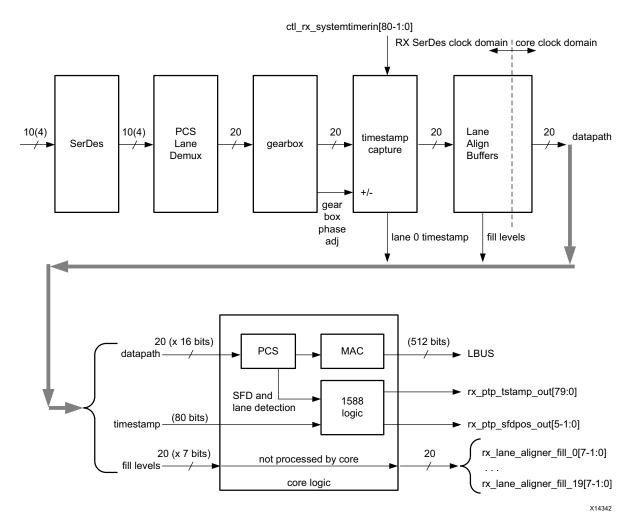

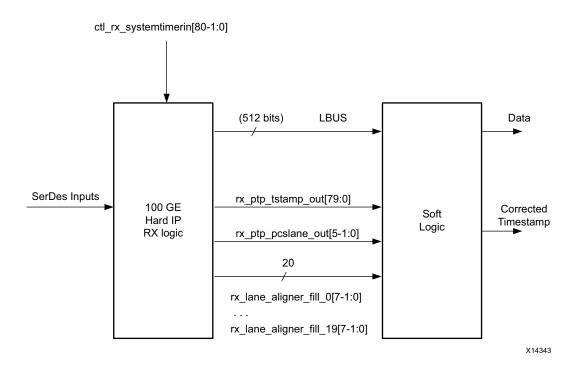

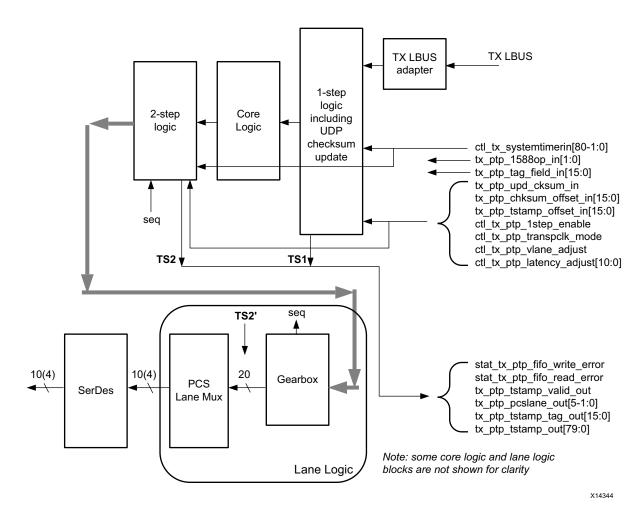

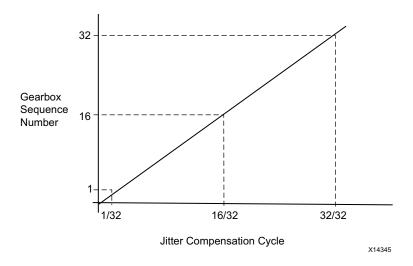

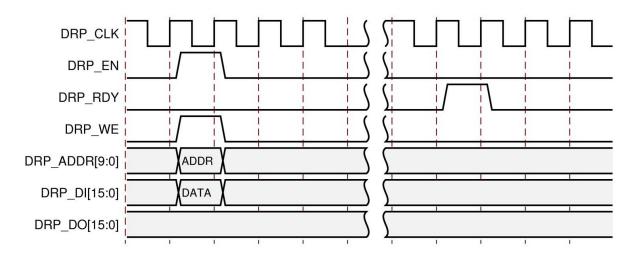

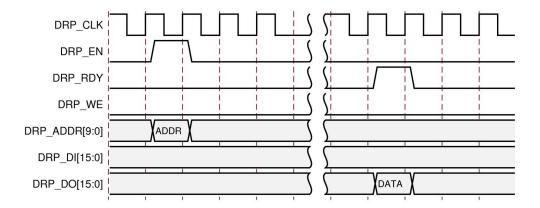

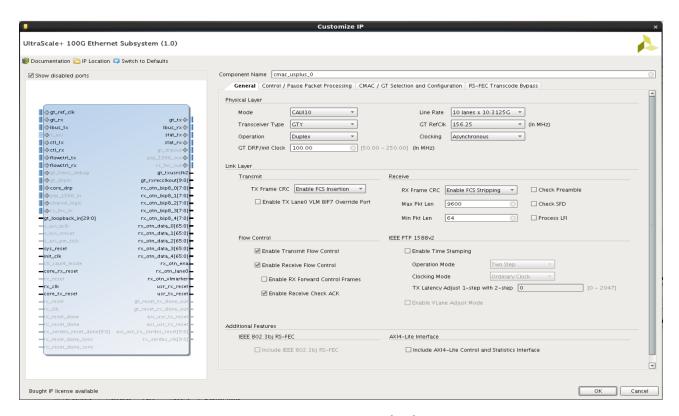

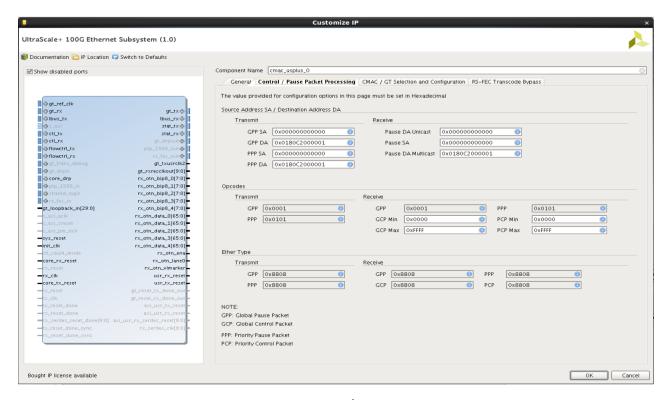

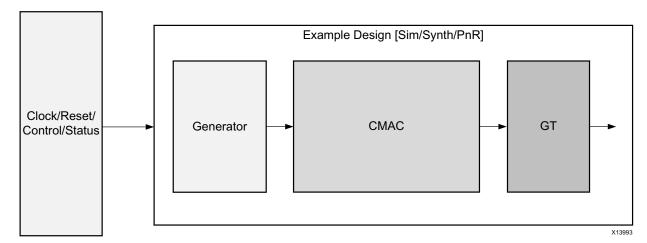

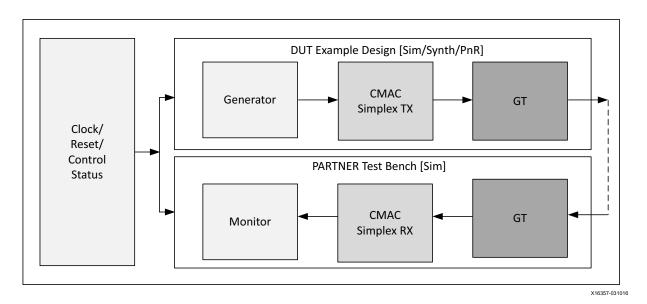

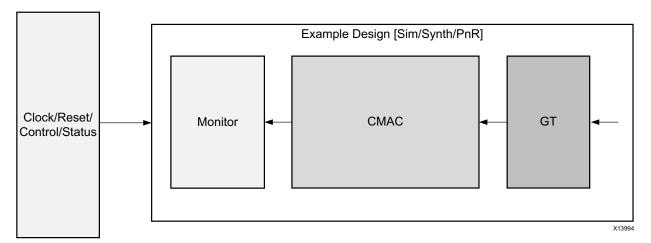

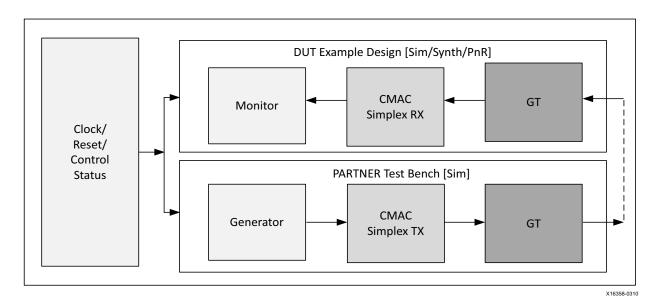

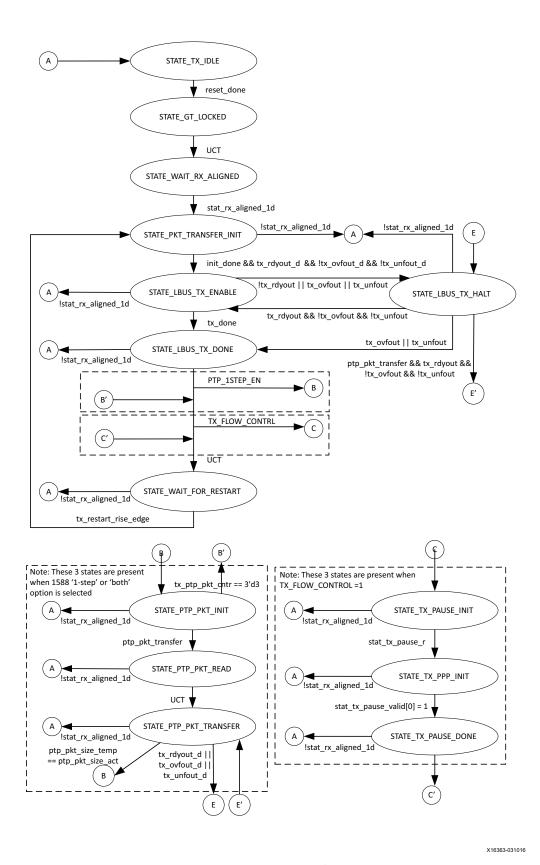

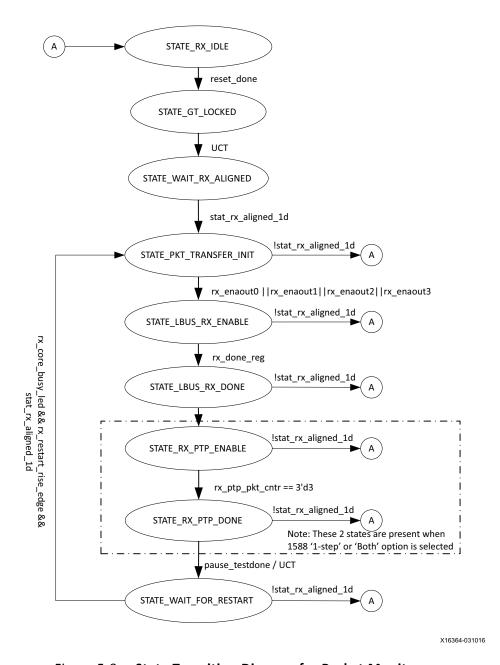

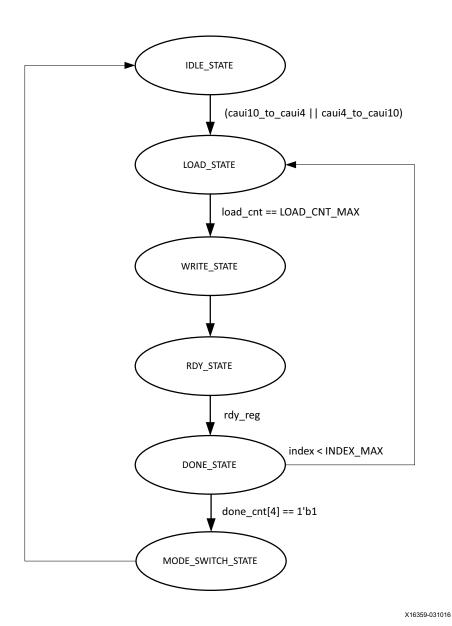

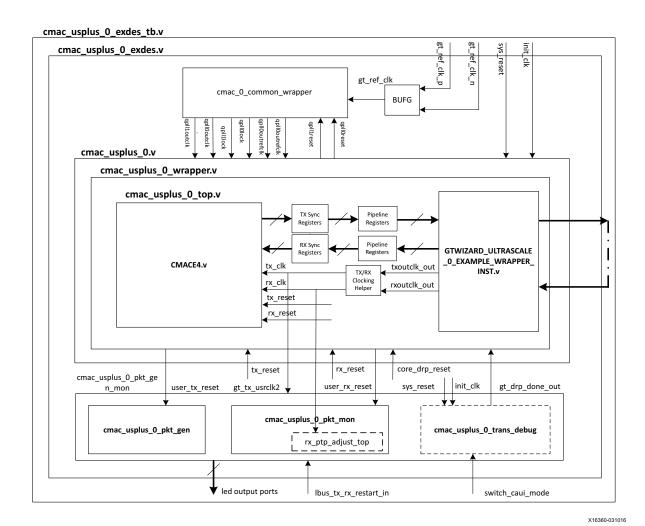

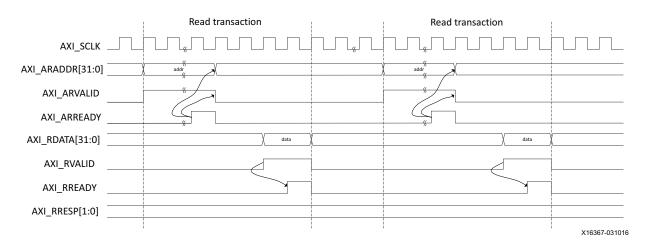

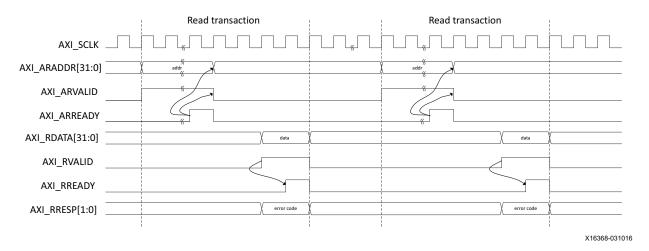

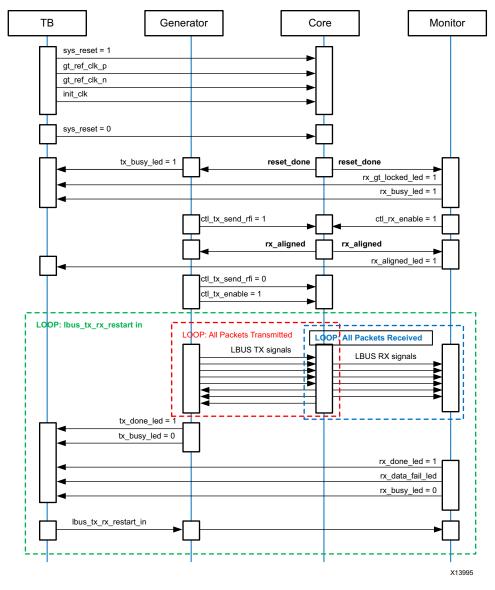

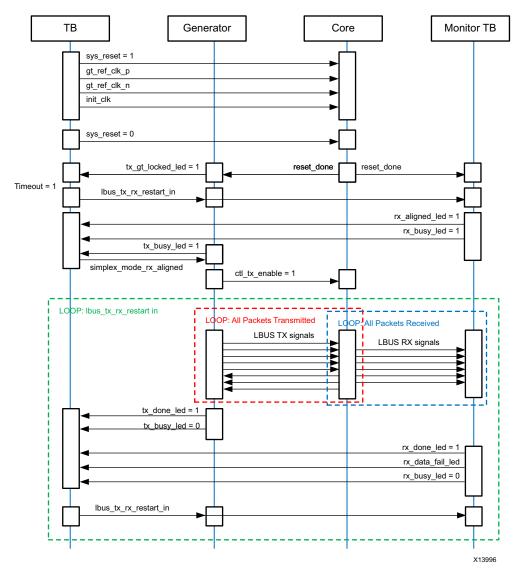

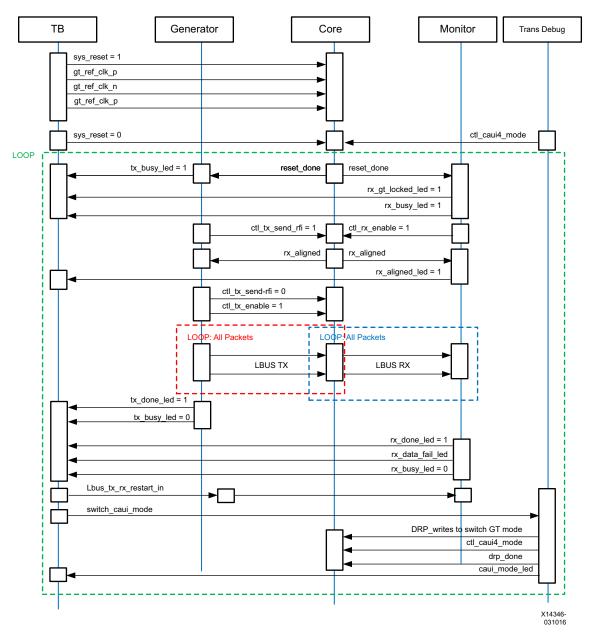

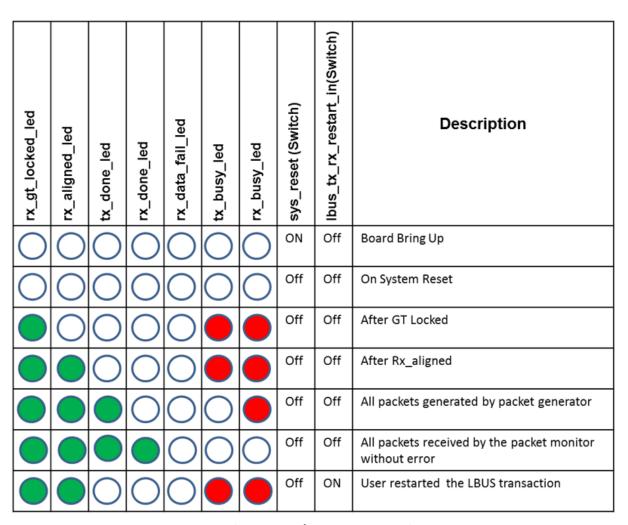

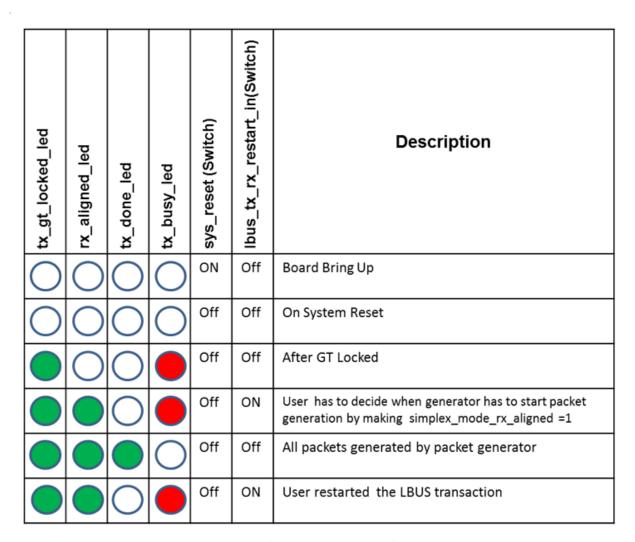

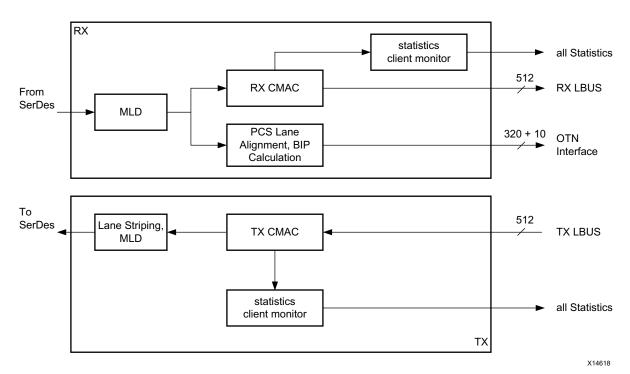

| STAT_RX_FRAMING_ERR_6[3:0]  | Output    | RX_CLK              | RX sync header bits framing error for lane 6.                                                                                                                                                                                                                                                                                                                                                      |