# **CAN FD v1.0**

# LogiCORE IP Product Guide

Vivado Design Suite

PG223 October 5, 2016

# **Table of Contents**

#### **IP Facts**

### Chapter 1: Overview

| Core Description                   | 7 |

|------------------------------------|---|

| Licensing and Ordering Information | 8 |

### **Chapter 2: Product Specification**

| Standards            | 9  |

|----------------------|----|

| Performance          | 9  |

| Resource Utilization | 9  |

| Port Descriptions    | 9  |

| Register Space       | 10 |

### **Chapter 3: Designing with the Core**

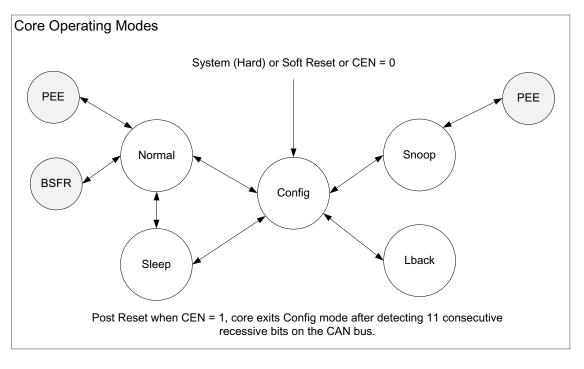

| Operating Modes and States | 57 |

|----------------------------|----|

| Programming Model          | 62 |

| Clocking                   | 70 |

| Resets                     | 70 |

| Interrupts                 | 71 |

### **Chapter 4: Design Flow Steps**

| Customizing and Generating the Core | 73 |

|-------------------------------------|----|

| Constraining the Core               | 76 |

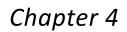

| Simulation                          | 77 |

| Synthesis and Implementation        | 77 |

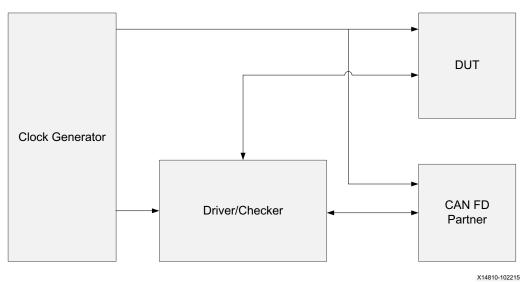

## Chapter 5: Example Design

| Overview                      | 78 |

|-------------------------------|----|

| Simulating the Example Design | 79 |

## Chapter 6: Test Bench

| Appendix A: Verification, Compliance, and Interoperability |  |

|------------------------------------------------------------|--|

| Compliance Testing                                         |  |

| Appendix B: Migrating and Upgrading                        |  |

| Migrating to the Vivado Design Suite         83            |  |

| Upgrading in the Vivado Design Suite                       |  |

| Appendix C: Debugging                                      |  |

| Finding Help on Xilinx.com    84                           |  |

| Debug Tools                                                |  |

| Hardware Debug                                             |  |

| Interface Debug                                            |  |

| Appendix D: Additional Resources and Legal Notices         |  |

| Xilinx Resources                                           |  |

| References                                                 |  |

| Revision History    90                                     |  |

| Please Read: Important Legal Notices       90              |  |

## Introduction

The Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP CAN with Flexible Data-Rate (CAN FD) core is ideally suited for automotive and industrial applications such as automotive body control units, automotive test equipment, instrument clusters, sensor controls, and industrial networks. The core can be used in stand-alone mode or connected to Xilinx MicroBlaze<sup>™</sup> processors or the ARM<sup>®</sup> Cortex-A9 processors in Zynq<sup>®</sup>-7000 All Programmable SoC.

## Features

- Designed to ISO 11898-1/2015 specification

- Supports both CAN and CAN FD frames

- Parameterized support to select between ISO CAN FD frame or non-ISO CAN FD frame formats<sup>(1)</sup>

- Supports up to 64 bytes CAN FD frames

- Supports flexible data rates > 4 Mb/s

- Transmitter Delay compensation up to three data bit

- TX and RX mailbox buffers with a user configuration depth

- 32-deep Sequential RX buffers (FIFO mode) with 32 ID Filter-Mask pairs

- Message with lowest ID transmitted first

- Supports TX Message Cancellation

- Separate error logging for fast data rate

**IMPORTANT:** It is required to have a valid Bosch CAN FD protocol license before selling a device containing the Xilinx CAN FD IP core.

| LogiCORE™ IP Facts Table                          |                                                                                                               |  |  |  |  |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Core Specifics                                    |                                                                                                               |  |  |  |  |

| Supported<br>Device Family <sup>(1)</sup>         | UltraScale+™ Families,<br>UltraScale™ Architecture,<br>Zynq <sup>®</sup> -7000 All Programmable SoC, 7 Series |  |  |  |  |

| Supported User<br>Interfaces                      | AXI4-Lite                                                                                                     |  |  |  |  |

| Resources                                         | Performance and Resource Utilization web page                                                                 |  |  |  |  |

|                                                   | Provided with Core                                                                                            |  |  |  |  |

| Design Files                                      | Encrypted RTL                                                                                                 |  |  |  |  |

| Example Design                                    | Verilog                                                                                                       |  |  |  |  |

| Test Bench                                        | Verilog                                                                                                       |  |  |  |  |

| Constraints File                                  | XDC                                                                                                           |  |  |  |  |

| Simulation<br>Model                               | Not Provided                                                                                                  |  |  |  |  |

| Supported<br>S/W Driver <sup>(2)</sup>            | Standalone and Linux                                                                                          |  |  |  |  |

|                                                   | Tested Design Flows <sup>(3)</sup>                                                                            |  |  |  |  |

| Design Entry                                      | Vivado <sup>®</sup> Design Suite                                                                              |  |  |  |  |

| Simulation                                        | For supported simulators, see the<br>Xilinx Design Tools: Release Notes Guide.                                |  |  |  |  |

| Synthesis                                         | Vivado Synthesis                                                                                              |  |  |  |  |

| Support                                           |                                                                                                               |  |  |  |  |

| Provided by Xilinx at the Xilinx Support web page |                                                                                                               |  |  |  |  |

#### Notes:

- 1. For a complete listing of supported devices, see the Vivado IP catalog.

- Standalone driver details can be found in the SDK directory (<install\_directory>/SDK/<release>/data/embeddedsw/doc/ xilinx\_drivers.htm). Linux OS and driver support information is available from the Xilinx Wiki page.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

www.xilinx.com

<sup>1.</sup> CAN FD frame format specified in ISO 11898:2015 specification [Ref 1] is called ISO CAN FD frame format. CAN FD frame format specified in Bosch CAN FD specification [Ref 2] is called non-ISO CAN FD frame format.

## **Other Features**

- Timestamp for transmitted and received messages

- Supports the following:

- Disable Auto-retransmission (DAR) mode

- Snoop (Bus Monitoring) mode

- Sleep mode with Wake-up interrupt

- Internal Loopback mode

## Overview

This product guide describes features of the Xilinx LogiCORE IP CAN FD core and the functionality of the various registers in the design. In addition, the core interface and its customization options are defined in this document.

Information on the CAN or CAN FD protocol is outside the scope of this document, and knowledge of the relevant CAN and CAN FD specifications is assumed.

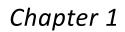

Figure 1-1 illustrates the high-level architecture of the CAN FD core and provides the interface connectivity.

*Note:* The core requires an external PHY to be connected to communicate on the CAN bus.

## **Core Description**

The core functions are divided into two independent layers as shown in Figure 1-1. Object layer interfaces with the Host Control through the AXI4-Lite interface and works in the AXI4 clock domain. The Transfer Layer interfaces with the external PHY and operates in the CAN clock domain. Information exchanges between the two layers is done through the CDC synchronizers. The CAN FD object layer provides a state-of-the-art transmission and reception method to manage message buffers.

## **Object Layer (Logical Link Layer)**

The object layer is divided into the following submodules:

- **Register Module** This module allows for read and write access to the registers through the external Host interface.

- **TX Buffer Management Module** TX Buffer Management Module (TBMM) interfaces with the CAN FD protocol engine to provide the next buffer to transmit on the CAN bus. It manages the Host access to the TX block RAM.

- RX Buffer Management Module RX Buffer Management Module (RBMM) interfaces with the CAN FD protocol engine to provide storage for message reception from the CAN bus. It manages the Host access to the RX block RAM.

## Transfer Layer (Medium Access Control Layer)

Transfer layer provides the following main functions:

- Initiation of the transmission process after recognizing bus idle (compliance with inter-frame space).

- Serialization of the frame

- Bit stuffing

- Arbitration and passing into receive mode in case of loss of arbitration

- ACK check

- Presentation of a serial bitstream to PHY for transmission

- CRC sequence calculation including stuff bit count for FD frames

- Bit rate switching

- Reception of a serial bitstream from the PHY.

- Deserialization and recompiling of the frame structure

- Bit de-stuffing

- Transmission of ACK

- Bit rate switching

- Bit timing functions.

- Error detection and signaling.

- Recognition of an overload condition and reaction.

## **Licensing and Ordering Information**

**IMPORTANT:** It is required to have a valid Bosch CAN FD protocol license before selling a device containing the Xilinx CAN FD IP core.

## **License Checkers**

If the IP requires a license key, the key must be verified. The Vivado<sup>®</sup> design tools have several license checkpoints for gating licensed IP through the flow. If the license check succeeds, the IP can continue generation. Otherwise, generation halts with error. License checkpoints are enforced by the following tools:

- Vivado synthesis

- Vivado implementation

- write\_bitstream (Tcl command)

**IMPORTANT:** *IP license level is ignored at checkpoints. The test confirms a valid license exists. It does not check IP license level.*

## License Type

The core is provided under the terms of the CAN FD LogiCORE<sup>™</sup> IP License Agreement for <u>Automotive</u> or <u>Non-Automotive</u> applications. <u>Click here</u> for more information about obtaining a CAN FD license.

For more information, visit the CAN FD product web page.

Information about other Xilinx LogiCORE IP modules is available at the <u>Xilinx Intellectual</u> <u>Property</u> page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your <u>local Xilinx sales representative</u>.

## Chapter 2

# **Product Specification**

## Standards

The CAN FD core conforms to the ISO-11898-1/2015 standard specification.

## Performance

For full details about performance and resource utilization, visit the <u>Performance and</u> <u>Resource Utilization web page</u>.

## **Resource Utilization**

For full details about performance and resource utilization, visit the <u>Performance and</u> <u>Resource Utilization web page</u>.

## **Port Descriptions**

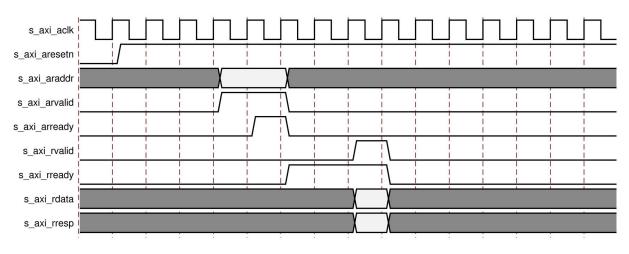

The Host interface of the CAN FD core is the AXI4-Lite Interface. Table 2-1 defines the core interface signaling.

| Signal Name                      | Interface                                                                                                                                    | Туре | Default | Description                                                                        |  |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|---------|------------------------------------------------------------------------------------|--|--|

| AXI4-Lite Interface Signals      |                                                                                                                                              |      |         |                                                                                    |  |  |

| s_axi_* <sup>(1)</sup>           | s_axi_* <sup>(1)</sup> S_AXI_LITE – – See the <i>Vivado AXI Reference Guide</i> (UG1037)<br>[Ref 6] for the description of the AXI4 signals. |      |         |                                                                                    |  |  |

| Clock, Interrupt and PHY Signals |                                                                                                                                              |      |         |                                                                                    |  |  |

| ip2bus_intrevent                 | Interrupt                                                                                                                                    | 0    | 0x0     | Active-High interrupt line. <sup>(2)(3)</sup>                                      |  |  |

| can_clk                          | Clock                                                                                                                                        | Ι    | -       | CAN Clock input. Oscillator frequency tolerance as per the standard specification. |  |  |

| Table 2-1: | CAN FD  | Core | I/O Signa   | ls |

|------------|---------|------|-------------|----|

|            | 0/11110 | 00.0 | 1, 0 0.5.10 |    |

www.xilinx.com

Table 2-1: CAN FD Core I/O Signals (Cont'd)

| Signal Name | Interface | Туре | Default | Description                                          |  |

|-------------|-----------|------|---------|------------------------------------------------------|--|

| can_phy_tx  | РНҮ       | 0    | 1       | CAN bus transmit signal to PHY.                      |  |

| can_phy_rx  | РНҮ       | Ι    | -       | <ul> <li>CAN bus receive signal from PHY.</li> </ul> |  |

Notes:

1. The core does not support wstrb signal on the AXI4-Lite interface.

- 2. The interrupt line is level sensitive. Interrupts are indicated by the transition of the interrupt line logic from 0 to 1.

- 3. The AXI4-Lite interface signals and ip2bus\_intrevent are synchronous to s\_axi\_aclk clock.

## **Register Space**

The CAN FD core requires 8 KB memory mapped space to be allocated in system memory. Division of this addressable space within the core is shown in Table 2-2.

**Note:** The AXI4-Lite write access register is updated by the 32-bit AXI Write Data (\*\_wdata) signal, and is not impacted by the AXI Write Data Strobe (\*\_wstrb) signal. For write access, both the AXI Write Address Valid (\*\_awvalid) and AXI Write Data Valid (\*\_wvalid) signals should be asserted together.

| Start Address | End Address | Section              | Notes                                                                                                                                                                                                                                                                                                                  |

|---------------|-------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000        | 0x00FF      | Core Registers Space | This space is implemented with flip-flops. See Table 2-3 and Table 2-4.                                                                                                                                                                                                                                                |

| 0x0100        | 0x0FFF      | TX Message Space     | This space is implemented with TX block RAM and provides storage for a maximum 32 TX buffers. See Table 2-28.                                                                                                                                                                                                          |

| 0x1000        | 0x1FFF      | RX Message Space     | This space is implemented with RX block RAM.<br>For RX Sequential buffer mode (FIFO mode), it<br>provides storage for 32-deep message FIFO and 32<br>ID Filter-Mask pairs. See Table 2-32.<br>For RX Mailbox buffer mode, it provides storage for<br>maximum 48 RX Buffers and respective ID Masks.<br>See Table 2-38. |

Table 2-2: CAN FD Address Space Division

#### Table 2-3: CAN FD Core Register Address Map

| Start<br>Address  | Name     | Access                    | Description                                                                | Notes                                                            |

|-------------------|----------|---------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------|

| 0x0000            | SRR      | Read, Write               | Software Reset Register                                                    |                                                                  |

| 0x0004            | MSR      | Read, Write               | Mode Select Register                                                       |                                                                  |

| 0x0008            | BRPR     | Read, Write               | Arbitration Phase Baud Rate Prescaler<br>Register                          |                                                                  |

| 0x000C            | BTR      | Read, Write               | Arbitration Phase Bit Register                                             |                                                                  |

| 0x0010            | ECR      | Read                      | Error Counter Register                                                     |                                                                  |

| 0x0014            | ESR      | Read, Write<br>1 to clear | Error Status Register                                                      |                                                                  |

| 0x0018            | SR       | Read                      | Status Register                                                            |                                                                  |

| 0x001C            | ISR      | Read                      | Interrupt Status Register                                                  |                                                                  |

| 0x0020            | IER      | Read, Write               | Interrupt Enable Register                                                  |                                                                  |

| 0x0024            | ICR      | Write                     | Interrupt Clear Register                                                   | Registers present in both RX Mailbox and RX                      |

| 0x0028            | TSR      | Read, Write               | Timestamp Register                                                         | Sequential/FIFO buffer                                           |

| 0x002C-<br>0x0084 | Reserved | -                         | Reserved space. Write has no effect. Read always returns 0.                | mode.                                                            |

| 0x0088            | DP_BRPR  | Read, Write               | Data Phase Baud Rate Prescaler Register                                    |                                                                  |

| 0x008C            | DP_BTR   | Read, Write               | Data Phase Bit Timing Register                                             |                                                                  |

| 0x0090            | TRR      | Read, Write               | TX Buffer Ready Request Register                                           |                                                                  |

| 0x0094            | IETRS    | Read, Write               | Interrupt Enable TX Buffer Ready Request<br>Served/Cleared Register        |                                                                  |

| 0x0098            | TCR      | Read, Write               | TX Buffer Cancel Request Register                                          |                                                                  |

| 0x009C            | IETCS    | Read, Write               | Interrupt Enable TX Buffer Cancellation<br>Request Served/Cleared Register |                                                                  |

| 0x00A0-<br>0x00AC | Reserved | -                         | Reserved space. Write has no effect. Read always returns 0.                |                                                                  |

| 0x00B0            | RCS0     | Read, Write               | RX Buffer Control Status Register 0                                        |                                                                  |

| 0x00B4            | RCS1     | Read, Write               |                                                                            |                                                                  |

| 0x00B8            | RCS2     | Read, Write               | See RX Buffer Control Status Register 0                                    |                                                                  |

| 0x00BC            | Reserved | -                         | Reserved space. Write has no effect. Read always returns 0                 | Registers present only<br>in RX Mailbox buffer<br>mode otherwise |

| 0x00C0            | IERBF0   | Read, Write               | Interrupt Enable RX Buffer Full Register 0                                 | reserved.                                                        |

| 0x00C4            | IEBRF1   | Read, Write               | Interrupt Enable RX Buffer Full Register 1                                 |                                                                  |

| 0x00C8-<br>0x00DC | Reserved | -                         | Reserved space. Write has no effect. Read always returns 0.                |                                                                  |

| Start<br>Address  | Name     | Access      | Description                                                 | Notes                                          |

|-------------------|----------|-------------|-------------------------------------------------------------|------------------------------------------------|

| 0x00E0            | AFR      | Read, Write | Acceptance Filter (Control) Register                        |                                                |

| 0x00E4            | Reserved | -           | Reserved space. Write has no effect. Read always returns 0. | Registers present only                         |

| 0x00E8            | FSR      | Read, Write | RX FIFO Status Register                                     | in RX Sequential/FIFO<br>buffer mode otherwise |

| 0x00EC            | WMR      | Read, Write | RX FIFO Watermark Register                                  | reserved.                                      |

| 0x00F0-<br>0x00FF | Reserved | -           | Reserved space. Write has no effect. Read always returns 0. |                                                |

#### Table 2-3: CAN FD Core Register Address Map (Cont'd)

## **Core Register Descriptions**

Table 2-4 shows the CAN FD core register space. The thick ruling represents the RX Mailbox specific register bits and the gray means RX FIFO specific register bits.

Table 2-4: CAN FD Core Register Space

| Start<br>Address | 31      | 30            | 29 | 28  | 27  | 26                      | 25     | 24       | 23     | 22     | 21      | 20        | 19    | 18          | 17         | 16          | 15   | 14      | 13    | 12    | 11      | 10    | 9     | 8       | 7         | 6    | 5      | 4         | 3     | 2     | 1     | 0         | Name<br>(Reset<br>Value) |

|------------------|---------|---------------|----|-----|-----|-------------------------|--------|----------|--------|--------|---------|-----------|-------|-------------|------------|-------------|------|---------|-------|-------|---------|-------|-------|---------|-----------|------|--------|-----------|-------|-------|-------|-----------|--------------------------|

| 0x0000           | RS      | SVD           |    |     |     |                         |        |          |        |        |         |           |       |             |            |             |      |         |       |       |         |       |       |         |           |      |        |           |       |       | CEN   | SRST      | SRR (0x0)                |

| 0x0004           | RS      | SVD           |    |     |     |                         |        |          |        |        |         |           |       |             |            |             |      |         |       |       |         |       |       |         | ABR       | SBR  | DPEE   | DAR       | BRSD  | SNOOP | LBACK | SLEEP     | MSR<br>(0x0)             |

| 0x0008           | RS      | SVD           |    |     |     |                         |        |          |        |        |         |           |       |             |            |             |      |         |       |       |         |       |       |         | BR        | P [7 | :0]    |           |       |       |       |           | BRPR<br>(0x0)            |

| 0x000C           | RS      | SVD           |    |     |     |                         |        |          |        |        |         |           | SJ    | W[3         | :0]        |             | RS   | SVD     |       |       | ΤS      | 2[3:0 | )]    |         | RS        | VD   |        | TS        | 1[5:0 | )]    |       |           | BTR (0x0)                |

| 0x0010           | RS      | SVD           |    |     |     |                         |        |          |        |        |         |           |       |             |            | RE          | C[7  | :0]     |       |       |         |       |       | TE      | C[7:0     | D]   |        |           |       |       |       | ECR (0x0) |                          |

| 0x0014           | RS      |               |    |     |     |                         |        |          |        |        |         |           |       | CRCER       | ESR (0x0)  |             |      |         |       |       |         |       |       |         |           |      |        |           |       |       |       |           |                          |

| 0x0018           | RS      | SVD TDCV[6:0] |    |     |     |                         |        |          | RS     | SVD    |         | SNOOP     | NISO  | BSFR_CONFIG | PEE_CONFIG | EETAT [1:0] |      | ERRWRN  | BBSY  | BIDLE | NORMAL  | SLEEP | LBACK | CONFIG  | SR (0x1)  |      |        |           |       |       |       |           |                          |

| 0x001C           | RS<br>D | SV            | RX | BOF | ELW | _I [5:0] RXLRM_BI [5:0] |        |          |        | RXMNF  | RXBOFLW | RXBFL     | TXCRS | TXRRS       | RXFWMFLL   | WKUP        | SLP  | BSOFF   | ERROR | RSVD  | RXFOFLW | RSVD  | RXOK  | BSFRD   | PEE       | тхок | ARBLST | ISR (0x0) |       |       |       |           |                          |

| 0x0020           | RS      | RSVD          |    |     |     |                         | ERXMNF | ERXBOFLW | ERXBFL | ETXCRS | ETXRRS  | ERXFWMFLL | EWKUP | ESLP        | EBSOFF     | EERROR      | RSVD | ERXOFLW | RSVD  | ERXOK | EBSFRD  | EPEE  | ETXOK | EARBLST | IER (0x0) |      |        |           |       |       |       |           |                          |

#### Table 2-4: CAN FD Core Register Space (Cont'd)

| Start<br>Address      | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30                                                                                                                                                                                                   | 29     | 28     | 27     | 26     | 25     | 24     | 23     | 22     | 21     | 20        | 19             | 18              | 17             | 16       | 15     | 14     | 13     | 12        | 11     | 10     | 9      | 8      | 7     | 6       | 5            | 4     | 3      | 2     | 1     | 0       | Name<br>(Reset<br>Value) |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------|----------------|-----------------|----------------|----------|--------|--------|--------|-----------|--------|--------|--------|--------|-------|---------|--------------|-------|--------|-------|-------|---------|--------------------------|

| 0x0024                | RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VD                                                                                                                                                                                                   |        |        |        |        |        |        |        |        |        |           |                |                 | CRXMNF         | CRXBOFLW | CRXBFL | CTXCRS | CTXRRS | CRXFWMFLL | CWKUP  | CSLP   | CBSOFF | CERROR | RSVD  | CRXOFLW | RSVD         | CRXOK | CBSFRD | CPEE  | стхок | CARBLST | ICR (0x0)                |

| 0x0028                | TI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MES                                                                                                                                                                                                  | TAN    | 1P_C   | CNT    | 15:0   | )]     |        |        |        |        |           |                |                 |                | RS       | VD     |        |        |           | •      |        |        |        |       |         |              |       |        |       |       | CTS     | TSR (0x0)                |

| 0x002C<br>-<br>0x0084 | RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VD                                                                                                                                                                                                   |        |        |        |        |        |        |        |        |        |           |                |                 |                |          |        |        |        |           |        |        |        |        |       |         |              |       |        |       |       |         | Reserved                 |

| 0x0088                | RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VD                                                                                                                                                                                                   |        |        |        |        |        |        |        |        |        |           |                |                 |                | TDC_EN   | RS     | VD     |        | TD        | COF    | F [4   | :0]    |        | DP    | _BR     | P [7:        | :0]   |        |       |       |         | DP_BRPR<br>(0x0)         |

| 0x008C                | RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RSVD DP_SJW RSVD DP_TS2 RSVD DP_TS1[3:0]                                                                                                                                                             |        |        |        |        |        |        |        |        |        |           | )]             | DP_BTR<br>(0x0) |                |          |        |        |        |           |        |        |        |        |       |         |              |       |        |       |       |         |                          |

| 0x0090                | RR31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RR30<br>RR25<br>RR25<br>RR25<br>RR25<br>RR24<br>RR24<br>RR23<br>RR23<br>RR21<br>RR21<br>RR19<br>RR19<br>RR19<br>RR13<br>RR16<br>RR13<br>RR13<br>RR16<br>RR13<br>RR16<br>RR13<br>RR16<br>RR13<br>RR13 |        |        |        |        |        |        |        |        | RR0    | TRR (0x0) |                |                 |                |          |        |        |        |           |        |        |        |        |       |         |              |       |        |       |       |         |                          |

| 0x0094                | ERRS31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                      |        |        |        |        |        |        |        |        |        |           |                | ERRSO           | IETRS<br>(0x0) |          |        |        |        |           |        |        |        |        |       |         |              |       |        |       |       |         |                          |

| 0x0098                | CR31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CR30                                                                                                                                                                                                 | CR29   | CR28   | CR27   | CR26   | CR25   | CR24   | CR23   | CR22   | CR21   | CR20      | CR19           | CR18            | CR17           | CR16     | CR15   | CR14   | CR13   | CR12      | CR11   | CR10   | CR9    | CR8    | CR7   | CR6     | CR5          | CR4   | CR3    | CR2   | CR1   | CR0     | TCR (0x0)                |

| 0x009C                | ECRS31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ECRS30                                                                                                                                                                                               | ECRS29 | ECRS28 | ECRS27 | ECRS26 | ECRS25 | ECRS24 | ECRS23 | ECRS22 | ECRS21 | ECRS20    | ECRS19         | ECRS18          | ECRS17         | ECRS16   | ECRS15 | ECRS14 | ECRS13 | ECRS12    | ECRS11 | ECRS10 | ECRS9  | ECRS8  | ECRS7 | ECRS6   | <b>ECRS5</b> | ECRS4 | ECRS3  | ECRS2 | ECRS1 | ECRSO   | IETCS<br>(0x0)           |

| 0x00A0                | RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VD                                                                                                                                                                                                   |        |        |        |        |        |        |        |        |        |           |                |                 |                |          |        |        |        |           |        |        |        |        |       |         |              |       |        |       |       |         | Reserved                 |

| 0x00A4                | RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VD                                                                                                                                                                                                   |        |        |        |        |        |        |        |        |        |           |                |                 |                |          |        |        |        |           |        |        |        |        |       |         |              |       |        |       |       |         | Reserved                 |

| 0x00A8                | RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VD                                                                                                                                                                                                   |        |        |        |        |        |        |        |        |        |           |                |                 |                |          |        |        |        |           |        |        |        |        |       |         |              |       |        |       |       |         | Reserved                 |

| 0x00AC                | RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VD                                                                                                                                                                                                   |        |        | -      |        | -      |        | r –    |        |        |           |                |                 |                |          |        |        |        |           | -      | 1      | -      |        |       |         |              | -     | 1      | -     | -     |         | Reserved                 |

| 0x00B0                | CSB15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CSB14                                                                                                                                                                                                | CSB13  | CSB12  | CSB11  | CSB10  | CSB9   | CSB8   | CSB7   | CSB6   | CSB5   | CSB4      | CSB3           | CSB2            | CSB1           | CSB0     | HCB15  | HCB14  | HCB13  | HCB12     | HCB11  | HCB10  | HCB9   | HCB8   | HCB7  | HCB6    | HCB5         | HCB4  | HCB3   | HCB2  | HCB1  | HCB0    | RCS0<br>(0x0)            |

| 0x00B4                | CSB31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CSB30                                                                                                                                                                                                | CSB29  | CSB28  | CSB27  | CSB26  | CSB25  | CSB24  | CSB23  | CSB22  | CSB21  | CSB20     | CSB19          | CSB18           | CSB17          | CSB16    | HCB31  | HCB30  | HCB29  | HCB28     | HCB27  | HCB26  | HCB25  | HCB24  | HCB23 | HCB22   | HCB21        | HCB20 | HCB19  | HCB18 | HCB17 | HCB16   | RCS1<br>(0x0)            |

| 0x00B8                | CSB47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CSB46                                                                                                                                                                                                | CSB45  | CSB44  | CSB43  | CSB42  | CSB41  | CSB40  | CSB39  | CSB38  | CSB37  | CSB36     | CSB35          | CSB34           | CSB33          | CSB32    | HCB47  | HCB46  | HCB45  | HCB44     | HCB43  | HCB42  | HCB41  | HCB40  | HCB39 | HCB38   | HCB37        | HCB36 | HCB35  | HCB34 | HCB33 | HCB32   | RCS2<br>(0x0)            |

| 0x00BC                | RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VD                                                                                                                                                                                                   |        |        |        |        |        |        |        |        |        |           |                |                 |                |          |        |        |        |           |        |        |        |        |       |         |              |       |        |       |       |         | Reserved                 |

| 0x00C0                | ERBF31         ERBF30         ERBF30         ERBF23         ERBF26         ERBF26         ERBF26         ERBF27         ERBF26         ERBF27         ERBF26         ERBF27         ERBF27         ERBF26         ERBF27         ERBF27         ERBF21         ERBF16         ERBF17         ERBF18         ERBF16         ERBF17         ERBF16         ERBF17         ERBF16         ERBF16         ERBF17         ERBF18         ERBF16         ERBF17         ERBF16         ERBF17         ERBF16         ERBF17         ERBF16         ERBF17         ERBF16         ERBF17         ERBF18         ERBF18         ERBF18         ERBF5         ERBF6         ERBF7         ERBF6         ERBF7         ERBF6         ERBF7         ERBF7         ERBF7 |                                                                                                                                                                                                      |        |        |        |        |        |        |        |        |        | ERBFO     | IERBF<br>(0x0) |                 |                |          |        |        |        |           |        |        |        |        |       |         |              |       |        |       |       |         |                          |

| 0x00C4                | 4         ERBF47           ERBF46         ERBF46           ERBF45         ERBF46           ERBF46         ERBF46           ERBF47         ERBF46           ERBF48         ERBF48           ERBF38         ERBF38           ERBF34         ERBF38           ERBF34         ERBF38                                                                                                                                                                                                                                             |                                                                                                                                                                                                      |        |        |        |        |        |        |        |        |        |           | ERBF32         | IERBF<br>(0x0)  |                |          |        |        |        |           |        |        |        |        |       |         |              |       |        |       |       |         |                          |

| 0x00C8                | RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VD                                                                                                                                                                                                   |        |        |        |        |        |        |        |        |        |           |                |                 |                |          |        |        |        |           |        |        |        |        |       |         |              |       |        |       |       |         | Reserved                 |

| 0x00CC                | RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VD                                                                                                                                                                                                   |        |        |        |        |        |        |        |        |        |           |                |                 |                |          |        |        |        |           |        |        |        |        |       |         |              |       |        |       |       |         | Reserved                 |

| 0x00D0                | RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RSVD                                                                                                                                                                                                 |        |        |        |        |        |        |        |        |        | Reserved  |                |                 |                |          |        |        |        |           |        |        |        |        |       |         |              |       |        |       |       |         |                          |

#### Table 2-4: CAN FD Core Register Space (Cont'd)

| Start<br>Address | 31    | 30                                                | 29    | 28    | 27    | 26    | 25    | 24    | 23    | 22    | 21    | 20    | 19    | 18    | 17        | 16       | 15    | 14    | 13    | 12    | 11    | 10    | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | Name<br>(Reset<br>Value) |

|------------------|-------|---------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-----------|----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|--------------------------|

| 0x00D4           | RS    | VD                                                |       |       |       |       |       |       |       |       |       |       |       |       |           |          |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      | Reserved                 |

| 0x00D8           | RS    | VD                                                |       |       |       |       |       |       |       |       |       |       |       |       |           |          |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      | Reserved                 |

| 0x00DC           | RS    | VD                                                |       |       |       |       |       |       |       |       |       |       |       |       |           |          |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      | Reserved                 |

| 0x00E0           | UAF31 | UAF30                                             | UAF29 | UAF28 | UAF27 | UAF26 | UAF25 | UAF24 | UAF23 | UAF22 | UAF21 | UAF20 | UAF19 | UAF18 | UAF17     | UAF16    | UAF15 | UAF14 | UAF13 | UAF12 | UAF11 | UAF10 | UAF9 | UAF8 | UAF7 | UAF6 | UAF5 | UAF4 | UAF3 | UAF2 | UAF1 | UAFO | AFR (0x0)                |

| 0x00E4           | RS    |                                                   |       |       |       |       |       |       |       |       |       |       |       |       |           | Reserved |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |                          |

| 0x00E8           | RS    | RSVD<br>RSVD FL[5:0] $\overrightarrow{B}$ RI[4:0] |       |       |       |       |       |       |       |       |       |       |       |       | FSR (0x0) |          |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |                          |

| 0x00EC           | RS    | VD                                                |       |       |       |       |       |       |       |       |       |       |       |       |           |          |       |       |       |       |       |       |      |      |      |      |      | RX   | FWN  | ۸[4: | 0]   |      | WMR<br>(0xF)             |

| 0x00F0           | RS    | VD                                                |       |       |       |       |       |       |       |       |       |       |       |       |           |          |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      | Reserved                 |

| 0x00F4           | RS    | RSVD                                              |       |       |       |       |       |       |       |       |       |       |       |       | Reserved  |          |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |                          |

| 0x00F8           | RS    | VD                                                |       |       |       |       |       |       |       |       |       |       |       |       |           |          |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      | Reserved                 |

| 0x00FC           | RS    | VD                                                |       |       |       |       |       |       |       |       |       |       |       |       |           |          |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      | Reserved                 |

### Software Reset Register (Address Offset + 0x0000)

Writing to the Software Reset Register (SRR) places the core in the Configuration mode. In Configuration mode, the core drives recessive on the bus line and does not transmit or receive messages. During power-up, CEN and SRST bits are 0 and the CONFIG bit in the Status Register (SR) is 1. The Transfer Layer Configuration Registers can be changed only when the CEN bit in the SRR is 0. Mode Select Register bits (except SLEEP and SBR) can be changed only when CEN bit is 0.

If the CEN bit is changed during core operation, Xilinx recommends resetting the core so that operation starts over.

Table 2-5: Software Reset Register

| Bits | Name     | Access | Default<br>Value | Description |

|------|----------|--------|------------------|-------------|

| 31:2 | Reserved | _      | 0                | Reserved    |

| Bits | Name | Access | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                                       |

|------|------|--------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | CEN  | R/W    | 0                | CAN Enable<br>The Enable bit for the core.<br>1 = core is in Loopback, Sleep, Snoop, or Normal mode depending on the<br>LBACK, SLEEP, and SNOOP bits in the MSR<br>0 = core is in the Configuration mode<br><b>Note:</b> If the CEN bit is cleared during core operation, Xilinx recommends resetting<br>the core so that operations starts over. |

| 0    | SRST | WO     | 0                | Reset<br>The software reset bit for the core.<br>1 = core is reset<br>If a 1 is written to this bit, all core configuration registers (including the<br>SRR) are reset. Reads to this bit always returns 0.<br><b>Note:</b> After performing soft or hard reset, wait for 16 AXI4 clock cycles before<br>initiating next AXI4-Lite transaction.   |

#### Table 2-5: Software Reset Register (Cont'd)

### Mode Select Register (Address Offset + 0x0004)

Writing to the Mode Select Register (MSR) enables the core to enter Snoop, Sleep, Loopback, or Normal modes. In Normal mode, the core participates in normal bus communication. If the SLEEP bit is set to 1, the core enters Sleep mode. If the LBACK bit is set to 1, the core enters Loopback mode. If the SNOOP mode is set to 1, the core enters Snoop mode and does not participate in bus communication but only receives messages.

**IMPORTANT:** LBACK, SLEEP, and SNOOP bits should never be set to 1 at the same time. At any given point, the core can either be in Loopback, Sleep, or Snoop mode. When all three bits are set to 0, the core can enter Normal mode subject to other conditions.

| Bits | Name     | Access | Default<br>Value | Description                                                                                                                                                                                                                                                     |

|------|----------|--------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | Reserved | -      | 0                | Reserved                                                                                                                                                                                                                                                        |

| 7    | ABR      | R/W    | 0                | Auto Bus-off Recovery Request<br>1 = auto bus-off recovery request<br>0 = no such request<br>If this bit is set, node does auto bus-off recovery irrespective of SBR bit<br>setting in this register.<br>This bit can be written only when CEN bit in SRR is 0. |

Table 2-6: Mode Select Register

#### Table 2-6: Mode Select Register (Cont'd)

| Bits | Name  | Access | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|-------|--------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6    | SBR   | R/W    | 0                | Start Bus-off Recovery Request<br>1 = start bus-off recovery request<br>0 = no such request<br>Node stays in bus-off state until SBR bit is set to 1 (provided ABR bit in<br>this register is not set).<br>This bit can be written only when node is in bus-off state.<br>This bit auto clears after node completes the bus-off recovery or leave<br>bus-off state due to hard/soft reset or CEN deassertion.                                                                                                                                                                                                                                                                                                                                                                                 |

| 5    | DPEE  | R/W    | 0                | Disable Protocol Exception Event Detection/Generation<br>1 = disable Protocol Exception Event detection/generation by CAN FD<br>receiver if "res" bit in CAN FD frame is detected as 1. In this case, CAN FD<br>receiver generates Form error.<br>0 = PEE detection/generation is enabled. If CAN FD receiver detects "res"<br>bit as 1, it goes to Bus Integration state (PEE_config) and waits for Bus Idle<br>condition (11 consecutive nominal recessive bits). Error counter remains<br>unchanged.<br>This bit can be written only when CEN bit in SRR is 0.                                                                                                                                                                                                                             |

| 4    | DAR   | R/W    | 0                | Disable Auto retransmission<br>1 = disable auto retransmission on CAN bus to provide single shot<br>transmission<br>0 = auto retransmission enabled<br>This bit can be written only when CEN bit in SRR is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3    | BRSD  | R/W    | 0                | CAN FD Bit Rate Switch Disable Override<br>1 = makes core transmit CAN FD frames only in nominal bit rate (by<br>overriding TX Message element BRS bit setting)<br>0 = makes core transmit CAN FD frames as per BRS bit in TX Message<br>element<br>This bit can be written only when CEN bit in SRR is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2    | SNOOP | R/W    | 0                | <ul> <li>SNOOP Mode Select/Request</li> <li>The Snoop mode request bit.</li> <li>1 = request core to be in Snoop mode</li> <li>0 = no such request</li> <li>This bit can be written only when CEN bit in SRR is 0.</li> <li>Make sure that Snoop mode is programmed only after system reset or software reset.</li> <li>For the core to enter Snoop mode, LBACK and SLEEP bits in this register should be set to 0.</li> <li>The features of Snoop mode are:</li> <li>Core transmits recessive bits on to CAN bus</li> <li>Receives messages that are transmitted by other nodes but does not ACK. Stores received messages in RX block RAM based on programmed ID filtering.</li> <li>Error counters are disabled and cleared to 0. Reads to error counter register returns zero.</li> </ul> |

| Bits | Name  | Access | Default<br>Value | Description                                                                                                                                                                                                                                                                                     |

|------|-------|--------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | LBACK | R/W    | 0                | Loopback Mode Select/Request<br>The Loopback mode request bit.<br>1 = request core to be in Loopback mode<br>0 = no such request<br>This bit can be written only when CEN bit in SRR is 0.<br>For the core to enter Loopback mode, SLEEP and SNOOP bits in this<br>register should be set to 0. |

| 0    | SLEEP | R/W    | 0                | Sleep Mode Select/Request<br>The Sleep mode request bit.<br>1 = request core to be in Sleep mode<br>0 = no such request<br>This bit is cleared when the core wakes up from the Sleep mode.<br>For core to enter Sleep mode, LBACK and SNOOP bits in this register<br>should be set to 0.        |

#### Table 2-6: Mode Select Register (Cont'd)

# Arbitration Phase (Nominal) Baud Rate Prescaler Register (Address Offset + 0x0008)

The CAN clock for the core is divided by (programmed prescaler value + 1) to generate the quantum clock needed for sampling and synchronization.

Table 2-7: Arbitration Phase Baud Rate Prescaler Register

| Bits | Name     | Access | Default<br>Value | Description                                                                                                                                                                                                                     |

|------|----------|--------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | Reserved | -      | 0                | Reserved                                                                                                                                                                                                                        |

| 7:0  | BRP[7:0] | R/W    | 0                | Arbitration Phase (Nominal) Baud Rate Prescaler<br>These bits indicate the prescaler value.<br>The actual value is one more than the value written to the register.<br>These bits can be written only when CEN bit in SRR is 0. |

### Arbitration Phase (Nominal) Bit Timing Register (Address Offset + 0x000C)

| Table 2-8: | Arbitration | Phase | Bit | Register |

|------------|-------------|-------|-----|----------|

|------------|-------------|-------|-----|----------|

| Bits  | Name     | Access | Default<br>Value | Description                                                                                                                                                                                                                                                        |

|-------|----------|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|