# CLK104 RF Clock Add-on Card

## **User Guide**

UG1437 (v1.1) August 25, 2022

Xilinx is creating an environment where employees, customers, and partners feel welcome and included. To that end, we're removing noninclusive language from our products and related collateral. We've launched an internal initiative to remove language that could exclude people or reinforce historical biases, including terms embedded in our software and IPs. You may still find examples of non-inclusive language in our older products as we work to make these changes and align with evolving industry standards. Follow this <u>link</u> for more information.

# Table of Contents

| Chapter 1: Introduction                                    | 4  |

|------------------------------------------------------------|----|

| •<br>Overview                                              |    |

| Module Features                                            |    |

| Block Diagram                                              |    |

| Module Specifications                                      |    |

| Chapter 2: Setup and Configuration                         | 8  |

| Component Location                                         |    |

| PLL Mode Configuration                                     |    |

| PLL Loop Filters and Parameters                            |    |

| Appendix A: SAMTEC LPAM Host Interface Connector           | 16 |

| Appendix B: CLK104 RF Clock Add-on Card Configuration with |    |

| the ZCU216 SCUI                                            | 18 |

| Appendix C: CLK104 RF Clock Add-on Card Configuration with |    |

| the ZCU216 APU                                             | 21 |

| Appendix D: Additional Resources and Legal Notices         | 22 |

| Xilinx Resources                                           |    |

| Documentation Navigator and Design Hubs                    |    |

| References                           | 22 |

|--------------------------------------|----|

| Revision History                     | 23 |

| Please Read: Important Legal Notices |    |

# AMDA XILINX

## Chapter 1

## Introduction

## Overview

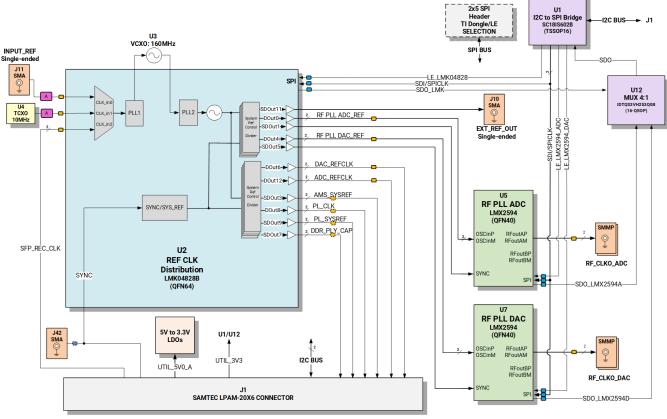

The CLK104 RF clock add-on card is designed for use with Zynq<sup>®</sup> UltraScale+<sup>™</sup> RFSoC Gen3 ZCU216 and ZCU208 evaluation boards. It provides an ultra low-noise, wideband RF clock source for the analog-to-digital and digital-to-ananlog converters (ADCs and DACs).

The clock distribution PLL provides the low frequency reference clock for integrated PLL of RFSoC devices. RFSoC devices accept one RF sampling clock for all ADC channels and one RF sampling clock for all DAC channels. ADCs and DACs have dedicated RF PLLs physically located close to them. The CLK104 supports multi-tile and multi-board synchronization.

### **Module Features**

The CLK104 provides the following features:

- On-module dedicated low noise LDO regulators supply 3.3V power to the GP PLL and RF PLLs.

- I2C serial interface

- TI USB2ANY interface (customized adapter/cable is required)

- LEDs indicate lock status of GP PLL and RF PLLs

- Programmable tracking on-module TCXO clock (10 MHz), or an external reference clock through SMA or a recovered clock from the PL bank

- Clock distribution PLL reference clock options

- External reference clock

- Single-ended clock through SMA connector

- 3 dB attenuation

- AC coupled

- Free running on-module reference clock

- 10.0 MHz TCXO

- Manual mute option

- Recovered clock

- Differential clock through interface connector

- Routed to RFSoC PL bank on evaluation board

- Clock distribution PLL output clock options

- 。 ADC RF PLL and DAC RF PLL differential reference clock signals (two pairs)

- Two single-ended SYNC signals for the ADC RF PLL and DAC RF PLL

- 。 RFSoC ADC and DAC differential reference clock signals (two pairs)

- 。 SYSREF differential clock signal (one pair)

- 。 RFSoC differential clocks for PL banks (three pairs)

- Single-ended external reference clock to SMA connector

- RF clock options

- 。 ADC RF clocks (two pairs)

- Programmable to any frequency up to 10 GHz

- Programmable output power level, typical > 4 dBm

- Phase noise performance: -131 dBc/Hz at 1 MHz offset with 4 GHz carrier

- 。 DAC clock options (two pairs)

- Programmable to any frequency up to 10 GHz

- Programmable output power level, typical > 4 dBm

- Phase noise performance: -124 dBc/Hz at 1 MHz offset with 10 GHz carrier

## **Block Diagram**

XILINX

The block diagram for the CLK104 is shown in the following figure.

Figure 1: CLK104 RF Clock Add-on Card Block Diagram

X27001-082422

## **Module Specifications**

Specifications for the CLK104 RF clock add-on card are as follows:

- Dimensions

- Height: 2.0 inches (50.8 cm)

- 。 Width: 8.0 inches (203.2 cm)

- Thickness: 0.068 inches (0.173 cm)

- Environmental

- 。 Temperature

- Operating: 0°C to +45°C

- Storage: -25°C to +60°C

- Humidity: 10% to 90% non-condensing

## Chapter 2

# Setup and Configuration

## **Component Location**

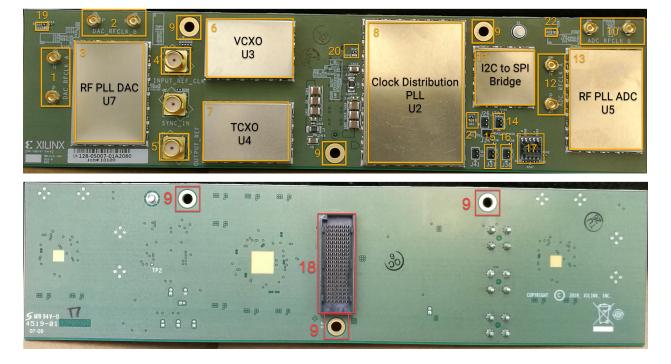

The following figure shows the CLK104 RF clock add-on card and its components. Each numbered component referenced in the figure is described in the table and sections that follow.

**CAUTION!** The CLK104 add-on card must be secured to the evaluation board with three screws before <sup>1</sup> operation. The mounting holes are shown in the figure.

**IMPORTANT!** The figure is for reference only and might not reflect the current revision of the board.

#### Figure 2: CLK104 Component Locations

| Table 1: CLK104 Component Locations (Bac | k) |

|------------------------------------------|----|

|------------------------------------------|----|

| Callout | Reference<br>Designation | Description                                                         |

|---------|--------------------------|---------------------------------------------------------------------|

| 1       | J20, J21                 | DAC_RFCLK_A, DAC RF PLL output A                                    |

| 2       | J31, J32                 | DAC_RFCLK_B, DAC RF PLL output B                                    |

| 3       | U7                       | RF PLL for DAC (LMX2594) with RF cage                               |

| 4       | J11                      | INPUT_REF_CLK, (U2 external reference clock)                        |

| 5       | J10                      | OUTPUT_REF (U2 output reference clock)                              |

| 6       | U3                       | VCXO 160.00MHz, VX-501-0245-160M0                                   |

| 7       | U4                       | TCXO 10.0MHz, DOT050F-010.0M                                        |

| 8       | U2                       | Clock distribution PLL (LMK04828B) with RF cage                     |

| 9       | MH1, MH2, MH3            | Mounting holes                                                      |

| 10      | J29, J30                 | ADC_RFCLK_B, ADC RF PLL output B                                    |

| 11      | U1, U12                  | I2C to SPI bridge and multiplexer                                   |

| 12      | J27, J28                 | ADC_RFCLK_A, ADC RF PLL output A                                    |

| 13      | U5                       | RF PLL for ADC (LMX2594) with RF cage                               |

| 14      | J38*                     | LE_LMK04828 selection, NPB02SVAN-RC                                 |

| 15      | J37*                     | LE_2594_DAC selection, NPB02SVAN-RC                                 |

| 16      | J36*                     | LE_2594_ADC selection, NPB02SVAN-RC                                 |

| 17      | J33*                     | TI USB2ANY interface connector (customized adapter/cables required) |

| 18      | J1                       | Host interface connector (LPAM-20-01.0-L-06-2-K-TR)                 |

| 19      | DS3                      | U7 PLL lock LED (DAC RF PLL)                                        |

| 20      | DS4                      | 5.0V power supply LED                                               |

| 21      | DS1                      | U2 PLL lock LED (clock distribution PLL)                            |

| 22      | DS2                      | U5 PLL lock LED (ADC RF PLL)                                        |

*Note:* J38, J37, J36, and J33 headers are only needed for use with the USB2ANY interface. If using I2C programming, shunts are not required.

## **PLL Mode Configuration**

#### LMK04828B

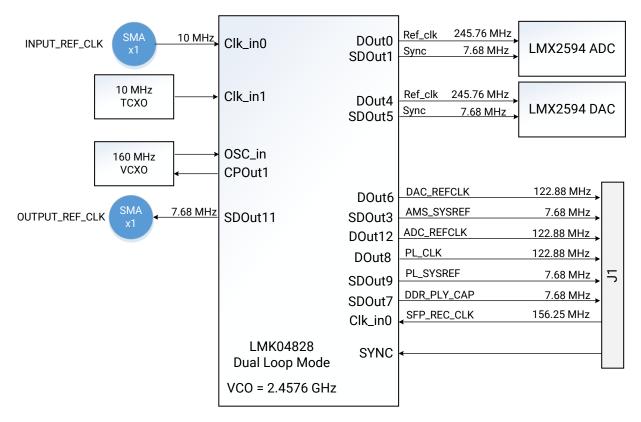

LMK04828B (U2) is a dual loop jitter cleaner and clock generator. The first stage PLL (PLL1) is driven by either an external reference clock, the on-module TCXO reference clock (10.0 MHz), or the recovered reference clock from the RFSoC. An external 160.00 MHz VCXO provides a frequency-accurate, low-phase noise reference clock for the second stage PLL (PLL2). PLL2 operates with a wide-loop bandwidth and generates the input references and SYNC signal for the ADC/DAC RF PLLs (U5 and U7), the PLL reference clocks, the SYSREF signal for the RFSoC ADC/DAC, the reference clocks for the RFSoC PL banks, and the output reference clock for multi-tile and multi-board synchronization.

U2 can be configured in dual-loop mode if synchronization is not required between the outputs and reference input. If it is configured in nested 0-delay mode, either DCLKout6 or DCLKout8 needs to be selected by the feedback multiplexer, as it establishes a fixed deterministic phase relationship of the phase of PLL1 input reference to the phase of outputs. DCLKoutX can be driven from either the internal VCO or the output divider. The internal PLL2 VCO frequency range is 2,370 to 2,630 MHz and 2,920 to 3,080 MHz. Each DCLKoutX has a single clock output divider (from 2 to 32). The output of this divider can also be directed to SDCLKoutY, where Y=X +1. SDCLKoutY can be driven from either output divider or a common SYSREF divider (from 8 to 8,191).

The following figure shows an example of a typical LMK04828B configuration. Note that no external cables are required.

#### Figure 3: LMK04828B (U2) Configuration Example

X23689-021020

#### LMX2594

LMX2594 ADC (U5) and LMX2594 DAC (U7) provide dedicated RF PLLs for the RFSoC ADC RFSoC DAC. RF output port A is usually the main RF output, and uses the Carlisle SSMP loopback cable (TM40-0153) to connect it to the RF sampling clock connector on the RFSoC EVM. The following figure shows the RF clock connections between the CLK104 and the ZCU216.

#### *Figure 4:* **RF Clock Connections using SSMP Loopback Cables**

As a part of frequency planning, you need to select the proper input frequency for the LMX2594. If possible, use the integer mode as it is preferred to avoid fractional spurs. For example, for a 3.93216 GHz output, select the input frequency at 245.76 MHz. For an 8 GHz output, select the input frequency at 300.00 MHz. New configuration designs should be assessed on the spectrum analyzer before use.

## **PLL Loop Filters and Parameters**

#### LMK04828B

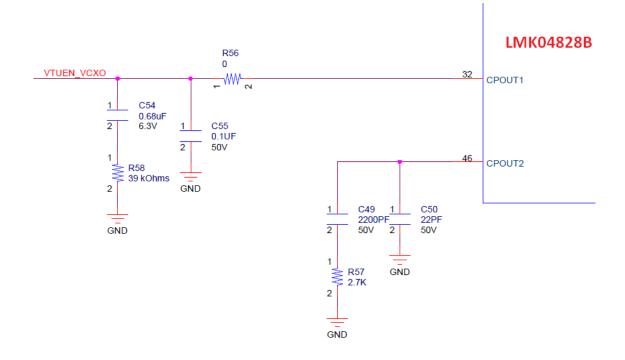

The following figure shows the external loop filter design for LMK04828B (U2) PLL1 and PLL2.

The following two tables identify typical U2 loop filter configurations for PLL1 in both dual-loop and nested 0-delay modes.

| Table 2: Typical U2 PLL1 Loop Filte | r Configuration in Dual-Loop Mode |

|-------------------------------------|-----------------------------------|

|-------------------------------------|-----------------------------------|

| Parameter                      | Value    |

|--------------------------------|----------|

| VCO Gain                       | 8 KHz/V  |

| Loop Bandwidth                 | 29 Hz    |

| Phase Margin                   | 46 deg   |

| C55 (C1_LF)                    | 100 nF   |

| C54 (C2_LF)                    | 680 nF   |

| R58 (R2_LF)                    | 39 ΚΩ    |

| Effective Charge Pump Gain     | 150 uA   |

| Phase Detector Frequency (MHz) | 1.25 MHz |

| External VCXO Frequency        | 160 MHz  |

| Parameter                      | Value    |

|--------------------------------|----------|

| VCO Gain                       | 8 KHz/V  |

| Loop Bandwidth                 | 21 Hz    |

| Phase Margin                   | 50 deg   |

| C55 (C1_LF)                    | 100 nF   |

| C54 (C2_LF)                    | 680 nF   |

| R58 (R2_LF)                    | 39 ΚΩ    |

| Effective Charge Pump Gain     | 1,050 uA |

| Phase Detector Frequency (MHz) | 0.08 MHz |

| External VCXO Frequency        | 160 MHz  |

#### Table 3: Typical U2 PLL1 Loop Filter Configuration in Nested 0-Delay Mode

The following table identifies a typical U2 loop filter configuration for PLL2.

#### Table 4: Typical U2 PLL2 Loop Filter Configuration

| Parameter                      | Value       |

|--------------------------------|-------------|

| VCO Gain                       | 21 MHz/V    |

| Loop Bandwidth                 | 79 KHz      |

| Phase Margin                   | 68 deg      |

| C50 (C1_LF)                    | 22 pF       |

| C49 (C2_LF)                    | 2,200 pF    |

| R57 (R2_LF)                    | 2.7 ΚΩ      |

| Internal Loop Filter R3        | 200 Ω       |

| Internal Loop Filter C3        | 10 pF       |

| Internal Loop Filter R4        | 200 Ω       |

| Internal Loop Filter C4        | 10 pF       |

| Effective Charge Pump Gain     | 3,200 uA    |

| Phase Detector Frequency (MHz) | 6.4 MHz     |

| VCXO Frequency                 | 2,457.6 MHz |

#### LMX2594

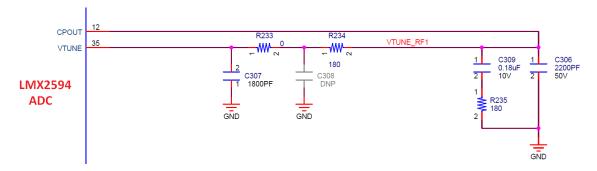

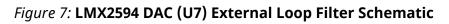

The following figures show the external loop filter design for LMX2594 ADC (U5) and DAC (U7).

Figure 6: LMX2594 ADC (U5) External Loop Filter Schematic

The following table identifies a typical LMX2594 loop filter configuration.

| Parameter                      | Value                                                         |

|--------------------------------|---------------------------------------------------------------|

| VCO Gain                       | 239 MHz/V                                                     |

| Loop Bandwidth                 | 32.7 kHz                                                      |

| Phase Margin                   | 69 deg                                                        |

| C306, C319 (C1_LF)             | 2200 pF                                                       |

| C309, C318 (C2_LF)             | 180 nF                                                        |

| C307, C320 (R2_LF)             | 1800 pF                                                       |

| R235, R241 (R2)                | 180 Ω                                                         |

| R234, R240 (R3_LF)             | 180 Ω                                                         |

| Effective Charge Pump Gain     | 3 mA                                                          |

| Phase Detector Frequency (MHz) | 24.576 MHz                                                    |

| VCXO Frequency                 | Designed for 15 GHz, but works over the whole frequency range |

## Appendix A

# AMD7 XILINX

## SAMTEC LPAM Host Interface Connector

The CLK104 RF clock add-on card mates with RFSoC evaluation boards using a low profile, 120pin, high-speed SAMTEC LPA connector. The following figure shows the mezzanine module connector pin-out and the table that follows identifies the pins.

|   | 1 | 2     | 3      | 4 | 5         | 6          | 7 | 8     | 9       | 10 | 11 | 12   | 13    | 14 | 15     | 16     | 17 | 18     | 19     | 20 |

|---|---|-------|--------|---|-----------|------------|---|-------|---------|----|----|------|-------|----|--------|--------|----|--------|--------|----|

| A | G | G     | G      | G | G         | G          | G | G     | G       | G  | G  | G    | G     | G  | G      | G      | G  | G      | G      | G  |

| В | G | ADC_F | REFCLK | G | CLK_SPI_M | IUX_SEL0/1 | G | AMS_I | REFCLK  | G  | G  | PL_S | YSREF | G  | PL_    | CLK    | G  | DDL_PL | Y_SYNC | G  |

| с | G | G     | G      | G | G         | G          | G | G     | G       | G  | G  | G    | G     | G  | G      | G      | G  | G      | G      | G  |

| D | G | G     | G      | G | 3V3       | 3V3        | G | G     | G       | G  | G  | 5V0  | 5V0   | G  | G      | G      | G  | G      | G      | G  |

| E | G | DAC_F | REFCLK | G | 3V3       | 3V3        | G |       | SYNC_IN | G  | G  | 5V0  | 5V0   | G  | SFP_RI | EC_CLK | G  | SCLK   | SDA    | G  |

| F | G | G     | G      | G | G         | G          | G | G     | G       | G  | G  | G    | G     | G  | G      | G      | G  | G      | G      | G  |

#### Figure 8: LPA Connector Pin-out

#### Table 6: LPA Connector Pin Descriptions

| Pin | Signal Name        | Description                                           | LMK04828 Pin |  |

|-----|--------------------|-------------------------------------------------------|--------------|--|

| E2  | DAC_REFCLK_P       | DAC REFCLK, routed to RFSoC DAC on board              | DCLKout6*    |  |

| E3  | DAC_REFCLK_N       | DAC REFELR, TOULED TO RESOL DAC ON BOARD              | DCLKOUL6*    |  |

| B2  | ADC_REFCLK_P       | ADC REFCLK, routed to RFSoC ADC on board              | DCLKout12*   |  |

| B3  | ADC_REFCLK_N       | ADC REFELK, FOULED TO RESOL ADC ON BOARD              | DCLKOUL12*   |  |

| B8  | AMS_SYSREF_P       | AMS SYSDEF routed to DESpC SYSDEF on board            | SDCLKout3*   |  |

| B9  | AMS_SYSREF_N       | AMS SYSREF, routed to RFSoC SYSREF on board           | SDCLROULS"   |  |

| B15 | PL_CLK_P           | PL CLK, routed to PL bank on board                    | DCLKout8*    |  |

| B16 | PL_CLK_N           | PECER, TOULED TO PE Dank of Doard                     | DCLKOUI8"    |  |

| B12 | PL_SYSREF_P        | PL SYSREF, routed to PL bank on board                 | SDCLKout9*   |  |

| B13 | PL_SYSREF_N        | PL_STSKEF, TOULED TO PL DAIR OF DOALD                 | SDCEROUL9"   |  |

| B18 | DDR_PLY_CAP_SYNC_P | DDR Playback/Capture Sync, routed to PL bank on board | SDCLKout7*   |  |

| B19 | DDR_PLY_CAP_SYNC_N | Dornayback/ capture Sync, routed to FE bank of board  | SUCLKOUT/*   |  |

#### Table 6: LPA Connector Pin Descriptions (cont'd)

| Pin | Signal Name      | Description                            | LMK04828 Pin |

|-----|------------------|----------------------------------------|--------------|

| E15 | SFP_REC_CLK_P    | Recovered clock from RFSoC PL banks    | CLKin0       |

| E16 | SFP_REC_CLK_N    |                                        |              |

| E9  | SYNC_IN          | SYNC signal routed to PL bank on board | SYNC         |

| E18 | CLK104_SCL       | I2C bus SCL                            |              |

| E19 | CLK104_SDA       | I2C bus SDA                            |              |

| B5  | CLK_SPI_MUX_SEL0 | PLL SPI MUX SEL0                       |              |

| B6  | CLK_SPI_MUX_SEL1 | PLL SPI MUX SELO                       |              |

*Note:* The output frequency, power level, and enable/disable of each LMK04828B output are subject to change as determined by the configuration files.

# AMDA XILINX

## Appendix B

## CLK104 RF Clock Add-on Card Configuration with the ZCU216 SCUI

#### **Clock Configuration Files**

The PLL configuration files are included with the ZCU216 SCUI. New PLL configuration files can be added to the corresponding clock files folder before launching the SCUI as shown in the following screen capture.

| Name ^      | Date modified    | Туре           | Size |

|-------------|------------------|----------------|------|

| 8a34001     | 12/18/2019 11:19 | File folder    |      |

| Imk04828    | 12/18/2019 11:19 | File folder    |      |

| Imx2594_adc | 12/18/2019 11:19 | File folder    |      |

| Imx2594_dac | 12/18/2019 11:19 | File folder    |      |

| si5341      | 12/18/2019 11:19 | File folder    |      |

| gitignore   | 12/18/2019 11:47 | GITIGNORE File | 1 KB |

| Revision    | 12/18/2019 11:47 | Text Document  | 1 KB |

The naming convention of the LMK04828B (U2) configuration files are as follows:

#### • Example:

LMK04828B\_BxxxxMx\_DualLoop\_C0in10M\_C1in10M\_C2in156M25\_DATECODE.txt

- 。 BxxxxMx: PLL2 internal VCO frequency

- $_{\circ}$  DualLoop or Nested: LMK mode

- C0in\_xxM: CinO input reference frequency

- Clin\_yyM: Cin1 input reference frequency

- C2inzzMzz: Cin2 input reference frequency

The naming convention of the LMK2594 ADC/DAC RF PLL (U5/U7) configuration files are as follows:

- Example: LMX2594\_REF-xxxMxx\_\_OUT-xxxxMxx\_DATECODE.txt

- REF-xxxMxx: Expected input reference frequency

- OUT-xxxxMxx: RF output frequency

Send Feedback

*Note*: PLL configuration files that do not follow the naming conventions do not affect the configuration content, but will result in incorrect information in the SCUI.

#### **Configuring Clock PLLs**

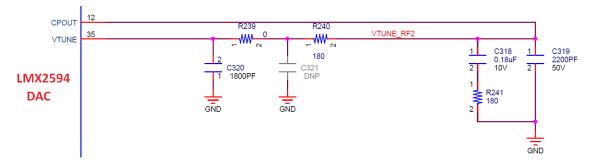

Proceed as follows to configure the clock PLLs:

1. From the \BoardUI\ working directory, double-click BoardUI.exe. The following is displayed:

| Enter Board Information |                       |   |

|-------------------------|-----------------------|---|

| Board:                  | ZCU216                | ~ |

| Revision:               | REV_A02               | ~ |

| Silicon:                | prod                  | ~ |

| Mode:                   | default               | ~ |

| Serial Number:          | 0500301 <b>A</b> 2024 | ~ |

| MAC Address:            | 01:02:03:04:05:06     |   |

|                         | OK                    |   |

- 2. Click OK.

- 3. Select the System\_Controller tab, then the Clocks tab, followed by the CLK-104 tab.

- 4. Select the expected clock file from the pull-down menu adjacent to the *Set LMK04828 Params* button. Click **Set LMK04828 Params** button and wait until the DS1 LED illuminates (green).

- 5. Select the expected clock file from the pull-down menu adjacent to the *Set LMX2594 ADC freq* button. Click **Set LMX2594 ADC freq** button and wait until the DS2 LED illuminates (green).

- 6. Select the expected clock file from the pull-down menu adjacent to the *Set LMX2594 DAC freq* button. Click **LMX2594 DAC freq** button and wait until the DS2 LED illuminates (green).

Appendix C

## CLK104 RF Clock Add-on Card Configuration with the ZCU216 APU

The CLK104 RF clock add-on card can be programmed and controlled by the RFCLK driver implemented in the Linux/baremetal application of the APU on the ZCU216 evaluation board. This excludes the external programming dongle. An example demonstrating how the RFCLK driver can control the CLK104 is provided in the Zynq<sup>®</sup> UltraScale+<sup>™</sup> RFSoC RF data converter evaluation tool (see *Zynq UltraScale+ RFSoC ZCU208 and ZCU216 RF Data Converter Evaluation Tool User Guide* (UG1433)). The example code with a simple application that controls the CLK104 is available at: https://github.com/Xilinx/embeddedsw/tree/master/XilinxProcessorIPLib/drivers/board\_common/src/rfclk.

## Appendix D

## Additional Resources and Legal Notices

## **Xilinx Resources**

For support resources such as Answers, Documentation, Downloads, and Forums, see Xilinx Support.

## **Documentation Navigator and Design Hubs**

Xilinx<sup>®</sup> Documentation Navigator (DocNav) provides access to Xilinx documents, videos, and support resources, which you can filter and search to find information. To open DocNav:

- From the Vivado<sup>®</sup> IDE, select Help → Documentation and Tutorials.

- On Windows, select Start → All Programs → Xilinx Design Tools → DocNav.

- At the Linux command prompt, enter docnav.

Xilinx Design Hubs provide links to documentation organized by design tasks and other topics, which you can use to learn key concepts and address frequently asked questions. To access the Design Hubs:

- In DocNav, click the **Design Hubs View** tab.

- On the Xilinx website, see the Design Hubs page.

*Note*: For more information on DocNav, see the Documentation Navigator page on the Xilinx website.

## References

These documents provide supplemental material useful with this guide:

- 1. ZCU208 Evaluation Board User Guide (UG1410)

- 2. ZCU216 Evaluation Board User Guide (UG1390)

These websites provide supplemental material useful with this guide:

- 1. Texas Instruments: https://www.ti.com/

- 2. Carlisle Interconnect Technologies: https://www.carlisleit.com/

## **Revision History**

The following table shows the revision history for this document.

| Section                                                                   | Revision Summary            |  |  |  |

|---------------------------------------------------------------------------|-----------------------------|--|--|--|

| 08/25/2022 Version 1.1                                                    |                             |  |  |  |

| Appendix C: CLK104 RF Clock Add-on Card Configuration with the ZCU216 APU | Added link to example code. |  |  |  |

| 03/19/2020 Version 1.0                                                    |                             |  |  |  |

| Initial release.                                                          | N/A                         |  |  |  |

## **Please Read: Important Legal Notices**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials

without prior written consent. Certain products are subject to the terms and conditions of Xilinx's limited warranty, please refer to Xilinx's Terms of Sale which can be viewed at https://www.xilinx.com/legal.htm#tos; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in such critical applications, please refer to Xilinx's Terms of Sale which can be viewed at https://www.xilinx.com/legal.htm#tos.

#### Copyright

© Copyright 2020-2022 Xilinx, Inc. Xilinx, the Xilinx logo, Alveo, Artix, Kintex, Kria, Spartan, Versal, Vitis, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.