# ZC706 PCIe Targeted Reference Design

# User Guide

**Vivado Design Suite**

UG963 (v2015.4) January 19, 2016

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials without prior written consent. Certain products are subject to the terms and conditions of Xilinx's limited warranty, please refer to Xilinx's Terms of Sale which can be viewed at <a href="http://www.xilinx.com/legal.htm#tos">http://www.xilinx.com/legal.htm#tos</a>; IP cores may be fail-safe performance; you assume sole risk and liability for use of Xilinx products in such critical applications, please refer to Xilinx's Terms of Sale which can be viewed at <a href="http://www.xilinx.com/legal.htm#tos">http://www.xilinx.com/legal.htm#tos</a>.

#### **Automotive Applications Disclaimer**

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

© Copyright 2012–2016 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight, Cortex, and PrimeCell are trademarks of ARM in the EU and other countries. PCI, PCIe, and PCI Express are trademarks of PCI-SIG and used under license. HDMI, HDMI logo, and High-Definition Multimedia Interface are trademarks of HDMI Licensing LLC. All other trademarks are the property of their respective owners.

# **Revision History**

The following table shows the revision history for this document.

| Date                                        | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|---------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 11/15/2012                                  | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 01/08/2013 2.0 Updated for ISE Design Suite |         | Updated for ISE Design Suite v14.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 05/14/2013                                  | 3.0     | Updated for ISE Design Suite v14.5. Replaced all references to<br>zynq_pcie_trd_14_3.zip with zc706-pcie-trd-rdf0287.zip through<br>document. Updated Figure 2-10 and Figure 2-11 screen captures.                                                                                                                                                                                                                                                                                                                                        |  |

| 02/28/2014                                  | 4.0     | Updated for ISE Design Suite v14.7. Deleted Chapter 2, <i>Getting Started</i> . Updated<br>Table 2-1. Updated Data Path Components. Updated Figure 2-9 and added<br>Figure 2-13. Updated Figure 2-13 and added Figure 2-13 and Table 2-5. Added<br>Appendix D, PetaLinux Software Development Kit.                                                                                                                                                                                                                                        |  |

| 03/12/2015                                  | 2014.3  | Updated for Vivado Design Suite 2014.3. Updated Processing System in Chapter 2.<br>Deleted Appendix A "Setting Up Board Communications". Added Sobel Filter<br>Registers to Appendix C, Register Description. Updated Appendix B, Extended<br>Display Identification Data and Appendix E, PetaLinux Software Development Kit.<br>Added Appendix F, Install the Zynq-7000 AP SoC Design and Development<br>Environment. and Appendix H, Regulatory and Compliance Information. Added<br>Appendix H, Regulatory and Compliance Information. |  |

| Date       | Version | Revision                                                                              |

|------------|---------|---------------------------------------------------------------------------------------|

| 03/13/2015 | 2014.4  | No content change for Vivado Design Suite 2014.4 other than document revision number. |

| 01/19/2016 | 2015.4  | No content change for Vivado Design Suite 2015.4 other than document revision number. |

# **Table of Contents**

| Revision History                                                        | 2   |

|-------------------------------------------------------------------------|-----|

| Chapter 1: Introduction                                                 |     |

| TRD Components                                                          | . 8 |

| Data Flow                                                               | . 9 |

| Resource Utilization                                                    | 10  |

| Chapter 2: Functional Description                                       |     |

| Hardware Architecture                                                   | 11  |

| Chapter 3: Performance Estimation                                       |     |

| Theoretical Estimate                                                    | 50  |

| Measuring PCIe Performance                                              | 52  |

| Measuring HP Port Performance                                           | 53  |

| Performance Observations                                                | 53  |

| Chapter 4: Designing with the Targeted Reference Design Platform        |     |

| PCIe Host System Software Modifications                                 | 55  |

| Appendix A: Setting Up Board Communications                             |     |

| Appendix B: Extended Display Identification Data                        |     |

| Storing and Programming EDID data                                       | 61  |

| Appendix C: Register Description                                        |     |

| Sobel Filter Registers                                                  | 62  |

| PCie DMA Registers                                                      | 71  |

| Host Software Common Registers                                          | 73  |

| User Space Registers                                                    | 74  |

| Demonstration Mode: Video Path                                          | 77  |

| Demonstration Mode: Generator/Checker/Loopback Registers for User APP 1 | 78  |

| Host and PS Communication Registers                                     | 79  |

### **E** XILINX.

### Appendix D: Troubleshooting

### Appendix E: PetaLinux Software Development Kit

| Appendix F: Install the Zynq-7000 AP SoC Design and Development Environmen | It |

|----------------------------------------------------------------------------|----|

| Install the Xilinx Vivado Design Suite                                     | 3  |

| Appendix G: Additional Resources                                           |    |

| Xilinx Resources                                                           | 4  |

| Solution Centers                                                           | 4  |

| References                                                                 | 4  |

# **XILINX**<sub>®</sub>

# Chapter 1

# Introduction

This chapter introduces the Zynq<sup>™</sup>-7000 PCIe® Targeted Reference Design (TRD), summarizes its modes of operation, and lists the TRD features.

The overall design is a video processing card that demonstrates these capabilities:

- PCIe connectivity:

- Use of the Zynq-7000 XC7Z045 AP SoC PCIe Endpoint block in x4 Gen2 configuration

- PCIe bus-compatible high performance low latency multichannel DMA

- Performance demonstration using a traffic generator and checker running in Programmable logic (PL) and host software containing a PCIe root port

- Cortex-A9 processing and offload:

- The use of a XC7Z045 AP SoC to offload and process video data

- The use of a Sobel filter in PL

- HDMI-based display controller

- Cortex-A9 multiprocessing core in the XC7Z045 AP SoC used as a video data coprocessor

- An example design showing independent memory management in the host system and the Zynq-7000 Processing System (PS)

The Zynq-7000 PCIe TRD demonstrates the operation of:

- PCIe Endpoint block (x4 Gen2)

- High-speed GTX transceivers

- High-speed multichannel DMA interface to a PCIe Endpoint

- Zynq-7000 PS

- Video DMA (VDMA) and Sobel filtering

- HDMI-based display controller

### **E** XILINX。

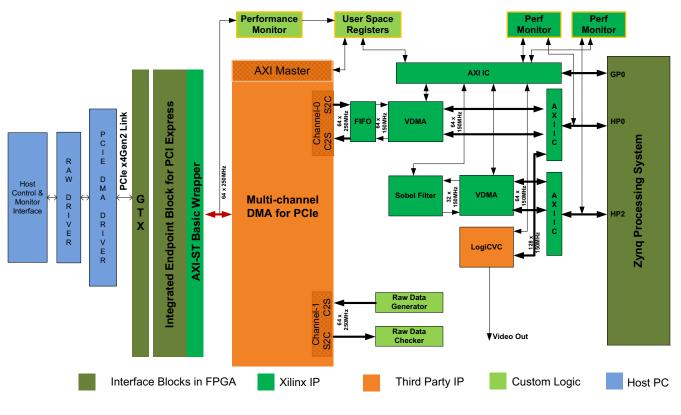

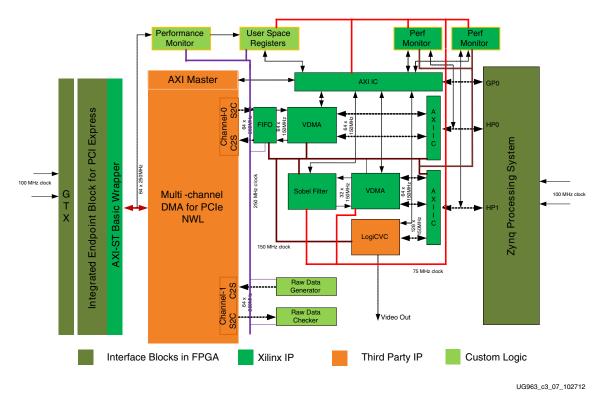

#### Figure 1-1 depicts the block diagram of the Zynq-7000 PCIe TRD.

UG963\_c1\_01\_103112

Figure 1-1: Zynq-7000 PCIe Targeted Reference Design Block Diagram

The Zynq-7000 PCIe TRD expands the Zynq-7000 Base Targeted Reference Design described in the Zynq-7000 All Programmable SoC ZC702 Base Targeted Reference Design User Guide (UG925) [Ref 1] by adding PCI Express® communication with a host system communicating at x4 Gen2 speed. In the Zynq-7000 Base TRD, the video processing pipeline input is provided by a test pattern generator in the PL. In the Zynq-7000 PCIe TRD, the video processing pipeline input is provided by an application running on the host computer at 1080p60 resolution and transmitted to the ZC706 board over the PCIe bus. The data is processed by video pipeline and passed back to the host system over the PCIe bus.

Because the full 1080p60 video stream uses about 4 Gb/s bandwidth, an additional data generator and a checker are implemented and connected to channel 1 of PCIe DMA to demonstrate the maximum x4 Gen2 bandwidth achieved by the hardware.

# **TRD Components**

The Zynq-7000 PCIe TRD features these components:

- PCI Express v2.1 compliant x4 Endpoint block operating at 5 Gb/s per lane, both directions:

- PCIe transaction interface utilization engine

- MSI and legacy interrupt support

- Bus mastering scatter-gather PCIe DMA to offload host processor:

- Multi-channel DMA

- AXI4 streaming interface for data

- AXI4 interface for register space access

- DMA performance engine

- Full duplex operation:

- Independent transmit and receive channels

- Multichannel video DMA with programmable VSIZE and HSIZE:

- AXI4 compliant

- Optional flush on frame sync

- Optional frame advancement on error

- Multilayer display controller:

- Alpha blending, transparency and move-around support

- Continuous switching mode support

- Sobel filter:

- AXI4 stream interface

- AXI4 control interface

- Supports image resolution up to 1080p

- Java-based GUI running on the PCIe host system:

- Test control panel

- PCIe performance monitoring

- A Qt-based GUI running in the PS:

- Monitors power and die temperature

- PS HP0 and HP2 performance numbers

- CPU utilization

Table 1-1 lists some terminology used in the document.

| Design Block Used in the TRD                                | Name             |

|-------------------------------------------------------------|------------------|

| PCIe DMA                                                    | NWL DMA          |

| Video DMA interfacing to the FIFO in the NWL DMA, channel 0 | SOURCE VDMA      |

| Video DMA interfacing to the Sobel filter                   | FILTER VDMA      |

| Host system with PCIe slot                                  | PCIe Host system |

| Control PC to monitor UART output                           | Control PC       |

# Data Flow

The Zynq-7000 PCIe TRD demonstrates the use of the XC7Z045 AP SoC to offload video processing tasks from a PCIe host system.

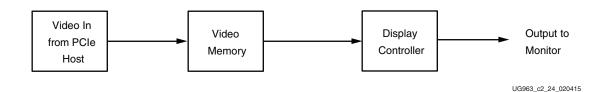

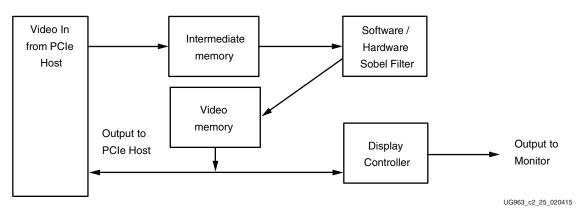

## Video Processing and Offload Demonstration on PCIe DMA Channel 0

The user application in the PCIe host system generates 1920 x 1080 pixel video frames. The PCIe host system software manages channel 0 of the PCIe DMA to transmit the video stream over a x4 Gen2 PCIe link to the ZC706 board. A PCIe DMA translates the stream of PCIe video data packets into AXI streaming data, which is connected to a Video DMA (VDMA). Software running in the PS on the Cortex-A9 processor manages the AXI VDMA and transfers the raw video frames into the PS DDR3 memory. The hardware-based Sobel filter reads the image using another VDMA and performs edge detection on the raw image and sends the data back to the PS DDR3. The processed data in PS DDR3 can either be transferred back to the host system using channel 0 of the card-to-system (C2S) interface of the PCIe DMA or be displayed on the monitor using the LogiCVC display controller. Due to the limitation of the PS DDR3 bandwidth, the same data cannot be displayed and sent back to the host system simultaneously.

# **Generator and Checker Demonstration on PCIe DMA Channel 1**

A generator and checker on channel 1 of the PCIe DMA allows the RX and TX paths to run independently. The hardware generator in the PL generates data packets with an incremental sequence pattern. The PCIe host system software checker verifies the incremental sequence pattern generated by the hardware generator. Independently, the PCIe host system driver generates a stream of incremental data which is transferred via the PCIe link by the NWL PCIe DMA to the checker implemented in the PL.

# **Resource Utilization**

*Note:* Device resource utilization results are indicative and are dependent on the implementation tool version. Exact results might vary.

Table 1-2: Resource Utilization

| Resource        | Total Available | Usage        |

|-----------------|-----------------|--------------|

| Slice Registers | 437,200         | 49,425 (11%) |

| Slice LUT       | 218,600         | 38,502 (17%) |

| RAMB36E1        | 545             | 61 (11%)     |

| MMCME2_ADV      | 8               | 2 (25%)      |

| BUFG/BUFGCTRL   | 32              | 10 (31%)     |

| XADC            | 1               | 1 (100%)     |

| IOB             | 362             | 26 (7%)      |

| GTXE2_CHANNEL   | 16              | 4 (25%)      |

| GTXE2_COMMON    | 4               | 1 (25%)      |

Building hardware is explained in the Zynq-7000 PCIe Targeted Reference Design wiki page at <u>http://wiki.xilinx.com/zynq-pcie-trd</u>.

# Chapter 2

# **Functional Description**

This chapter describes the hardware and software architecture.

# **Hardware Architecture**

The hardware design architecture is described under two sections:

- Processing System (PS)

- Programmable Logic (PL)

The NWL DMA and the video pipe are implemented in the PL. The following sections detail the implementation of the PS and PL blocks.

### **Processing System**

The Zynq-7000 PCIe TRD makes full use of four major components in the PS:

- Application Processor Unit

- Interconnect

- Input/Output Peripherals

- Memory Interfaces

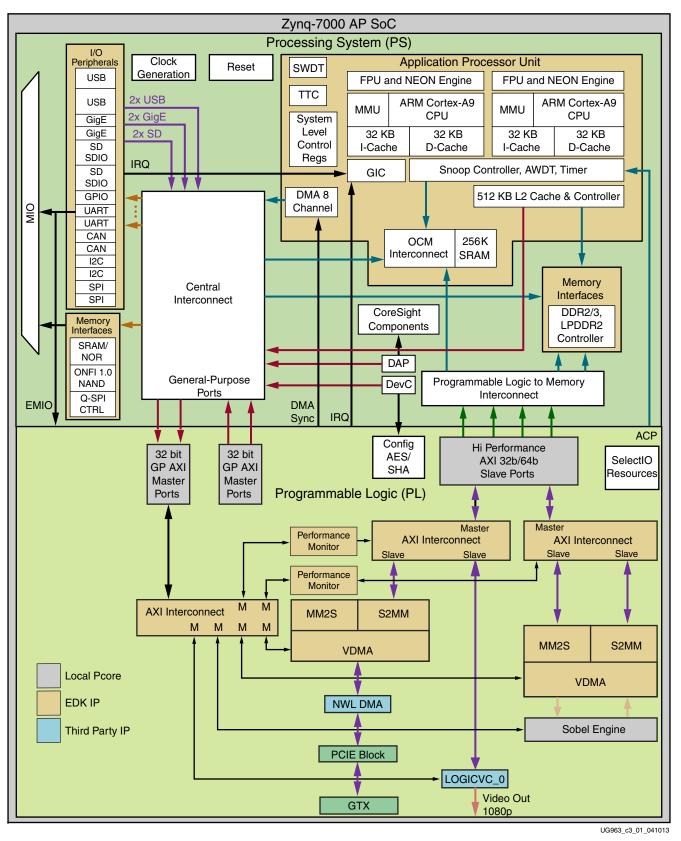

This section describes some of the features of the PS used in this design. A functional block diagram is shown in Figure 2-1.

Figure 2-1: Video Processing and Offloading Demo

#### **Application Processor Unit**

The application processor unit (APU) includes the dual configuration of the ARM Cortex-A9 multiprocessor core, snoop control unit (SCU), level-2 cache controller, dual ported on-chip RAM (OCM), 8-channel DMA, system watchdog timer (SWDT), and triple timer controller (TTC) blocks.

*Cortex-A9 Core* - The ARM Cortex-A9 multiprocessor core implements the ARMv7 architecture and runs 32-bit ARM instructions, 16-bit and 32-bit Thumb instructions, and 8-bit Java byte code in the Jazelle state. The media processing engine implements ARM NEON coprocessor technology, a single instruction multiple data (SIMD) architecture that adds instructions targeted at audio, video, 3D graphics, image, and speech processing.

*General Interrupt Controller (GIC)*- The GIC collects interrupts from various sources and distributes these interrupts to each of the ARM cores. The interrupt distributor holds the list of pending interrupts for each ARM Cortex-A9 multiprocessor core and then selects the highest priority interrupt before issuing it to the Cortex-A9 processor interface. Interrupts of equal priority are resolved by selecting the lowest ID. A total of 64 shared peripheral interrupts (PL interrupts and PS I/O peripheral interrupts) are supported, starting from ID 32.

#### Interconnect

The interconnect unit connects all PS and PL master and slave devices. There are a total of six AXI slave ports dedicated for AXI masters residing in the PL, and four of these ports contain deep FIFOs to improve data throughput. Two AXI master ports provide access to AXI slaves in the PL. In this design, masters in PL are connected through two AXI slave ports with deep FIFOs. One AXI master port is used to access registers in AXI slave IPs in the PL. An advanced peripheral bus (APB) master port is provided for accessing software programmable registers of all PS modules. The top level switch is AXI3-compliant, the soft IPs provided by Xilinx are AXI4-compliant, and the soft AXI interconnect IP provides protocol bridging as needed.

*Slave AXI interfaces (S\_AXI\_HP)* - The high performance S\_AXI\_HP connect the PL to AFI blocks in the PS. The PL has four AXI masters out of which two are connected to the S\_AXI\_HP0 port and two are connected to the S\_AXI\_HP2 port. The HP port enables a high-throughput data path between AXI masters in the programmable logic and the processing system DDR3 memory. The main purpose of the AXI FIFO interface (AFI) units is to smooth out variable latency, allowing the ability to stream data continuously from DDR to the PL masters and from the PL masters to DDR. The PL-side interface of AFI runs on the clock coming from the PL. In this design, a 150 MHz clock is connected from the PL side. The DDR-side clock is running at 2/3 of the DDR\_CLK (533 MHz). The high performance AXI interface module provides several hooks to assist in bandwidth management of masters connected to different PL ports. Controlling issuance capability available from the PL port is one of the hooks exercised in this design to obtain a fair share of bandwidth between two masters, FILTER VDMA, and the display controller.

AXI master port (M\_AXI\_GP) - This AXI master port interfaces with AXI slave IPs in the PL through an AXI-Lite interconnect. The CPU manages initializing and controlling the video pipeline through this port.

#### Input/Output Peripherals

The input/output peripherals (IOP) unit includes communication peripherals. GPIO, Ethernet, USB, I2C, and SD controllers from the PS are used extensively in this design.

*GPIO* - The 64-bit general purpose input/outputs (GPIOs) are connected to the PL through the extendable multiplexed I/O (EMIO) interface. Sixty-four bits are divided into two banks, each having 32 bits. Because each GPIO bit can be dynamically configured as input or output, GPIO bits are used in this design for a variety of functions.

#### **Memory Interfaces**

The memory interfaces unit includes the DDR memory controller and nonvolatile memory controllers. The DDR memory controller includes a 4-port arbiter. One AXI port is dedicated for ARM CPU access and two ports are dedicated for high performance AXI interface master devices in the programmable logic. The remaining port is shared by all other AXI masters. In this design, DDR3 is configured to run at 533 MHz, and the AXI interface is running at 355 MHz.

#### PL Clocks

The PS provides four (FCLKCLK[3:0]) fully programmable clocks to the PL. These clocks are routed directly to PL clock buffers to serve as a frequency source for the PL. The clock generator module in PL gets a 100 MHz clock from FCLKCLK[0].

#### PL Reset

The PS provides four (FCLKRESETN[3:0]) fully programmable reset signals to the PL. These signals are asynchronous to PS clocks. The PL logic reset block in this design receives input from FCLKRESETN[0] and generates necessary reset signals for the design implemented in PL.

### **Programmable Logic**

The video IP and custom logic implemented is implemented in PL.

#### **PCIe Endpoint Device**

The Zynq-7000 ZC7Z045 AP SoC has a x4 Gen2 capable PCIe block. This block interfaces to the root port in the host system and forms the basic communicating entity with the host. The PCIe Endpoint block provides an AXI Stream compliant interface with 64-bit width operating at 250 MHz.

#### **NWL DMA**

The PCIe compatible DMA from Northwest Logic, a Xilinx third-party alliance partner, has AXI stream compliant interface in the user side. Another AXI stream side of the DMA interfaces to the PCIe wrapper. The DMA accepts PCIe transaction layer packets and is responsible for transmitting the completion data back to PCIe block. The NWL DMA also provides an AXI memory-mapped interface that can be used as AXI-Lite compatible register interface.

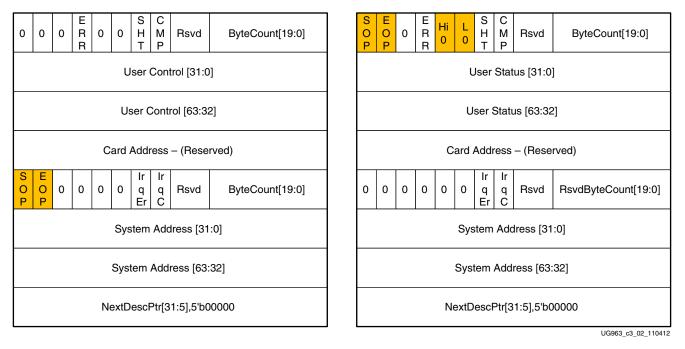

The NWL DMA performs read and write operations to system memory using buffer descriptors (BD). Each descriptor is mapped to a contiguous buffer of 4 KB in the TRD. A ring of such descriptors is established in a circular fashion and a descriptor is freed up to the free BD pool when the completion bit of the same descriptor is set by the DMA. The BD in the free pool can be reused to transfer another buffer. Each BD carries information of the packet SOP, EOP, byte count, and a pointer to next descriptor. Figure 2-2 shows the structure of NWL DMA BDs in the system to card (S2C) and card to system (C2S) direction.

#### Figure 2-2: S2C Buffer Descriptor and C2S Buffer Descriptor Format

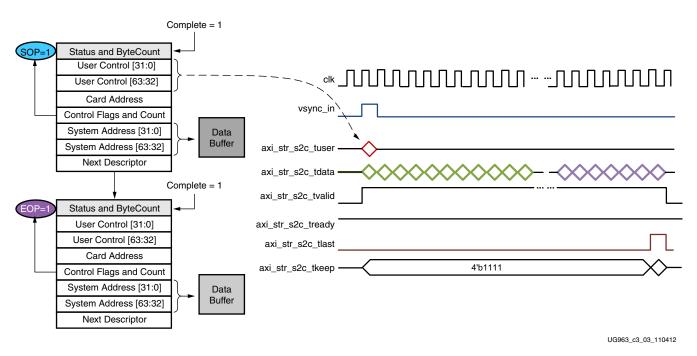

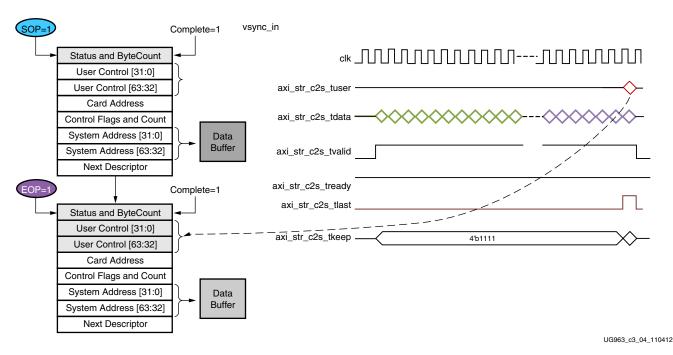

In the video processing and offload demonstration, the video frame synchronization signal is generated in host software and the information is passed over to hardware using the user control field of the NWL DMA BD. Figure 2-3 shows the timing diagram with video frame synchronization signal.

*Figure 2-3:* Video Data Transfer in S2C Direction

In the C2S direction video frames are received continuously. The timing diagram of C2S direction is shown in Figure 2-4. Note that there video frame synchronization signal is not present in the C2S interface because the video processing logic in host does not require any video synchronization signal.

Figure 2-4: Video Data Transfer in C2S Direction

### **AXI Interconnect**

The PL design has two interconnects for AXI memory-mapped masters and one interconnect for the AXI register interface. AXI memory-mapped interconnects are connected to masters like AXI\_VDMA and logiCVC-ML. Slaves connected to these interconnects include HP0 and HP2 ports of the Zynq-7000 XC7Z045 AP Soc PS. This interconnect operates at 150 MHz and the data width is 64-bits. The read/write acceptance and issuance are set to 8 levels. The acceptance and issuance helps improve system performance. The PS HP port can accept a maximum burst length of 16 levels. This imposes a limitation on getting minimum acceptable bandwidth for every master in a multi-master system. The optimum setting of issuance and acceptance reduces throttle on the bus and compensates for long latencies. The AXI register interface is clocked at 75 MHz. The XC7Z045 AP Soc GP0 port acts as master on this interconnect and connected slaves have register maps. AXI TPG and AXI VTC are examples of slaves connected to this interconnect. The operations of the video pipeline are controlled by registers inside every IP. Depending upon data flow required in the video pipeline, the processor writes these registers through the AXI-Lite interconnect. The AXI-Lite interconnect accepts write or read transfers from the CPU, performs address decoding, selects a particular slave, and establishes a communication channel between the CPU and the slave device.

#### AXI Video DMA

The AXI VDMA has an AXI streaming interface on one side and an AXI memory-mapped interface on the other side. The VDMA has two channels: MM2S (memory-mapped to streaming) and S2MM (streaming to memory-mapped). The MM2S channel reads the number of data beats programmed through the C MM2S MAX BURST LENGTH parameter and presents it to the slave device connected through the streaming interface. The data width of the streaming interface can be different than the memory-mapped interface and controlled through C M AXIS MM2S TDATA WIDTH. The data width of the S2MM memory-mapped interface is controlled by the C\_M\_AXI\_MM2S\_DATA\_WIDTH parameter. The S2MM channel receives data from the master device connected through the streaming interface. The C\_S\_AXIS\_S2MM\_TDATA\_WIDTH parameter decides the width of the streaming interface. Data received on the streaming interface is then written into the system memory through the memory-mapped interface. The C\_M\_AXI\_S2MM\_DATA\_WIDTH parameter decides the data width of the memory-mapped interface and C\_S2MM\_MAX\_BURST\_LENGTH governs the burst length of the write transaction. In this design, the streaming interface data width is set to 32-bits and the memory-mapped interface is configured as 64-bits wide. The AXI VDMA is used in simple register direct mode, which removes the area cost of the scatter-gather feature. Initialization, status, and management registers in the AXI VDMA core are accessed through an AXI4-Lite slave interface. To get the best possible throughput for AXI VDMA instances, the maximum burst length is set to 16. In addition, the master interfaces have a read and write issuance of 8 levels and a read and write FIFO depth of 512 to maximize throughput. The line buffers inside the AXI VDMA for the read and write sides are set to 4K deep and the store and forward feature of the AXI VDMA are enabled on both channels to improve system performance and reduce the risk of system throttling.

#### logiCVC-ML

The logiCVC-ML is a multi-layer video display controller from Xylon. The logiCVC-ML controller refreshes the display image by reading the video memory and converting the read data into a data stream acceptable for the display interface. It generates control signals for the display, and supports multiple layers with video processing functions such as alpha blending, transparency, and move around.

#### **PS XADC**

The PS XADC provides the device temperature. Application software running on the PS periodically monitors the power and die temperature and displays the corresponding graphs on the Qt GUI.

#### **AXI Performance Monitor**

The AXI Performance Monitor can monitor and analyze system behavior on the AXI interface. This core is used in the TRD to measure read and write throughput on AXI slave ports of the PS (HP0 and HP2), which are used to access DDR memory from the PL. The core consists of the AXI4-Lite interface to configure and control the core. This core is configured to measure the read and write throughput by counting the number of transactions per second. When the configured time interval expires, measured throughput in bytes is loaded into a register and read by the software application.

#### **PL Address Map**

Table 2-1 shows the address mapping of various peripherals used in the TRD.

| Instance             | Base Address | High Address |

|----------------------|--------------|--------------|

| SOURCE_VDMA          | 0x40090000   | 0x4009FFFF   |

| FILTER_VDMA          | 0x400b0000   | 0x400bFFFF   |

| LOGICVC_0            | 0x40030000   | 0x4003FFFF   |

| PERF_MONITOR_HP0_HP2 | 0x400F0000   | 0x400FFFFF   |

| FILTER_ENGINE        | 0x400D0000   | 0x400DFFFF   |

| AXI_EXT_SLAVE_CONN_0 | 0x40020000   | 0x4002FFFF   |

## **GEN/CHECK** Performance Mode Modules

This performance mode module provides the following options-

- AXI-Stream traffic generation (for a programmed frame size) for C2S direction

- The frame data will be incremental or be a sequence number for ease of data integrity check in software driver.

- AXI-Stream traffic checker (for a programmed frame size) for S2C direction

- The frame data generated by software will be incremental or be a sequence number for ease of data integrity check in hardware.

- Option to loopback S2C traffic to C2S engine

- Data is generated by software and looped back in hardware.

The traffic generator and checker interface follows AXI4 stream protocol. The packet length is configurable through control interface.

The traffic generator and checker module can be used in three different modes- a loopback mode, a data checker mode, and a data generator mode. The module enables specific functions depending on the configuration options selected by the user (which are programmed through control interface to user space registers). On the transmit path, the data checker verifies the data transmitted from the host system via the Packet DMA. On the receive path, data can be sourced either by the data generator or transmit data from host system can be looped back to itself. Based on user inputs, the software driver programs user space registers to enable checker, generator, or loopback mode of operation.

If the Enable Loopback bit is set, the transmit data from DMA in the S2C direction is looped back to receive data in the C2S direction. In the loopback mode, data is not verified by the checker. Hardware generator and checker modules are enabled if Enable Generator and Enable Checker bits are set from software.

The data received and transmitted by the module is divided into packets. The first two bytes of each packet define the length of packet. All other bytes carry the tag - which is sequence number of the packet. The tag increases by one per packet. Table below shows the pre-decided packet format used.

The tag or sequence number is 2-bytes long. The least significant 2 bytes of every start of a new packet is formatted with packet length information. Remaining bytes are formatted with a sequence number which is unique per packet. The subsequent packets have incremental sequence number. Packet format is shown in Table 2-2.

| [63:56] | [47:40] | [31:24] | [15:8] |

|---------|---------|---------|--------|

| [55:48] | [39:32] | [23:16] | [7:0]  |

| TAG     | TAG     | TAG     |        |

#### Table 2-2: Packet Format

| TAG | TAG | TAG | TAG |

|-----|-----|-----|-----|

| TAG | TAG | TAG | TAG |

|     |     |     |     |

|     |     |     |     |

| TAG | TAG | TAG | TAG |

Table 2-2: Packet Format (Cont'd)

The software driver can also define the wrap around value for sequence number through a user space register.

#### **Packet Checker**

If the Enable Checker bit is set (registers as defined in Appendix C), as soon as data is valid on the DMA transmit channels (namely S2C1) each data byte received is checked against a pre-decided data pattern. If there is a mismatch during a comparison, the data\_mismatch signal is asserted. This status is reflected back in register which can be read through control plane.

#### **Packet Generator**

If the Enable Generator bit is set (Register as defined in Section 7.2.1.2) and the data produced by the generator is passed to the receive channel of the DMA (namely C2S1). The data from the generator also follows the same pre-decided data pattern as the packet checker.

#### **Register Interface**

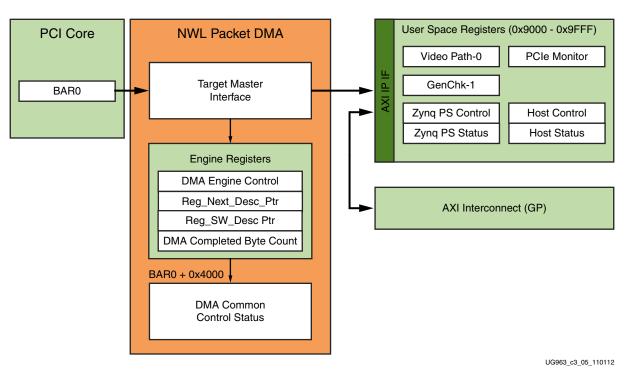

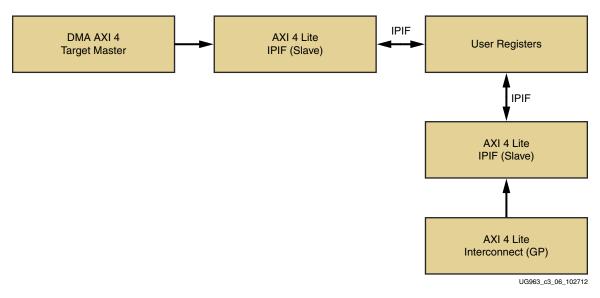

DMA provides AXI4 target interface for user space registers. Register address offsets from  $0 \times 0000$  to  $0 \times 7$ FFF on BAR0 are consumed internally by the DMA engine. Address offset space on BAR0 from  $0 \times 8000$  to  $0 \times FFFF$  is provided to user. Transactions targeting this address range are made available on the AXI4 target interface.

The design has the user space control register interface defining design mode configuration, control and status.

AXI4LITE Interconnect is used to fan out the AXI4 target interface to the appropriate slave address region as defined below.

*Figure 2-5:* **Register Interface**

In order for the user space registers to connect to the AXI-Lite interface; these registers will be wrapped under AXI-Lite slave. IP axi\_lite\_ipif\_v1\_01\_a will be used to provide the AXI-Lite interface. The registers read/write logic will be connected to the IPIF back end.

Figure 2-6: Register Logic Blocks

**XILINX**

### **Clocking and Reset**

This section provides details on clocking and reset connections in the TRD.

#### Clocking

The PL design has four clock domains:

- PCIe clock domain- 100 MHz differential SSC PCIe clock from host system through PCIe connector

- AXI MM (memory-mapped) interconnect 150 MHz

- AXI register interface- 75 MHz

- Video clock- 148.5 MHz

The PCIe clocks are derived from the 100 MHz differential clock. The NWL DMA uses the 250 MHz clock generated by the PCIe block. The NWL DMA provides an AXI master interface which will be used as control interface in the TRD for communicating with the host. A domain crossing FIFO will be used to bring the clock frequency down to 75 MHz in the control path. The clocking scheme of the TRD is shown in Figure 2-7.

Figure 2-7: Clocking Scheme

In the video path, the clock generator module receives a 100 MHz input clock from the PS FCLKCLK[0] and generates 75 MHz and 150 MHz. The AXI-Lite interconnect works on

75 MHz. Apart from the AXI-Lite interconnect, the register interface of AXI VDMA, logiCVC-ML and perf\_monitor cores are driven by the 75 MHz clock. sobel\_filter is driven by 150 MHz clock. Two instances of the AXI\_MM interconnect connected to the HP port of the PS run on 150 MHz. The S2MM (stream to memory map) and MM2S (memory map to stream) channels of VDMAs are running at 150 MHz. The 150 MHz clock also drives the logiCVC-ML memory read interface. The video clock comes from the external clock synthesizer

#### Reset

In PCIe based systems, no external reset pins (esp. switches, push buttons) are used. There is only a PERST# driven by the host processor which is a hard reset and for all intermittent purposes, soft resets (resets driven under software control through register programming) should be used.

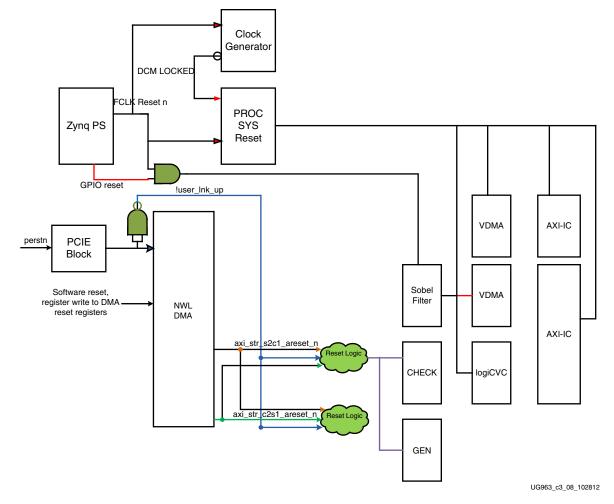

Reset to the blocks present in the video processing path is derived from PROC SYS reset module which gets FCLK reset, DCM lock and PCIe user link up as inputs. The Sobel filter gets an additional reset from the PS GPIO pin which is driven by the PS software. The NWL DMA soft reset is applied to SOURCE VDMA block based on the decision from PS software. The raw path traffic generator and checker blocks are reset based on PCIe user link up status and soft reset coming from NWL DMA block.

Figure 2-8 shows the detailed reset scheme used in the TRD.

Figure 2-8: TRD Reset Scheme

PERSTN or PCIe Link down is the master reset for everything. PCIe wrapper, memory controller and 10GBASE-R PHY get PERSTN directly - these blocks have higher initialization latency hence these are not reset under any other condition. Once initialized, PCIe asserts user\_lnk\_up, memory controller asserts calib\_done and 10G PHY asserts block\_lock (bit position zero in status vector).

The DMA provides per channel soft resets which are also connected to appropriate user logic. Additionally, to reset only the AXI wrapper in MIG and AXI-Interconnect another soft reset via a user space register is provided. However, this reset is to be asserted only when DDR3 FIFO is empty and there is no data lying in FIFO or in transit in FIFO.

# **Software Architecture**

The software for Zynq-7000 PCIe TRD comprises of several Linux kernel-space drivers and a user-space application. Traffic is generated from user application. Format of data changes

from 1080p HD video to raw data modes. The following sections explain data and control path flow.

#### **Host System**

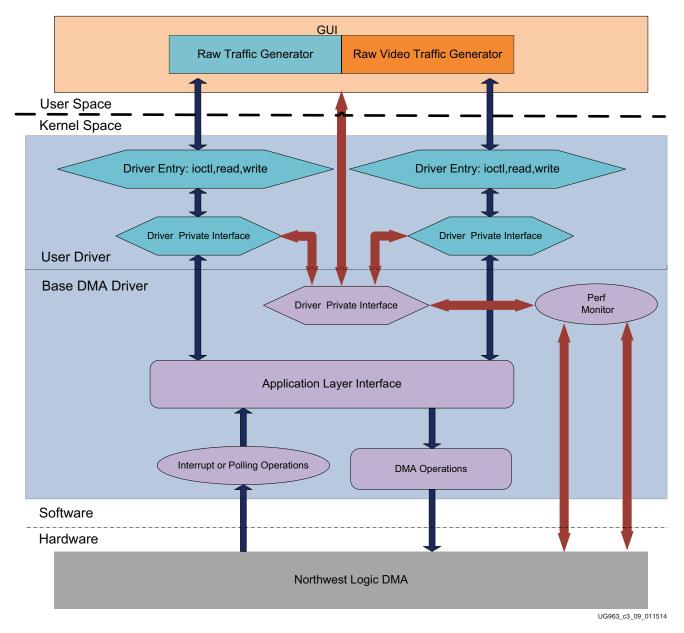

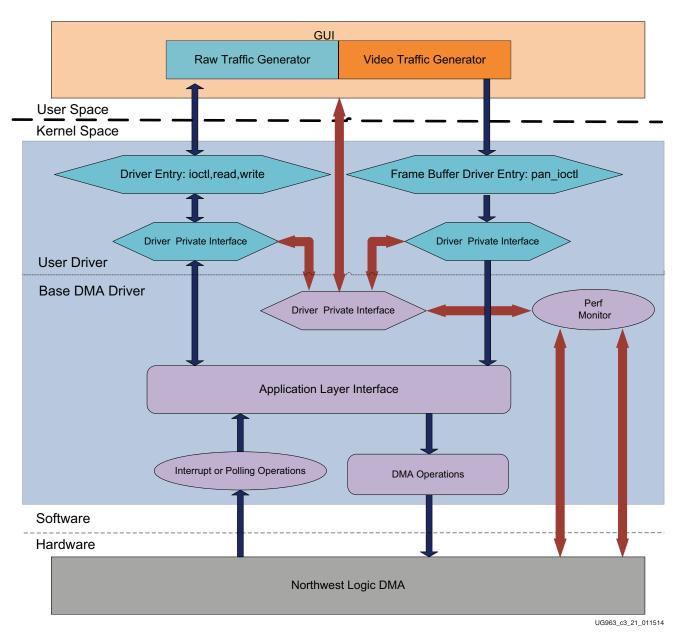

The software driver architecture for generating the color bar pattern is shown in Figure 2-9. The software driver architecture for streaming HD video data from a video file is shown in Figure 2-10.

Figure 2-9: Software Driver Architecture for Streaming HD for Color Bar Pattern

Figure 2-10: Software Driver Architecture for Streaming HD

The application software in host formats three buffers with three different color bar patterns. Each color bar pattern is transmitted through the NWL DMA to the logiCVC display block present in the video path or transferred back to host after Sobel processing. Each buffer contains one video frame of size 1920x1080p and each data buffer is scheduled to transfer through the NWL DMA in a 4KB packet size. Each NWL DMA data buffer spans a size of 1920 pixels.

Each NWL DMA spans = 1920x4 = 7680B.

Number of BDs required to transfer one video frame = 1080.

A BD ring of size 2999 BDs is initialized to generate traffic on the video path. As the completion BDs come from the DMA,

BDs can be pushed back to free BD pool and the data transfer rate can be maintained.

The host software generates video frame synchronization signal at the start of every video frame. The application software also maintains appropriate inter-frame gap so that video processing can be carried out in PS. Figure 2-12, page 31 shows the video frame processing in the host software.

Following sections describe the software components in the TRD in details. The description is divided into data and control path components.

### **Data Path Components**

In the host system, the drivers can be configured in one of two modes:

- 1. Performance demo

- 2. Video demo

#### Video Traffic Generator

The performance demo consists of a Video Traffic Generator. This block generates the video data by decompressing the HD video file selected from the GUI using a VLC media player and transfers the raw RGB data using driver entry points provided by the application driver interface.

#### **Video Driver Entry Point**

This block creates a frame buffer driver interface and enhances different driver entry points for user application. Kernel memory is memory mapped into a VLC media player to enable fast transfer of information from the VLC media player to the frame buffer driver. The VLC media player uses a pan\_ioctl function to intimate the driver of new frame arrivals.

#### Video Driver Private Interface

This block enables interaction with the DMA driver through a private data structure interface. The data that comes from the user application through driver entry points is sent to the DMA driver through private driver interface. The private interface handles received data and does housekeeping of completed transmit buffers by putting them in a completed queue.

#### **Test Pattern Traffic Generator**

This block generates the video data in the form of color bar. The application opens the interface of application driver through exposed driver entry points. Application transfers

the data using read and write entry points provided by application driver interface. Application video traffic generator also performs the data integrity test in receiver side, if enabled.

#### **Driver Entry Point**

This block creates a character driver interface and enhances different driver entry points for user application. The Entry point also enables sending of free user buffers for filling DMA descriptor. Additionally the entry point conveys completed transmit and receive buffers from driver queue to user application.

#### **Driver Private Interface**

This block enables interaction with DMA driver through private data structure interface. The data that comes from user application through driver entry points is sent to DMA driver through private driver interface. The private interface handles received data and housekeeping of completed transmit and receive buffers by putting them in completed queue.

#### **Application Driver Interface**

This block is responsible for dynamic registering and unregistering of user application drivers. The data that is transmitted from user application driver is sent over to DMA operations block.

#### **NWL DMA Operation**

For each DMA channel, the driver sets up a buffer descriptor ring. At test start, the receive ring (associated with a C2S channel) is fully populated with buffers meant to store incoming packets, and the entire receive ring is submitted for DMA while the transmit ring (associated with a S2C channel) is empty. As packets arrive at the base DMA driver for transmission, they are added to the buffer descriptor ring and submitted for DMA transfer.

#### **Interrupt or Polling Operation**

If interrupts are enabled, the interrupt service routine (ISR) handles interrupts from the DMA engine. The driver sets up the DMA engine to interrupt after every N descriptors that it processes. This value of N is set by a compile-time macro. The ISR schedules bottom half (BH) which invokes the functionality in the driver private interface pertaining to handling received data and housekeeping of completed transmit and receive buffers.

In polling mode, the driver registers a timer function which periodically polls the DMA descriptors. The poll function performs the following

a. Housekeeping of completed transmit and receive buffer

b. Handling of received data.

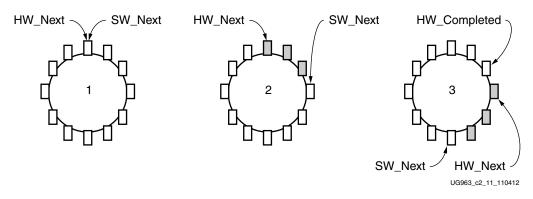

### **DMA Descriptor Management**

This section describes the descriptor management portion of the DMA operation. It also describes the data alignment requirements of the DMA engine.

The nature of traffic, is bursty, and packets are not of fixed sizes. For example, connect/disconnect establishment and ACK/NAK packets are small. Therefore, the software is not able to determine in advance the number of packets to be transferred, and accordingly set up a descriptor chain for it. Packets can fit in a single descriptor, or may be required to span across multiple descriptors. Also, on the receive side the actual packet may be smaller than the original buffer provided to accommodate it.

It is therefore required that:

- The software and hardware are each able to independently work on a set of buffer descriptors in a supplier-consumer model

- The software is informed of packets being received and transmitted as it happens

- On the receive side, the software needs a way of knowing the size of the actual received packet

The rest of this section describes how the driver designed uses the features provided by third party DMA IP to achieve the earlier stated objectives.

The status fields in descriptor help define the completion status, start and end of packet to the software driver.

Table 2-3 presents a summary of the terminology used in the upcoming sections.

| Term         | Description                                                                               |  |

|--------------|-------------------------------------------------------------------------------------------|--|

| HW_Completed | Register with the address of the last descriptor that DMA engine has completed processing |  |

| HW_Next      | Register with the address of the next descriptor that DMA engine will process             |  |

| SW_Next      | Register with the address of the next descriptor that software will submit for DMA        |  |

| ioctl()      | Input Output Control function is a driver entry point invoked by the application tool     |  |

Table 2-3: Terminology Summary

#### **Dynamic DMA Updates**

This section describes how the descriptor ring is managed in the Transmit or System-to-Card (S2C) and Receive or Card-to-System (C2S) directions. It does not give details on the driver's interactions with upper software layers.

#### **Initialization Phase**

Driver prepares descriptor rings, each containing 8192 descriptors, for each DMA channel. In the current design, driver will thus prepare 4 rings.

#### Transmit (S2C) Descriptor Management

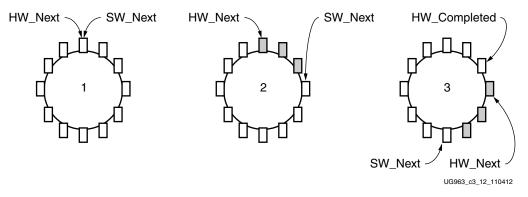

In Figure 2-11, the dark blocks indicate descriptors that are under hardware control, and the light blocks indicate descriptors that are under software control.

Figure 2-11: Transmit Descriptor Ring Management

- Initialization Phase (continued)

- Driver initializes HW\_Next and SW\_Next registers to start of ring

- Driver resets HW\_Completed register

- Driver initializes and enables DMA engine

- Packet Transmission

- Packet arrives in packet handler

- Packet is attached to one or more descriptors in ring

- Driver marks SOP, EOP and IRQ\_on\_completion in descriptors

- Driver adds any User Control information (e.g. checksum-related) to descriptors

- Driver updates SW\_Next register

- Post-Processing

- Driver checks for completion status in descriptor

- Driver frees packet buffer

This process continues as the driver keeps adding packets for transmission, and the DMA engine keeps consuming them. Since the descriptors are already arranged in a ring, post-processing of descriptors is minimal and dynamic allocation of descriptors is not required.

###

#### **Receive (C2S) Descriptor Management**

In Figure 2-12, the dark blocks indicate descriptors that are under hardware control, and the light blocks indicate descriptors that are under software control.

Figure 2-12: Receive Descriptor Ring Management

- Initialization Phase (continued)

- Driver initializes each receive descriptor with an appropriate Raw Data buffer

- Driver initializes HW\_Next register to start of ring and SW\_Next register to end of ring

- Driver resets HW\_Completed register

- Driver initializes and enables DMA engine

- Post-Processing after Packet Reception

- Driver checks for completion status in descriptor

- Driver checks for SOP, EOP and User Status information

- Driver forwards completed packet buffer(s) to upper layer

- Driver allocates new packet buffer for descriptor

- Driver updates SW\_Next register

This process continues as the DMA engine keeps adding received packets in the ring, and the driver keeps consuming them. Since the descriptors are already arranged in a ring, post-processing of descriptors is minimal and dynamic allocation of descriptors is not required.

# **User Interface - Control & Monitor GUI**

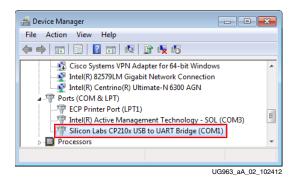

While invoking GUI a launching page is displayed which detects the PCIe device for this design (Vendor ID = 0x10EE and Device ID = 0x7042). Only on detection of the appropriate device, it allows driver installation to proceed through.

#### **GUI Control Function**

Several parameters are controlled through the GUI:

- Driver Mode selection

- Video processing selection on the video path

- Packet size variation on the data path.

- Test type **loopback**, **Hw checker**, or **Hw generator** for performance on the data path

- GUI monitor function

The driver always maintains information about the hardware status. The GUI periodically invokes an I/O Control interrupt, ioctl() to read this status information which is comprised of:

- PCIe link status and device status

- DMA engine status

The driver maintains a set of arrays to hold per-second sampling points of different kinds of statistics, which are periodically collected by the performance monitor handler. The arrays are handled in a circular fashion. The GUI periodically invokes an ioctl() interrupt to read these statistics, and then displays them:

- PCIe link statistics provided by hardware

- DMA engine statistics provided by DMA hardware

- Graph display of all of the above

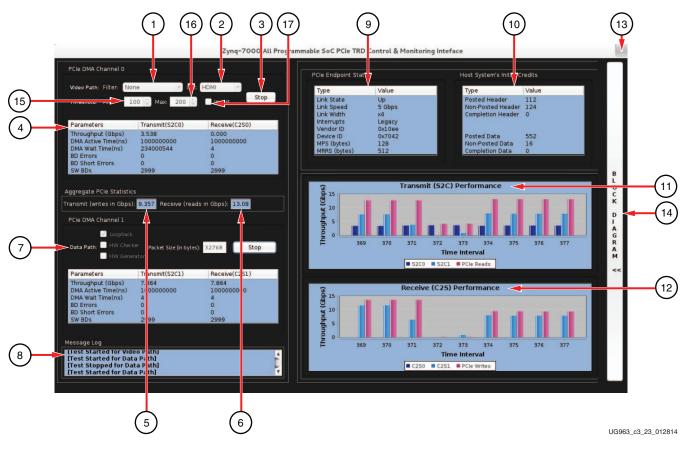

The various Performance GUI fields (with respect to the numbering in Figure 2-13), are explained here.

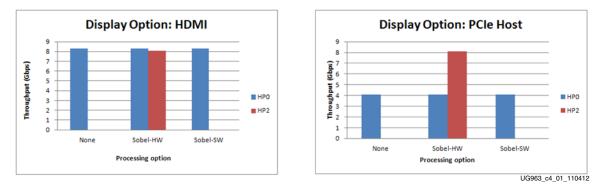

- 1. Sobel Filter- available options are: None, HW-Sobel, SW-Sobel. None does not enable any processing on the generated Video frame. HW-Sobel enables Sobel processing in the PL and SW-Sobel enables processing of the video frame in the PS.

- 2. Video Out- available options are: HDMI, PCIe Host. In the HDMI mode, the generated video frames are displayed on the 1080p60 monitor. In the PCIe Host mode, the Sobel processed (HW or SW) frames return back to PCIe Host.

- 3. Test start/stop control for performance mode

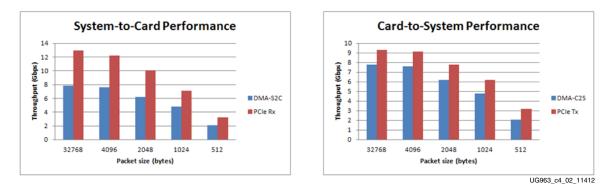

- 4. DMA statistics and software BD gives following information:

- Throughput (Gb/s). DMA payload throughput in gigabits per second for each engine.

- DMA Active Time (ns). The time in nanoseconds that the DMA engine has been active in the last second.

- DMA Wait Time (ns). The time in nanosecond that the DMA was waiting for the software to provide more descriptors.

- BD Errors. Indicates a count of descriptors that caused a DMA error. Indicated by the error status field in the descriptor update.

- BD Short Errors. Indicates a short error in descriptors in the transmit direction when the entire buffer specified by length in the descriptor could not be fetched. This field is not applicable for the receive direction.

- SW BDs. Indicates the count of total descriptors set up in the descriptor ring.

Figure 2-13: GUI in Performance Mode

Table Table 2-4 describes the user interface functions.

| Table 2-4: User Interface Function |

|------------------------------------|

|------------------------------------|

| Callout | Function     | Description                                                                                                                                                |

|---------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Sobel Filter | Sobel Filter ON/OFF selection option. Sobel-HW enables hardware Sobel filter operation. Sobel-SW enables software Sobel filter operation.                  |

| 2       | Video Out    | Output video option. HDMI option enables display on HDMI monitor. PCIe Host option sends the processed video data (HW-Sobel or SW-Sobel) back to PCIe host |

| 3       | Stop Button  | Test stop button.                                                                                                                                          |

| Callout | Function                       | Description                                                                                                                                                                            |  |  |

|---------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 4       | DMA Channel<br>Parameters      | NWL DMA Statistics.                                                                                                                                                                    |  |  |

| 5       | PCIe Transmit<br>Writes        | Reports the transmitted (Endpoint card to host) utilization as obtained from the P performance monitor in hardware (Gb/s).                                                             |  |  |

| 6       | PCIe Receive Reads             | Reports the received (host to Endpoint card) utilization as obtained from the PCIe performance monitor in hardware (Gb/s).                                                             |  |  |

| 7       | Operating Mode                 | In performance GEN/CHEK mode user has options of selecting Loopback or Hw Gen/Hw checker option.                                                                                       |  |  |

| 8       | Message Log                    | Shows messages, warnings, or errors.                                                                                                                                                   |  |  |

| 9       | PCIe Endpoint<br>Status        | Reports the status of PCIe fields in the Endpoint configuration space.                                                                                                                 |  |  |

| 10      | Host System Initial<br>Credits | Initial Flow control credits advertised by the host system after link training with the Endpoint. A value of zero implies infinite flow control credits.                               |  |  |

| 11      | Transmit<br>Performance Plots  | Plots the PCIe transactions on the AXI4-Stream interface and shows the payload statistics graphs based on DMA engine performance monitor.                                              |  |  |

| 12      | Receive<br>Performance Plots   | Plots the PCIe transactions on the AXI4-stream interface and shows the payload stati<br>graphs based on DMA engine performance monitor.                                                |  |  |

| 13      | Close Button                   | Closes GUI.                                                                                                                                                                            |  |  |

| 14      | Block Diagram<br>Button        | This button displays a block diagram of the currently running mode.                                                                                                                    |  |  |

| 15      | Sobel Minimum<br>Threshold     | The minimum threshold value that can be programmed into the Sobel filter. Both Hardware and Software Sobel filters make use of this value.                                             |  |  |

| 16      | Sobel Maximum<br>Threshold     | The maximum threshold value that can be programmed into the Sobel filter. Both Hardware and Software Sobel filters make use of this value. It cannot be less than t minimum threshold. |  |  |

| 17      | Invert                         | Checking this box will enable Sobel Inversion.                                                                                                                                         |  |  |

Table 2-4: User Interface Functions (Cont'd)

This GUI is JAVA based. Java Native Interface (JNI) is used to build the bridge between driver and UI. The same code can be used for windows operating systems with minor changes in JNI for operating system-related calls.

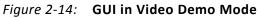

The various Performance GUI fields (with respect to the numbering in Figure 2-14), are explained here.

- 1. Browse: Enables selection of video file in the host file system to be transmitted to the Zynq-7000 device.

- Filter available options are: None, HW-Sobel, SW-Sobel. None does not enable any

processing on the generated video frame and the unmodified frame is displayed on the

monitor. HW-Sobel enables Sobel processing in the PL and SW-Sobel enables

processing of the video frame in the PS.

- 18. File Name: Displays the complete path and file name of the current file being transmitted to the Zynq-7000 device. Hovering the mouse on the text field highlights the entire path.

- 19. Pause: Enables the user to pause and restart the video stream transmission.

| (15) | 18     1     16       PCle DMA Channel 0     PCle DMA Channel 0     PCle DMA Channel 0       Vedio Path:     rround.avd        Intesnoid:     -rrint     100       Parameters     Transmit/S2C0)       Throughput (Cbps)     1.483                                                                            | NE Stop<br>Invert Pause<br>Receive(L2SU)<br>Ven                            | Le SoC PCIe TRD Contro &        | honitoring Inteface<br>Host System's Initia 7<br>Type<br>Posted Header<br>Non-Posted Header<br>Completion Header<br>Posted Data | Value<br>32            | 13                       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------|

| 7    | DMA Active Time(ns) 100000000<br>DMA Active Time(ns) 833623808<br>BD Errors 0<br>SW BDS 2999<br>Aggregate PCle Statistics<br>Transmit (writes in COps): 0.063<br>PCle DMA Channel 1<br>C Loopback<br>PCle DMA Channel 1<br>C Loopback<br>PAcket Size (in byte<br>HW Cenerat r<br>Parameters 1<br>ansmit/S2C1) | 1000000000<br>0<br>0<br>2999<br>5): <u>32768</u><br>51art<br>Receive(c 51) | S (bytes) 128<br>RS (bytes) 512 | Non-Posted Data<br>Completion Data                                                                                              | 0<br>128<br>0<br>41 42 | B (11)<br>0 C K D (14)   |

| 8    | Throughput (Cbps)         C 000           DMA Agit Time(ns)         1 00000000           BD Frors         G           BD Short Errors         G           SW BDs         2 999                                                                                                                                | 0.000<br>100000C 100<br>100000C 100<br>0<br>29999<br>6                     |                                 | Receive (C2S) Performance<br>36 37 38 39 4<br>Time Interval<br>■ C2S0 ■ C2S1 ■ PCIe Writes                                      | 0 41 42                | 12<br>UG963_c3_22_012814 |

Table Table 2-5 describes the user interface functions.

| Callout | Function                  | Description                                                                                                                   |  |

|---------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | Browse button             | Used to browse the host file system and select the HD video                                                                   |  |

| 2       | Filter                    | Filter ON/OFF selection option:                                                                                               |  |

|         |                           | Sobel-HW: Enables hardware Sobel filter operation.                                                                            |  |

|         |                           | Sobel-SW: Enables software Sobel filter operation.                                                                            |  |

|         |                           | None: Displays on unmodified video on the monitor.                                                                            |  |

| 3       | Stop Button               | Test stop button.                                                                                                             |  |

| 4       | DMA Channel<br>Parameters | NWL DMA Statistics.                                                                                                           |  |

| 5       | PCIe Transmit<br>Writes   | Reports the transmitted (Endpoint card to host) utilization as obtained from the PCIe performance monitor in hardware (Gb/s). |  |

| 6       | PCIe Receive Reads        | Reports the received (host to Endpoint card) utilization as obtained from the PCIe performance monitor in hardware (Gb/s).    |  |

| 7       | Operating Mode            | In performance GEN/CHEK mode user has options of selecting Loopback or Hw Gen/Hw checker option.                              |  |

| 8       | Message Log               | Shows messages, warnings, or errors.                                                                                          |  |

| 9       | PCIe Endpoint<br>Status   | Reports the status of PCIe fields in the Endpoint configuration space.                                                        |  |

| Table 2-5: L | Jser Interface | Functions |

|--------------|----------------|-----------|

|--------------|----------------|-----------|

| Callout | Function                       | Description                                                                                                                                                                                    |  |

|---------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 10      | Host System Initial<br>Credits | Initial Flow control credits advertised by the host system after link training with the Endpoint. A value of zero implies infinite flow control credits.                                       |  |

| 11      | Transmit<br>Performance Plots  | Plots the PCIe transactions on the AXI4-Stream interface and shows the payload statistigraphs based on DMA engine performance monitor.                                                         |  |

| 12      | Receive<br>Performance Plots   | Plots the PCIe transactions on the AXI4-stream interface and shows the payload statistics graphs based on DMA engine performance monitor.                                                      |  |

| 13      | Close Button                   | Closes GUI.                                                                                                                                                                                    |  |

| 14      | Block Diagram<br>Button        | This button displays a block diagram of the currently running mode.                                                                                                                            |  |

| 15      | Sobel Minimum<br>Threshold     | The minimum threshold value that can be programmed into the Sobel filter. Both<br>Hardware and Software Sobel filters make use of this value.                                                  |  |

| 16      | Sobel Maximum<br>Threshold     | The maximum threshold value that can be programmed into the Sobel filter. Both<br>Hardware and Software Sobel filters make use of this value. It cannot be less than the<br>minimum threshold. |  |

| 17      | Invert                         | Checking this box will enable Sobel Inversion.                                                                                                                                                 |  |

| 18      | File Name                      | Displays the video file path which is currently being transmitted.                                                                                                                             |  |

| 19      | Pause                          | Pauses video frame transmission. Press it again to continue streaming.                                                                                                                         |  |

Table 2-5: User Interface Functions (Cont'd)

# **Processing System**

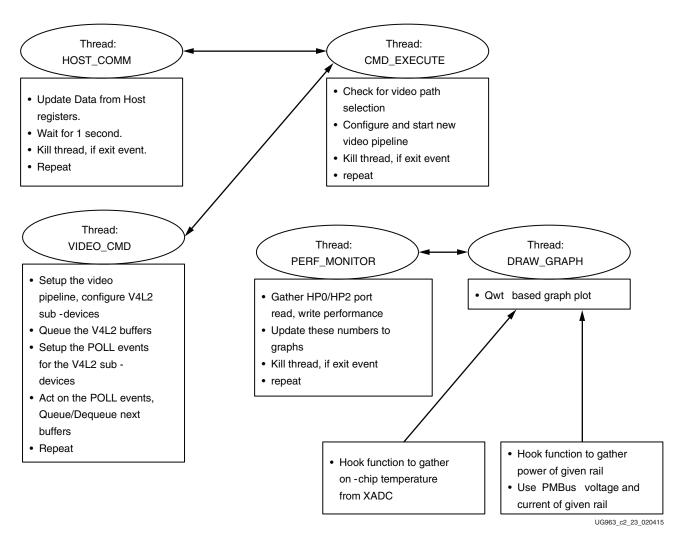

A multi-threaded Linux application calls the appropriate device driver to configure the hardware and enable a particular data path. Three major components are involved:

- Boot Loader

- Xilinx Linux Kernel

- Application

A two-stage boot loader is used for the XC7Z045 AP SoC Linux boot-up. The Xilinx Linux kernel is based on the mainline open source kernel git tree, adding support for a variety of Xilinx IP core drivers and reference boards.

#### **Boot Loader**

The first stage boot loader (FSBL) is responsible for initializing required hardware and loads the second-stage boot loader, U-Boot, which is responsible for loading kernel images in the DDR memory. The FSBL source code is generated through the Xilinx SDK tool, depending on the hardware design specification.

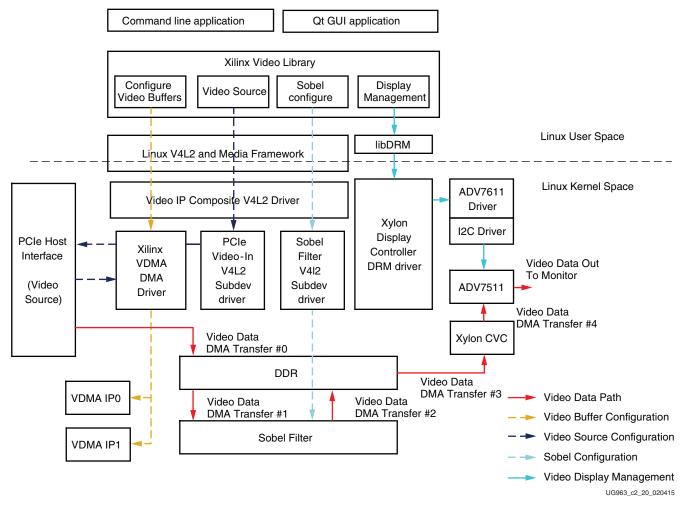

#### **Kernel Drivers**

The Zynq PCIe TRD software design is based on video pipelines. The TRD serves as a reference design to Zynq-7000 AP SoC users who want to implement a video pipeline that includes video input, processing of input video, and output of processed video data. You can reuse hardware/software components of the TRD in their video pipeline designs.

Software drivers of PS peripherals and PL logic (Xylon CVC, VDMA, and Sobel IP) are deployed in the TRD.

A multi-threaded Linux application is responsible for running the TRD demonstration. This application uses the Qt-based GUI, which is displayed through the display monitor. User inputs are provided by the PCIe host application, through a set of registers. Depending on the inputs, it calls device drivers to configure the hardware and to enable a particular data path. The Zynq PCIe TRD software stack implements standard Linux video framework for data capture, processing, and display.

The data capture block is controlled by V4L2 and media framework. Captured frames are then processed either in the hardware block or in the application depending on the Sobel mode selection. Finally, video buffers are submitted to the DRM driver for the scan out. The Zynq PCIe TRD uses these Linux frameworks:

- V4L2 framework

- Media framework

- Linux DMA driver framework

- Device Rendering Manager (DRM) framework

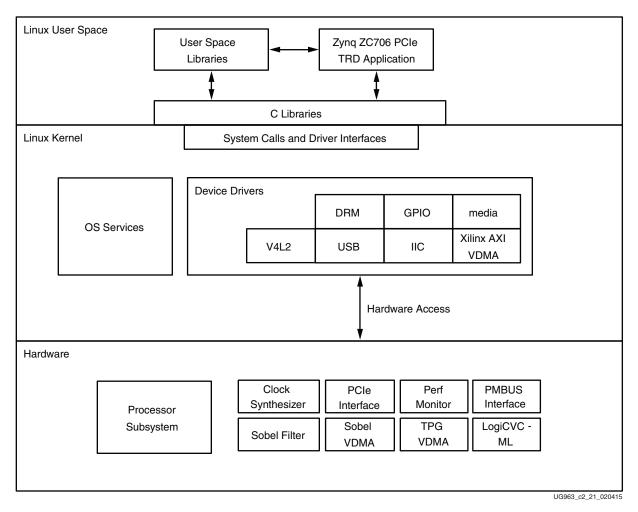

#### A software functional block diagram is shown in Figure 2-15.

Figure 2-15: Software Functional Block Diagram

#### **TRD Software Components**

The following are software components (Linux User space and Kernel space) included in the PCIe TRD system. The components are either native to the Linux operating system or supplied by Xilinx third party partners, or developed in-house at Xilinx.

#### **PCIe Interface Module**

The PCIe Interface Module consists of a set of APIs that handle commands and status from the PCIe Host. The commands and status are communicated over a set of registers operated by both Zynq software and the PCIe Host application. In addition, two application threads are spawned in the Zynq software. The first thread performs frequent monitoring of commands/status and acts upon the command/status received from PCIe Host. The second thread operates on the video pipelines as directed by the commands received.

#### **Control Application**

Control Application consists of a command line Linux user space application and a QT GUIbased application that operates the video pipeline of the PCIe TRD. As the logic of operating the video pipeline is common, some is captured in the Xilinx Video Library. Interfaces exported by this library are used by the command line and QT GUI applications.

- The V4L2 interface is used by the application to configure the required video device (for example, TPG, Sobel IP, etc.).

- The V4L2 interface is also used to manage video buffers used for streaming in and processing video data.

- The DRM interface is used by the application to display video data.

- Media framework is used to configure device internal topology at run time.

Significant logic implemented in the Xilinx Video Library includes:

- Video Buffer Management

- Responsible for supplying video buffers (allocated in kernel space) to receive video data from TPG/external video source and invokes V4L2 composite driver logic, which in turn depends on the VDMA IP driver to manage the transfer of video data into DDR.

- If the Sobel filter is enabled, the Video Buffer management logic facilitates transfer of incoming video data from video buffers to the Sobel IP and from the Sobel IP to the DRM driver buffers.

- Video source/sink selection

- Interfaces with Media framework to configure enabled video devices.

- Selects the source of video data to the external input (PCIe Host) and invokes the entry points of the video IP composite driver, and subsequently the V4L2 sub-device driver to select the video source based on user input.

- Similarly, the video sink is selected based on user application. The video output can be either HDMI monitor or VMDA MM2S channel (frames sent back to PCIe Host). The video pipeline is configured accordingly.

- Sobel configuration

- Enables and configures the Sobel filter hardware IP and invokes the entry points of the Sobel Filter V4L2 sub-device driver to control the Sobel IP.

- Media framework

- This is the standard media framework in Linux. Discovering a device internal topology, and configuring it at run time, is one of the goals of the media framework. Two topology-of-devices are registered with PCIe Host Video IN and Xylon CVC for one tree. Other topology is PCIe Host Video In, Sobel and Xylon CVC.

Toggling between these trees leads to choosing of Sobel filtering of incoming video data.

- Linux V4L2 framework

- This is the standard V4L2 framework in Linux. The Xilinx video IP composite driver registers with the V4L2 framework to provide control of the various elements of the video pipeline.

- Video IP composite driver

- This is a Xilinx V4L2 complaint driver that registers with the Linux V4L2 framework. The PCIe Host Video In and Sobel filer V4L2 sub device drivers register with this composite driver to allow the user application to manage the PCIe TRD video pipeline adhering to the V4L2 standard.

- Also uses the Xilinx VDMA driver to move video data within the PCIe TRD video pipeline.

- Xylon display controller DRM driver

- This driver (from Xylon) adheres to DRM framework in Linux and drives the Xylon CVC display controller. The DRM driver facilitates the DMA included in Xylon CVC to transfer video data (typically from PCIe Host video in/Sobel IP) in DDR to Xylon CVC for display by ADV7511 (HDMI) to the monitor. The driver also initializes the ADV7511 peripheral on the ZC706 board through the Xilinx I2C driver.

- Xilinx VDMA driver

- Adheres to the Linux DMA framework and controls the VDMA IP to facilitate video data transfers in the PCIe TRD video pipeline. The VDMA driver's APIs are invoked by the Xilinx video IP composite V4L2 driver to move video data within the video pipeline under control of the buffer management logic of application software.

- PCIe Host Video In subdev driver

- Adheres to the Linux V4L2 and Media framework, and registers with both of the frameworks. The V4L2 control interface is used to configure PCIe Host Video In to generate different test patterns.

- ADV7611 subdev driver

- Adheres to Linux V4L2 and Media framework and registers with both of the frameworks. Also provides an interface to get/set EDID data, set/get video timing, etc.

- Sobel Filter V4L2 subdev driver

- Controls the Sobel filter IP. It is used to configure Sobel co-efficients, minimum/maximum thresholds, and Sobel invert.

- ADV7511 Driver

- Used by the Xylon CVC DRM driver to configure the display of video output over HDMI. The ADV7511 driver is stacked on the I2C driver. It reads EDID data that has been broadcasted by Monitor.

A top-level view of the software architecture is shown in Figure 2-16.

Figure 2-16: Software Architecture: Top Level View

#### Xilinx Linux Kernel

The Xilinx Linux kernel is based on the mainline open source kernel Git tree, adding support for a variety of Xilinx IP core drivers and reference boards. The source code is available on the Xilinx Open Source ARM Git Repository: <u>github.com/xilinx</u>.

Building the Linux kernel is explained in the Zynq-7000 PCIe Targeted Reference Design wiki page at <u>http://wiki.xilinx.com/zynq-pcie-trd</u>. Table 2-9 lists kernel drivers used for the PCIe TRD.

| Linux Driver                   | Function                                                                                                                                                                                                                | Called by                                                                                                                                                                                                                                |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Xylon DRM                      | Drives the display controller<br>(logiCVC-ML) to display the<br>application UI.                                                                                                                                         | <ul> <li>TRD application uses the libDRM library<br/>to interface with the DRM driver.</li> <li>Linux fbconsole uses the frame buffer<br/>interface to emulate the console.</li> </ul>                                                   |

| Xilinx PCIe Video In<br>(V4L2) | Configures PCIe video IN (currently<br>does nothing) using a standard<br>V4L2 interface. Registers itself a<br>media entity.                                                                                            | <ul> <li>The TRD application uses the v4l2<br/>interface to configure PCIe video IN<br/>(currently does nothing) parameters.</li> <li>The Xilinx video IP composite driver uses<br/>the v4l2 subdev for stop/stop operations.</li> </ul> |

| Xilinx Video IP<br>Composite   | Configures the Xilinx video pipeline.<br>Registers as a media and video<br>device. Sets up links and configures<br>all entities in the pipeline.                                                                        | <ul> <li>The TRD application uses media control<br/>lib to set up the link.</li> <li>The TRD application uses the V4L2<br/>interface for V4L2 buffer handling and<br/>stream on/off operations.</li> </ul>                               |

| Xilinx VDMA<br>Engine Driver   | Configures Xilinx VDMA IP.                                                                                                                                                                                              | The Xilinx video IP composite driver uses slave-DMA API to configure/start/stop VDMA.                                                                                                                                                    |

| UIO                            | Provides a generic framework for<br>UIO devices. Each UIO device is<br>accessed through a device file and<br>several <i>sysfs</i> attribute files. Each UIO<br>node is used to access the address<br>space of the card. | The TRD application uses UIO framework to<br>map device address space, and then control<br>the device using write/read as defined by<br>the register map.                                                                                |