# AXI Interface Based KC705 Embedded Kit MicroBlaze Processor Subsystem Data Sheet

DS669 (v2.0) April 23, 2013

**Product Specification**

## Introduction

The KC705 Embedded Kit MicroBlaze<sup>™</sup> Processor Subsystem showcases various features of the KC705 evaluation board. The targeted reference designs (TRDs) are built around a MicroBlaze soft processor with various peripherals to enable embedded applications. Two TRDs are provided with this package: the KC705\_System (BIST system) and the video demonstration system. Along with these TRDs, a stand-alone software application and webserver-based application are provided.

The BIST TRDs provide an embedded system platform to jump-start embedded system development on the KC705 evaluation platform. The video demonstration is the superset of the BIST system. It provides a MicroBlaze processor based embedded platform that can be used to develop complex video systems. This data sheet describes both of the MicroBlaze processor subsystems.

## **BIST Hardware Platform**

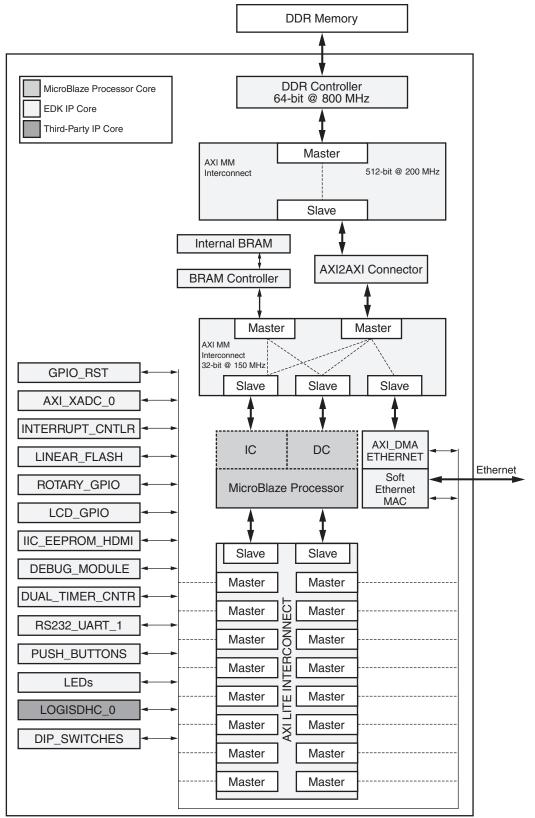

The block diagram for the KC705 MicroBlaze processor subsystem is shown in Figure 1.

© Copyright 2012, 2013 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. AMBA and ARM are trademarks of ARM in the EU and other countries. PCI, PCIe, and PCI Express are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

DS669\_01\_041013

Figure 1: BIST Hardware Block Diagram

www.xilinx.com

Connections between the AXI-Lite interconnect and other peripherals are shown as buses for better graphical representation. The actual connections are point-to-point between each master port of the interconnect to the corresponding peripheral.

This system is implemented in the Kintex®-7 XC7K325TFFG900-2 FPGA using the ISE® Design Suite: Embedded Edition 14.x. The device utilization for the system is:

- Total LUTs used: 32,986 out of 203,800 (15%)

- Total I/Os used: 235 out of 500 (47%)

The specific feature utilization for the system is shown here:

| Number of RAMB36E1/FIF036E1s:           |     | out | of  | 445      | 7%       |

|-----------------------------------------|-----|-----|-----|----------|----------|

| Number using RAMB36E1 only:             | 32  |     |     |          |          |

| Number using FIFO36E1 only:             | 0   |     |     |          |          |

| Number of RAMB18E1/FIF018E1s:           |     | out | of  | 890      | 18       |

| Number using RAMB18E1 only:             | 7   |     |     |          |          |

| Number using FIF018E1 only:             | 0   |     |     |          |          |

| Number of BUFG/BUFGCTRLs:               | 6   | out | of  | 32       | 18%      |

| Number used as BUFGs:                   | 5   |     |     |          |          |

| Number used as BUFGCTRLs:               | 1   |     |     |          |          |

| Number of IDELAYE2/IDELAYE2_FINEDELAYs: | 74  | out | of  | 500      | 14%      |

| Number used as IDELAYE2s:               | 74  |     |     |          |          |

| Number used as IDELAYE2_FINEDELAYs:     | 0   |     |     |          |          |

| Number of ILOGICE2/ILOGICE3/ISERDESE2s: | 96  | out | of  | 500      | 19%      |

| Number used as ILOGICE2s:               | 32  |     |     |          |          |

| Number used as ILOGICE3s:               | 0   |     |     |          |          |

| Number used as ISERDESE2s:              | 64  |     |     |          |          |

| Number of ODELAYE2/ODELAYE2_FINEDELAYs: | 0   | out | of  | 150      | 0%       |

| Number of OLOGICE2/OLOGICE3/OSERDESE2s: | 192 | out | of  | 500      | 38%      |

| Number used as OLOGICE2s:               | 89  |     |     |          |          |

| Number used as OLOGICE3s:               | 0   |     |     |          |          |

| Number used as OSERDESE2s:              | 103 |     |     |          |          |

| Number of PHASER_IN/PHASER_IN_PHYs:     | 8   | out | of  | 40       | 20%      |

| Number used as PHASER_INs:              | 0   |     |     |          |          |

| Number used as PHASER IN PHYs:          | 8   |     |     |          |          |

| Number of LOCed PHASER IN PHYs:         | 8   | out | of  | 8        | 100%     |

| Number of PHASER_OUT/PHASER_OUT_PHYs:   |     |     |     | 40       |          |

| Number used as PHASER_OUTs:             | 0   |     |     |          |          |

| Number used as PHASER_OUT_PHYs:         | 11  |     |     |          |          |

| Number of LOCed PHASER_OUT_PHYs:        |     | out | of  | 11       | 100%     |

| Number of BSCANs:                       |     | out |     | 4        | 25%      |

| Number of BUFHCEs:                      |     | out |     |          | 0%       |

| Number of BUFRs:                        |     | out |     |          | 2%       |

| Number of CAPTUREs:                     |     | out |     |          | 0%       |

| Number of DNA_PORTs:                    |     | out |     |          |          |

| Number of DSP48E1s:                     |     | out |     |          |          |

| Number of EFUSE_USRs:                   |     | out |     | 1        | 08       |

| Number of FRAME_ECCs:                   |     | out |     |          | 0%       |

| Number of GTXE2_CHANNELs:               |     |     |     | 16       |          |

| Number of GTXE2_COMMONs:                |     | out |     |          |          |

| Number of ICAPs:                        |     | out |     | 2        | 0%       |

| Number of IDELAYCTRLs:                  |     | out |     |          |          |

| Number of IN_FIFOs:                     |     | out |     | 40       | 20%      |

| Number of LOCed IN_FIFOs:               |     | out |     | -10<br>8 | 100%     |

| Number of MMCME2_ADVs:                  |     | out |     | 10       | 20%      |

| Number of OUT_FIFOs:                    |     | out |     | 40       | 27%      |

| Number of LOCed OUT FIFOs:              |     | out |     | 40<br>11 | 100%     |

| Number of PCIE_2_1s:                    |     | out |     | 1        | 80<br>80 |

| Number of PHASER_REFs:                  |     | out |     | 10       | 30%      |

| Number of LOCed PHASER_REFs:            |     | out |     | 3        | 100%     |

| Number of PHY_CONTROLs:                 |     | out |     | 10       | 30%      |

| NOUNCE OF LUIT_COINTIONS.               | 2   | Juc | OT. | ΤŪ       | 500      |

| Number of LOCed PHY_CONTROLs: | 3 | out | of | 3  | 100% |

|-------------------------------|---|-----|----|----|------|

| Number of PLLE2_ADVs:         | 1 | out | of | 10 | 10%  |

| Number of STARTUPs:           | 0 | out | of | 1  | 0%   |

| Number of XADCs:              | 1 | out | of | 1  | 100% |

Note: Device resource utilization results are indicative and are dependent on the implementation tool versions. Exact results might vary.

The advantage of implementing this system in an FPGA is that the system can easily be expanded and customized in these ways:

- Configure/modify the MicroBlaze processor.

- Configure/modify the existing peripherals.

- Increase the amount of internal RAM.

- Remove peripherals that are not needed in the user's application. For example, remove one of the GPIO instances.

- Add instances of Xilinx IP that are from the Xilinx IP Catalog or third-party IP.

- Add AXI IP or custom logic in the ISE tools top-level wrapper.

- Add custom logic that either interfaces to the MicroBlaze processor embedded system or is totally independent.

Instructions for modifying the hardware platform can be found in AXI Interface Based KC705 Embedded Kit MicroBlaze Processor Subsystem Hardware Tutorial [Ref 1].

## **System Features**

### **Processor Block**

🗶 XILINX.

- 32-bit MicroBlaze processor with 8 KB instruction cache (I-cache) and 8 KB data cache (D-cache):

- Hardware barrel shifter

- Memory management unit (MMU):

- Provides full MMU functionality

- Controls effective-address to physical-address mapping

- Provides memory protection with two memory protection zones

- 8 KB local memory for instructions and data

- Debug module

- Interrupt controller

- Dual 32-bit timer/counter

#### Memory

- 1 GB 64-bit wide 800 MHz DDR3 SDRAM

- 64 KB internal block RAM

- 128 MB linear (parallel) flash

- Secure digital high-capacity (SDHC) controller

- 1 KB IIC EEPROM

### Input/Output

- Three general-purpose input controllers:

- 5-bit pushbutton controller

- 4-bit DIP switch interface

- 3-bit rotary switch interface

- Two general-purpose output controllers:

- 7-bit LCD interface

- 8-bit LED interface

- 16550 UART:

- Software configurable baud rate, data width, parity, and stop bits

- 10/100 /1000 Mb/s Tri-mode Ethernet MAC (TEMAC):

- GMII interface to PHY

- Scatter-gather direct memory access (DMA)

- axi\_xadc:

- Software configurable XADC block includes a dual 12-bit, 1 MSPS analog-to-digital convertor (ADC) and on-chip sensors

# **BIST Address Map**

The address map of the MicroBlaze processor subsystem is shown in Table 1.

Table 1: KC705 MicroBlaze Processor Subsystem Address Map

| Instance            | Peripheral        | Base Address | High Address |

|---------------------|-------------------|--------------|--------------|

| microblaze_0        | I-cache/D-cache   | 0x80000000   | 0xffffffff   |

| LocalMemory_Cntlr_D | Imb_bram_if_cntlr | 0x00000000   | 0x0000FFFF   |

| LocalMemory_Cntlr_I | Imb_bram_if_cntlr | 0x00000000   | 0x0000FFFF   |

| Interrupt_Cntlr     | axi_intc          | 0x40100000   | 0x4010FFFF   |

| debug_module        | mdm               | 0x40200000   | 0X4020FFFF   |

| Dual_Timer_Counter  | axi_timer         | 0x40300000   | 0X4030FFFF   |

| RS232_Uart_1        | axi_uart16550     | 0x40400000   | 0x4040FFFF   |

| Push_Buttons_5Bits  | axi_gpio          | 0x40500000   | 0x4050FFFF   |

| LEDs_8Bits          | axi_gpio          | 0x40600000   | 0x4060FFFF   |

| DIP_Switches_4Bits  | axi_gpio          | 0x40700000   | 0x4070FFFF   |

| LCD_GPIO            | axi_gpio          | 0x40800000   | 0x4080FFFF   |

| ROTARY_GPIO         | axi_gpio          | 0x40900000   | 0x4090FFFF   |

| IIC_EEPROM          | axi_iic           | 0x40A00000   | 0x40A0FFFF   |

| Logisdhc_0          | logisdhc          | 0x40B00000   | 0x40B0FFFF   |

| axi_xadc_0          | axi_xadc          | 0x40D00000   | 0x40D0FFFF   |

| Linear_Flash        | axi_emc           | 0x48000000   | 0x4FFFFFFF   |

| AXI_DMA_Ethernet    | axi_dma           | 0x50000000   | 0x5000FFFF   |

| Soft_Ethernet_MAC   | axi_ethernet      | 0x50100000   | 0X5013FFFF   |

| DDR3_SDRAM          | axi_7series_ddrx  | 0x80000000   | 0xBFFFFFFF   |

| Internal_BRAM       | axi_bram_ctrl     | 0xC0000000   | 0xC000FFFF   |

# **BIST System Configuration**

## **Clocking Methodology and Considerations**

This system runs off a reference clock frequency of 200 MHz from the differential clock source on the board. The AXI MM and streaming masters/slaves operate at 150 MHz, the AXI-Lite and streaming masters/slaves operate at 100 MHz, and the DDR3 memory runs at 800 MHz. Table 2 shows the system clocks.

### Table 2: System Clocks

| Clock Signal                  | Source                      | Frequency<br>(MHz) | Use                                                                                                            |

|-------------------------------|-----------------------------|--------------------|----------------------------------------------------------------------------------------------------------------|

| Phased Locked Loop 0 (PLLE0)  |                             |                    |                                                                                                                |

| CLK _P, CLK_N                 | External differential clock | 200                | Input clock provided from the board.                                                                           |

| freq_refclk                   | Internal PLL                | 800                | Same as mem_refclk phase shifted by 337.5°.                                                                    |

| mem_refclk                    | Internal PLL                | 800                | Clock used for the memory controller.                                                                          |

| sync_pulse                    | Internal PLL                | 50                 | 0.0625 x freq_refclk. This signal must have a duty cycle of 1/16 or 6.25%.                                     |

| clk_ref                       | Internal PLL                | 200                | IDELAY clock for memory controller and TEMAC, also used for AXI MM interface.                                  |

| sys_clk_axilite_s             | Internal MMCM               | 100                | Low-speed slave clocks for axi4lite_0 interconnect.                                                            |

| Mixed Mode Clock Manager 0 (M | MCM0)                       |                    |                                                                                                                |

| sys_clk_s                     | Internal MMCM               | 150                | Clock for Microblaze processor and instruction local memory bus (ILMB)/data local memory bus (DLMB) block RAM. |

| ethernet_clk                  | Internal clock gen          | 125                | TEMAC GTX reference clock.                                                                                     |

### **Clocks Generator Configuration**

Clocks are generated by the clock generator. Based on the user's clock configuration inputs, the clock generator determines the correct configuration of the PLLs. The clock generator configuration wizard is invoked by selecting **Hardware > Launch Clock Wizard**. The clock generator configuration settings are shown in Table 3.

| Table 3: Clock Generator Config | guration Settings |

|---------------------------------|-------------------|

|---------------------------------|-------------------|

| Component                            | Frequency<br>(MHz) | Phase | Buffered |

|--------------------------------------|--------------------|-------|----------|

| Input Clock                          |                    |       |          |

| CLK                                  | 200.000000         |       |          |

| Processor                            |                    |       |          |

| microblaze_0                         | 150.000000         | 0     | TRUE     |

| Buses                                |                    |       |          |

| axi4_0                               | 200.000000         | 0     | TRUE     |

| axi4lite_0                           | 100.000000         | 0     | TRUE     |

| Peripherals                          |                    |       |          |

| proc_sys_reset_0                     |                    |       |          |

| <ul> <li>Slowest_sync_clk</li> </ul> | 100.000000         | 0     | TRUE     |

| Interrupt_Cntlr                      |                    |       |          |

| <ul> <li>S_AXI_ACLK</li> </ul>       | 100.000000         | 0     | TRUE     |

| ilmb                                 |                    |       |          |

| LMB_CLK                              | 150.000000         | 0     | TRUE     |

| dlmb                                 |                    |       |          |

| LMB_CLK                              | 150.000000         | 0     | TRUE     |

| debug_module                         |                    |       |          |

| S_AXI_ACLK                           | 100.000000         | 0     | TRUE     |

| Dual_Timer_Counter                   |                    |       |          |

| S_AXI_ACLK                           | 100.000000         | 0     | TRUE     |

### Table 3: Clock Generator Configuration Settings (Cont'd)

| Component                           | Frequency<br>(MHz) | Phase | Buffered |

|-------------------------------------|--------------------|-------|----------|

| Internal_BRAM                       |                    |       |          |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| RS232_Uart_1                        |                    |       |          |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| Push_Buttons_5Bits                  |                    |       |          |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| LEDs_8Bits                          |                    |       |          |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| DIP_Switches_4Bits                  |                    |       |          |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| LCD_GPIO                            |                    |       |          |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| ROTARY_GPIO                         |                    |       | +        |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| Linear_Flash                        |                    |       | 1        |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| RdClk                               | 100.000000         | 0     | TRUE     |

| IIC_EEPROM                          |                    |       |          |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| DDR3_SDRAM                          |                    |       |          |

| • clk                               | 200.000000         | 0     | TRUE     |

| mem_refclk                          | 800.000000         | 0     | FALSE    |

| freq_refclk                         | 800.000000         | 337.5 | FALSE    |

| sync_pulse                          | 50.000000          | 10    | FALSE    |

| clk_ref                             | 200.000000         | 0     | TRUE     |

| AXI_DMA_Ethernet                    |                    |       |          |

| <ul> <li>s_axi_lite_aclk</li> </ul> | 100.000000         | 0     | TRUE     |

| <ul> <li>m_axi_sg_aclk</li> </ul>   | 150.000000         | 0     | TRUE     |

| <ul> <li>m_axi_mm2s_aclk</li> </ul> | 150.000000         | 0     | TRUE     |

| <ul> <li>m_axi_s2mm_aclk</li> </ul> | 150.000000         | 0     | TRUE     |

| Soft_Ethernet_MAC                   |                    |       | -        |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| AXI_STR_TXD_ACLK                    | 150.000000         | 0     | TRUE     |

| AXI_STR_TXC_ACLK                    | 150.000000         | 0     | TRUE     |

| AXI_STR_RXD_ACLK                    | 150.000000         | 0     | TRUE     |

| • AXI_STR_RXS_ACLK                  | 150.000000         | 0     | TRUE     |

| • GTX_CLK                           | 125.000000         | 0     | TRUE     |

| REF_CLK                             | 200.000000         | 0     | TRUE     |

| axi_xadc_0                          |                    |       |          |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

#### Table 3: Clock Generator Configuration Settings (Cont'd)

| Component                    | Frequency<br>(MHz) | Phase | Buffered |

|------------------------------|--------------------|-------|----------|

| logisdhc_0                   |                    |       |          |

| sd_base_clk                  | 100.000000         | 0     | TRUE     |

| • S_AXI_ACLK                 | 100.000000         | 0     | TRUE     |

| Top-Level Output Clock Ports |                    |       |          |

| • ddr_ck                     | 800.000000         | 0     | FALSE    |

| • sd_clk                     | 12.500000          | 0     | FALSE    |

### Reset

Resets for the MicroBlaze processor subsystem are generated from the active-High reset input from the board. The external board reset is filtered and synchronized to the system clock. The AXI interconnect reset signals are active-Low and are sequenced coming out of reset in this order:

- 1. Bus structures come out of reset.

- 2. Peripheral(s) come out of reset 16 clocks later.

- 3. The CPU comes out of reset 16 clocks after the peripherals

Resets to the MicroBlaze processor subsystem are generated by the Proc Sys Reset IP core.

### **MicroBlaze Processor Configuration**

The MicroBlaze processor is configured for performance optimization with a hardware barrel shifter and an MMU, and is optimized for speed.

The hardware barrel shifter can shift or rotate a data word by any number of bits in a single clock cycle. Data shifting is a required element of many key operations such as address generation and arithmetic functions. The action of a barrel shifter can be emulated in software, but this takes valuable time which is not available in real-time applications.

In the processor subsystem, full MMU functionality is enabled, including virtual memory address translation. In virtual mode, the MMU translates effective addresses into physical addresses. The MMU also supports memory protection, which allows small blocks of memory to be individually protected from unauthorized access.

The I-cache master and D-cache master are both enabled, each with a cache size of 8 KB. In addition, the I-cache and D-cache execute burst transactions up to eight data beats (8 x 32-bits). The cacheable block of the system is accessed through the axi4\_0 interconnect where the Kintex-7 FPGA AXI DDRX memory controller and other high-speed slave peripherals are connected. The data port (DP) master of the MicroBlaze processor is enabled and connected to the axi4lite\_0 interconnect where the low-speed slaves (like the axi\_gpio and axi\_timer) are connected (slaves that have register functionality or slaves that don't generate burst transactions).

Exceptions are generated for all illegal op codes, unaligned data accesses, and bus errors. More information about the MMU, exceptions, I-cache, D-cache, and performance optimization can be found in the *MicroBlaze Processor Reference Guide Embedded Development Kit* [Ref 2].

### **AXI Interconnect Configuration**

There are three AXI interconnects inside the KC705 MicroBlaze processor subsystem: axi4\_0, axi\_mm\_mb, and axi4lite\_0. The axi4\_0 and axi\_mm\_mb interconnects are for masters and slaves that fully utilize the AMBA® AXI4<sup>™</sup> protocol. This includes masters like the MicroBlaze processor I-cache and D-cache, and axi\_dma masters. The axi\_7series\_ddrx is connected as a slave to this interconnect. This system is a subset of the video demonstration system which has four AXI interconnects connected in hierarchical fashion. The hierarchical connection allows better timing closure and expansion of current hardware to support more AXI masters. It also helps in better floorplanning of the design. In this system also, the two interconnects (axi4\_0 and axi\_4\_0\_mb) are connected in hierarchical fashion, which allows design symmetry with the video demonstration design where multiple masters and slaves are connected through multiple interconnects to share the load.

The axi4lite\_0 interconnect is for masters and slaves that are geared for the AXI4-Lite<sup>™</sup> protocol (32-bit interface, supports only single transactions). This includes masters like the MicroBlaze processor instruction port and data port. In this design, the MicroBlaze processor instruction port is not connected. Slaves connected to this interconnect have register maps or user logic that does not contain high-speed logic like bursting. The axi\_gpio and axi\_timer IP cores are examples of slaves connected to the axi4lite\_0 interconnect.

### Interrupt Controller Configuration

The axi\_intc contains one AXI4-Lite interface slave connection. The master connected to the axi\_intc on the axi4lite\_0 interconnect is the MicroBlaze processor DP. The MicroBlaze processor subsystem shows the internal interrupts generated in the embedded system and the priority ordering of the interrupts (Table 4).

| Signal                                       | Source        | Description                                                                                                          |

|----------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------|

| AXI_DMA_Ethernet_mm2s_introut <sup>(1)</sup> | axi_dma       | Transmit complete interrupt from the DMA.                                                                            |

| AXI_DMA_Ethernet_s2mm_introut                | axi_dma       | Receive complete interrupt from the DMA.                                                                             |

| Soft_Ethernet_MAC_INTERRUPT                  | axi_ethernet  | Interrupt condition in the Ethernet has occurred, as indicated in the TEMAC Interrupt Status register.               |

| Dual_Timer_Counter_Interrupt                 | axi_timer     | In Generate Mode, indicates that the counter rolled over. In Capture Mode, the interrupt event is the capture event. |

| IIC_EEPROM_Intr                              | axi_iic       | Interrupt condition in the IIC controller has occurred, as indicated in the IIC Interrupt Status register.           |

| RS232_Uart_1_Intr                            | axi_uart16550 | Interrupt condition in the UART 16550 has occurred, as indicated in the UART Interrupt Identification register.      |

| logisdhc_0_interrupt                         | logisdhc      | Interrupt from SDHC Controller.                                                                                      |

| xadc_Irpt <sup>(2)</sup>                     | axi_xadc      | Interrupt condition in the XADC has occurred, as indicated in the XADC Interrupt Status register.                    |

|                    |          |           | -         |            |

|--------------------|----------|-----------|-----------|------------|

| Table 4: MicroBlaz | Droceeor | Subevetom | Interrunt | Drioritiae |

|                    |          | Subsystem | micrupi   | rnonues    |

#### Notes:

- 1. This signal has highest priority.

- 2. This signal has lowest priority.

- 3. The IP core data sheets are easily accessed within XPS by right-clicking on the IP core of interest and selecting View PDF Data Sheet.

- 4. For more information about the interrupt controller, see the axi\_intc data sheet.

- 5. For specific information about the interrupt outputs generated by the peripherals in the system, see the corresponding IP core's data sheet.

## **Dual Timer/Counter**

The axi\_timer contains one AXI4-Lite interface slave connection. The master connected to the axi\_timer through the shared mode on the axi4lite\_0 interconnect is the MicroBlaze processor DP. The axi\_timer core is configured to provide two 32-bit timers.

### debug\_module

This instance includes a UART with a configurable slave bus interface that is configured for the AXI4-Lite interface. The MicroBlaze processor DP port is the master connected to the debug\_module slave connections through the shared mode on the axi4lite\_0 interconnect. The UART TX and RX signals are transmitted over the FPGA JTAG port to and from the Xilinx Microprocessor Debug (XMD) tool.

### axi\_bram\_ctrl Configuration

The axi\_bram\_ctrl contains one AXI4 interface slave connection. The slave's data width is configured for 32 bits using the AXI4 interface. Masters connected to the axi\_bram\_ctrl are the MicroBlaze processor I-cache and D-cache through the AXI\_4\_0 interconnect, by means of the shared mode.

The C\_S\_AXI\_SUPPORTS\_NARROW\_BURST is set to zero because all masters inside the system are 32 bits. This parameter should be set to one when connecting to masters bigger than 32 bits inside the design. Setting the parameter to zero allows for resource savings.

### axi\_7series\_ddrx Configuration

The axi\_7series\_ddrx allows the user to use the Memory Interface Generator (MIG) to configure the memory controller. The axi\_7series\_ddrx contains one AXI4 interface slave connection. The slave's data width is configured for 512 bits. The DDRX controller is configured to support data throughput up to 100 Gb/s (512 bits x 200 MHz) whereas a 64-bit DDR memory can also support up to 100 Gb/s with an operating frequency of 800 MHz (64 bits x 1.6 Gb/s).

Masters connected to the axi\_7series\_ddrx through the AXI MM interconnects are I-cache and D-cache ports of the MicroBlaze processor, scatter-gather (SG), memory-map-to-stream (MM2S), and stream-to-memory-map (S2MM) ports of the DMA Ethernet controller. Masters have the ability of issuing one or more transactions to the interconnect. The read acceptance and write acceptance limit of the axi\_7series\_ddrx controller are both set to 32.

### **IIC Controller Configuration**

The axi\_iic contains one AXI4-Lite interface slave connection. The master connected to the axi\_iic through the shared mode on the axi4lite\_0 interconnect is the MicroBlaze processor DP.

The IIC controller supports 7-bit or 10-bit addressing and contains 16-byte transmit and receive FIFOs. It can be configured for standard mode operation (100 KHz) or fast mode operation (>100 KHz–400 KHz).

In the MicroBlaze processor subsystem, the IIC controller is used to interface to the IIC EEPROM and is configured for standard mode operation (100 KHz) with 7-bit addressing.

### Linear Flash Controller Configuration

The axi\_emc contains one AXI4-Lite interface slave connection. The master connected to the axi\_emc through the shared mode on the axi4lite\_0 interconnect is the MicroBlaze processor DP.

The axi\_emc is used to interface with the external linear flash device (16-bit wide 128 Mb Numonyx Flash device PC28F00AP30TF). The flash controller is configured to execute multiple memory access cycles to match memory bank x data width to AXI data width (C\_INCLUDE\_DATAWIDTH\_MATCHING\_0 = 1).

### **GPIO Configuration**

The axi\_gpio contains one AXI4-Lite interface slave connection. The master connected to the axi\_gpio instances through the shared mode on the axi4lite\_0 interconnect is the MicroBlaze processor DP.

The axi\_gpio core is instantiated five times in the system to allow the embedded system to control and access the pushbuttons (Push\_Buttons\_5Bits), DIP switches (DIP\_Switches\_4Bits), LCD interface (LCD\_GPIO), rotary switch (ROTARY\_GPIO), and LEDs (LEDs\_8Bits).

- The Push\_Buttons\_5Bits instance is an input-only GPIO with a width of 5 bits.

- The DIP\_Swithes\_4Bits instance is an input-only GPIO with a width of 4 bits.

- The LEDs\_8Bits instance is an output-only GPIO with a width of 8 bits.

- The LCD\_GPIO instance is an output-only GPIO with a width of 7 bits.

- The ROTARY\_GPIO instance is an input-only GPIO with a width of 3 bits.

### **UART Configuration**

The axi\_uart16550 contains one AXI4-Lite interface slave connection. The master connected to the axi\_uart16550 through the shared mode on the axi4lite\_0 interconnect is the MicroBlaze processor DP.

The UART core is configured to use interrupts. The baud rate, data bits, and parity settings are controlled through software.

### axi\_dma

The axi\_dma is connected to the axi\_ethernet by means of the AXI-Stream protocol. The AXI-Stream interface width is 32 bits for the axi\_ethernet. The MM2S interface is equivalent to transmit (TX) and the S2MM is equivalent to receive (RX). The MM2S, S2MM, and SG interfaces are connected to the AXI\_4\_0 interconnect. The axi4lite\_0 connection of the core is connected to the axi4lite\_0 interconnect.

*Note:* The AXI interface slave connection clock on the axi\_dma drives the axi\_dma SG engine.

### **Ethernet Configuration**

The axi\_ethernet contains one AXI4-Lite interface slave connection and two AXI-Stream interfaces. The MicroBlaze processor DP port is the master connected to the axi\_ethernet slave connections through the shared mode on the axi4lite\_0 interconnect. The two AXI-Stream interfaces are connected to the stream interface of the axi\_dma IP.

The TEMAC is configured to support a GMII/MII PHY interface and contains internal 4 KB transmit and receive FIFOs. In addition, TX and RX checksum offloading is enabled. On power-up or on reset, the on-board PHY is configured to operate in GMII mode with the PHY address set to 00001. The TEMAC can run at 10 Mb/s, 100 Mb/s, or 1,000 Mb/s depending on the network to which it is attached.

### axi\_xadc Configuration

The axi\_xadc IP core consists of these major blocks:

- AXI4-Lite Interface Module

- XADC Core Logic

- XADC Hard Macro

The MicroBlaze processor DP port is connected as a master to the AXI-Lite interface of axi\_xadc. Read and write transactions at the AXI4 are translated into equivalent XADC core logic and XADC hard macro transactions by the AXI4-Lite Interface Module.

Interrupt controller logic is included in the XADC core logic by setting the parameter C\_INCLUDE\_INTR = 1. The XADC hard macro can be accessed via both the JTAG Test Access Port (TAP) and the axi\_xadc IP core. When simultaneous access of the XADC hard macro occurs, the JTAGLOCKED port can be asserted High by JTAG TAP. In this scenario, the axi\_xadc IP core is not allowed to do any read/write access from/to the DRP or FPGA logic.

### logisdhc Configuration

This is a third-party IP core used for accessing SD cards on KC705 board. The logisdhc IP contains one AXI4-Lite interface slave connection. The MicroBlaze processor DP port is the master connected to the logisdhc slave connections through the shared mode on the axi4lite\_0 interconnect. The SD base clock is 100 MHz. The clock generator lock output is connected to the base clock input of the IP core to ensure that the clocks are stable well in advance.

## Software Application and Board Support Package

This section provides a description of the software application and its associated board support package that is provided with the system (Table 5).

Table 5:

KC705 MicroBlaze Processor Subsystem Software Application

| Software Platform | Software Application     |

|-------------------|--------------------------|

| Stand-alone       | Board_Test_App_Console   |

| Xilkernel         | Board_Test_App_Webserver |

See AXI Interface Based KC705 Embedded Kit MicroBlaze Processor Subsystem Software Tutorial [Ref 3] for more information on how to execute and modify the software platform.

### **Stand-alone Platform**

The stand-alone software platform is a simple, single-threaded environment that is used when an application accesses processor functions directly.

### Board\_Test\_App\_Console

The Board\_Test\_App\_Console software application is a simple application that exercises most of the KC705 evaluation board features. In console mode, a menu appears in the UART console, and user inputs and outputs are conveyed through the same UART console. The Board\_Test\_App\_Console has a simple design to start with.

### Xilkernel Software Platform

This is a simple embedded processor kernel that can be customized to a large degree for a given system. Xilkernel has the key features of an embedded kernel such as multi-tasking, priority-driven preemptive scheduling, inter-processor communication, synchronization facilities, and interrupt handling. Xilkernel is small, modular, and user-customizable. It can be used in different system configurations.

### Board\_Test\_App\_Webserver

In webserver mode, the KC705 system is built based on the Xilkernel OS and Lightweight IP (IwIP). The target supports webserver and is configured with a static IP address. When the host PC is connected to the KC705 target with an Ethernet cable and browse with the static IP address, a web page appears on the host PC with the board test applications menu. The user can select the test applications in the web page and click to run the tests on target. The KC705 board then runs the selected tests and posts the results of the board tests to the host PC, displaying them in the web page.

## **KC705 BIST System Directory Structure**

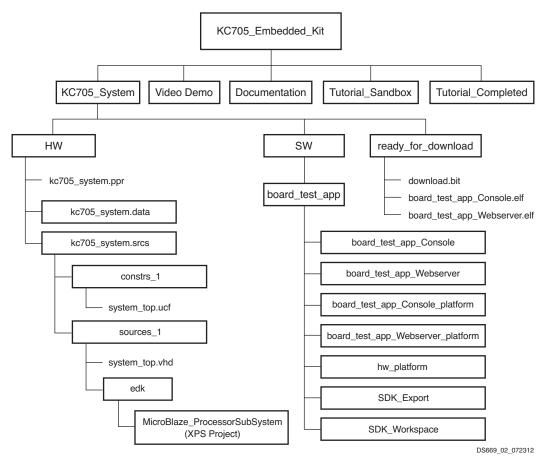

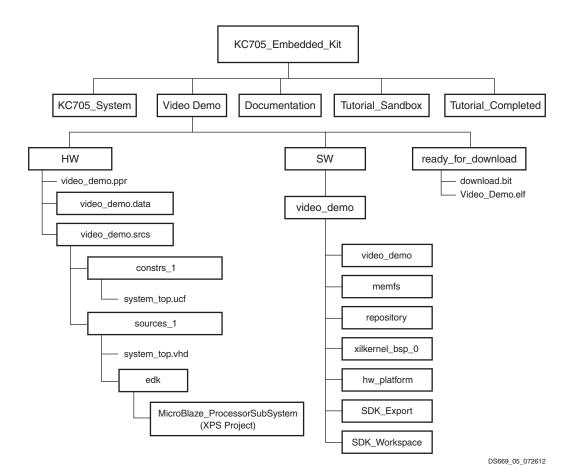

Figure 2 shows the top-level directory structure of the KC705 MicroBlaze processor subsystem.

Figure 2: BIST System Directory Structure

www.xilinx.com

# Use Cases

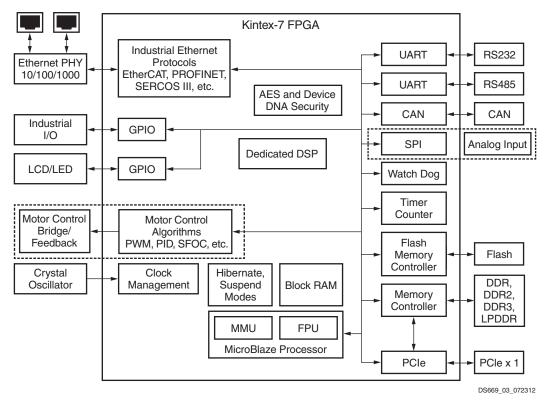

The MicroBlaze processor subsystem is the base platform for embedded systems in many use models. Figure 3 shows an example of the MicroBlaze processor subsystem used in an industrial command and control system.

Note: The system shown in Figure 3 is an example only and is not provided as part of the KC705 Embedded Kit.

## **Video Demonstration**

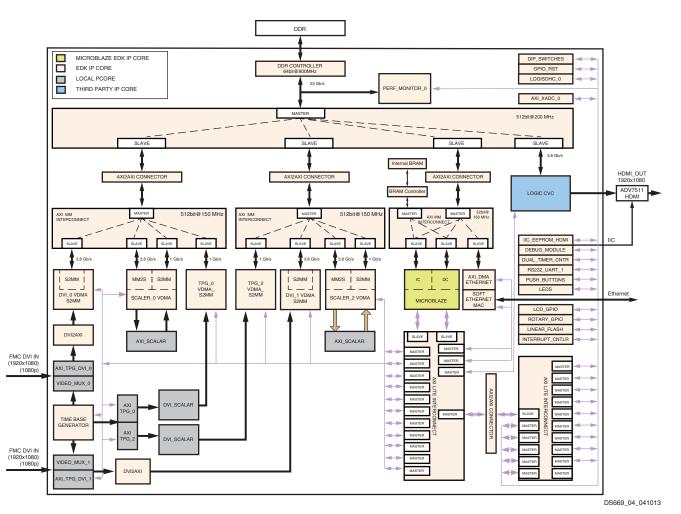

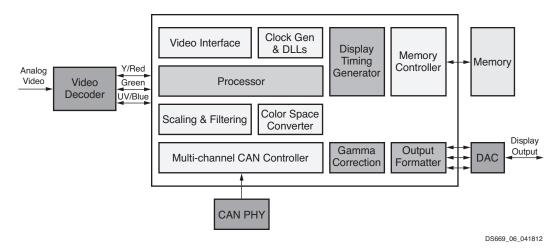

The block diagram for the KC705 MicroBlaze processor subsystem is shown in Figure 4.

Figure 4: Video Demonstration Block Diagram

*Note:* Connections between the AXI-Lite interconnect and other peripherals are shown as buses only for better graphical representation. The actual connections are point-to-point between each master port of the interconnect to the corresponding peripheral.

This system is implemented in the Kintex-7 XC7K325TFFG900-2 FPGA using the ISE Design Suite: Embedded Edition 14.x. The device utilization for the system is:

- Total LUTs used: 86482 out of 203,800 (42%)

- Total I/Os used: 311 out of 500 (61%)

The specific feature utilization for the system is shown here:

| Number of RAMB36E1/FIF036E1s:         |        | out | of | 445 | 45% |

|---------------------------------------|--------|-----|----|-----|-----|

| Number using RAMB36E1 only:           | 203    |     |    |     |     |

| Number using FIFO36E1 only:           | 0      |     |    |     |     |

| Number of RAMB18E1/FIF018E1s:         | 47     | out | of | 890 | 5%  |

| Number using RAMB18E1 only:           | 47     |     |    |     |     |

| Number using FIF018E1 only:           | 0      |     |    |     |     |

| Number of BUFG/BUFGCTRLs:             | 8      | out | of | 32  | 25% |

| Number used as BUFGs:                 | 5      |     |    |     |     |

| Number used as BUFGCTRLs:             | 3      |     |    |     |     |

| Number of IDELAYE2/IDELAYE2_FINEDELAY | 's: 74 | out | of | 500 | 14% |

| Number used as IDELAYE2s:             | 74     |     |    |     |     |

| Number used as IDELAYE2_FINEDELAYs:   | 0      |     |    |     |     |

| Number of ILOGICE2/ILOGICE3/ISERDESE2 | s: 96  | out | of | 500 | 19% |

| Number used as ILOGICE2s:             | 32     |     |    |     |     |

| Number used as ILOGICE3s:             | 0      |     |    |     |     |

|                                       |        |     |    |     |     |

| Number used as ISERDESE2s:              | 64  |     |    |     |      |  |

|-----------------------------------------|-----|-----|----|-----|------|--|

| Number of ODELAYE2/ODELAYE2_FINEDELAYs: | 0   | out | of | 150 | 0%   |  |

| Number of OLOGICE2/OLOGICE3/OSERDESE2s: | 212 | out | of | 500 | 42%  |  |

| Number used as OLOGICE2s:               | 109 |     |    |     |      |  |

| Number used as OLOGICE3s:               | 0   |     |    |     |      |  |

| Number used as OSERDESE2s:              | 103 |     |    |     |      |  |

| Number of PHASER_IN/PHASER_IN_PHYs:     | 8   | out | of | 40  | 20%  |  |

| Number used as PHASER_INs:              | 0   |     |    |     |      |  |

| Number used as PHASER_IN_PHYs:          | 8   |     |    |     |      |  |

| Number of LOCed PHASER_IN_PHYs:         | 8   | out | of | 8   | 100% |  |

| Number of PHASER_OUT/PHASER_OUT_PHYs:   | 11  | out | of | 40  | 27%  |  |

| Number used as PHASER_OUTs:             | 0   |     |    |     |      |  |

| Number used as PHASER_OUT_PHYs:         | 11  |     |    |     |      |  |

| Number of LOCed PHASER_OUT_PHYs:        | 11  | out | of | 11  | 100% |  |

| Number of BSCANs:                       | 1   | out | of | 4   | 25%  |  |

| Number of BUFHCEs:                      | 0   | out | of | 168 | 0%   |  |

| Number of BUFRs:                        | 1   | out | of | 40  | 2%   |  |

| Number of CAPTUREs:                     | 0   | out | of | 1   | 0%   |  |

| Number of DNA_PORTs:                    | 0   | out | of | 1   | 0%   |  |

| Number of DSP48E1s:                     | 19  | out | of | 840 | 2%   |  |

| Number of EFUSE_USRs:                   | 0   | out | of | 1   | 08   |  |

| Number of FRAME_ECCs:                   | 0   | out | of | 1   | 08   |  |

| Number of GTXE2_CHANNELs:               | 0   | out | of | 16  | 0%   |  |

| Number of GTXE2_COMMONs:                | 0   | out | of | 4   | 0%   |  |

| Number of ICAPs:                        | 0   | out | of | 2   | 08   |  |

| Number of IDELAYCTRLs:                  | 3   | out | of | 10  | 30%  |  |

| Number of IN_FIFOs:                     | 8   | out | of | 40  | 20%  |  |

| Number of LOCed IN_FIFOs:               | 8   | out | of | 8   | 100% |  |

| Number of MMCME2_ADVs:                  | 2   | out | of | 10  | 20%  |  |

| Number of LOCed MMCME2_ADVs:            | 1   | out | of | 2   | 50%  |  |

| Number of OUT_FIFOs:                    | 11  | out | of | 40  | 27%  |  |

| Number of LOCed OUT_FIFOs:              | 11  | out | of | 11  | 100% |  |

| Number of PCIE_2_1s:                    | 0   | out | of | 1   | 0%   |  |

| Number of PHASER_REFs:                  | 3   | out | of | 10  | 30%  |  |

| Number of LOCed PHASER_REFs:            | 3   | out | of | 3   | 100% |  |

| Number of PHY_CONTROLs:                 | 3   | out | of | 10  | 30%  |  |

| Number of LOCed PHY_CONTROLs:           | 3   | out | of | 3   | 100% |  |

| Number of PLLE2_ADVs:                   | 1   | out | of | 10  | 10%  |  |

| Number of LOCed PLLE2_ADVs:             | 1   | out | of | 1   | 100% |  |

| Number of STARTUPs:                     | 0   | out | of | 1   | 08   |  |

| Number of XADCs:                        | 1   | out | of | 1   | 100% |  |

|                                         |     |     |    |     |      |  |

Note: Device resource utilization results are indicative and are dependent on the implementation tool versions. Exact results can vary.

### **System Features**

#### **Processor Block**

- MicroBlaze 32-bit processor with 8 KB I-cache and 8 KB D-cache

- Hardware barrel shifter

- MMU:

- Provides full MMU functionality

- Controls effective-address to physical-address mapping

- Provides memory protection with two memory protection zones

- 8 KB local memory for instructions and data

- Debug module

- Interrupt controller

- Dual 32-bit timer/counter

### Memory

- 1 GB 64-bit wide 800 MHz DDR3 SDRAM

- 64 KB internal block RAM

- 128 MB linear (parallel) flash

- SDHC controller

- 2 GB SD card

- 1 KB IIC EEPROM

#### Input/Output

- Three general-purpose input controllers:

- 5-bit pushbutton controller

- 4-bit DIP switch interface

- 3-bit rotary switch interface

- Two general-purpose output controllers:

- 7-bit LCD interface

- 8-bit LED interface

- 16550 UART:

- Software configurable baud rate, data width, parity, and stop bits

- 10/100 /1000 Mb/s TEMAC:

- GMII interface to PHY

- Scatter-gather DMA

- axi\_xadc:

- Software configurable XADC block includes a dual 12-bit, 1 MSPS ADC and on-chip sensors

### **Video Processing**

- VSRC\_SEL:

- · Video multiplexer for external video and internally generated test patterns

- AXI interconnect:

- Four AXI MM interconnects are connected in a hierarchical fashion with a 512-bit AXI MM interconnect running at 200 MHz

- Two AXI-Lite interconnects connected in a hierarchical fashion

- Twelve AXI masters are connected to AXI MM interconnects

- Thirty-two AXI-Lite slaves are connected to an AXI-Lite interconnect

- · Performance monitor: Captures throughput values on the AXI Interface of the DDR controller

- logiCVC: AXI-based third-party display controller capable of supporting up to five layers of video display along with the Alpha blending feature

- v\_tc: AXI-based internal video timing control signal generator

- AXI TPG: AXI-based test pattern generator

- AXI Scaler: AXI-based scaler that scales the video frame from 1920 x 1080 to 960 x 540

- DVI Scaler: Digital visual interface (DVI) in-line scaler that scales the video frame from 1920 x 1080 to 960 x 540

### Video Data Throughput Calculation

The data throughput calculation for the video demonstration is:

- 1080p pixel clock frequency = (2200 pixels) x (1125 rows) x (60 frames/sec) = 148.5 MHz

- For one full frame write or read AXI data:

(1920 active pixels) x (1080 active rows) x (32 bits/pixel) x (60 frames/sec) = 3.71 Gb/s (approximate)

• For one scaled frame write or read AXI data:

(960 active pixels) x (540 active rows) x (32 bits/pixel) x (60 frames/sec) = 1 Gb/s (approximate)

- Stream 1 throughput:

- DVI 0 video direct memory access (VDMA) S2MM (one full frame write) = 3.71 Gb/s

- SCALER 0 VDMA MM2S(one full frame read) = 3.71 Gb/s

- SCALER 0 VDMA S2MM (one scaled frame write) = 1 Gb/s

- Stream 2 throughput:

- TPG 0 VDMA S2MM (one scaled frame write) = 1 Gb/s

- Stream 3 throughput:

- DVI 1 VDMA S2MM (one full frame write) = 3.71 Gb/s

- SCALER 2 VDMA MM2S(one full frame read) = 3.71 Gb/s

- SCALER 2 VDMA S2MM (one scaled frame write) = 1 Gb/s

- Stream 4 throughput:

- TPG 2 VDMA S2MM (one scaled frame write) = 1 Gb/s

- Display controller throughput:

- logiCVC MM2S (one full frame read) = 3.71 Gb/s

- Total throughput for displaying four scaled video streams on the video data is 23 Gb/s (11.5 Gb/s for write and 11.5 Gb/s for read)

### **Video Demonstration Address Map**

The address map of the MicroBlaze processor subsystem is shown in Table 6.

Table 6: KC705 MicroBlaze Processor Subsystem Address Map

| Instance            | Peripheral        | Base Address | High Address |

|---------------------|-------------------|--------------|--------------|

| microblaze_0        | I-cache/D-cache   | 0x80000000   | Oxffffffff   |

| LocalMemory_Cntlr_D | Imb_bram_if_cntlr | 0x00000000   | 0x0000FFFF   |

| LocalMemory_Cntlr_I | Imb_bram_if_cntIr | 0x00000000   | 0x0000FFFF   |

| Interrupt_Cntlr     | axi_intc          | 0x40100000   | 0x4010FFFF   |

| debug_module        | mdm               | 0x40200000   | 0X4020FFFF   |

| Dual_Timer_Counter  | axi_timer         | 0x40300000   | 0X4030FFFF   |

| RS232_Uart_1        | axi_uart16550     | 0x40400000   | 0x4040FFFF   |

| Push_Buttons_5Bits  | axi_gpio          | 0x40500000   | 0x4050FFFF   |

| LEDs_8Bits          | axi_gpio          | 0x40600000   | 0x4060FFFF   |

| DIP_Switches_8Bits  | axi_gpio          | 0x40700000   | 0x4070FFFF   |

| LCD_GPIO            | axi_gpio          | 0x40800000   | 0x4080FFFF   |

| ROTARY_GPIO         | axi_gpio          | 0x40900000   | 0x4090FFFF   |

| IIC_EEPROM          | axi_iic           | 0x40A00000   | 0x40A0FFFF   |

| Logisdhc_0          | logisdhc          | 0x40B00000   | 0x40B0FFFF   |

| GPIO_RST            | axi_gpio          | 0x40C00000   | 0x40C0FFFF   |

| axi_xadc_0          | axi_xadc          | 0x40D00000   | 0x40D0FFFF   |

| Linear_Flash        | axi_emc           | 0x48000000   | 0x4FFFFFFF   |

| AXI_DMA_Ethernet    | axi_dma           | 0x50000000   | 0x5000FFFF   |

www.xilinx.com

| Instance          | Peripheral       | Base Address | High Address |

|-------------------|------------------|--------------|--------------|

| Soft_Ethernet_MAC | axi_ethernet     | 0x50100000   | 0X5013FFFF   |

| axi_tpg_dvi_0     | axi_tpg          | 0x50200000   | 0x5020FFFF   |

| DVI_IN_0_VDMA     | axi_vdma         | 0x50300000   | 0x5030FFFF   |

| SCALER_0_VDMA     | axi_vdma         | 0x50400000   | 0x5040FFFF   |

| timebase_0        | v_tc             | 0x50500000   | 0X5050FFFF   |

| axi_tpg_0         | axi_tpg          | 0x50600000   | 0x5060FFFF   |

| TPG_0_VDMA        | axi_vdma         | 0x50700000   | 0X5070FFFF   |

| axi_tpg_dvi_1     | axi_tpg          | 0x50800000   | 0x5080FFFF   |

| DVI_IN_1_VDMA     | axi_vdma         | 0x50900000   | 0X5090FFFF   |

| SCALER_2_VDMA     | axi_vdma         | 0x50A00000   | 0X50A0FFFF   |

| axi_tpg_2         | axi_tpg          | 0x50B00000   | 0x50B0FFFF   |

| TPG_2_VDMA        | axi_vdma         | 0x50C00000   | 0X50C0FFFF   |

| CVC_DISPLAY       | logicvc          | 0x80000000   | 0x9FFFFFFF   |

| Internal_BRAM     | axi_bram_ctrl    | 0xC0000000   | 0xC000FFFF   |

| DDR3_SDRAM        | axi_7series_ddrx | 0x80000000   | 0xBFFFFFFF   |

#### Table 6: KC705 MicroBlaze Processor Subsystem Address Map (Cont'd)

### Video Demonstration System Configuration

### **Clocking Methodology and Considerations**

This is the same as in the BIST system (see Clocking Methodology and Considerations, page 5).

#### **Clock Generator Configuration**

Clocks are generated by the clock generator. Based on the user's clock configuration inputs, the clock generator determines the correct configuration of the PLLs. The clock generator configuration wizard is invoked by selecting **Hardware > Launch Clock Wizard**. The clock generator configuration settings are shown in Table 7.

| Table 7: Clock Generator Configuration Setting |

|------------------------------------------------|

|------------------------------------------------|

| Component        | Frequency<br>(MHz) | Phase | Buffered |  |

|------------------|--------------------|-------|----------|--|

| Input Clock      |                    |       |          |  |

| CLK              | 200.000000         |       |          |  |

| Processor        |                    |       |          |  |

| microblaze_0     | 150.000000         | 0     | TRUE     |  |

| Buses            |                    |       |          |  |

| axi4_0           | 150.000000         | 0     | TRUE     |  |

| axi4lite_0       | 100.000000         | 0     | TRUE     |  |

| Peripherals      |                    |       |          |  |

| proc_sys_reset_0 |                    |       |          |  |

| Slowest_sync_clk | 100.000000         | 0     | TRUE     |  |

| Interrupt_Cntlr  | ,                  |       |          |  |

| S_AXI_ACLK       | 100.000000         | 0     | TRUE     |  |

| ilmb             |                    |       |          |  |

| LMB_CLK          | 150.000000         | 0     | TRUE     |  |

### Table 7: Clock Generator Configuration Settings (Cont'd)

| Component                           | Frequency<br>(MHz) | Phase | Buffered |

|-------------------------------------|--------------------|-------|----------|

| dlmb                                |                    |       |          |

| LMB_CLK                             | 150.000000         | 0     | TRUE     |

| debug_module                        |                    |       |          |

| S_AXI_ACLK                          | 100.000000         | 0     | TRUE     |

| Dual_Timer_Counter                  |                    |       |          |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| Internal_BRAM                       | ł                  |       | +        |

| <ul> <li>S_AXI_ACLK</li> </ul>      | 100.000000         | 0     | TRUE     |

| RS232_Uart_1                        |                    |       |          |

| S_AXI_ACLK                          | 100.000000         | 0     | TRUE     |

| Push_Buttons_5Bits                  | 1                  | 1     |          |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| LEDs_8Bits                          | ļ.                 | +     | +        |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| DIP_Switches_8Bits                  |                    | I     |          |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| LCD_GPIO                            | J.                 | 1     | 1        |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| ROTARY_GPIO                         | ł                  |       | +        |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| Linear_Flash                        | J.                 | 1     | 1        |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| RdClk                               | 100.000000         | 0     | TRUE     |

| IIC_EEPROM                          | J.                 | 1     | 1        |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| DDR3_SDRAM                          |                    | 1     |          |

| • clk                               | 200.000000         | 0     | TRUE     |

| mem_refclk                          | 800.000000         | 0     | FALSE    |

| <ul> <li>freq_refclk</li> </ul>     | 800.000000         | 337.5 | FALSE    |

| <ul> <li>sync_pulse</li> </ul>      | 50.000000          | 10    | FALSE    |

| clk_ref                             | 200.000000         | 0     | TRUE     |

| AXI_DMA_Ethernet                    |                    |       | •        |

| <ul> <li>s_axi_lite_aclk</li> </ul> | 100.000000         | 0     | TRUE     |

| <ul> <li>m_axi_sg_aclk</li> </ul>   | 150.000000         | 0     | TRUE     |

| <ul> <li>m_AXI_MM2S_aclk</li> </ul> | 150.000000         | 0     | TRUE     |

| <ul> <li>m_axi_s2mm_aclk</li> </ul> | 150.000000         | 0     | TRUE     |

| Soft_Ethernet_MAC                   | 1                  | +     | +        |

| • S_AXI_ACLK                        | 100.000000         | 0     | TRUE     |

| AXI_STR_TXD_ACLK                    | 150.000000         | 0     | TRUE     |

| AXI_STR_TXC_ACLK                    | 150.000000         | 0     | TRUE     |

### Table 7: Clock Generator Configuration Settings (Cont'd)

| Component                                  | Frequency<br>(MHz) | Phase | Buffered   |

|--------------------------------------------|--------------------|-------|------------|

| AXI_STR_RXD_ACLK                           | 150.000000         | 0     | TRUE       |

| AXI_STR_RXS_ACLK                           | 150.000000         | 0     | TRUE       |

| • GTX_CLK                                  | 125.000000         | 0     | TRUE       |

| REF_CLK                                    | 200.000000         | 0     | TRUE       |

| axi_xadc_0                                 |                    |       |            |

| • S_AXI_ACLK                               | 100.000000         | 0     | TRUE       |

| logisdhc_0                                 |                    |       |            |

| <ul> <li>sd_base_clk</li> </ul>            | 100.000000         | 0     | TRUE       |

| • S_AXI_ACLK                               | 100.000000         | 0     | TRUE       |

| axi_tpg_dvi_0                              |                    | 1     | ł          |

| S_AXI_ACLK                                 | 100.000000         | 0     | TRUE       |

| • clk                                      | 150.000000         | 0     | TRUE       |

| DVI_0_2_AXI_SM                             |                    |       | - <b>h</b> |

| <ul> <li>fmc_hpc_dvidp_dvii_clk</li> </ul> | 150.000000         | 0     | TRUE       |

| <ul> <li>m_axi_s2mm_aclk</li> </ul>        | 150.000000         | 0     | TRUE       |

| DVI_IN_0_VDMA                              |                    |       | <u> </u>   |

| <ul> <li>s_axis_s2mm_aclk</li> </ul>       | 150.000000         | 0     | TRUE       |

| <ul> <li>s_axi_lite_aclk</li> </ul>        | 100.000000         | 0     | TRUE       |

| <ul> <li>m_axi_s2mm_aclk</li> </ul>        | 150.000000         | 0     | TRUE       |

| SCALER_0_VDMA                              |                    | 1     |            |

| <ul> <li>s_axis_s2mm_aclk</li> </ul>       | 150.000000         | 0     | TRUE       |

| m_axis_mm2s_aclk                           | 150.000000         | 0     | TRUE       |

| <ul> <li>m_axi_s2mm_aclk</li> </ul>        | 150.000000         | 0     | TRUE       |

| <ul> <li>m_AXI_MM2S_aclk</li> </ul>        | 150.000000         | 0     | TRUE       |

| <ul> <li>s_axi_lite_aclk</li> </ul>        | 100.000000         | 0     | TRUE       |

| SCALER_0                                   |                    | 1     |            |

| <ul> <li>m_AXI_MM2S_aclk</li> </ul>        | 150.000000         | 0     | TRUE       |

| <ul> <li>m_axi_s2mm_aclk</li> </ul>        | 150.000000         | 0     | TRUE       |

| timebase_0                                 |                    |       |            |

| <ul> <li>video_clk_in</li> </ul>           | 150.000000         | 0     | TRUE       |

| axi_tpg_0                                  |                    | 1     | ļ          |

| • S_AXI_ACLK                               | 100.000000         | 0     | TRUE       |

| • clk                                      | 150.000000         | 0     | TRUE       |

| TPG_0_SCALE_2_AXI_SM                       |                    | +     | ļ          |

| • fmc_hpc_dvidp_dvii_clk                   | 150.000000         | 0     | TRUE       |

| m_axi_s2mm_aclk                            | 150.000000         | 0     | TRUE       |

| TPG_0_VDMA                                 |                    | +     | ļ          |

| <ul> <li>s_axis_s2mm_aclk</li> </ul>       | 150.000000         | 0     | TRUE       |

| <ul> <li>s_axi_lite_aclk</li> </ul>        | 100.000000         | 0     | TRUE       |

| <ul> <li>m_axi_s2mm_aclk</li> </ul>        | 150.000000         | 0     | TRUE       |

### Table 7: Clock Generator Configuration Settings (Cont'd)

| Component                                  | Frequency<br>(MHz) | Phase | Buffered |

|--------------------------------------------|--------------------|-------|----------|

| axi_tpg_dvi_1                              |                    |       |          |

| • S_AXI_ACLK                               | 100.000000         | 0     | TRUE     |

| • clk                                      | 150.000000         | 0     | TRUE     |

| DVI_1_2_AXI_SM                             |                    |       | +        |

| <ul> <li>fmc_hpc_dvidp_dvii_clk</li> </ul> | 150.000000         | 0     | TRUE     |

| <ul> <li>m_axi_s2mm_aclk</li> </ul>        | 150.000000         | 0     | TRUE     |

| DVI_IN_1_VDMA                              |                    |       |          |

| <ul> <li>s_axis_s2mm_aclk</li> </ul>       | 150.000000         | 0     | TRUE     |

| <ul> <li>s_axi_lite_aclk</li> </ul>        | 100.000000         | 0     | TRUE     |

| <ul> <li>m_axi_s2mm_aclk</li> </ul>        | 150.000000         | 0     | TRUE     |

| SCALER_2_VDMA                              | I                  |       |          |

| <ul> <li>s_axis_s2mm_aclk</li> </ul>       | 150.000000         | 0     | TRUE     |

| <ul> <li>m_axis_mm2s_aclk</li> </ul>       | 150.000000         | 0     | TRUE     |

| <ul> <li>m_axi_s2mm_aclk</li> </ul>        | 150.000000         | 0     | TRUE     |

| • m_AXI_MM2S_aclk                          | 150.000000         | 0     | TRUE     |

| <ul> <li>s_axi_lite_aclk</li> </ul>        | 100.000000         | 0     | TRUE     |

| SCALER_2                                   | I                  |       |          |

| <ul> <li>m_AXI_MM2S_aclk</li> </ul>        | 150.000000         | 0     | TRUE     |

| <ul> <li>m_axi_s2mm_aclk</li> </ul>        | 150.000000         | 0     | TRUE     |

| axi_tpg_2                                  |                    |       |          |

| • S_AXI_ACLK                               | 100.000000         | 0     | TRUE     |

| • clk                                      | 150.000000         | 0     | TRUE     |

| TPG_2_SCALE_2_AXI_SM                       |                    |       |          |

| <ul> <li>fmc_hpc_dvidp_dvii_clk</li> </ul> | 150.000000         | 0     | TRUE     |

| <ul> <li>m_axi_s2mm_aclk</li> </ul>        | 150.000000         | 0     | TRUE     |

| TPG_2_VDMA                                 | I                  |       |          |

| <ul> <li>s_axis_s2mm_aclk</li> </ul>       | 150.000000         | 0     | TRUE     |

| <ul> <li>s_axi_lite_aclk</li> </ul>        | 100.000000         | 0     | TRUE     |

| <ul> <li>m_axi_s2mm_aclk</li> </ul>        | 150.000000         | 0     | TRUE     |

| CVC_DISPLAY                                | I                  |       |          |

| • S_AXI_ACLK                               | 100.000000         | 0     | TRUE     |

| • mclk                                     | 150.000000         | 0     | TRUE     |

| • vclk                                     | 150.000000         | 0     | TRUE     |

| dvi_24_to_16bit_ycbcr_0                    | I                  |       |          |

| • clk                                      | 150.000000         | 0     | TRUE     |

| Top-Level Output Clock Po                  | orts               |       | 1        |

| • ddr_ck                                   | 800.000000         | 0     | FALSE    |

| • sd_clk                                   | 12.500000          | 0     | FALSE    |

| <ul> <li>hdmi_clk</li> </ul>               | 150.000000         | 0     | FALSE    |

#### Reset

Configuration details are the same as in the BIST system (see Reset, page 8).

#### **MicroBlaze Processor Configuration**

Configuration details are the same as in the BIST system (see MicroBlaze Processor Configuration, page 8).

#### **Dual Timer/Counter**

Configuration details are the same as in the BIST system (see Dual Timer/Counter, page 9).

#### debug\_module

Configuration details are the same as in the BIST system (see debug\_module, page 9).

#### axi\_bram\_ctrl Configuration

Configuration details are the same as in the BIST system (see axi\_bram\_ctrl Configuration, page 9).

#### axi\_7series\_ddrx Configuration

Configuration details are the same as in the BIST system (see axi\_7series\_ddrx Configuration, page 10).

#### **IIC Controller Configuration**

Configuration details are the same as in the BIST system (see IIC Controller Configuration, page 10).

#### Linear Flash Controller Configuration

Configuration details are the same as in the BIST system (see Linear Flash Controller Configuration, page 10).

#### **GPIO Configuration**

Configuration details are the same as in the BIST system (see GPIO Configuration, page 10).

#### **UART** Configuration

Configuration details are the same as in the BIST system (see UART Configuration, page 10).

#### axi\_dma

Configuration details are the same as in the BIST system (see axi\_dma, page 10).

#### **Ethernet Configuration**

Configuration details are the same as in the BIST system (see Ethernet Configuration, page 11).

#### axi\_xadc Configuration

Configuration details are the same as in the BIST system (see axi\_xadc Configuration, page 11).

#### logisdhc Configuration

Configuration details are the same as in the BIST system (see logisdhc Configuration, page 11).

#### **AXI Interconnect Configuration**

Two types of interconnects are implemented in the system. The AXI\_MM type interconnect is for masters and slaves that fully utilize the AXI4 protocol for high-throughput data exchange. The AXI\_Lite type is for masters and slaves that are geared for the AXI4-Lite protocol (32-bit interface, supports only single transactions).

Four AXI\_MM interconnects (axi4\_0, axi\_mm\_mb, axi\_mm\_video12, and axi\_mm\_video34) are connected in a hierarchical fashion. This allows for better timing closure and expansion of current hardware to support more AXI masters. It also helps in floorplanning of the design. The axi4\_0 interconnect is configured for 512-bit width and operates at 200 MHz. A total of 12 masters are connected in the design, and the DDRX controller is the only slave connected to axi4\_0 that is accessible to all the masters.

The design is partitioned so that the MicroBlaze processor and Ethernet DMA are connected to axi\_mm\_mb, the first two video pipelines (four VDMA masters) are connected to axi\_mm\_video12, the last two video pipelines (four VDMA masters) are connected to axi\_mm\_video34, and finally, the three interconnects are connected to the axi4\_0 interconnect through the axi2axi connector. Apart from this, the logiCVC display controller is another master on the axi4\_0 interconnect. This design can be expanded to support more video pipelines to either axi\_mm\_video12 or axi\_mm\_video34 interconnects. Each of these two interconnects can support 12 more masters.

Two AXI\_Lite interconnects (axi4lite\_0 and axi4lite\_1) are connected in hierarchical fashion. The MicroBlaze processor is the master for axi4lite\_0, and through the axi2axi connector, axi4lite\_1 is connected as one of the slaves to axi4lite\_0. Slaves connected to this interconnect have register maps or user logic that does not contain high-speed logic like bursting. A total of 32 slaves are connected to the MicroBlaze processor through these two interconnects. All interconnects are configured for 32-bit widths and operate at 100 MHz. The axi\_gpio and axi\_timer IP cores are examples of slaves connected to the axi4lite\_0 interconnect.

#### Video Source Select

Video Source Select multiplexes between internally generated test patterns or external video. The output of this block is given to the DVI2AXI block. Selection is through a GPIO register bit (position 4 of the GPIO reset register: 0x40C00000). Two instances of this block handle multiplexing of the two external video streams.

#### **Video Timing Controller**

The v\_tc is one of the AXI\_Lite slaves to the MicroBlaze processor connected through the axi4lite\_0 interconnect. Time base is configured to work in generate mode by setting the parameter GENERATE\_EN. It is configured to generate timing control signals for a video resolution of 1080p. Timing control signals generated from this block are common for all the video test patterns generated internally.

#### DVI2AXI

This block converts a video input consisting of parallel video data, video syncs, blanks, and data enable to an AXI4-Stream<sup>™</sup> master bus that follows the AXI4-Stream Video protocol. This functionality is achieved using Video In to AXI4-Stream core. This core handles the asynchronous clock boundary crossing between the video clock domain and the AXI4-Stream clock domain. Two instances of this IP are implemented in the system to support two external video streams.

### AXI\_SCALAR

This block scales down the video frame by a factor of four, i.e., from a 1920 x 1080 input resolution, AXI\_SCALAR generates video with a resolution of 960 x 540. It has two streaming interfaces that are connected to the S2MM and MM2S channels of Scalar VDMA. Two instances of this IP are connected to scale two video pipelines.

#### DVI\_SCALAR

This block scales down the video frame by a factor of four. The functionality of DVI\_SCALAR is the same as AXI\_SCALAR, provided it scales the video image dynamically before writing it into the memory. However, AXI\_SCALAR reads the frame from memory, scales it, and writes it back to the frame in a different location of the memory. The input interface of this block is the DVI interface, and the output interface is a streaming interface towards the S2MM channel of the TPG VDMA. Two instances of this IP are connected to two scale video pipelines.

#### axi\_tpg

The axi\_tpg contains one AXI4-Lite interface slave connection. The master connected to the axi\_tpg on the axi4lite\_0 interconnect is the MicroBlaze processor DP. Different video patterns can be generated inside the FPGA by configuring pattern select registers. Four instances of the IP are implemented in the system to generate four different test patterns.

### DVI\_IN\_0\_VDMA

DVI\_IN\_0\_VDMA has two interfaces: one is the 32-bit streaming interface towards the DVI2AXI block, and the other is a 64-bit AXI MM interface towards the axi\_mm\_video12 interconnect. The S2MM channel is enabled, and the C\_PRMRY\_IS\_ACLK\_ASYNC parameter is set because the clocks connected to the VDMA are of different frequencies. User register slices on all channels are set to 8. The S2MM line buffer is set to 4096, and the burst length is set to 256. Write FIFO delay in the interconnect settings is enabled with a FIFO delay of 512. The AXI MM and AXI Streaming interfaces

operate at 150 MHz, and the AXI-Lite interface operates at 100 MHz. The MicroBlaze processor acts as a master for the Lite interface of the VDMA that is used for register configuration.

### SCALER\_0\_VDMA

SCALER\_0\_VDMA has four interfaces: two are 32-bit streaming interfaces towards the AXI\_SCALAR block, and the other two are a 64-bit AXI MM interface towards the axi\_mm\_video12 interconnect. Both S2MM and MM2S channels are enabled, and the C\_PRMRY\_IS\_ACLK\_ASYNC parameter is set because clocks connected to the VDMA are of different frequencies. User register slices on all channels are set to eight. The S2MM line buffer is set to 4096, and burst length is set to 256. The MM2S line buffer is set to 256, and the burst length is set to 256. Write FIFO delay in the interconnect settings is enabled with a FIFO delay of 512. The AXI MM and AXI Streaming interfaces operate at 150 MHz, and the AXI-Lite interface operates at 100 MHz. The MicroBlaze processor acts as a master for the Lite interface of the VDMA that is used for register configuration.

### TPG\_0\_VDMA

TPG\_0\_VDMA has two interfaces: one is the 32-bit streaming interface towards the DVI SCALAR block, and the other is the 64-bit AXI MM interface towards the axi\_mm\_video12 interconnect. The S2MM channel is enabled, and the C\_PRMRY\_IS\_ACLK\_ASYNC parameter is set because clocks connected to the VDMA are of different frequencies. User register slices on all channels are set to 8. The S2MM line buffer is set to 4096, and the burst length is set to 256. Write FIFO delay in the interconnect settings are enabled with a FIFO delay of 512. The AXI MM and AXI Streaming interfaces operate at 150 MHz, and the AXI-Lite interface operates at 100 MHz. The MicroBlaze processor acts as a master for the Lite interface of the VDMA that is used for register configuration.

### DVI\_IN\_1\_VDMA

DVI\_IN\_1\_VDMA has two interfaces: one is the 32-bit streaming interface towards the DVI2AXI block, and the other is a 64-bit AXI MM interface towards the axi\_mm\_video34 interconnect. The S2MM channel is enabled and the C\_PRMRY\_IS\_ACLK\_ASYNC parameter is set because clocks connected to the VDMA are of different frequencies. User register slices on all channels are set to 8. The S2MM line buffer is set to 4096, and the burst length is set to 256. Write FIFO delay in the interconnect settings is enabled with a FIFO delay of 512. The AXI MM and AXI Streaming interfaces operate at 150 MHz, and the AXI-Lite interface operates at 100 MHz. The MicroBlaze processor acts as a master for the Lite interface of the VDMA that is used for register configuration.

### SCALER\_2\_VDMA

SCALER\_2\_VDMA has four interfaces: two are 32-bit streaming interfaces towards the AXI SCALAR block, and the other two are a 64-bit AXI MM interface towards the axi\_mm\_video34 interconnect. Both the S2MM and MM2S channels are enabled, and the C\_PRMRY\_IS\_ACLK\_ASYNC parameter is set because clocks connected to VDMA are of different frequencies. User register slices on all channels are set to 8. The S2MM line buffer is set to 4096, and the burst length is set to 256. The MM2S line buffer is set to 256, and the burst length is set to 256. Write FIFO delay in the interconnect settings is enabled with a FIFO delay of 512. The AXI MM and AXI Streaming interfaces operate at 150 MHz, and the AXI-Lite interface operates at 100 MHz. The MicroBlaze processor acts as a master for the Lite interface of the VDMA that is used for register configuration.

### TPG\_2\_VDMA

TPG\_2\_VDMA has two interfaces: one is the 32-bit streaming interface towards the DVI SCALAR block, and the other is a 64-bit AXI MM interface towards the axi\_mm\_video34 interconnect. The S2MM channel is enabled, and the C\_PRMRY\_IS\_ACLK\_ASYNC parameter is set because clocks connected to the VDMA are of different frequencies. User register slices on all channels are set to 8. The S2MM line buffer is set to 4096, and the burst length is set to 256. Write FIFO delay in the interconnect settings is enabled with a FIFO delay of 512. The AXI MM and AXI Streaming interfaces operate at 150 MHz, and the AXI-Lite interface operates at 100 MHz. The MicroBlaze processor acts as a master for the Lite interface of the VDMA that is used for register configuration.

### CVC\_DISPLAY

CVC\_DISPLAY is a third-party display controller from Xylon. It has three interfaces: an AXI4-Lite interface slave connection controlled by the MicroBlaze processor, an AXI MM interface towards the AXI MM interconnect, and a video output interface towards the 24bit\_16bit\_ycbcr converter. The AXI MM data width is configured as 128. Configured for five layers, which includes one background layer, the data width of all the layers is configured as 24 bits. User register slices on all channels

are set to 8. The FIFO depth towards the interconnect is set as 512. Frame sync for each layer is controlled by the frame sync out of the VDMAs corresponding to each video pipeline.

#### Interrupt Controller Configuration

The axi\_intc contains one AXI4-Lite interface slave connection. The master connected to the axi\_intc on the axi4lite\_0 interconnect is the MicroBlaze processor DP. Table 8 shows the internal interrupts generated in the embedded system and the priority ordering of the interrupts.

#### Table 8: MicroBlaze Processor Subsystem Interrupt Priorities

| Signal                                       | Source        | Description                                                                                                          |

|----------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------|

| AXI_DMA_Ethernet_mm2s_introut <sup>(1)</sup> | axi_dma       | Transmit complete interrupt from the DMA.                                                                            |

| AXI_DMA_Ethernet_s2mm_introut                | axi_dma       | Receive complete interrupt from the DMA.                                                                             |

| Soft_Ethernet_MAC_INTERRUPT                  | axi_ethernet  | Interrupt condition in the Ethernet has occurred, as indicated in the TEMAC Interrupt Status register.               |

| Dual_Timer_Counter_Interrupt                 | axi_timer     | In Generate mode, indicates that the counter rolled over. In Capture mode, the interrupt event is the capture event. |

| IIC_EEPROM_Intr                              | axi_iic       | Interrupt condition in the IIC controller has occurred, as indicated in the IIC Interrupt Status register.           |

| RS232_Uart_1_Intr                            | axi_uart16550 | Interrupt condition in the UART 16550 has occurred, as indicated in the UART Interrupt Identification register.      |

| logisdhc_0_interrupt                         | logisdhc      | Interrupt from SDHC controller.                                                                                      |

| DVI_IN_0_VDMA_s2mm_introut                   | DVI_IN_0_VDMA | S2MM interrupt from DVI_IN_0 VDMA.                                                                                   |

| SCALER_0_VDMA_mm2s_introut                   | SCALER_0_VDMA | MM2S interrupt from Scaler_0 VDMA.                                                                                   |