# **Versal ACAP**

# **Technical Reference Manual**

AM011 (v1.4) April 26, 2022

Xilinx is creating an environment where employees, customers, and partners feel welcome and included. To that end, we're removing non-inclusive language from our products and related collateral. We've launched an internal initiative to remove language that could exclude people or reinforce historical biases, including terms embedded in our software and IPs. You may still find examples of non-inclusive language in our older products as we work to make these changes and align with evolving industry standards. Follow this <a href="link">link</a> for more information.

# **Table of Contents**

| Section 1: Introduction                         | 17 |

|-------------------------------------------------|----|

| Chapter 1: Introduction to Versal ACAP          | 18 |

| Chapter 2: Navigating Content by Design Process | 20 |

| Chapter 3: Device Overview                      | 22 |

| Device-Level Block Diagram                      | 24 |

| Processing System                               | 26 |

| Platform Management Controller                  | 26 |

| Applications                                    | 28 |

| Software Code and Data Files                    | 28 |

| System Performance                              | 30 |

| Device Comparisons and IP Revisions             | 32 |

| Chapter 4: Documentation                        | 38 |

| Versal ACAP Technical Reference Manual Outline  | 38 |

| Additional Documents                            | 40 |

| Xilinx Documentation Navigator                  | 41 |

| Section II: Hardware Architecture               | 42 |

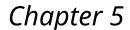

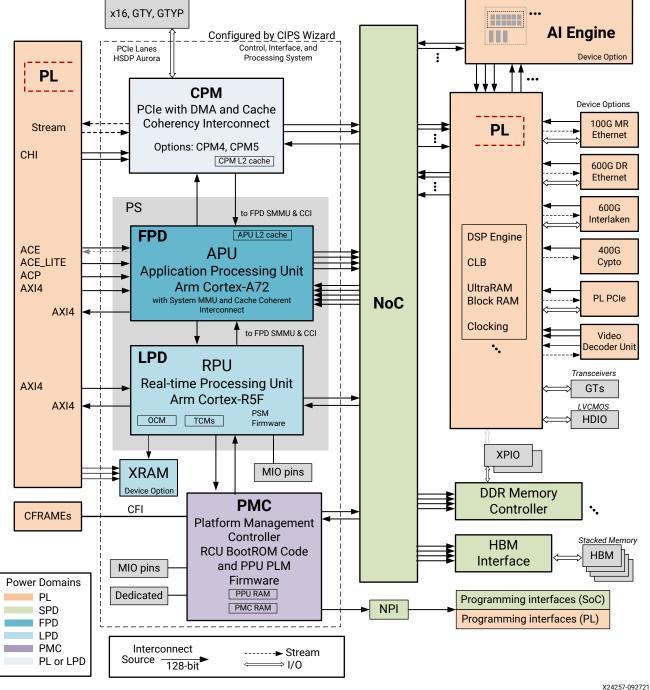

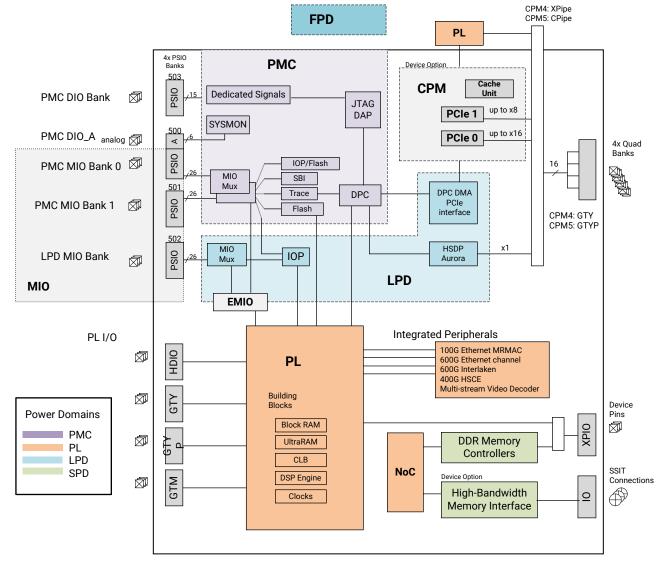

| Chapter 5: High-level Interconnect Diagrams     | 43 |

| Device-Level Interconnect Diagram               | 43 |

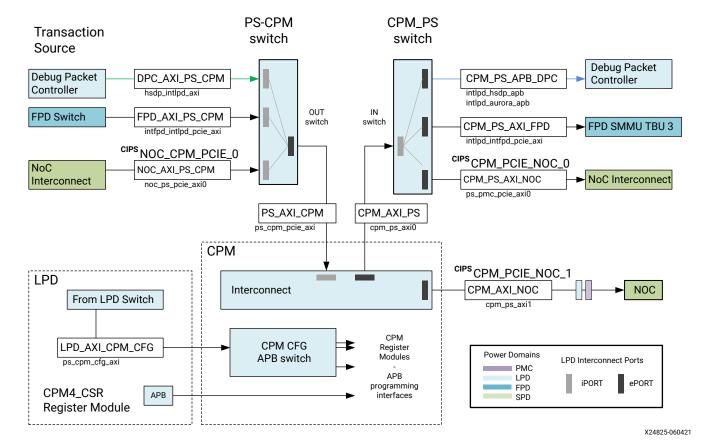

| PMC-PS-CPM Interconnect Diagram                 | 45 |

| Chapter 6: PMC and PS Architectures             | 47 |

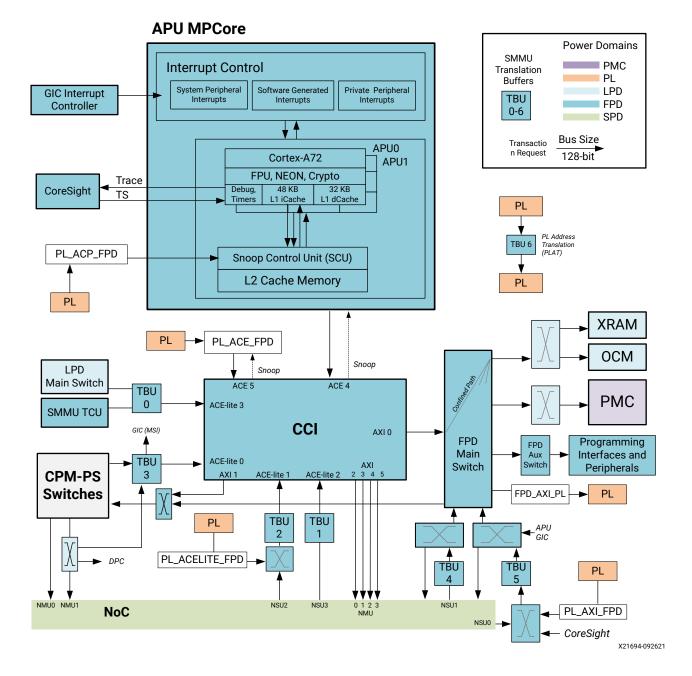

| PS FPD Architecture                             | 48 |

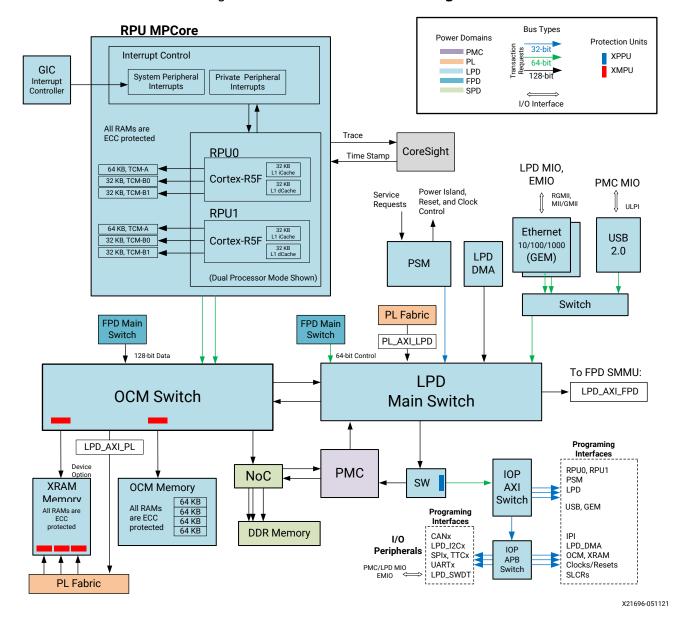

| PS LPD Architecture                             | 51 |

| PMC Architecture                                | 54 |

| Chapter 7: Integrated Hardware                  | 63 |

|                                                 |    |

| DDR4 Memory Controller                          | 63 |

|-------------------------------------------------|----|

| PL Building Blocks                              | 63 |

| Network on Chip Interconnect                    | 64 |

| Embedded Memories                               | 64 |

| Test and Debug                                  | 65 |

| Chapter 8: Integrated Hardware Options          | 66 |

| Summary of Hardware Options                     | 66 |

| AI Engine                                       | 66 |

| Accelerator RAM                                 | 67 |

| High-Bandwidth Memory Interface                 | 67 |

| Chapter 9: Integrated Peripheral Options        | 68 |

| 100G Multirate Ethernet MAC                     | 68 |

| 600G Channelized Multirate Ethernet             | 69 |

| 600G Interlaken with FEC                        | 69 |

| 400G High-Speed Crypto Engine                   | 70 |

| Multistream Video Decoder Unit                  | 70 |

| Chapter 10: PL Fabric Overview                  | 71 |

| PL Block Diagram                                | 72 |

| Adaptable Engines in PL                         | 74 |

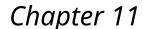

| Chapter 11: Device I/O Connectivity             | 76 |

| Device-Level Diagram                            | 76 |

| MIO and Dedicated I/O Banks                     | 77 |

| GTY and GTYP Pipe Transceivers                  | 79 |

| PL HDIO Banks                                   | 80 |

| DDR I/O Banks                                   | 81 |

| Chapter 12: Silicon Integrated into Package     | 83 |

| Monolithic Physical Layout Example              | 83 |

| Si Interposer Design for High-bandwidth Memory  | 84 |

| Section III: Platform Boot, Control, and Status | 86 |

| Chapter 13: Overview                            | 87 |

| Comparison to Previous Generation Devices       |    |

| Chapter 14: Non-Secure Boot Flow                   | 91  |

|----------------------------------------------------|-----|

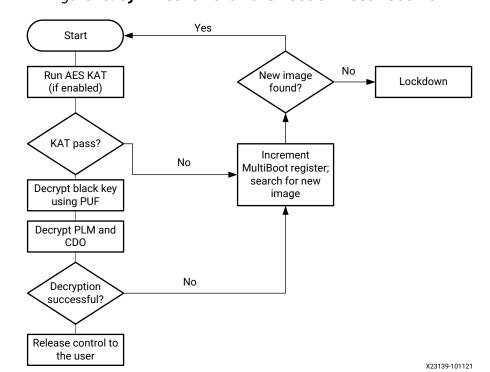

| Chapter 15: Secure Boot Flow                       | 95  |

| Asymmetric Hardware Root of Trust Secure Boot      |     |

| Symmetric Hardware Root of Trust Secure Boot       |     |

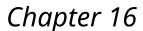

| Chapter 16: Boot Image                             | 103 |

| PDI Size Estimation                                |     |

| Boot Header                                        |     |

| Chapter 17: Boot Modes                             | 110 |

| JTAG Boot Mode                                     |     |

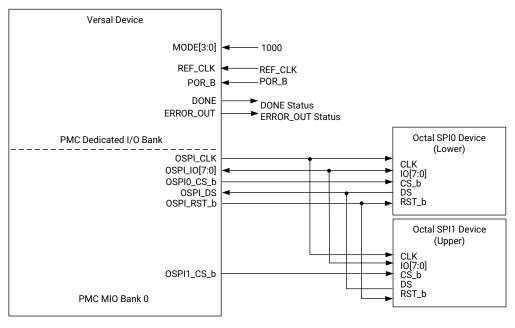

| Octal SPI Boot Mode                                |     |

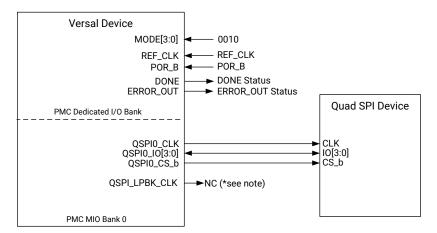

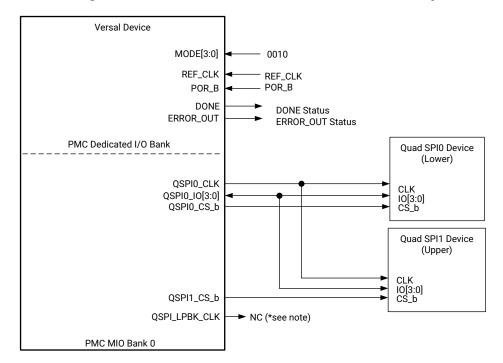

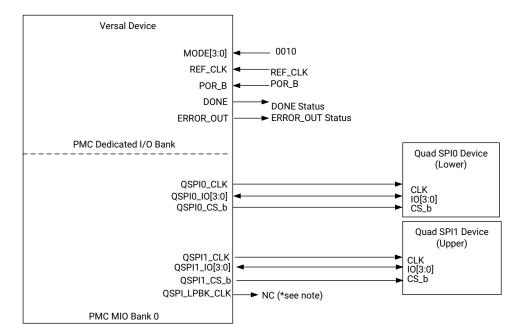

| Quad SPI Boot Mode                                 |     |

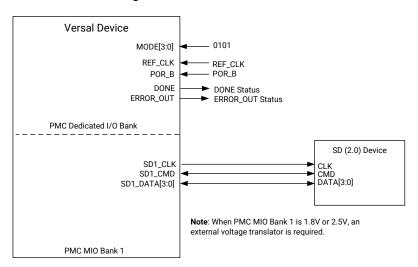

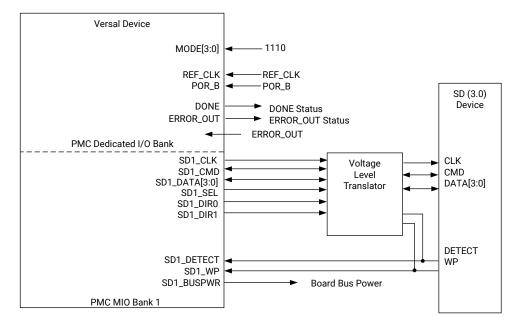

| SD Boot Modes                                      |     |

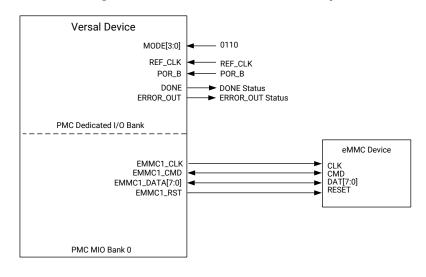

| eMMC1 Boot Mode                                    |     |

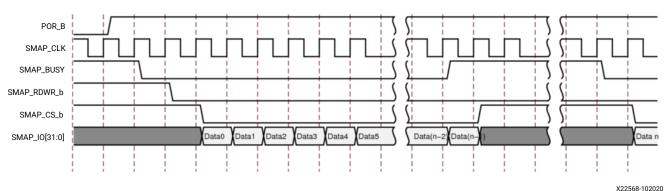

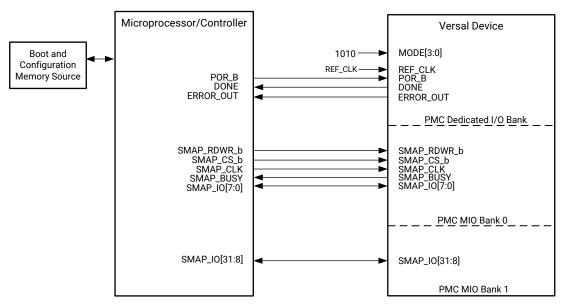

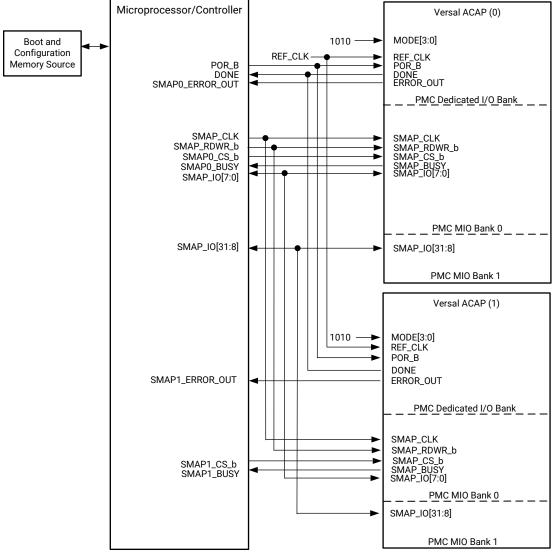

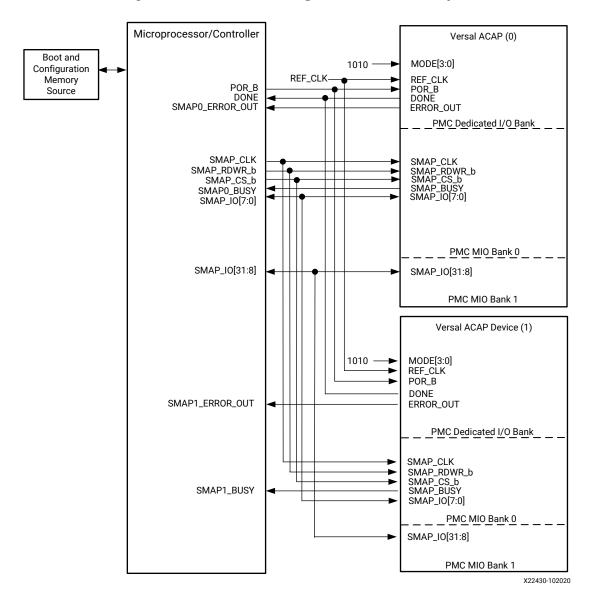

| SelectMAP Boot Mode                                |     |

| Chapter 18: Platform Management                    | 140 |

| Functional Safety Management                       |     |

| Dynamic Function eXchange                          | 143 |

| Power Management                                   | 143 |

| Security Management                                | 146 |

| PL Soft Error Mitigation                           | 153 |

| PMC and PS System Error Management                 | 153 |

| Chapter 19: Platform Hardware Reference            | 154 |

| Hardware Boot Events                               | 154 |

| Boot Header Register Initialization Feature        | 155 |

| Device State After RCU BootROM                     | 156 |

| PL-PMC GPI and GPO Port Signals                    | 157 |

| Software Platform Service Requests                 | 158 |

| Hardware Allocated to RCU BootROM Code             | 159 |

| Hardware Allocated to PLM Firmware                 | 160 |

| BootROM Error Code Table                           | 161 |

| Device Identification                              | 171 |

| ection IV: Address Maps and Programming Interfaces | 173 |

| Chapter 20: Address Maps                           | 174   |

|----------------------------------------------------|-------|

| High-level Address Map                             | 177   |

| 4 GB Address Map by Address                        | 179   |

| 4 GB Address Map by Name                           | 203   |

| NoC Address Map                                    | 228   |

| Chapter 21: Register Programming Interfaces        | 5230  |

| List of Programming Interfaces by Block            | 230   |

| APB, AXI Programming Interfaces                    | 231   |

| NPI Programming Interface                          | 232   |

| CFU Programming Interface                          | 233   |

| Chapter 22: NPI Register Modules                   | 234   |

| Section V: Signals, Interfaces, Pins, and Controls | S 236 |

| Chapter 23: Power and PMC Dedicated Pins           | 227   |

| Power Pins                                         |       |

| PMC Dedicated Pins                                 |       |

| Time Dedicated Final                               |       |

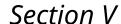

| Chapter 24: Multiplexed I/O Signals and Pins       | 241   |

| MIO-at-a-Glance                                    | 241   |

| MIO Routing Considerations                         | 246   |

| MIO-EMIO Interface Routing Options                 | 246   |

| MIO Pin Buffer Controls                            | 248   |

| MIO Pin Routing                                    | 250   |

| MIO Pin Programming Example                        | 253   |

| PCIe Reset on MIO                                  | 254   |

| Section VI: Engines                                | 255   |

| Chapter 25: Overview                               | 256   |

| Scalar Engines                                     |       |

| Intelligent Engines                                | 257   |

| Adaptable Engines                                  | 258   |

| DMA Units                                          | 258   |

| Chapter 26: Processor Support Units                | 259   |

| 1- 3                                               |       |

| Processor Communications                | 259 |

|-----------------------------------------|-----|

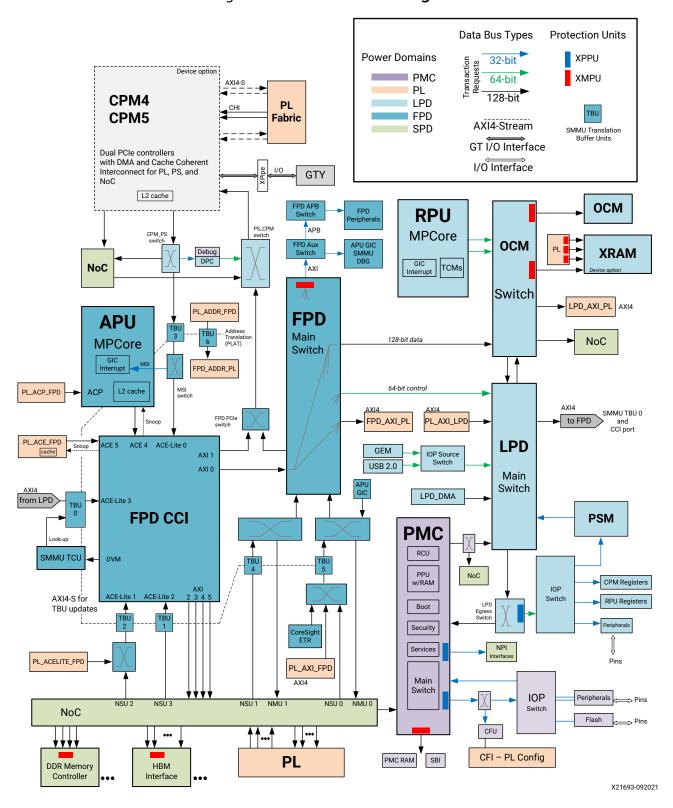

| Chapter 27: Application Processing Unit | 260 |

| Features                                |     |

| System Perspective                      |     |

| Memory Space                            | 265 |

| Execution Pipelines                     | 266 |

| APU Address Model                       |     |

| Virtualization                          | 268 |

| Server Architecture                     | 268 |

| Processor Counters                      | 269 |

| PS FPD Interrupts                       | 272 |

| Register Reference                      | 275 |

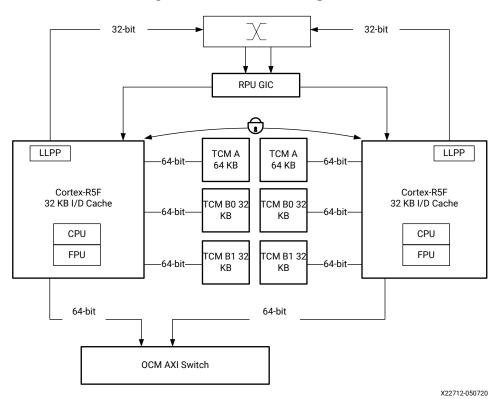

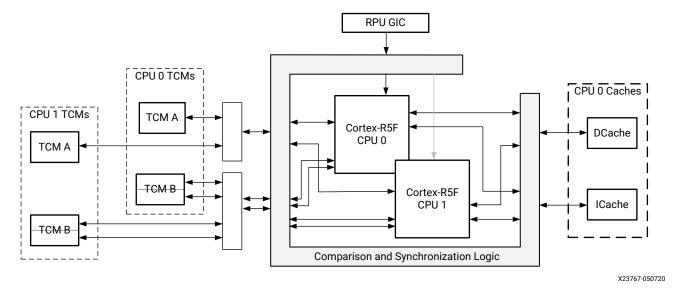

| Chapter 28: Real-time Processing Unit   | 277 |

| Features                                | 277 |

| Cortex-R5F Processor Implementation     | 278 |

| System Perspective                      | 278 |

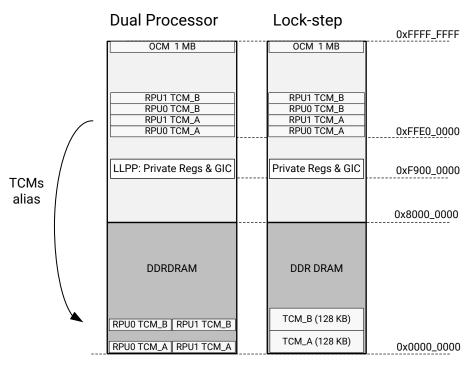

| Operating Modes                         | 279 |

| Power Modes and States                  | 281 |

| Address Maps                            | 282 |

| Processor Memory Datapaths              | 286 |

| Tightly-coupled Memories                | 287 |

| Memory Error Detection and Correction   | 287 |

| RPU Memory Protection Unit              | 288 |

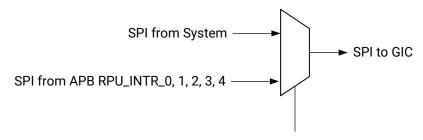

| Interrupts                              | 288 |

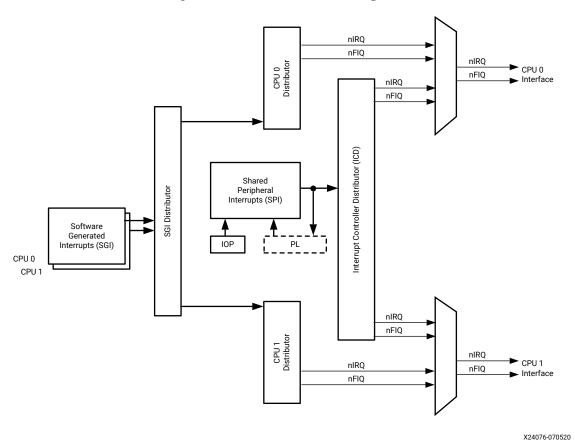

| GIC Interrupt Controller                | 290 |

| System Errors Generated by RPU          | 293 |

| Test and Debug                          | 293 |

| Register Reference                      | 294 |

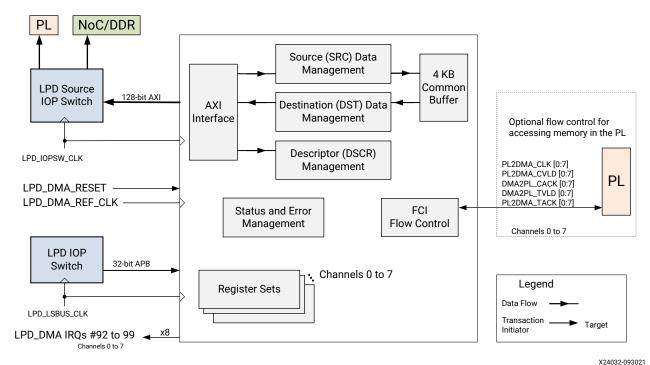

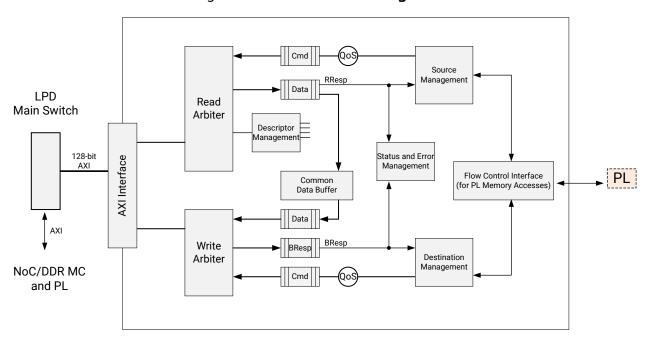

| Chapter 29: PS DMA Controller           | 296 |

| Features                                | 296 |

| System Perspective                      | 298 |

| Channel Block Diagram                   |     |

| Modes and States                        | 301 |

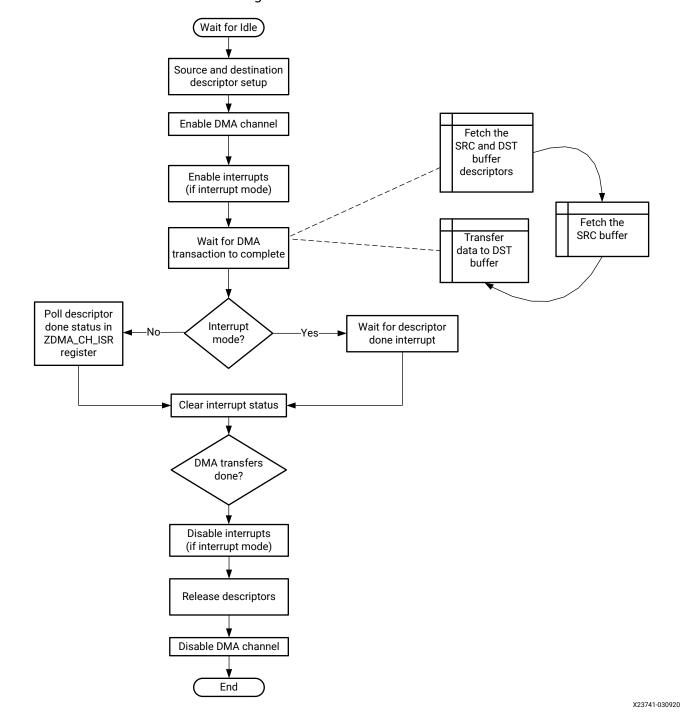

| Simple Mode Programming                 | 302 |

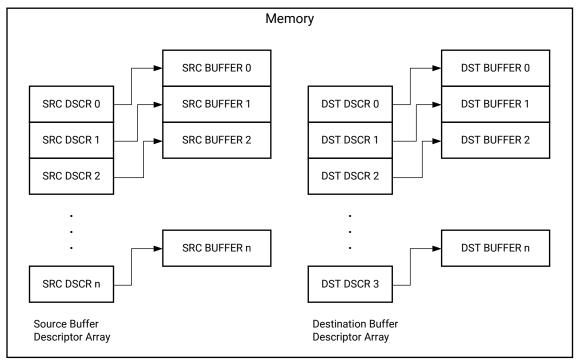

| Descriptor Mode Programming             | 304 |

| Done Interrupt Accounting               | 314 |

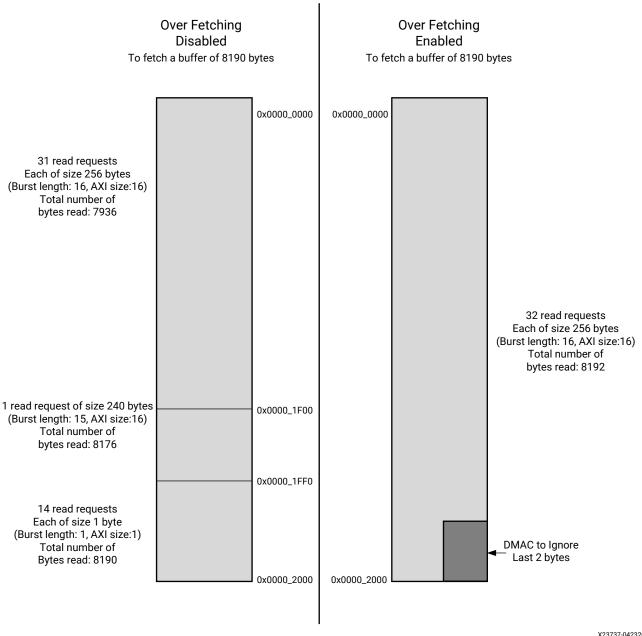

| Over Fetch                                          | 314 |

|-----------------------------------------------------|-----|

| Transaction Control                                 | 317 |

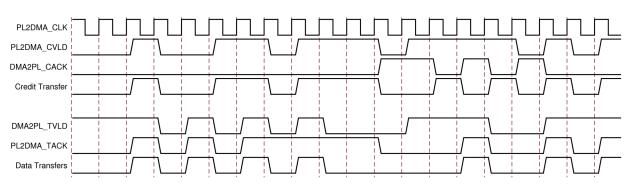

| PL Flow-Control Interface                           | 318 |

| Interrupts                                          | 323 |

| Transaction Security                                | 325 |

| Channel Pause                                       | 326 |

| Programming Model for Changing DMA Channel States   | 326 |

| Register Reference                                  | 328 |

| I/O Flow Control Signals                            | 329 |

| Section VII: Embedded Processor, Configuration, and | -   |

| Units                                               | 330 |

| Chapter 30: Overview                                | 331 |

| Chapter 31: Platform Processing Unit                | 333 |

| Features                                            | 333 |

| Programming Model                                   | 333 |

| Interrupts                                          | 334 |

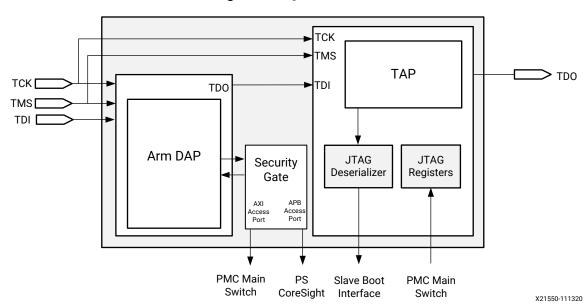

| Authenticated JTAG                                  | 335 |

| Tamper Event Monitoring and Response System         | 335 |

| PMC Register Reference                              | 335 |

| Chapter 32: Processing System Manager               | 340 |

| Features                                            | 340 |

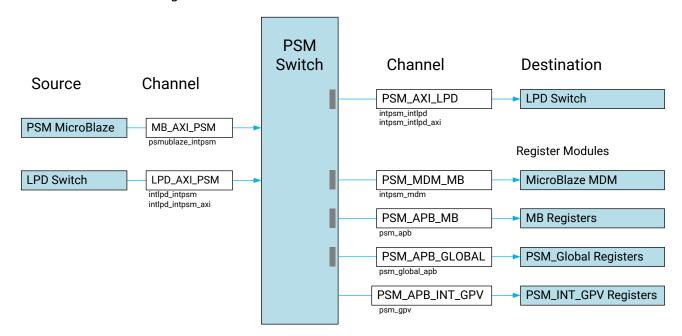

| System Perspective                                  | 340 |

| Interrupts                                          | 340 |

| Reset                                               | 341 |

| PSM Register Reference                              | 342 |

| Chapter 33: PL Configuration                        | 347 |

| Configuration Frame Unit                            | 347 |

| Configuration Frame Interface                       | 349 |

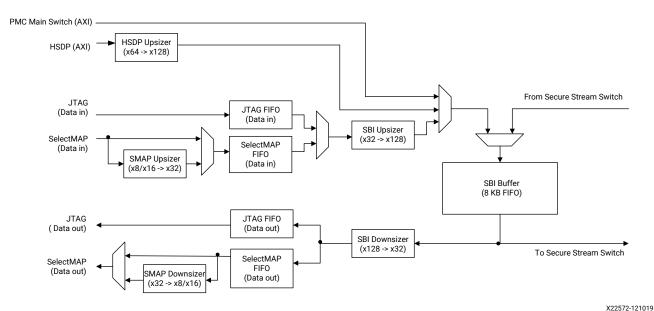

| Chapter 34: SBI for JTAG and SelectMAP              | 350 |

| Chapter 35: PMC Security Units                      | 351 |

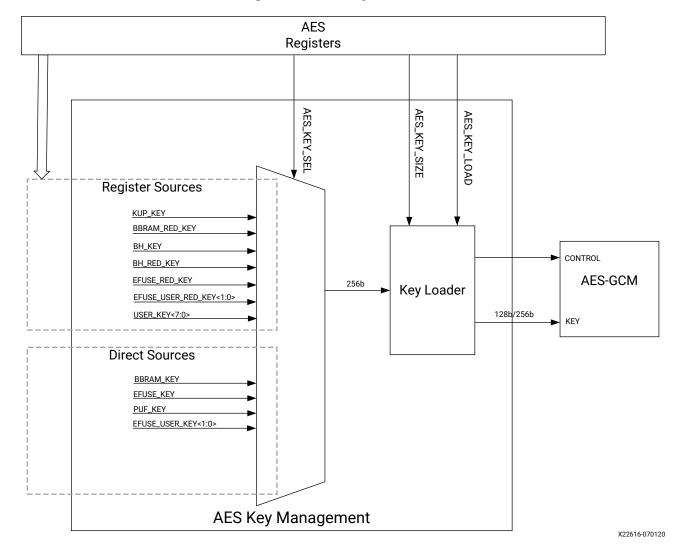

| AES-GCM                                             |     |

| SHA3-384                                            |     |

| RSA/ECDSA                                  | 352 |

|--------------------------------------------|-----|

| True Random Number Generator               | 353 |

| Physically Unclonable Function             | 354 |

| Chapter 36: Secure Stream Switch           | 355 |

| PMC DMAs                                   |     |

| Section VIII: Interconnect                 | 357 |

| Chapter 37: Overview                       | 358 |

| Features                                   | 359 |

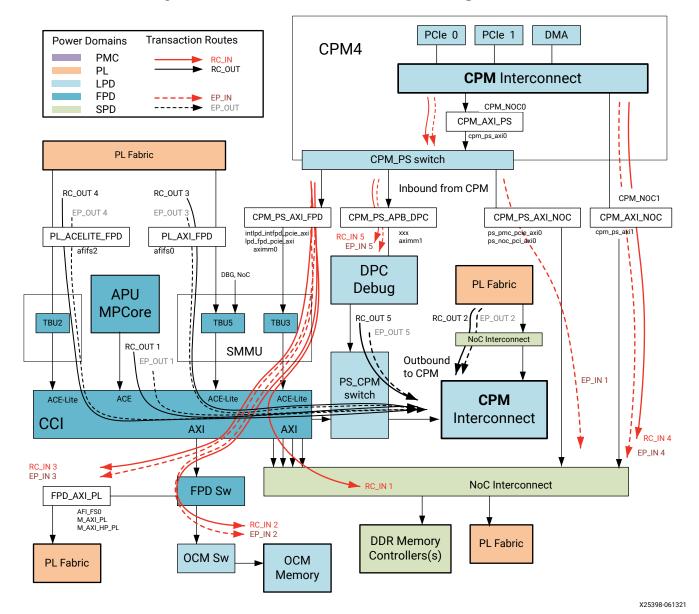

| System Perspective                         | 362 |

| Chapter 38: AXI Interconnect Switches      | 364 |

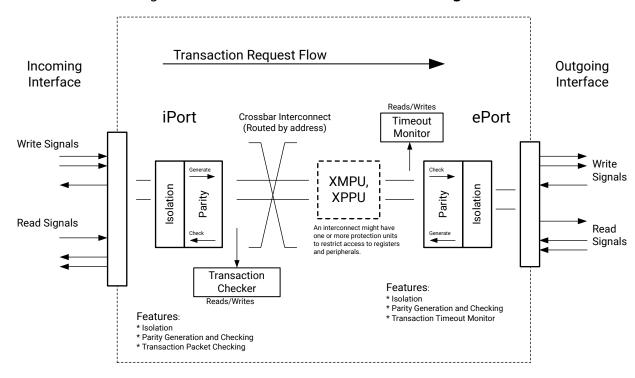

| Switch Architecture                        | 365 |

| Switch Ingress Ports                       | 367 |

| Switch Egress Ports                        | 369 |

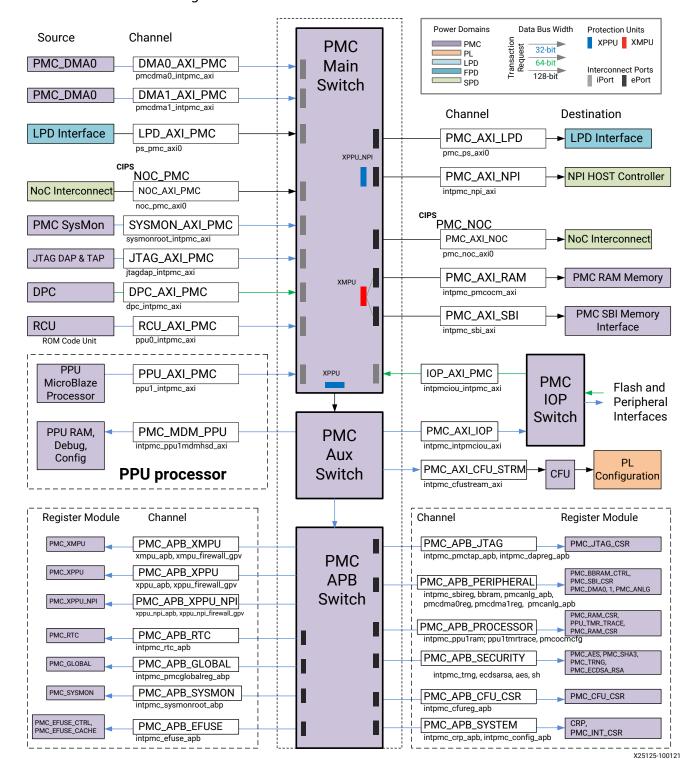

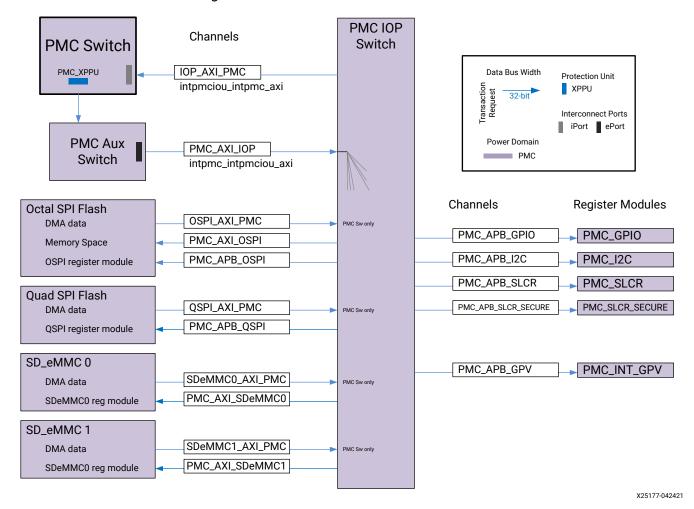

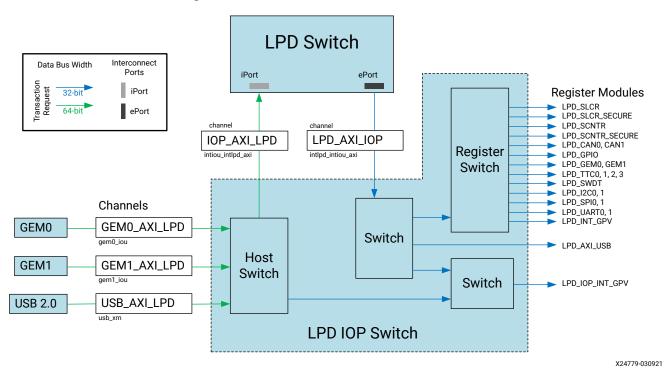

| Interconnect Switch Diagrams               | 372 |

| Interconnect Channels and Ports            | 380 |

| Interconnect Register Set Overview         |     |

| Chapter 39: Transaction Attributes         | 386 |

| Address                                    |     |

| Data                                       | 387 |

| System Management ID                       | 387 |

| TrustZone Security                         |     |

| AxCACHE                                    | 395 |

| Quality of Service                         | 396 |

| Safety Features                            | 397 |

| Poisoned Transaction                       | 398 |

| Chapter 40: Transaction Routes             | 399 |

| Routing and Coherency Controls             | 399 |

| CPM Transaction Route Use Cases            | 400 |

| CPM and CCI Transaction Route Restrictions | 403 |

| OSPI Direct Access by PMC DMA via CCI      | 405 |

| Chapter 41: PL Interconnect Interfaces     | 406 |

| PL to PS Interfaces                        | 406 |

| PS to PL Interfaces                           | 407 |

|-----------------------------------------------|-----|

| Register Reference                            | 408 |

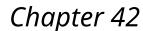

| Chapter 42: Shared Virtual Memory             | 409 |

| System Perspective                            |     |

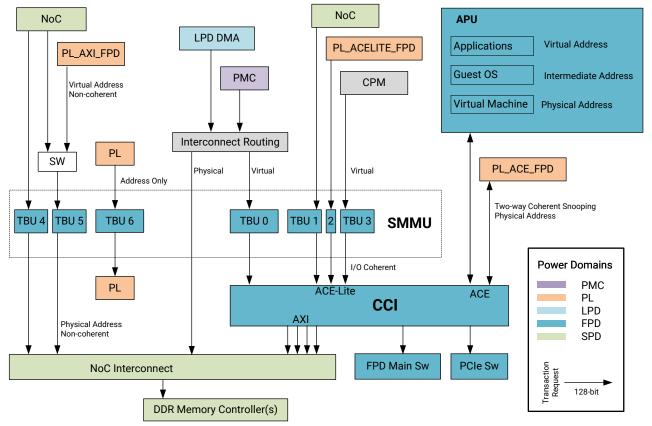

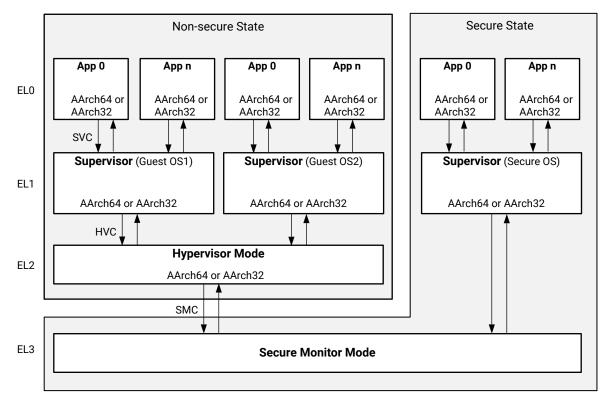

| APU Virtualization                            | 411 |

| Interrupt Virtualization                      | 414 |

| Chapter 43: System Memory Management Unit     | 415 |

| Features                                      | 415 |

| SMMU TBU Instances                            | 415 |

| Address Translation Examples                  | 416 |

| Memory Protection Functionality               | 417 |

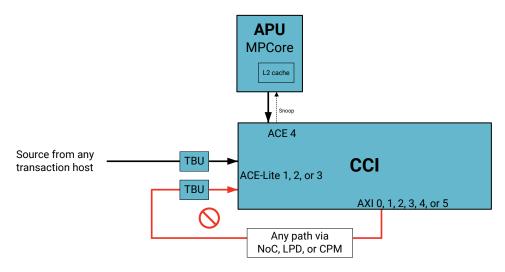

| Chapter 44: Cache Coherent Interconnect       | 418 |

| Features                                      | 420 |

| Cache Coherency                               | 421 |

| Snoop Filter                                  | 422 |

| AXI Outgoing Ports                            | 422 |

| Transaction Attribute Management              | 424 |

| CCI Register Reference                        | 424 |

| Chapter 45: Memory Space Protection           | 426 |

| Types of Protection Units                     | 426 |

| Protection Units                              | 427 |

| Use Case Example                              | 428 |

| TrustZone Security                            | 428 |

| Chapter 46: Xilinx Memory Protection Unit     | 429 |

| Features                                      | 430 |

| System Perspective                            | 431 |

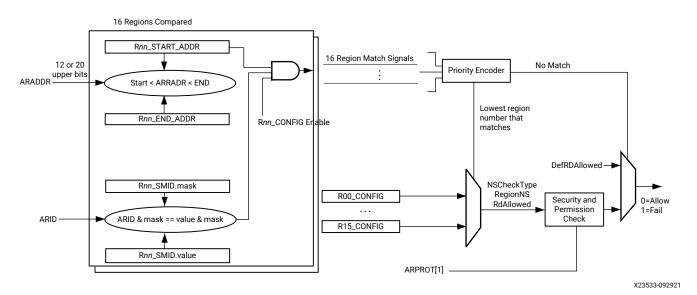

| Access Checking Operations                    | 433 |

| Error Handling                                | 434 |

| AXI Transaction Signals                       | 435 |

| Configuration                                 | 435 |

| XMPU Register Reference                       | 436 |

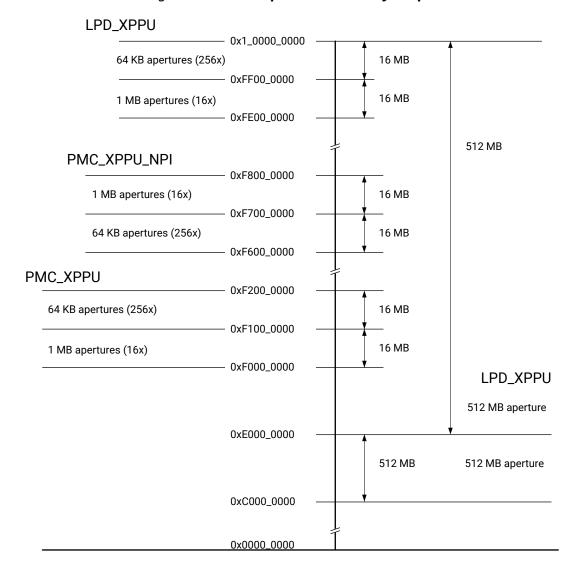

| Chapter 47: Xilinx Peripheral Protection Unit | 438 |

| Features                                      | 438 |

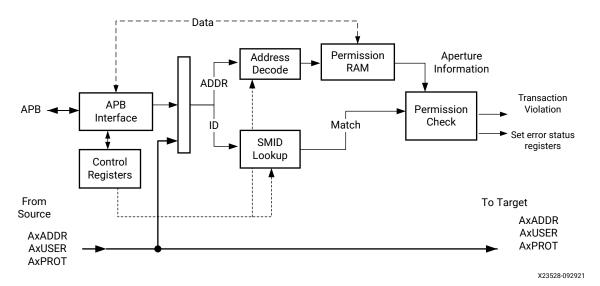

| System Perspective                     | 439 |

|----------------------------------------|-----|

| Transaction Checking Operations        | 441 |

| SMID Checking                          | 442 |

| Aperture Permission Checking           | 443 |

| Errors                                 | 444 |

| XPPU Register Reference                | 445 |

| Section IX: Interrupts and Errors      | 448 |

| Chapter 48: System Interrupts          | 449 |

| System Interrupt Controllers           | 449 |

| IRQ System Interrupts                  | 450 |

| Register Reference                     | 453 |

| Chapter 49: Inter-Processor Interrupts | 455 |

| Features                               | 456 |

| System Perspective                     | 458 |

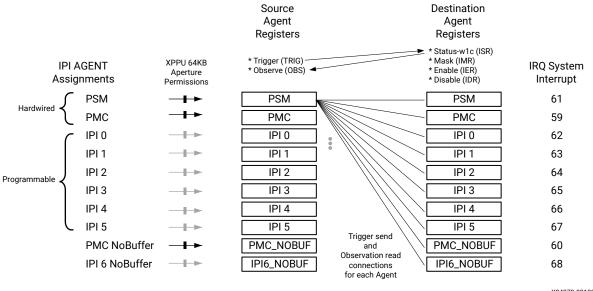

| List of Agents                         | 459 |

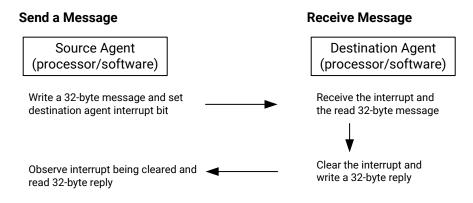

| Agent Communications                   | 459 |

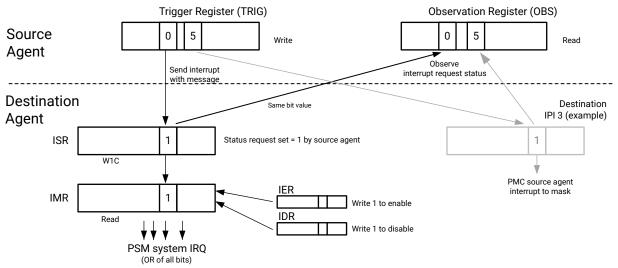

| Interrupt Architecture                 | 460 |

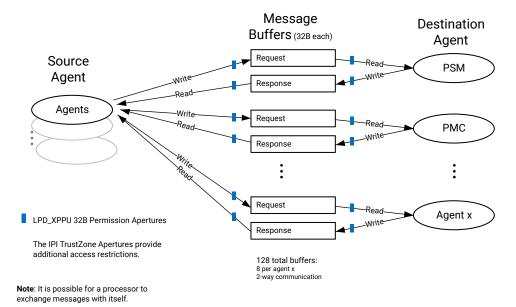

| Message Passing Architecture           | 462 |

| Register Reference and Address Map     | 464 |

| Programming Examples                   | 468 |

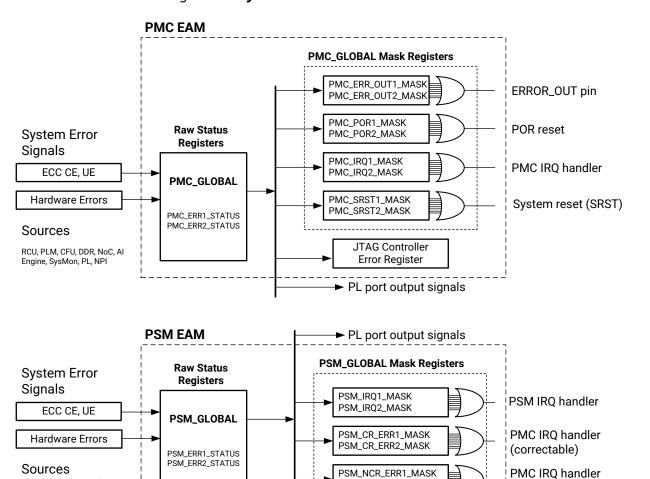

| Chapter 50: System Errors              | 470 |

| Error Accumulator Modules              | 472 |

| Types of Errors                        | 473 |

| System Error Accumulator Registers     | 475 |

| Programming Model                      | 481 |

| Section X: Timers, Counters, and RTC   | 483 |

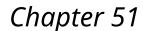

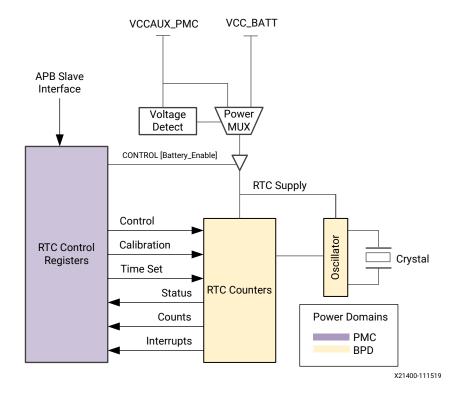

| Chapter 51: Real-Time Clock            | 484 |

| Features                               | 485 |

| Counter Module                         | 486 |

| Calibration                            | 486 |

| RTC Accuracy                           | 487 |

| Interfaces and Signals                 | 488 |

| Registers                              | 488 |

| Chapter 52: System Counters               | 490 |

|-------------------------------------------|-----|

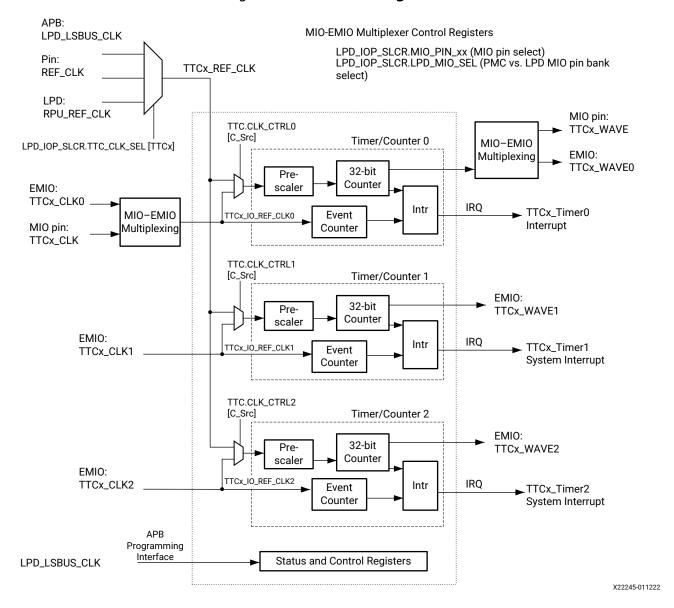

| Chapter 53: Triple-Timer Counters         | 492 |

| Features                                  | 492 |

| Block Diagram                             | 493 |

| Overflow Detection Functional Model       | 495 |

| Interval Timing Functional Model          | 496 |

| Event Timer Functional Model              | 496 |

| Register Reference                        | 497 |

| TTC I/O Signals                           | 498 |

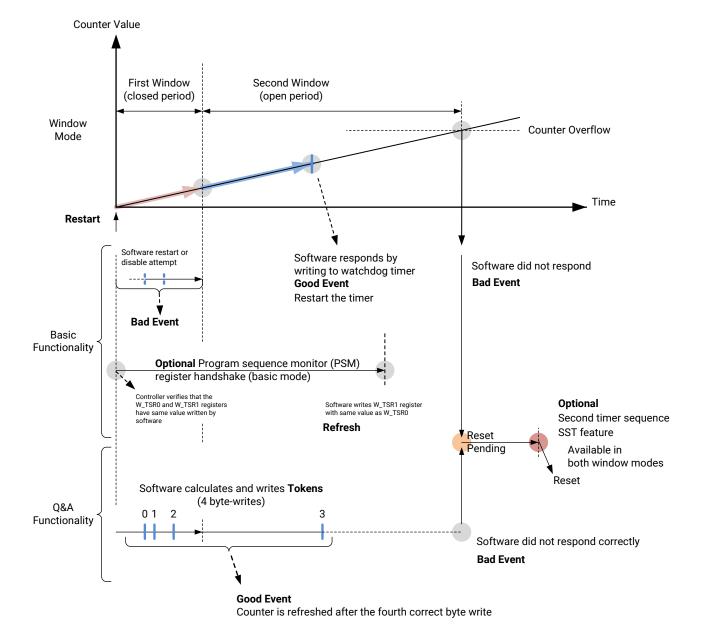

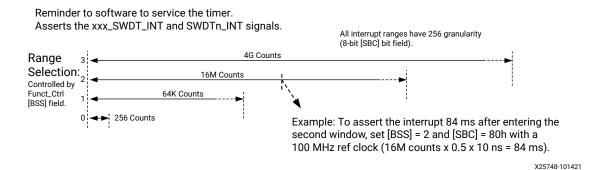

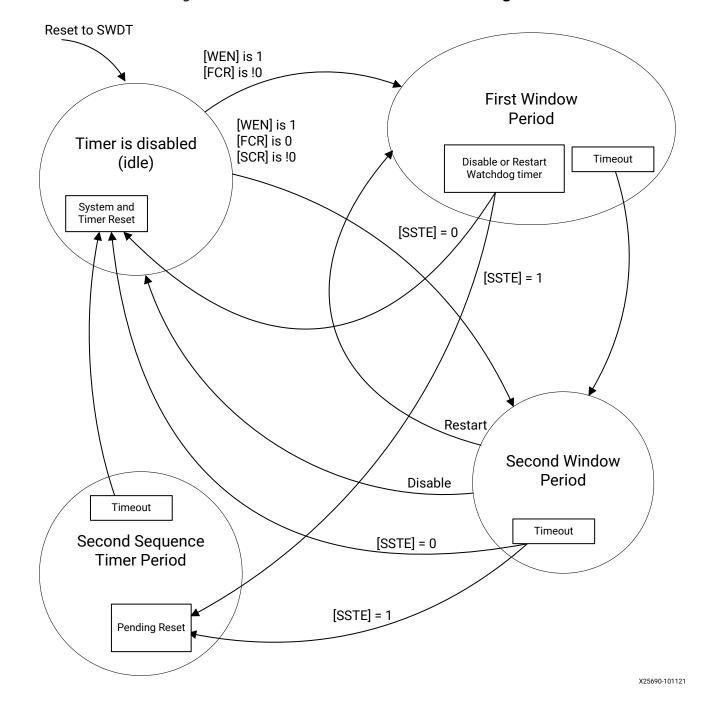

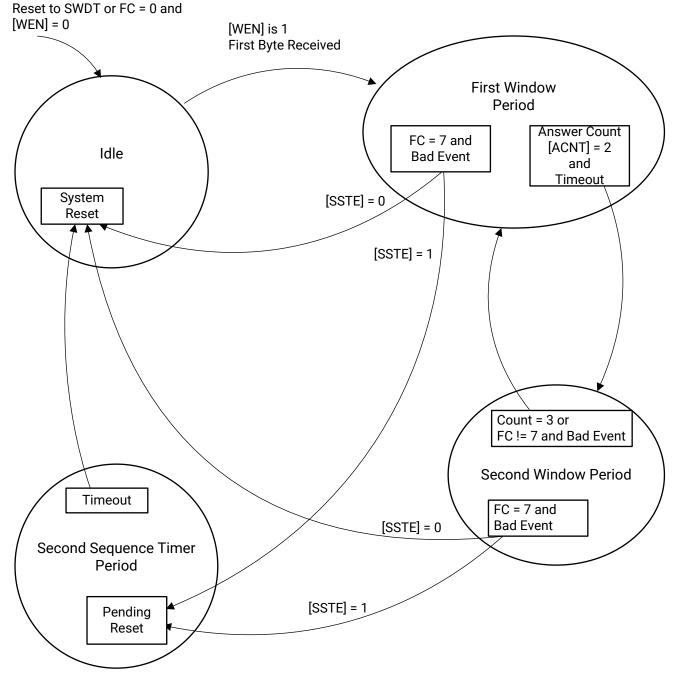

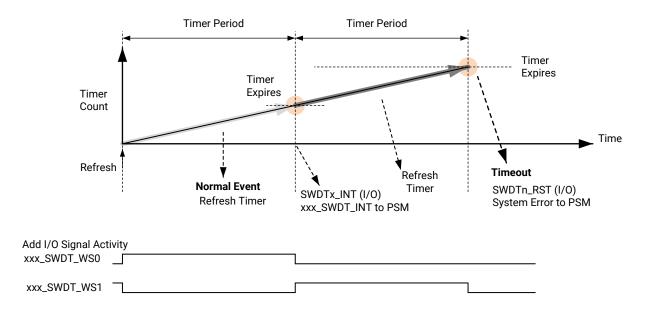

| Chapter 54: System Watchdog Timers        | 499 |

| Features                                  | 499 |

| System Perspective                        | 501 |

| Window Watchdog Timer Mode                | 506 |

| Generic Watchdog Timer Mode               | 518 |

| Register Reference                        | 520 |

| SWDT I/O Signals                          | 521 |

| ection XI: Memory                         | 523 |

| •                                         |     |

| Chapter 55: Overview                      | 524 |

| Chapter 56: On-Chip Memory                | 526 |

| Features                                  | 526 |

| System Perspective                        | 527 |

| States                                    | 527 |

| Address Map                               | 528 |

| Memory Address Protection                 | 528 |

| ECC Protection                            | 529 |

| ECC Operations                            | 529 |

| Chapter 57: Battery-Backed RAM            | 531 |

| Chapter 58: Accelerator RAM               | 533 |

| Chapter 59: External Memories             | 534 |

| Chapter 60: Embedded Addressable Memories | 535 |

| Chapter 61: Small Storage Elements      | 536 |

|-----------------------------------------|-----|

| Chapter 62: PL Memory Building Blocks   | 537 |

| Block RAM                               | 537 |

| UltraRAM                                | 538 |

| Section XII: I/O Peripheral Controllers | 540 |

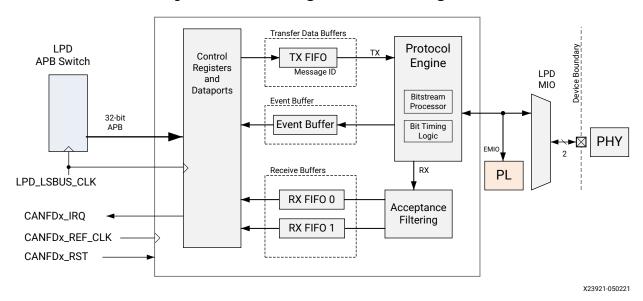

| Chapter 63: CAN FD Controller           | 541 |

| Features                                | 541 |

| System Perspective                      | 543 |

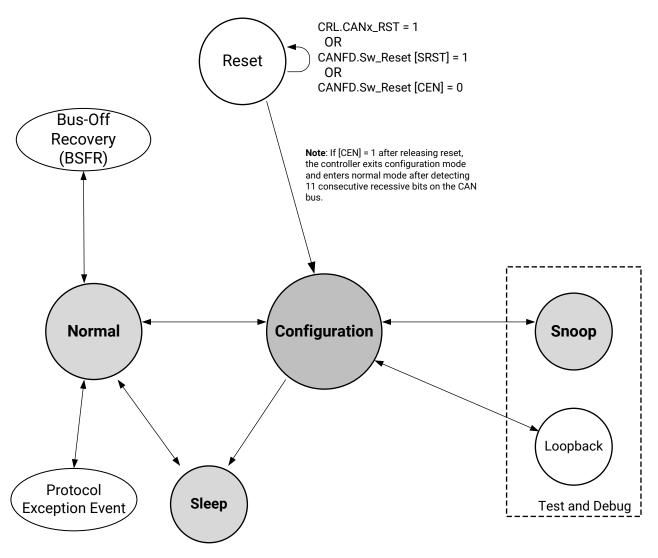

| Modes and States                        | 547 |

| Configuration Sequence                  | 553 |

| Message Transmission                    | 554 |

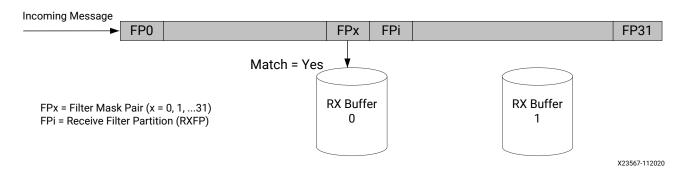

| Message Reception                       | 557 |

| Register Reference                      | 560 |

| I/O Signal Reference                    | 563 |

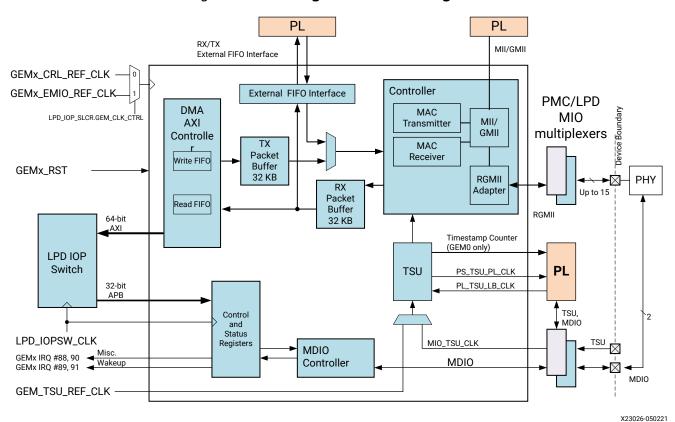

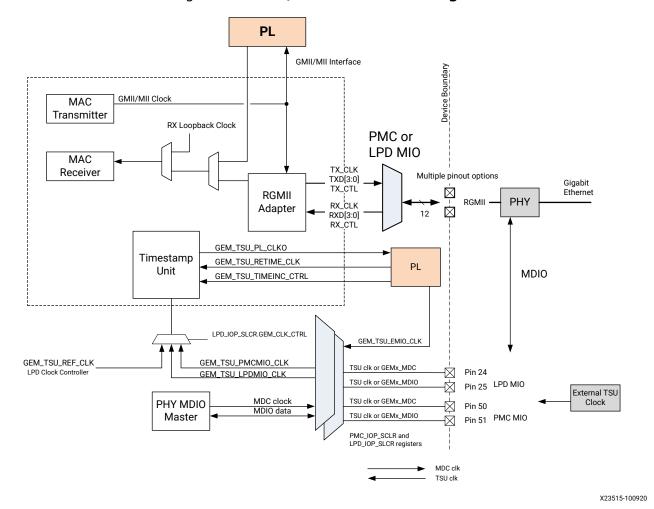

| Chapter 64: Gigabit Ethernet MAC        | 564 |

| Features                                |     |

| System Perspective                      |     |

| Modes and States                        |     |

| Memory Packet Descriptors               |     |

| DMA AXI Transactions                    | 576 |

| Transmit Dataflow                       | 578 |

| MAC Transmitter                         | 582 |

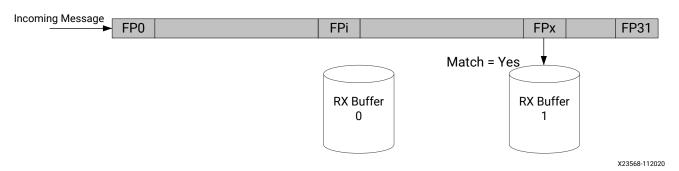

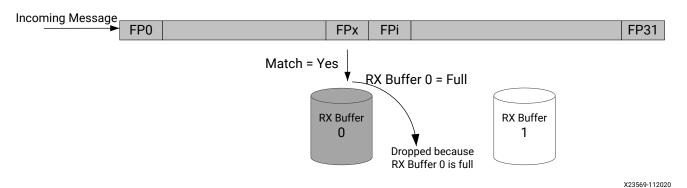

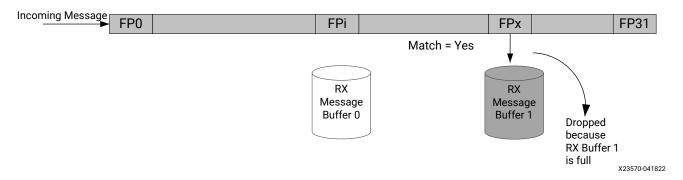

| Receive Dataflow                        | 585 |

| MAC Receiver                            | 590 |

| Precision Timestamp Unit                | 597 |

| MAC Pause Frames                        | 599 |

| Checksum Hardware                       | 602 |

| Register Reference                      | 604 |

| I/O Signal Reference                    | 610 |

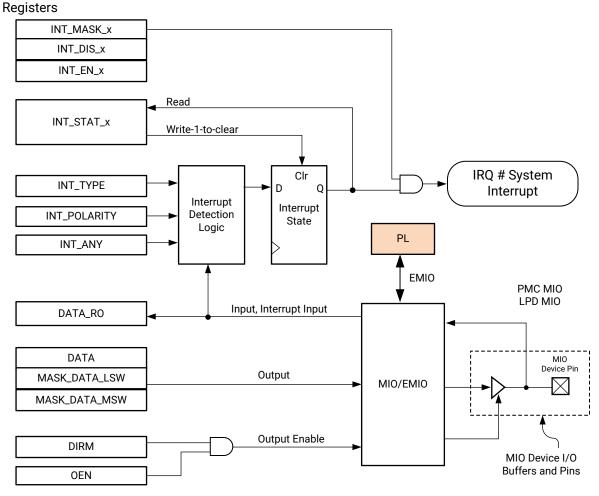

| Chapter 65: GPIO Controller             | 613 |

| Features                                |     |

| System Perspective                      |     |

| Channel Block Diagram                   | 618 |

| Input Programming Model        | 619 |

|--------------------------------|-----|

| Interrupt Programming Model    | 620 |

| Output Programming Model       | 621 |

| Registers                      | 621 |

| GPIO I/O Signals               | 624 |

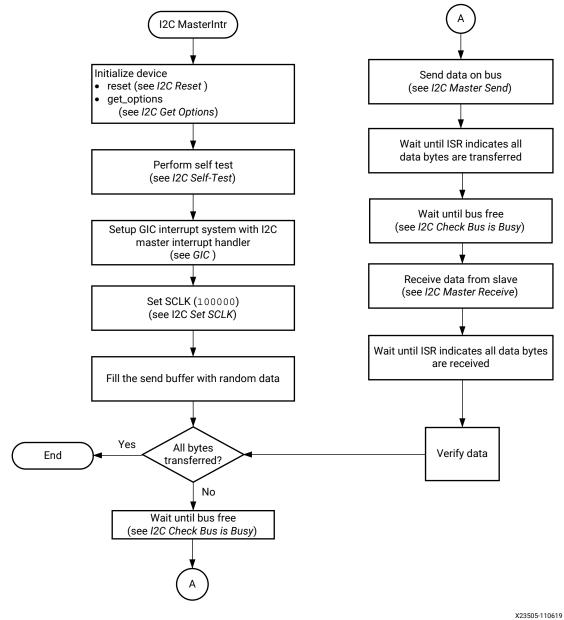

| Chapter 66: I2C Controller     | 626 |

| Features                       | 627 |

| System Perspective             | 628 |

| Programming Model              | 629 |

| Programming Sequences          | 635 |

| Software Routines              | 637 |

| Register Reference             | 648 |

| I2C I/O Interface              | 650 |

| Chapter 67: SPI Controller     | 652 |

| Features                       |     |

| System Perspective             |     |

| Modes and States               |     |

| Functional Diagram             | 657 |

| Data Transfer                  | 659 |

| Register Reference             | 661 |

| I/O Interface                  | 662 |

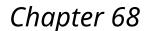

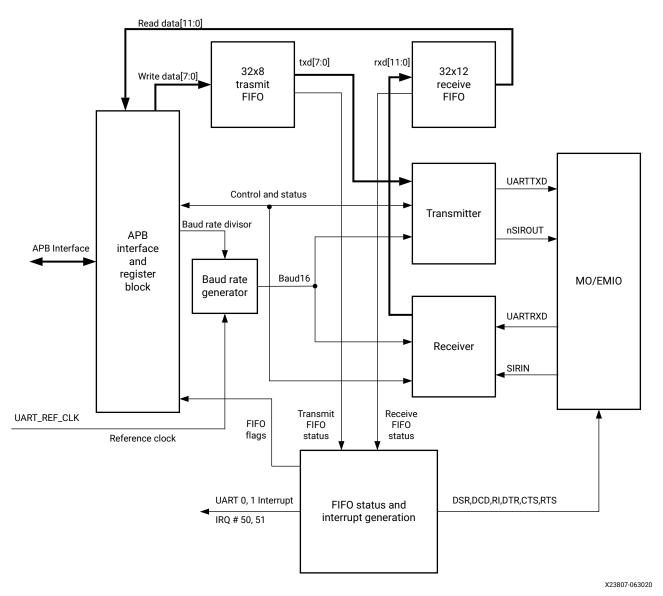

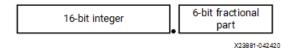

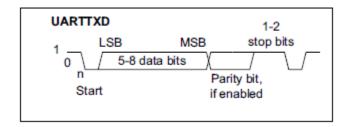

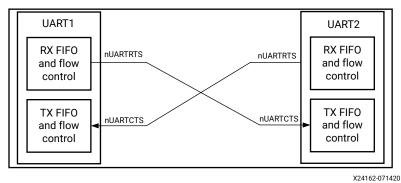

| Chapter 68: UART Controller    | 663 |

| Features                       | 663 |

| System Perspective             | 664 |

| Modes and States               | 666 |

| UART Functionality             | 667 |

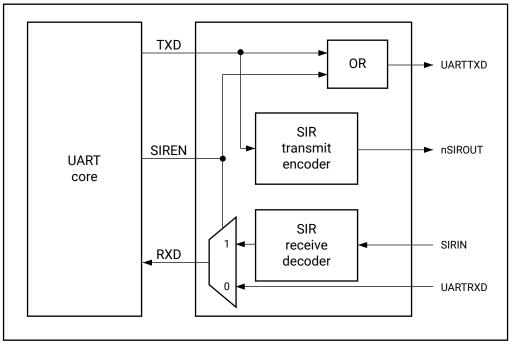

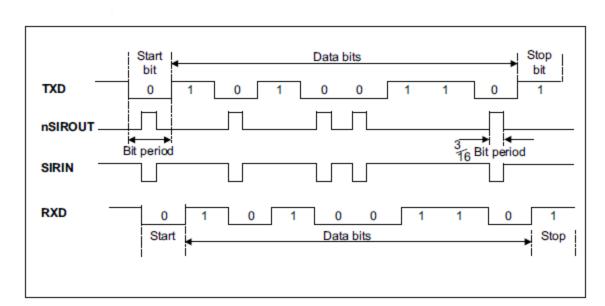

| IrDA Functionality             | 673 |

| Interrupts                     | 675 |

| Registers                      | 677 |

| UART I/O Signals               | 679 |

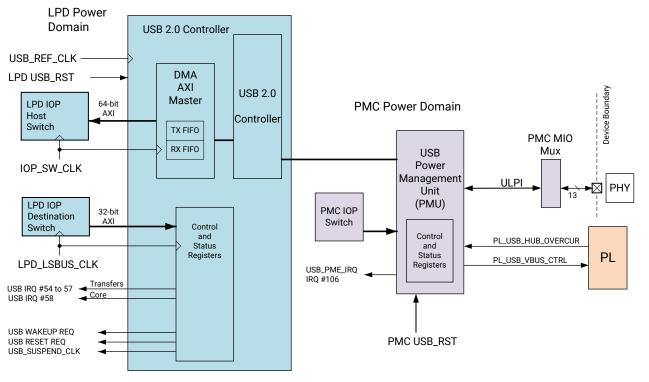

| Chapter 69: USB 2.0 Controller | 681 |

| Features                       |     |

| System Perspective             |     |

| Host Mode Data Structures      |     |

| Register Reference             |     |

|                                |     |

| USB I/O Signals                        | 696 |

|----------------------------------------|-----|

| Section XIII: Flash Memory Controllers | 697 |

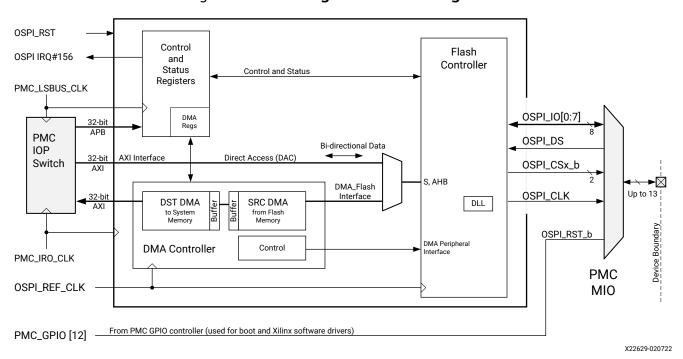

| Chapter 70: Octal SPI Controller       | 698 |

| Features                               |     |

| System Perspective                     |     |

| Access Modes                           |     |

| DMA Programming Model                  |     |

| Interrupts                             | 710 |

| Register Reference                     |     |

| OSPI I/O Interface                     | 714 |

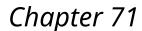

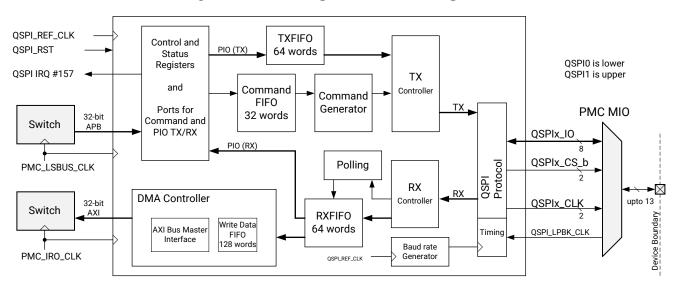

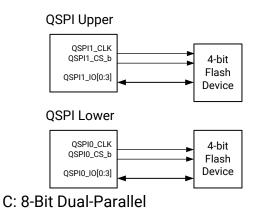

| Chapter 71: Quad SPI Controller        | 716 |

| Features                               |     |

| System Perspective                     | 717 |

| Modes and States                       | 723 |

| I/O Programming                        | 725 |

| Command Words                          | 727 |

| Programming                            | 728 |

| PIO Mode Programming Model             | 731 |

| DMA Programming Model                  | 732 |

| Polling Programming Model              | 732 |

| Register Reference                     | 733 |

| QSPI I/O Interface                     | 734 |

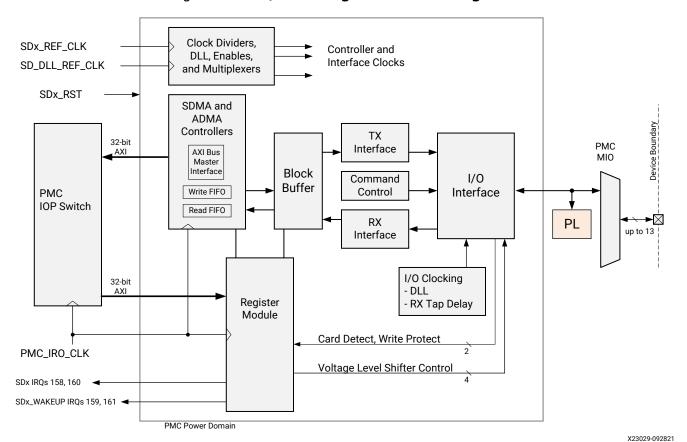

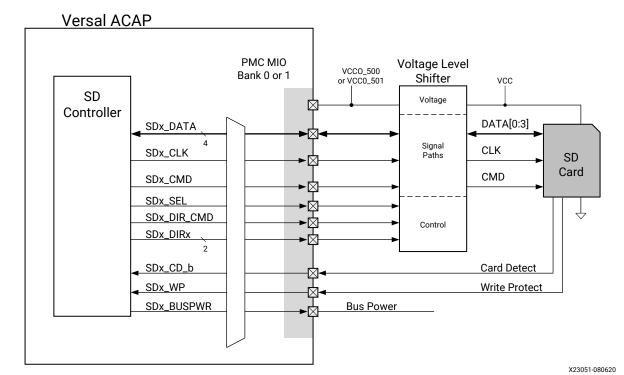

| Chapter 72: SD/eMMC Controllers        | 737 |

| Features                               | 737 |

| System Perspective                     | 739 |

| Modes and States                       | 744 |

| Main Functionality                     | 745 |

| I/O Functionality                      | 747 |

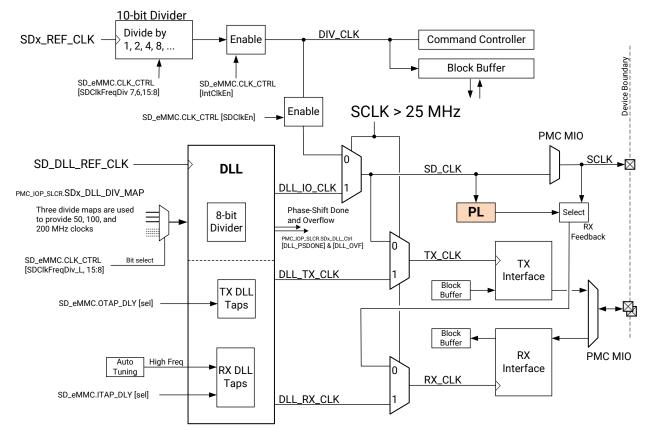

| I/O Clock Functionality                | 749 |

| SD Commands                            | 758 |

| Register-driven DMA Mode               | 761 |

| Descriptor-driven DMA Mode             | 761 |

| Software Routines                      | 761 |

| Register Reference                     | 762 |

| I/O Signals                            | 767 |

| Section XIV: Clocks, Resets, and Power           | 769 |

|--------------------------------------------------|-----|

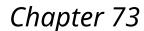

| Chapter 73: Clocks                               | 770 |

| Clock Distribution Diagram                       |     |

| Clock Frequency Considerations                   |     |

| PMC Source Clocks                                |     |

| PLL Clock Generators                             |     |

| Reference Clock Frequency Dividers               | 777 |

| Registers                                        |     |

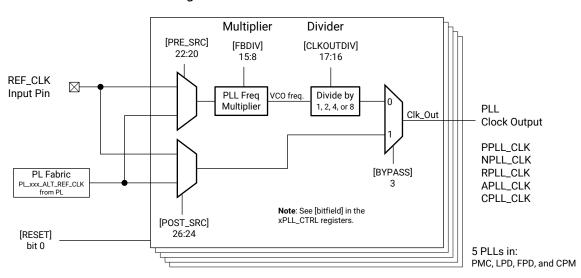

| Chapter 74: Clock Monitor                        | 783 |

| Base Time Period                                 |     |

| Calculate Threshold Counts                       | 784 |

| Monitored Clocks                                 | 785 |

| Interrupts                                       | 785 |

| Register Reference                               | 786 |

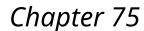

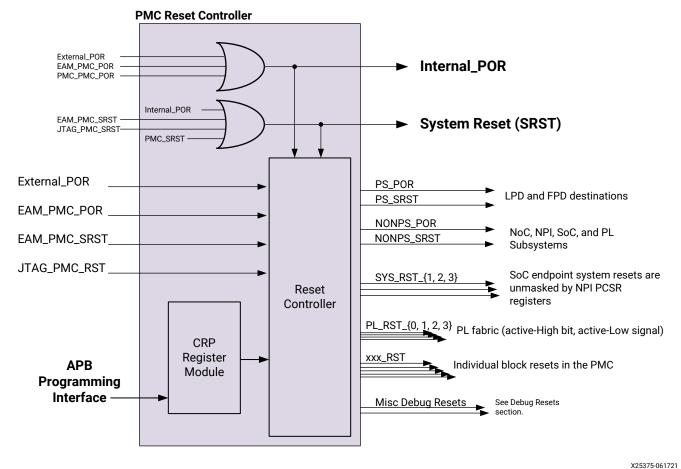

| Chapter 75: Resets                               | 787 |

| Comparison to Previous Generation Xilinx Devices | 788 |

| System Perspective                               | 789 |

| Resets Overview                                  | 793 |

| POR_B Reset                                      | 796 |

| System Integrity Monitoring                      | 798 |

| Reset Reference for Individual Blocks            | 799 |

| Persistent Registers                             | 803 |

| Chapter 76: Power                                | 808 |

| Power Diagram                                    | 809 |

| Power Domains                                    | 811 |

| Power Domain State Requirements                  | 811 |

| Power Islands                                    | 811 |

| Section XV: Test and Debug                       | 813 |

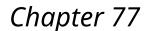

| Chapter 77: Overview                             | 814 |

| Chapter 78: Integrated Debug                     | 815 |

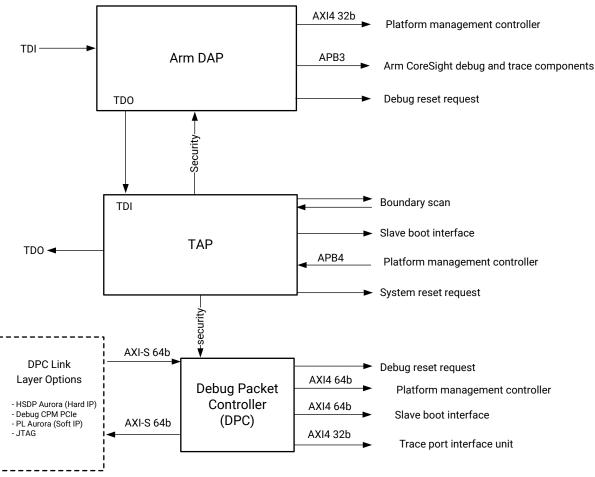

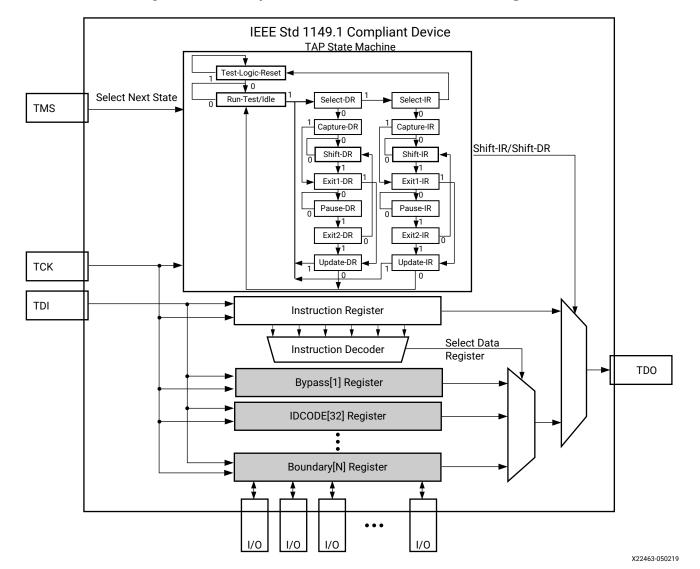

| JTAG and Boundary-Scan                           | 816 |

| Arm DAP Controller                                 | 825 |

|----------------------------------------------------|-----|

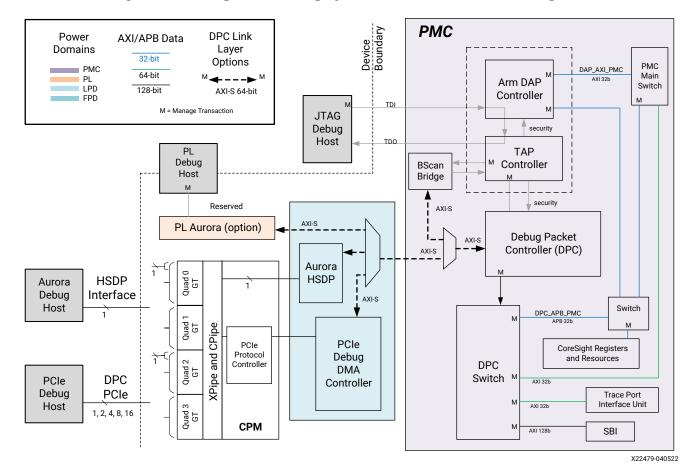

| Debug Packet Controller                            | 826 |

| Chantay 70: CayoSight Dahug                        | 020 |

| Chapter 79: CoreSight Debug                        |     |

| Funnels                                            | 830 |

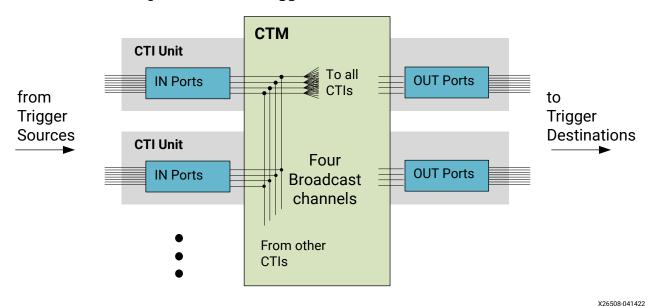

| Cross-Trigger Functionality                        | 831 |

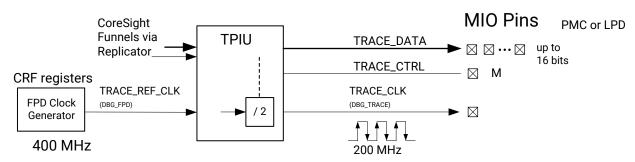

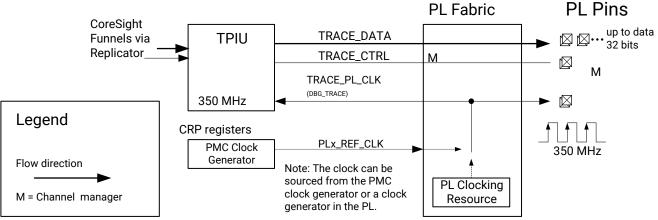

| Trace Port Interface Unit                          | 835 |

| CoreSight Register Reference                       | 838 |

| Debug Timestamp Counter                            | 838 |

| Appendix A: Additional Resources and Legal Notices | 839 |

| Xilinx Resources                                   | 839 |

| Documentation Navigator and Design Hubs            | 839 |

|                                                    |     |

| References                                         | 839 |

| References<br>Revision History                     |     |

|                                                    | 841 |

# Introduction

This section includes these chapters:

- Introduction to Versal ACAP

- Navigating Content by Design Process

- Device Overview

- Documentation

# Introduction to Versal ACAP

Versal® adaptive compute acceleration platforms (ACAPs) combine Scalar Engines, Adaptable Engines, and Intelligent Engines with leading-edge memory and interfacing technologies to deliver powerful heterogeneous acceleration for any application. Most importantly, Versal ACAP hardware and software are targeted for programming and optimization by data scientists and software and hardware developers. Versal ACAPs are enabled by a host of tools, software, libraries, IP, middleware, and frameworks to enable all industry-standard design flows.

Built on the TSMC 7 nm FinFET process technology, the Versal portfolio is the first platform to combine software programmability and domain-specific hardware acceleration with the adaptability necessary to meet today's rapid pace of innovation. The portfolio includes six series of devices uniquely architected to deliver scalability and AI inference capabilities for a host of applications across different markets—from cloud—to networking—to wireless communications—to edge computing and endpoints.

The Versal architecture combines different engine types with a wealth of connectivity and communication capability and a network on chip (NoC) to enable seamless memory-mapped access to the full height and width of the device. Intelligent Engines are SIMD VLIW AI Engines for adaptive inference and advanced signal processing compute, and DSP Engines for fixed point, floating point, and complex MAC operations. Adaptable Engines are a combination of programmable logic blocks and memory, architected for high-compute density. Scalar Engines, including Arm® Cortex®-A72 and Cortex-R5F processors, allow for intensive compute tasks.

The Versal AI Edge series focuses on AI performance per watt for real-time systems in automated drive, predictive factory and healthcare systems, multi-mission payloads in aerospace & defense, and a breadth of other applications. More than just AI, the Versal AI Edge series accelerates the whole application from sensor to AI to real-time control, all with the highest levels of safety and security to meet critical standards such as ISO26262 and IEC 61508.

The Versal AI Core series delivers breakthrough AI inference acceleration with AI Engines that deliver over 100x greater compute performance than current server-class of CPUs. This series is designed for a breadth of applications, including cloud for dynamic workloads and network for massive bandwidth, all while delivering advanced safety and security features. AI and data scientists, as well as software and hardware developers, can all take advantage of the high-compute density to accelerate the performance of any application.

The Versal Prime series is the foundation and the mid-range of the Versal platform, serving the broadest range of uses across multiple markets. These applications include 100G to 200G networking equipment, network and storage acceleration in the Data Center, communications test equipment, broadcast, and aerospace & defense. The series integrates mainstream 58G transceivers and optimized I/O and DDR connectivity, achieving low-latency acceleration and performance across diverse workloads.

The Versal Premium series provides breakthrough heterogeneous integration, very high-performance compute, connectivity, and security in an adaptable platform with a minimized power and area footprint. The series is designed to exceed the demands of high-bandwidth, compute-intensive applications in wired communications, data center, test & measurement, and other applications. Versal Premium series ACAPs include 112G PAM4 transceivers and integrated blocks for 600G Ethernet, 600G Interlaken, PCI Express® Gen5, and high-speed cryptography.

The Versal HBM series enables the convergence of fast memory, adaptable compute, and secure connectivity in a single platform. The series is architected to keep up with the higher memory needs of the most compute intensive, memory bound applications, providing adaptable acceleration for data center, wired networking, test & measurement, and aerospace & defense applications. Versal HBM ACAPs integrate the most advanced HBM2e DRAM, providing high memory bandwidth and capacity within a single device.

The Versal architecture documentation suite is available at: https://www.xilinx.com/versal.

# Navigating Content by Design Process

Xilinx® documentation is organized around a set of standard design processes to help you find relevant content for your current development task. All Versal® ACAP design process Design Hubs and the Design Flow Assistant materials can be found on the Xilinx.com website. This document covers the following design processes:

• System and Solution Planning: Identifying the components, performance, I/O, and data transfer requirements at a system level. Includes application mapping for the solution to PS, PL, and Al Engine.

The technical reference manual (TRM) describes the overall hardware architecture of the Versal® ACAP and provides details on the blocks in the platform management controller (PMC) and in the processing system (PS). The PS includes the real-time processing unit (RPU), application processing unit (APU), and their peripherals.

- Device-level block diagram: Device Overview chapter

- High-level Interconnect Diagrams chapter

- PMC and PS Architectures chapter

- PL Fabric Overview chapter

- Device I/O Connectivity chapter with I/O buffers and transceivers

- Section XIV: Clocks, Resets, and Power chapter with architectures and controls

There are several device families with different device options. The availability of a specific device option is listed in the *Versal Architecture and Product Data Sheet*: Overview (DS950). The TRM usually identifies these with the designation: device option.

- Integrated Hardware Options

- Integrated Peripheral Options

- Embedded Software Development: Creating the software platform from the hardware platform and developing the application code using the embedded CPU. Also covers XRT and Graph APIs.

Embedded software runs in the RPU and APU scalar engines in the PS.Arm® Cortex®:

#### **Versal ACAP:**

- Real-time Processing Unit: dual-core Cortex-R5F with lock-step option

- Application Processing Unit: dual-core Cortex-A72

#### Versal ACAP:

The system software boot up and operating system environments are described in the *Versal ACAP System Software Developers Guide* (UG1304). The PMC modules are described in the Section VII: Embedded Processor, Configuration, and Security Units section.

• **Board System Design:** Designing a PCB through schematics and board layout. Also involves power, thermal, and signal integrity considerations.

The TRM includes some important information to help with board design planning and development:

- Boot device interfaces: Boot Modes

- Pin planning for I/O peripherals: Multiplexed I/O Signals and Pins

- Power controls: Power Diagram

- JTAG interface: JTAG and Boundary-Scan

For package and pin information, see the Versal ACAP Packaging and Pinouts Architecture Manual (AMO13).

The electrical specifications are provided in the Versal Prime Series Data Sheet: DC and AC Switching Characteristics (DS956) and the Versal AI Core Series Data Sheet: DC and AC Switching Characteristics (DS957).

# **Device Overview**

The Versal<sup>®</sup> ACAP includes extensive functionality for high-end applications that need scalable processing power, integrated functional units, and a large amount of scalable programmable logic that can be dynamically configured and reconfigured during normal operation.

The device is partitioned into the following areas:

- Processing system (PS) with multicore application and multicore real-time processing units

- Platform management controller (PMC) for boot, configuration, monitoring, and power management

- PS manager (PSM) for PS power management

- On-chip memory (OCM) and optional accelerator RAM (XRAM)

- DDR memory controllers with ECC

- High-bandwidth memory (HBM) option

- Programmable logic (PL) with fabric, logic units, memory arrays, and DSP options

- Device-wide network on chip (NoC) interconnect

- Integrated hardware and I/O peripheral options

- Standard LVCMOS HDIO

- Gigabit transceiver options

The architecture includes a rich set of integrated hardware components and many user-programmable design options for system-level solutions. Each device incorporates PL,PS, PMC, and various integrated hardware subsystems and peripherals that are configured with a coherent flow. The PL and PS sections of the device each have many components that can be selectively used as needed and, if included, they are configured and initialized to accommodate different functional and power requirements demanded by the platform solution.

The PL supports AXI SmartConnect core functionality that can be instantiated using a library of LogiCORE™ IPs. The AXI SmartConnect core can be independent within the PL or extended and attached to the PS through several AXI interfaces with and without coherency with the APU system cache.

Additionally, the system is monitored during its runtime to detect errors and provide the necessary means to address the errors as a part of the security, reliability, and safety requirements. The configuration, bring-up, and general platform management tasks include reset, clocking, power management, and system monitoring. This is achieved by the PMC that exists in every device. The PMC also provides a unified interface for the cohesive debug and trace capture on the entire device including the PS, PL, and other components on the device.

All devices are based on the NoC interconnect to link processors and DMA units to system memory, other processors, and other resources within the device and to external devices with the various implementations of a coherent module with PCIe<sup>®</sup> (CPM) (a device option).

Each device has one or more DDR memory controllers. Some devices include an interface for an in-package HBM.

There are several types of I/O banks spread throughout the device to connect to external devices, including the PMC, PS, and the PL. The I/O banks include PSIO, HDIO, and the GT transceivers.

The size and composition of the PL, the number of memory controllers, the amount of I/O, and the integrated hardware blocks varies by device as defined in the *Versal Architecture and Product Data Sheet*: Overview (DS950).

There are several power domains with their own package power pins that are color-coded in the following section:

## Device-Level Block Diagram

All blocks and subsystems are controlled and monitored with hundreds of register modules. Each module includes twenty to thousands of individual registers. These are documented in several register reference manuals. Most functional units include one register module. Some functional units have multiple register modules. Some register modules are associated with multiple functional units that include the system-level control registers (SLCR) and the clock and reset registers (e.g., CRL). The register modules for the PS and PMC units are accessed by software using single 32-bit read and write transactions to the APB programming interfaces. The register sets for the DDR memory controller, NoC, AI Engine, and other integrated hardware are accessed via the NPI host interface. This interface supports 32-bit burst reads and writes. Access to NPI register modules is controlled by XPPU protection units. The software programming interfaces to read and write registers and program the device are described in Register Programming Interfaces section.

The device documents are listed in the Documentation chapter.

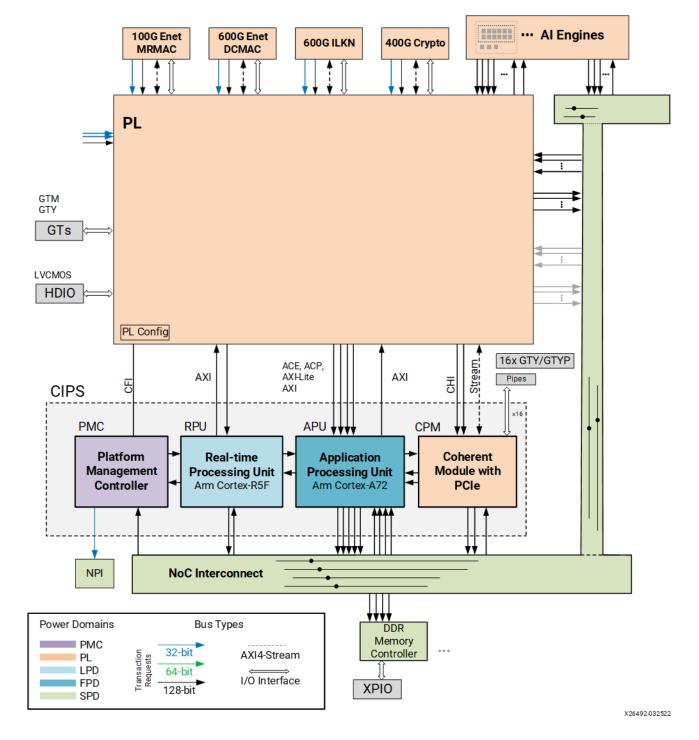

# **Device-Level Block Diagram**

The Versal device-level block diagram is shown in the following figure. The PMC and PS implementations are summarized in the Device Overview chapter.

**NoC Interconnect Integrated Hardware Processing System (PS) Building Blocks FPD Interconnect LPD Interconnect** \* Digital Signal Processors (DSP) \* Logic Blocks, RAM, and I/O pins System Memory Management (SMMU) Real-time Processing Unit (RPU): even translation buffer units (TBU) \* Dual Cortex-R5F processor core \* TCMs and on-chip memories \* Shared memory support Peripherals \* Ethernet MACs, Interlaken Cache Coherent Interconnect (CCI) TCM TCM • • • TCM \* Four NoC egress Ports

\* Ports to LPD and CPM \* High-speed Cryptography OCM On-chip Memory \* Video Decoder Unit Application Processing Unit (APU): XRAM Accelerator RAM Dual Cortex-A72 processor cores 1 MB L2-cache **Instantiated Blocks** \* MicroBlaze, interconnect L2 Cache \* Pipeline Slices \* Functional Units **Power Domains NoC Interconnect** PL **CPM** uB System Cache SPD FPD/LPD **DDR Memory HBM Memory** PMC PL or LPD Controllers Interface External DDR SSI Technology HBM Die \* 32/64-bit with ECC \* In-package memory \* Up to 256-bit width with ECC Interleaveable Platform Management Controller (PMC) PS Manager (PSM) ROM Code Unit (RCU): PSM Firmware: PMC Processing Unit (PPU): \* Runs BootROM code to load boot image Runs platform loader and manager (PLM) \* Runs firmware downloaded by PLM \* Provides system monitoring functions \* 32-bit MicroBlaze \* 32-bit MicroBlaze \* Deeply embedded 32-bit MicroBlaze

Figure 1: Device-Level Block Diagram

X24789-041122

## System Features

The PS is described in the Processing System section.

The PMC is described in the Platform Management Controller section.

#### **NoC Interconnect**

The NoC interconnect is pervasive across the device. See Versal ACAP Programmable Network on Chip and Integrated Memory Controller LogiCORE IP Product Guide (PG313).

#### **DDR Memory**

The device includes one or more DDR4/LPDDR4 memory controllers.

## **HBM Memory**

Some devices include one or more high-bandwidth memory interfaces that attach to the NoC interconnect and drive I/O buffers to the HBM die within the device. See High-Bandwidth Memory Interface.

#### **Programmable Logic**

The PL is a scalable structure that provides the ability to create many possible functions. The integrated hardware options have interconnect interfaces and connections to the PL fabric. The PL I/O includes both LVCMOS buffers and gigabit transceivers that cover a wide range of applications and frequencies. See PL Fabric Overview.

## **Integrated Hardware Options**

- Scalable Al Engine

- 1 MB Accelerator RAM (XRAM)

- Integrated Peripheral Options (includes documentation links):

- Ethernet MACs, Interlaken

- . Video decoder unit

- High-speed crypto engine

#### **Coherent Module with PCIe**

The coherent module with PCIe (CPM) interconnect provides coherency between the PCIe controllers, a PL processor, and the PS. The CXL module adds memory coherency with external devices over PCIe.

See Integrated Hardware Options. There are multiple types of CPM modules:

- CPM4 with CCIX interconnect (device option in Versal ACAP)

- CPM5 with CXL interconnect (device option in Versal ACAP)

# **Processing System**

## **Processing System**

The Versal ACAP PS includes a dual-core application processing unit (APU) in the full-power domain (FPD) and a dual-core real-time processing unit (RPU) in the low-power domain (LPD).

Operating system software can configure these MPCores in a symmetrical or asymmetrical multiprocessor configuration.

#### **APU**

The APU is a dual-core processing unit based on the Arm® Cortex®-A72 cores.

See Application Processing Unit

## **RPU**

The RPU is a dual-core processing unit based on the Arm Cortex-R5F2 cores with lockstep support.

See Real-time Processing Unit

## **Processor Communications**

Each device includes an inter-processor interrupt controller with small message passing and mutex register functionality.

- Inter-Processor Interrupts chapter

- PMC MUTEX n registers

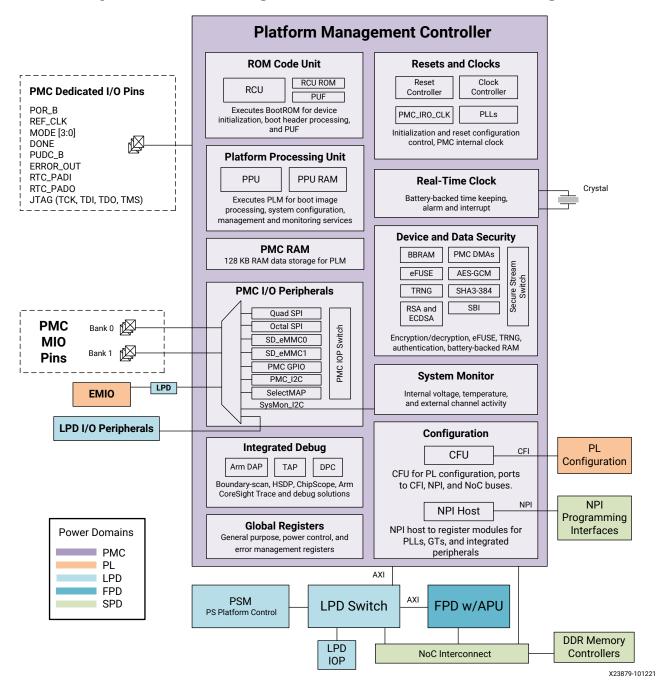

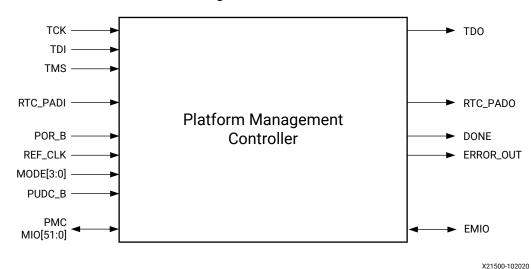

# **Platform Management Controller**

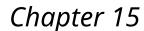

All SoC devices include a PMC. The PMC is responsible for boot, configuration, partial-reconfiguration, and other platform management tasks, such as security. The PMC includes the deeply embedded ROM code unit (RCU) for device boot and a platform processing unit (PPU) that executes the platform loader and manager (PLM) firmware. The PLM also manages the processing system management (PSM) controller firmware downloads.

See Section III: Platform Boot, Control, and Status.

## **PMC Block Diagram**

The platform management controller functional block diagram identifies the blocks and underlying units associated with each primary function.

Figure 2: Platform Management Controller Functional Block Diagram

## Features Supporting System Start-up

The platform management control includes several features to support system start-up, monitoring, and responses to system requests.

- ROM code unit (RCU) triple modular redundant (TMR) MicroBlaze<sup>™</sup> processor with a dedicated RCU BootROM for initial device boot and tamper monitoring

- Platform processing unit (PPU) TMR MicroBlaze processor

- System monitor (SYSMON) with temperature and power supply monitoring

- Global registers capture general-purpose, power, and error conditions

- Two streaming DMAs transfer data within the system for configuration and processing

# **Applications**

The general applications include:

- Industrial applications requiring high performance MPCore processors

- Level-3 and above advanced driver-assistance systems (ADAS) and autonomous driving automotive applications

- Wired and wireless

- Embedded computing

- Applications requiring the AI Engine or the programmable fabric

## **Software Code and Data Files**

Software components include the following:

- Real-time and application software:

- Arm application real-time processors.

- Platform processing unit (PPU) MicroBlaze™ triple-redundant processor.

- MicroBlaze processors instantiated in the PL.

- Embedded firmware

- PLM firmware generated by the design tools to program the PL using the configuration frame unit (CFU).

PSM firmware to configure the device and provide power management.

#### **Processor Communications**

Software has several hardware mechanisms to communicate between processors.

- Inter-Processor Interrupts with small message buffers.

- Set of 32 mutex registers, PMC\_MUTEX\_n.

## **Software Development**

Software can be developed on several platforms.

- Bare-metal software stack with standard C libraries: libc and libm, based on the open source Newlib library.

- Middleware libraries that provide networking, file system, and encryption support.

- Application examples include test applications.

- Linux-based tools and operating system software including:

- PetaLinux to quickly build an embedded OS.

- U-Boot and Yocto-based tools.

The software environments are described in the Versal ACAP System Software Developers Guide (UG1304).

## Debugger

Xilinx system debugger (XSDB) in coordination with Arm CoreSight™.

## **Embedded Processor Code**

There are three embedded MicroBlaze processors.

- ROM code unit (RCU) executes the BootROM code from read-only memory (ROM)

- PPU processor executes the PLM firmware from RAM, see the Platform Processing Unit chapter

- PSM processor executes the PSM firmware from RAM, see the Processing System Manager chapter

The functionality of the BootROM code is described in the Section III: Platform Boot, Control, and Status section. The functionality of the PLM and PSM firmware is described in the Versal ACAP System Software Developers Guide (UG1304). The MicroBlaze processor is described in the MicroBlaze Processor Reference Guide (UG984).

#### **RCU BootROM Code**

The deeply embedded RCU is the first processor to start up after a power-on reset (POR). The RCU executes its BootROM code to initialize the system and validate the boot device. The RCU processes the boot header provided by the boot device. The RCU downloads the platform loader and manager (PLM) firmware into the PPU RAM and releases the reset on the PPU processor.

#### **PLM Firmware Code**

The PLM firmware runs on the MicroBlaze-based platform processing unit (PPU). The PLM firmware is generated by the Vivado® and Vitis™ tools and configures the system for device boot. The PLM firmware includes code to support a single download or a series of downloads. After system boot, the PLM goes on to manage system resources.

The PLM reads the programmable device image (PDI) from the boot source and configures the system components for real-time and application program booting. The PLM configuration normally includes NoC initialization, DDR memory controller initialization, programmable logic configuration, and loading real-time and application software in the processing system (PS). The operations and responsibilities of the PLM are defined by the SoC application. When the PS takes control of the SoC, the PLM monitors system activity and responses to system requests from the real-time and application processing units, RPU and APU.

#### **PSM Firmware Code**

The embedded processing system manager (PSM) processor executes firmware downloaded by the PLM to control the power management features for the PS. The TRM provides programming models for the power control features in the PMC and PS. This includes power islands, memory chip enables, isolation, and APU sleep/wake events. The PSM is physically located in the low-power domain (LPD), and not the PMC power domain.

## **Data Packets**

There are several types of data packets.

- Debug packet controller with HSDP Aurora I/O for test and debug, see Debug Packet Controller.

- CFRAMEs to configure the programmable logic, see the CFU Programming Interface section.

# **System Performance**

There are inherent performance features in the system and several performance related configuration options. The TRM describes the inherent performance features and the functionality that can be used to obtain an optimal configuration.

- Inherent NoC interconnect design features with configurable, multichannel structures

- Multiple interconnect traffic types to control quality of service (QoS)

- Isochronous for video and other time-sensitive transactions

- Low latency for communications and other applications

- Best effort, bulk traffic for large data sets without critical timing needs

- Intelligent DDR memory controller scheduler

- Hardware acceleration in PL instantiated functions

## **Performance Tuning**

Performance tuning builds on the inherent features. This includes properly routing NoC traffic, optimizing the use of the DDR memory controller, and using the QoS traffic types. Performance tuning is not covered in the TRM.

## Interconnect Features

The interconnect has dedicated 128-bit AXI channel connections between the subsystems. These include low-latency datapaths and high-throughput datapaths with buffering. There are also noteworthy datapaths.

The interconnect optimizes the performance of the RPU and APU. The interconnect port connections are shown in PMC-PS-CPM Interconnect Diagram and listed in this section.

## **Low-latency Datapaths**

- APU to NoC: CCI connections to the NoC

- RPU to NoC: AXI egress port on OCM switch

- RPU to OCM: AXI egress port on OCM switch

- RPU to its TCMs: two cycle access with deterministic execution

## **High-throughput Datapaths**

Popular high-throughput datapaths:

- APU to NoC with four CCI egress ports

- RPU to NoC with main switch egress port

- LPD DMA to FPD main switch

## **Noteworthy Datapaths**

APU to CCI to FPD main switch to OCM switch to OCM and XRAM (optional)

## **Transaction Quality of Service**

Each transaction includes a quality of service (QoS) traffic attribute.

- Low-latency

- Isochronous

- Bulk transfer

The QoS attribute is recognized by the AMBA® switches and DDR memory controller. System performance can be obtained by setting the QoS attributes appropriately. Each master can generate one or more QoS values. The traffic types are detailed in Quality of Service.

# **Device Comparisons and IP Revisions**

The comparisons between the different SoC devices and the IP revision for major blocks are in this chapter:

• Comparison to Previous Generation Devices

## **Comparison to Previous Generation Devices**

The migration of functionality from a previous generation Xilinx $^{\mathbb{R}}$  device to Versal ACAP is captured on a per block basis. There are several *Comparison to Previous Generation Devices* topics throughout the TRM, including:

- Platform Management Controller (PMC)

- Real-time Processing Unit (RPU)

- Application Processing Unit (APU)

- LPD DMA

- Platform Processing Unit (PPU)

- Interconnect

- System Management IDs

- Inter-processor Interrupts (IPI)

- System Watchdog Timer

- On-chip Memory

- CAN FD

- Gigabit Ethernet MAC (GEM)

- General-purpose I/O (GPIO)

- I2C, SPI

- UART SBSA

- USB 2.0

- Octal SPI

- Quad SPI

- SD/eMMC

- Resets

Note: For additional Versal device comparison information, see Versal ACAP Design Guide (UG1273).

## **IP Block Revisions**

The following table lists the PMC-PS implementation summary organized by TRM section.

Table 1: PMC-PS Implementation Summary Organized by TRM Section

| Functional Unit                                                            | Description                                          | Instances, Description, and IP<br>Version                                                                                         |  |

|----------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| Section VI: Engines section                                                | Section VI: Engines section                          |                                                                                                                                   |  |

| APU MPCore                                                                 | Application processor cores.                         | Dual Arm Cortex-A72 processors with v8-architecture and NEON and VFPv4 floating point A74-MP and MP054 (Arm version r0p3-00rel0). |  |

|                                                                            | Extensions.                                          | Cryptography extension (A72-Crypto, MP055)<br>( version r0p2-00rel0).                                                             |  |

| APU GIC                                                                    | Application processor generic interrupt controller.  | Generic interrupt controller, GIC-500<br>(Arm version r1p1-00rel0).                                                               |  |

| RPU MPCore                                                                 | Real-time processor cores.                           | Dual processor cores, Cortex-R5F (Arm version AT570-r1p3-00rel0).                                                                 |  |

| RPU GIC                                                                    | Real-time processor generic interrupt controller.    | PL-390<br>(Arm version r0p0-00rel2).                                                                                              |  |

| LPD_DMA                                                                    | Descriptor-driven, general purpose DMA unit.         | PS DMA Controller chapter.                                                                                                        |  |

| Section VII: Embedded Processor, Configuration, and Security Units section |                                                      |                                                                                                                                   |  |

| AES-GCM                                                                    | Security engine for encryption and decryption.       |                                                                                                                                   |  |

| PMC_AES                                                                    |                                                      | Symmetric key cryptography for encryption and decryption, AES. (Athena version ro-2017-12-12).                                    |  |

| BBRAM controller                                                           | Battery-backed RAM controller<br>Battery-Backed RAM. | PMC                                                                                                                               |  |

Table 1: PMC-PS Implementation Summary Organized by TRM Section (cont'd)

| Functional Unit                  | Description                                                                                                   | Instances, Description, and IP<br>Version                                                                                                                                             |

|----------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFU                              | Configuration frame unit receives commands and read/writes PL configuration regions Configuration Frame Unit. | PMC                                                                                                                                                                                   |

| PMC DMAs                         | DMA0 and DMA1; streaming and memory-to-<br>memory transactions on PMC interconnect<br>port.                   |                                                                                                                                                                                       |

| DPC                              | Debug packet controller; connected to the PMC main switch, JTAG, Aurora HSDP, and PL Debug Packet Controller. |                                                                                                                                                                                       |

| eFUSE controller                 | Controller for eFUSE array.                                                                                   |                                                                                                                                                                                       |

| eFUSE cache                      | Cache of the eFUSEs<br>TBD.                                                                                   |                                                                                                                                                                                       |

| JTAG TAP controller              | TAG test access port controller for boundary scan and Xilinx opcodes.                                         |                                                                                                                                                                                       |

| JTAG Arm DAP controller          | Debug access port controller for PS<br>Arm DAP Controller.                                                    |                                                                                                                                                                                       |

| PPU                              | Platform Processing Unit.                                                                                     | PMC                                                                                                                                                                                   |

| PMC_RSA                          | Security public-key cryptography engine for authentication (RSA/ECDSA) RSA/ECDSA.                             |                                                                                                                                                                                       |

| PMC_RSA/ECDSA                    |                                                                                                               | Public-key crypto system, RSA, and elliptic curve digital signature algorithm,ECDSA, public-key cryptography enables authentication. (IP Cores version 5X-409603203 r2.0_12_20_2016). |

| PMC_RTC                          | Real-Time Clock battery backup time keeping.                                                                  |                                                                                                                                                                                       |

| SBI                              | Boot interface works with SelectMAP and JTAG data flows SBI for JTAG and SelectMAP.                           |                                                                                                                                                                                       |

| SHA3-384                         | Security engine for secure hash to authenticate.                                                              |                                                                                                                                                                                       |

| PMC_TRNG                         | True random number generator True Random Number Generator.                                                    | True random number generator, TRNG, (IP Cores version MP32 core r1.5).                                                                                                                |

| PMC SYSMON                       | System monitor for measuring temperature and voltage (root and satellite SYSMON units).                       | Main SYSMON is in the PMC, others are in FPD and elsewhere.                                                                                                                           |

| Section VIII: Interconnect secti | ion                                                                                                           |                                                                                                                                                                                       |

Table 1: PMC-PS Implementation Summary Organized by TRM Section (cont'd)

| Functional Unit                          | Description                                                                                                                                                                              | Instances, Description, and IP<br>Version                                                                                                                                                                   |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AXI interconnect                         |                                                                                                                                                                                          | AXI interconnect switches, NIC-400. AXI Interconnect Switches (Arm version r0p2).                                                                                                                           |

| FPD SMMU                                 | System memory management unit,<br>SMMU-500, supports memory virtualization<br>and access protection of peripherals and<br>memory System Memory Management Unit.                          | Includes 7 TBU instances.<br>(Arm TCU version is r2p4,<br>TBU version is r2p1).                                                                                                                             |

| APU cache coherency                      |                                                                                                                                                                                          | Cache coherent interconnect, CCI-500<br>Cache Coherent<br>Interconnect<br>(Arm version PL422-r1p0-00rel0).                                                                                                  |

| Xilinx memory protection unit (XMPU)     | Xilinx Memory Protection Unit.                                                                                                                                                           | PMC_XMPU<br>LPD_XMPU                                                                                                                                                                                        |

| Xilinx peripheral protection unit (XPPU) | Xilinx Peripheral Protection Unit.                                                                                                                                                       | PMC_XPPU, PMC_XPPU_NPI                                                                                                                                                                                      |

| Section X: Timers, Counters, and F       | RTC section.                                                                                                                                                                             |                                                                                                                                                                                                             |

| SCNTR                                    |                                                                                                                                                                                          | System counter, SCNTR. System Counters chapter (Arm version 1.0).                                                                                                                                           |

| SWDT                                     | System watchdog timer, SWDT, helps to maintain a healthy and secure system by detecting errant software, deadlock conditions, tampering, and unexpected behavior System Watchdog Timers. | System watchdog timer, SWDT (Xilinx version 0.08). LPD_SWDT FPD_SWDT.                                                                                                                                       |

| ттс                                      | Triple timer counter, TTC Triple-Timer Counters (Cadence version T-CS-PE-0005-100).                                                                                                      | Triple timer counter, TTC.<br>Four in PS LPD.                                                                                                                                                               |

| Section XII: I/O Peripheral Contro       | llers section                                                                                                                                                                            | •                                                                                                                                                                                                           |

| CAN FD controller                        | Controller area network with flexible datarage, CAN FD.                                                                                                                                  | Controller area network with flexible data-rate, CAN FD (Xilinx version v2.0).                                                                                                                              |

| GEM controller                           |                                                                                                                                                                                          | Gigabit Ethernet MAC controller, GXL and RGMII Gigabit Ethernet MAC chapter (Cadence version r1p12). Two in PS LPD.                                                                                         |

| GPIO                                     | General purpose I/O with output, tristate, and input. Input can be read and generate a system interrupt GPIO Controller.                                                                 | GPIO controllers. PMC_GPIO has two MIO banks (52 channels total) and two EMIO banks (64 channels total). PS LPD_GPIO has one MIO bank (26 channels) and one EMIO bank (32 channels). PMC_GPIO. PS LPD_GPIO. |

Table 1: PMC-PS Implementation Summary Organized by TRM Section (cont'd)

| Functional Unit                    | Description                                                                                                                            | Instances, Description, and IP<br>Version                                                                 |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| I2C                                | I2C controller I2C Controller (Cadence, dcw0701_R114_f0100_final).                                                                     | Inter-integrated circuit (I2C) controller.<br>Two LPD_I2Cx.<br>One PMC_I2C.<br>One SysMon_I2C.            |

| I3C                                | I3C controller.                                                                                                                        |                                                                                                           |

| SPI controller                     |                                                                                                                                        | SPI controller (two in LPD) SPI Controller chapter. (Cadence version r112).                               |

| UART SBSA controller               | UART SBSA controller, see UART Controller chapter.<br>(Arm version r1p5-00rel1).                                                       | UART SBSA controller:<br>two in PS LPD.                                                                   |

| USB 2.0 controller                 |                                                                                                                                        | USB 2.0 controller USB 2.0 Controller chapter. (Synopsys version USB3 3.30a core configured for USB 2.0). |

| USB 3.0 controller                 |                                                                                                                                        |                                                                                                           |

| Section XIII: Flash Memory Contr   | ollers section                                                                                                                         |                                                                                                           |

| OSPI                               | Octal SPI flash memory controller, see the Octal SPI Controller chapter (Cadence version DNV3100_R003_F004).                           | OSPI flash memory controller.                                                                             |

| QSPI                               | Quad SPI flash memory controller, see the Quad SPI Controller chapter (same as MPSoC with DMA addition).                               | QSPI flash memory controller.                                                                             |

| SD_eMMC                            | SD/SDIO/eMMC controller (eMMC v4.51), SD/eMMC Controllers                                                                              | SD_eMMC flash memory controller<br>(Arasan version 1p48_140929).                                          |

| Section XIV: Clocks, Resets, and P | ower section                                                                                                                           |                                                                                                           |

| PMC IRO CLK                        | Silicon-based internal ring oscillator, trimmed.                                                                                       | PMC Source Clocks.                                                                                        |

| PLLs                               | PLL clock controllers<br>PLL Clock Generators.                                                                                         | PMC PPLL,<br>NoC NPLL (PMC),<br>LPD RPLL,<br>FPD APLL,<br>CPM CPLL                                        |

| PMC ClkMon                         | Clock monitor<br>Clock Monitor.                                                                                                        | РМС                                                                                                       |

| Section XV: Test and Debug section | on                                                                                                                                     |                                                                                                           |

| Integrated debug                   | High-speed debug port, HSDP, provides a pathway to the GTY and GTYP transceivers for the Aurora packet-based debug unit (Xilinx, 1.0). |                                                                                                           |

### Table 1: PMC-PS Implementation Summary Organized by TRM Section (cont'd)

| Functional Unit         | Description                        | Instances, Description, and IP<br>Version                                 |  |  |

|-------------------------|------------------------------------|---------------------------------------------------------------------------|--|--|

| Debug packet controller | See Debug Packet Controller.       |                                                                           |  |  |

| CoreSight               | CoreSight™ debug.                  | CoreSight debug, CS_SoC-400, TM100).<br>(Arm, r3p2-00rel1).               |  |  |

|                         | CoreSight embedded logic analyzer. | CoreSight embedded logic analyzer,<br>ELA-500, TM300. (Arm, r2p2-00rel0). |  |  |

|                         | CoreSight logic analyzer kit.      | CoreSight logic analyzer kit LAK-500<br>A/I. (Arm, r1p0-00rel0).          |  |  |

|                         | CoreSight Stream.                  | CoreSight Stream (STM-500, TM963)<br>(Arm, r0p1-00rel1).                  |  |  |

## Documentation

For the Versal® ACAP, there are many sources of information, including:

- Versal ACAP Technical Reference Manual Outline

- Additional Documents

- Xilinx Documentation Navigator includes a link for downloading DocNav

The Versal ACAP Technical Reference Manual provides the details for the PMC and the PS. These are included in the control, interfaces, and processing system (CIPS) IP, which is configured by the CIPS wizard in the Vivado® tools.

**Note:** The TRM explains functionality with the assumption that a block is present in the system. The term device option is added to identify functionality that is not present in every device. The device variations are defined in the *Versal Architecture and Product Data Sheet: Overview* (DS950).

# Versal ACAP Technical Reference Manual Outline