## Memory and Peripheral Protection Unit for PL Isolation in Zynq UltraScale+ Devices

XAPP1353 (v1.1) May 4, 2022

## Summary

Isolation design methods help protect the system from erroneous application software and misbehaving hardware interfaces. Erroneous software may include malicious or unintentional code behavior that may corrupt system memory or cause system failures. Misbehaving hardware includes incorrect device configuration, malicious functionality, or unintentional design. The Zynq<sup>®</sup> UltraScale+™ devices includes TrustZone (TZ) technology to facilitate system design isolation.

The Zynq UltraScale+ MPSoCs and Zynq UltraScale+ RFSoCs incorporate many features for design security that includes Arm® TrustZone (TZ) technology, Xilinx® peripheral protection units (XPPU), Xilinx memory protection units (XMPU), a system memory management unit (SMMU), AXI translation buffer units (TBU), and TZ control registers for protection within the PS AXI infrastructure.

For more information, on TrustZone, Security, and Anti-Tamper measures, refer to the Zynq UltraScale+ Device Technical Reference Manual (UG1085). Isolation Methods in Zynq UltraScale+ MPSoCs (XAPP1320) provides a detailed example of implementing design isolation for the PS sub-systems.

This application note extends the isolation methods, described in XAPP1320, into the programmable Logic (PL) sub-system of the example design, by introducing a VHDL based XMPU PL softcore, to bridge the gap between PS and PL isolation methods including PS-to-PL interfaces.

**Note:** It is strongly recommended that you complete the isolation design tutorial in *Isolation Methods in Zynq UltraScale+ MPSoCs* (XAPP1320) prior to proceeding with the tutorials in this document. While the reference design in this application note specifically targets Zynq UltraScale+ MPSoC, all isolation methods apply to the Zynq UltraScale+ devices as well.

## Introduction

This application note includes all of the design concepts, functional descriptions, and specifications. If you need to fast-track the use of the XMPU in a PL design, you may skip ahead to the tutorials provided in the Isolation Example Design section, and refer to the Overview, Functional Description, and XMPU\_PL Usage Examples sections as needed.

Xilinx is creating an environment where employees, customers, and partners feel welcome and included. To that end, we're removing non-inclusive language from our products and related collateral. We've launched an internal initiative to remove language that could exclude people or reinforce historical biases, including terms embedded in our software and IPs. You may still find examples of non-inclusive language in our older products as we work to make these changes and align with evolving industry standards. Follow this link for more information.

The reference design provided with this application note ( $\mathtt{zup1\_xmpu\_v1\_0}$ ) implements an XMPU\_PL for Zynq PL designs. It is a functionally tested reference IP that includes software driver support for bare-metal standalone OS applications, but it is not a part of the Xilinx LogiCORE Library. This application note provides a detailed functional description of the XMPU\_PL module with implementation and usage tutorials.

### **Hardware and Software Requirements**

The hardware and software requirements for the reference design system includes:

- Xilinx ZCU102 evaluation platform

- Two USB type-A to USB mini-B cables (for UART, JTAG communication)

- Secure Digital (SD) memory card

- Xilinx Vivado® Design Suite and Vitis™ 2021.1 or newer

- Serial communication terminal software (such as Tera Term or PuTTY)

#### **Overview**

The Processor System (PS) of the Zynq UltraScale+ devices have eight XMPUs to protect the memory and FPD slaves (XMPU\_OCM, XMPU\_DDR (6) and XMPU\_FPD), and one XPPU to protect the LPD peripherals. However, the PL AXI interfaces are not protected by any of these protection units.

The reference design implements the XMPU\_PL function for Zynq UltraScale+ devices. It serves as both a memory and peripheral protection unit for the PL and utilizes a functional interface, similar to the XMPUs in the PS. Multiple XMPU\_PL(s) may be used within the PL design to selectively monitor AXI transactions. XMPU\_PL(s) may be used to provide protection to PL slaves from the PS masters, PS slaves from PL masters (such as MicroBlaze, PicoBlaze processors, DMAs, or custom PL masters), or anywhere within the user's PL AXI network design.

The Zynq UltraScale+ MPSoCs and Zynq UltraScale+ RFSoCs have three (PS->PL) AXI4-master I/Fs that may transmit AXI transactions originating from any one of fifty (50) PS masters. See *Appendix A: Master ID List* for a list of PS masters. The PS->PL master I/Fs are:

- M\_AXI\_HPM0\_LPD

- M\_AXI\_HPM0\_FPD

- M\_AXI\_HPM1\_FPD

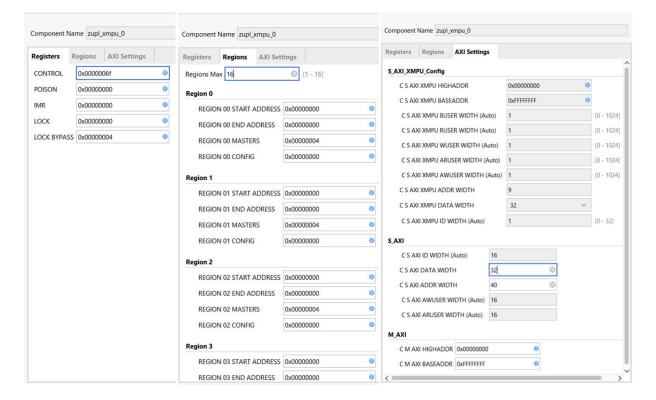

The XMPU\_PL verifies that a system master has access to an address and poisons unauthorized transactions. The XMPU\_PL IP Integrator (IPI) symbol is shown in the following figure and provides the following features:

- Slave AXI4-Full (32 bit) port for XMPU run-time configuration

- Slave AXI4-Full (32, 64, 128 bit) port for incoming AXI transactions to be monitored

- Master AXI4-Full port for transferred incoming transactions

- A single IRQ interrupt output for access attempt violations

- Up to 16 (sixteen) individually configurable address regions

- Supports Secure, Non-Secure, and Strictly Non-Secure regions

- Supports IP integrator with busif ports

- Supports static configuration through Customization GUI

- Detects the originating AXI master ID of incoming PS AXI transactions

- Detects the security level of transactions

- Supports poison-by-address and poison-by-attribute

- Supports both internal and external AXI Sink

Figure 1: zupl\_xmpu\_v1\_0 (XMPU\_PL) IPI Symbol

Figure 2: zupl xmpu v1 0 (XMPU PL) IPI Customization Window

## **XMPU PL Configuration**

The XMPU\_PL may be statically configured from the customization window in the IP Integrator. Refer to the Functional Description section for a detailed description of all the configuration registers. Alternatively, the XMPU\_PL may be dynamically configured at run-time through the S\_AXI\_XMPU\_AXI4 slave port. While some of the run-time interface registers are read-only, their initialization values may be controlled through the static interface of the customization GUI.

S\_AXI\_XMPU has been implemented as an AXI4-Full I/F to ensure the Master ID of the originating AXI master is available within the transaction, via the AxUser bus. AxUser is collectively AWUSER and ARUSER for write and read transactions, respectively.

The Regions Max, S\_AXI\_ DATA\_WIDTH, M\_AXI\_BASEADDR, and M\_AXI\_HIGHADDR values are VHDL parameters only and not available through the run-time interface.

Regions Max sets the number of AXI Monitors to be synthesized in the core. The SW cannot define more regions than this setting. The absolute maximum value is sixteen (16). Reducing this number decreases the utilized PL resources by ~130 LUTs per region. This parameter is exported to xparameters.h. Region configuration and Master IDs are explained in the following section.

S AXI DATA WIDTH sets the width of the AXI data bus to be protected. This must be selected by the user to match the upstream master. Available options are: 32, 64, 128-bit.

M AXI BASEADDR and M AXI HIGHADDR are not required to be set, and have no impact on the core's functionality. Their presence is for the user's convenience and they provide the address range mapped to M\_AXI. These values are exported to the xparameters.h

## **Configuration Lock**

The LOCK register, when set, locks out changes to all configuration registers (except interrupt status and control) by making the configuration registers read only. The lock can only be bypassed by those Master IDs enabled in the LOCK\_BYPASS register. However, any master with a mapped address to the S\_AXI\_XMPU port can enable, disable, or respond to XMPU\_PL interrupts.

**Note:** If LOCK is statically set and no Master IDs are enabled in the LOCK\_BYPASS, then run-time configuration changes will not be possible. Refer to Isolating the XMPU\_PL Configuration on how to restrict read access to the configuration registers.

## **Regions**

Each XMPU\_PL provides up to sixteen (16) regions, numbered from zero (0) to fifteen (15). Each region is defined by a start address and an end address. Regions are 256B address aligned. The start and ending address registers hold the upper 32 bits of a 40 bit address[39:8].

When a memory space is included in more than one XMPU\_PL region configuration, if any of the corresponding regions trigger a violation, then the transaction is poisoned in accordance with the REGION CONFIG register option settings. Refer to Functional Description for a detailed description.

Each region can be independently enabled or disabled. If a region is disabled, it is not used for protection checking. Each region is assigned a list of masters that are authorized to access the region and has an independent security and check type selection.

- Secure: Secure transactions from authorized masters.

- Non-Secure: Secure and non-secure transactions from authorized masters.

- Non-Secure Strict Check Type: Non-secure transactions from authorized masters.

**Note:** Non-secure transactions from unauthorized masters will be poisoned.

If the address requested does not match any of the regions, then the XMPU\_PL takes the default action (allow or poison) as specified in the control register options. There are three ways to poison a request:

- Poison by address internally

- Divert the transaction to a sink that resides inside the core.

- Poison by address externally

- Forward the transaction replacing the address with the value in the poison register.

- Poison by attribute

Forward the transaction with a poison attribute (AxProt[1]=1)

#### **Master IDs**

Each XMPU\_PL Region and Lock\_Bypass monitors use the Master ID in each AXI transaction to validate the transaction. The REGION MASTERS register selects specific Masters. Refer to the Functional Description section for a detailed register description. All the Master IDs and associated Masks are stored in the zupl\_xmpu reference design vhdl package. The Master ID is masked by a [MIDM] bit field and then compared against a [MID] bit field.

Depending on AXI Security Permission checks, the transaction is allowed when the following equation is satisfied:

For more information on Master ID, refer to the Zynq UltraScale+ Device Technical Reference Manual (UG1085). There are fifty masters with unique IDs in the Zynq UltraScale+ MPSoCs. These are summarized in the Appendix A: Master ID List.

**Note:** The user need not know the specific MasterID values to configure the XMPU\_PL Region and Lock\_Bypass. As described in the Functional Description section, each bit position within those registers corresponds to a particular master (master-pairs for DMA channels) that are enabled or disabled.

#### **AXI Permissions**

The AxProt[2:0] (ARPROT and AWPROT, collectively) holds the permission levels for the AXI transaction. AxProt[0] indicates the Privilege level, AxProt[1] indicates Security level, and AxProt[2] indicates whether it's an instruction or data type transaction. The definitions and values are shown in Table 1.

| ARPROT: | Read Transaction Permissions  |

|---------|-------------------------------|

|         |                               |

| AWPROT: | Write Transaction Permissions |

**Table 1: AXI Protection Permissions**

| AxPROT[2:0] | AXI Protection Level                                 |

|-------------|------------------------------------------------------|

| 000         | Data Access, <b>Secure</b> , Unprivileged            |

| 001         | Data Access, <b>Secure</b> , Privileged              |

| 010         | Data Access, <b>Non-secure</b> , Unprivileged        |

| 011         | Data Access, <b>Non-secure</b> , Privileged          |

| 100         | Instruction Access, <b>Secure</b> , Unprivileged     |

| 101         | Instruction Access, <b>Secure</b> , Privileged       |

| 110         | Instruction Access, <b>Non-secure</b> , Unprivileged |

| 111         | Instruction Access, <b>Non-secure</b> , Privileged   |

AxProt[1] holds the security level for the AXI transaction. In the Processing System (PS), the TrustZone (TZ) setting for an AXI master is transferred over the AXI3 infrastructure using AxUser[10], but this information is not transferred to the AXI4 PL interfaces. Unfortunately, AxProt[1] does not directly reflect the TZ setting for all masters.

PS masters having a TZ NONSECURE register setting, such as DMAs, use <code>AxProt[1]</code> to communicate the AXI Permission security level in accordance with its TZ setting. Therefore, regardless of whether isolation is enabled in the design, the DMA may be dynamically configured to make AXI transfers with either secure or non-secure AXI Permissions.

The APU sets AxProt bits in accordance with the exception level of the thread requesting the AXI transfer. Bare-metal standalone OS applications always execute at EL3 (AxProt[1]=0) which is AXI secure. Therefore, even if an APU application may be considered non-secure in the Isolated System, its AXI Permissions indicate it as it being secure. This is why you must use Master IDs to control region access authorization. However, APU applications running from a Linux kernel execute at EL0 (AxProt[1]=1) which is non-secure and may be elevated by the OS or hypervisor.

The RPU and PMU do not support multiple exception levels and always operate at EL3. Therefore, you must use the MasterIDs to block their access to a region.

**TIP:** Non-Secure Strict Check Type Regions will only allow transactions from authorized masters with a Non-Secure TZ setting, like DMAs, or with multiple exception level settings, such as a Linux app in the APU. Otherwise, simply define the region as secure and specify which masters should have access in the region configuration.

## **Poison By Address**

Poison-by-Address is enabled by default in the XMPU\_PL CTRL control register. This causes a poisoned transaction to be redirected to either an internal or external sink. If external sink is selected, then the poisoned transaction is redirected to the address specified in the *POISON* register. As with the region start and end registers, the poison register is 256B aligned and specifies the upper 32 bits of the 40-bit address[39:8].

Internal Sink is enabled by default and causes the poisoned transaction to be redirected to a hidden peripheral inside the core.

**Note:** The internal sink is not visible to, or address mapped, in the system.

DECERR (decode error) is the default setting in the CTRL register. The DECERR will likely result in an EXCEPTION in the processor that receives the response. Exception Handling should be installed in the application to avoid hanging the processor.

The data that is written to the internal sink is not stored and gets lost. The external sink option exists in the event that the designer wishes to construct their own SINK peripheral in order to capture additional information from the transaction.

Table 2: SINK AXI Response

| AXI Response Encoding |          |              |  |  |  |  |  |  |

|-----------------------|----------|--------------|--|--|--|--|--|--|

| RRESP[1:0] BRESP[1:0] | Response | Description  |  |  |  |  |  |  |

| 0                     | OKAY     | ОК           |  |  |  |  |  |  |

| 1                     | EXOKAY   | Exclusive OK |  |  |  |  |  |  |

| 2                     | SLVERR   | Slave Error  |  |  |  |  |  |  |

#### Table 2: SINK AXI Response (cont'd)

| AXI Response Encoding |                     |              |  |  |  |

|-----------------------|---------------------|--------------|--|--|--|

| 3                     | DECERR <sup>1</sup> | Decode Error |  |  |  |

#### Notes:

1. Default

## **Poison by Attribute**

The Poison-by-Attribute is enabled by default in the CTRL register. This results in any poisoned transaction that is transferred to the M\_AXI port to have non-secure privilege set (AxProt[1]=1).

There are only two conditions when this occurs:

- Poison by address is not enabled

- Poison by address is enabled with external sink

**TIP:** Using the Poison-by-Attribute while disabling Poison-by-Address can also be used with the secure option in the AXI interconnect advanced settings. The method is demonstrated in the XMPU\_PL Usage Examples section, Isolating Secure Slaves.

## **Functional Description**

This section provides further details on the core's architecture, functionality, and the configuration register module.

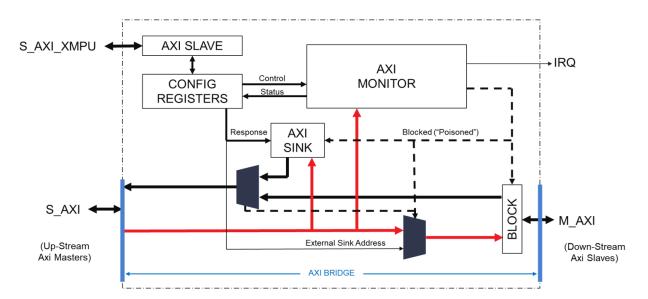

## XMPU\_PL Architecture

The XMPU\_PL block diagram is shown in the following figure. S\_AXI (slave) and M\_AXI (master) AXI4 ports form an AXI Bridge that passes through authorized transactions and blocks unauthorized transactions. AXI Read and Write channels are completely independent of each other. If one channel is blocked for a violation, the other proceeds; if it does not trigger a violation.

Figure 3: XMPU\_PL Block Diagram

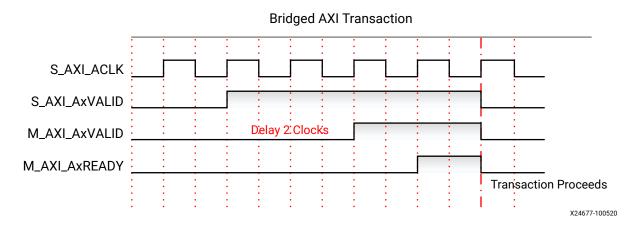

The bridge relationship makes the XMPU\_PL transparent to the system address mapping. Upstream masters still map directly to down-stream slaves. Incoming transactions are subject to a two clock-cycle delay while the AXI-Monitor determines whether to allow or block. An example timing diagram is shown in the following figure.

Figure 4: AXI Bridge Monitoring Delay Timing Diagram

Transactions between the upstream master and downstream slave are initiated by the master with the VALID signal. The XMPU\_PL initially delays the transmission of the VALID signal to evaluate the transaction. If a transaction is not to be blocked (not poisoned) it proceeds without any additional or accumulative clock cycle latency. This results in all following transitions of signals are not delayed.

Each region in the XMPU\_PL is independently activated and monitored. If a region is enabled and the requested transaction address is within its range, then the MasterID is compared to the enabled masters, and the AXI permissions are compared against the region's configuration settings to determine if a violation has been triggered. If any region triggers a violation, then the transaction is blocked in accordance with the poisoning type configuration settings.

When a violation occurs, the status is communicated back to the Configuration Registers Module to capture the transaction's target address and originating MasterID into the error status registers. If the violation corresponds to an enabled interrupt flag, then the ISR register is updated and the IRQ output is asserted.

## **Module Registers Summary**

The XMPU\_PL module registers and address offsets are shown in the following table. The following sections provide the bit field definitions for each module register.

**Table 3: XMPU\_PL Module Registers**

| Register Name      | Address Offset | Туре    | Description                          |  |  |  |  |  |

|--------------------|----------------|---------|--------------------------------------|--|--|--|--|--|

| Control and Status |                |         |                                      |  |  |  |  |  |

| CTRL               | 0x000          | mixed   | Control and Implementation           |  |  |  |  |  |

| ERR_STATUS1        | 0x004          | ro      | Error Status, Violation<br>Address   |  |  |  |  |  |

| ERR_STATUS2        | 0x008          | ro      | Error Status, Violation<br>Master ID |  |  |  |  |  |

| POISON             | 0x00C          | rw      | External Sink Address                |  |  |  |  |  |

| ISR                | 0x010          | mixed   | Interrupt Status and Clear           |  |  |  |  |  |

| IMR                | 0x014          | ro      | Interrupt Mask                       |  |  |  |  |  |

| IEN                | 0x018          | wo      | Interrupt Enable                     |  |  |  |  |  |

| IDS                | 0x01C          | wo      | Interrupt Disable                    |  |  |  |  |  |

| LOCK               | 0x020          | rw      | Register Write Lock                  |  |  |  |  |  |

| LOCK_BYPASS        | 0x024          | mixed   | Enable Master Access                 |  |  |  |  |  |

| REGIONS            | 0x028          | ro      | Number of Active Regions             |  |  |  |  |  |

|                    | Region         | Control | •                                    |  |  |  |  |  |

| R{00:15}_START     | 0x100+         | mixed   | Region starting base address         |  |  |  |  |  |

| R{00:15}_END       | 0x104+         | ro      | Region ending address                |  |  |  |  |  |

| R{00:15}_MASTERS   | 0x108+         | ro      | Select authorized PS Masters         |  |  |  |  |  |

| R{00:15}_CONFIG    | 0x10C+         | rw      | Enable and Configure                 |  |  |  |  |  |

## **CTRL Control Register**

The CTRL register is shown in the following table.

Table 4: XMPU\_PL CTRL Register Bit Field Summary

| Field Name | Bits | Туре | Reset Value | Description |

|------------|------|------|-------------|-------------|

| Reserved   | 31:7 | ro   | 0x0         | Reserved    |

Table 4: XMPU\_PL CTRL Register Bit Field Summary (cont'd)

| Field Name        | Bits | Туре | Reset Value | Description                                                                                                                                                                                                                                                |

|-------------------|------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PoisonAxiResp     | 6:5  | rw   | 0x3         | Select AXI response to poisoned transactions.  Ox0: OKAY  Ox0: EXOKAY  Ox2: SLVERR  X3: DECERR  Note: If ExternalSinkEn is enabled, then the peripheral at the address specified in the POISON register transmits the response.                            |

| ExternalSinkEn    | 4    | rw   | 0×0         | 0: Transactions poisoned by address terminate in the XMPU_PL  1: Transactions poisoned by address are routed to a sink specified by POISON[PL_SINK_ADDR]                                                                                                   |

| PoisonAttributeEn | 3    | rw   | 0x1         | 0: Transaction is not poisoned. AxProt[1] remains at original value.  1: Enables Poison by Address. Transaction routed to internal or external sink address. See CTRL[ExternalSinkEn]                                                                      |

| PoisonAddressEn   | 2    | rw   | 0x1         | 0: Transaction is not poisoned. Transaction proceeds to original address.  1: Enables Poison by Address. Transaction routed to internal or external sink address. See CTRL[ExternalSinkEn]                                                                 |

| DefWrAllowed      | 0    | rw   | 0x1         | Default Write Allowed. Ensure the following steps are implemented if a write transaction address and master ID miss in the Region List:  0: poison the transaction with a Write Permission Violation  1: transaction allowed, regardless of security level |

| DefRdAllowed      | 0    | rw   | 0x1         | Default Read Allowed. If a read transaction address and master ID miss in the Region List, then: 0: poison the transaction with a Read Permission Violation 1: transaction allowed, regardless of security level                                           |

## **Error Status 1 Register**

The ERR\_STATUS1 register is shown in the following table. The first AXI violation is recorded. Once an ISR[3:1] status bit is set, subsequent violations are not recorded, but their transactions are poisoned. The status bits are cleared by a system reset and can be cleared by software.

Table 5: ERR\_STATUS1 (XMPU\_PL) Register Bit Field Summary

| Field Name | Bits | Туре | Reset<br>Value | Description                                                     |

|------------|------|------|----------------|-----------------------------------------------------------------|

| AXI_ADDR   | 31:0 | ro   | 0x0            | Address bits of a poisoned read or write transaction. Readonly. |

## **Error Status 2 Register**

The ERR\_STATUS2 register is shown in the following table. The first AXI violation is recorded. Once an ISR[3:1] status bit is set, subsequent violations are not recorded, but their transactions are poisoned. The status bits are cleared by a system reset and can be cleared by a software.

Table 6: ERR\_STATUS2 (XMPU\_PL) Register Bit Field Summary

| Field Name | Bits  | Туре | Reset<br>Value | Description                                                    |

|------------|-------|------|----------------|----------------------------------------------------------------|

| Reserved   | 31:10 | ro   | 0x0            | Reserved                                                       |

| AXI_ID     | 9:0   | ro   | 0x0            | Master ID from a poisoned read or write transaction. Readonly. |

## **Poison Address Register**

The POISON register is shown in the following table.

Table 7: POISON (XMPU\_PL) Register Bit Field Summary

| Field Name   | Bits | Туре | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                       |

|--------------|------|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PL_SINK_ADDR | 31:0 | rw   | 0x00800000     | The value is set by user for poison base address, determined by PL Address Mapping. The XMPU replaces the incoming AXI address (39 down to 8) with the PL_SINK_ADDR. Address (7 down to 0) is retained from the originating address for alignment. Downstream, the XMPU_PL_Sink unit responds to the transaction. |

## **ISR Interrupt Status Register**

The ISR register interrupts are shown in the following table. The bits in the status register are sticky and remain asserted until cleared by writing a 1 to the asserted bit.

Reading AXI Access Violations:

- 0: no interrupt request

- 1: interrupt requested

Writing AXI Access Violations:

- 0: no effect

- 1: clear bit to 0

If a Status bit is 1 and its Mask is 0, then the IRQ interrupt signal is activated to the interrupt controller. The first AXI violation is recorded. Once an ISR[3:1] status bit is set, subsequent AXI violations are not recorded, but their transactions are poisoned. The status bits are cleared by a system reset and can be cleared by a software

Table 8: ISR (XMPU\_PL) Register Bit Field Summary

| Field Name  | Bits | Туре | Reset<br>Value | Description                                                                                                                                                                       |

|-------------|------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved    | 31:4 | ro   | 0x0            | Reserved                                                                                                                                                                          |

| SecurityVIO | 3    | wtc  | 0x0            | Security violation by AXI Master: A non-secure master tries to access a secure memory space.                                                                                      |

| WrPermVIO   | 2    | wtc  | 0x0            | Write Permission violation by AXI Master. Write access attempted to enabled region with WrAllowed = 0. Or the transaction missed in the region list and CNTRL [DefWrAllowed] = 0. |

| RdPermVIO   | 1    | wtc  | 0x0            | Read Permission violation by AXI Master. Read access attempted to enabled region with RdAllowed = 0.The transaction missed in the region list and CNTRL [DefRdAllowed] = 0.       |

| Reserved    | 0    | ro   | 0x0            | Reserved                                                                                                                                                                          |

## **IMR Interrupt Mask Register**

The IMR register is shown in the following table. For each violation interrupt mask bit:

- 0: enabled.

- 1: masked (disabled). If the ISR bit = 1 (asserted interrupt) and the IMR bit = 0 (not masked), then the IRQ to the interrupt controller is asserted.

Software checks the ISR to determine the cause of the interrupt. Read only.

Table 9: IMR (XMPU\_PL) Register Bit Field Summary

| Field Name  | Bits | Туре | Reset<br>Value | Description                              |

|-------------|------|------|----------------|------------------------------------------|

| Reserved    | 31:4 | ro   | 0x0            | Reserved                                 |

| SecurityVIO | 3    | ro   | 0x1            | Security violation by AXI master         |

| WrPermVIO   | 2    | ro   | 0x1            | Write Permission violation by AXI Master |

| RdPermVIO   | 1    | ro   | 0x1            | Read Permission violation by AXI Master  |

| Reserved    | 0    | ro   | 0x0            | Reserved                                 |

## **IEN Interrupt Enable Register**

The IEN register is shown in the following table.

- 0: no effect.

- 1: enable interrupt (sets mask = 0). Write-only.

Table 10: IEN (XMPU\_PL) Register Bit Field Summary

| Field Name | Bits | Туре | Reset<br>Value | Description |

|------------|------|------|----------------|-------------|

| Reserved   | 31:4 | ro   | 0x0            | Reserved    |

Table 10: IEN (XMPU\_PL) Register Bit Field Summary (cont'd)

| Field Name  | Bits | Туре | Reset<br>Value | Description                      |

|-------------|------|------|----------------|----------------------------------|

| SecurityVIO | 3    | wo   | 0x0            | Security violation by AXI Master |

| WrPermVIO3  | 2    | wo   | 0x0            | Write Permission violation       |

| RdPermVIO1  | 1    | wo   | 0x0            | Read Permission violation        |

| Reserved    | 0    | wo   | 0x0            | Reserved                         |

## **IDS Interrupt Disable Register**

The IDS register is shown in the following table.

- 0: no effect.

- 1: disable interrupt (sets mask = 1). Write-only.

Table 11: IDS (XMPU\_PL) Register Bit Field Summary

| Field Name  | Bits | Туре | Reset<br>Value | Description                      |

|-------------|------|------|----------------|----------------------------------|

| Reserved    | 31:4 | ro   | 0x0            | Reserved                         |

| SecurityVIO | 3    | wo   | 0x0            | Security violation by AXI Master |

| WrPermVIO   | 2    | wo   | 0x0            | Write Permission violation       |

| RdPermVIO   | 1    | wo   | 0x0            | Read Permission violation        |

| Reserved    | 0    | wo   | 0x0            | Reserved                         |

## **LOCK Register**

The LOCK register is shown in the following table.

Register writes to ZUP\_XMPU\_PL may be done by any bus masters when LOCK [RegWrDis] = 0. When LOCK [RegWrDis] = 1, all register writes may only be done by secure bus masters enabled in LOCK\_BYPASS register. The write lock prevents all other masters from writing to all registers except the interrupt status registers: ISR, IMR, IEN and IDS.

Note: All ZUP\_XMPU\_PL registers are readable by secure or non-secure bus masters.

**Note:** Regardless of the LOCK [RegWrDis] setting, the status registers are always writable by secure and non-secure bus masters.

Table 12: LOCK (XMPU\_PL) Register Bit Field Summary

| Field Na | me  | Bits | Туре | Reset<br>Value | Description                                                                                                                                                                                                        |

|----------|-----|------|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RegWrD   | vis | 0    | rw   | 0×0            | Register Write Disable. Applies to all registers except ISR, IMR, IEN and IDS.  0: read/write allowed  1: read-only  Once this bit is set, it can only be cleared by a master enabled in the LOCK_BYPASS register. |

### **BYPASS Register**

The BYPASS register is shown in the following table.

Register writes to ZUP\_XMPU\_PL may be done by any bus masters when LOCK [RegWrDis] = 0. When LOCK [RegWrDis] = 1, all register writes may only be done by secure bus masters enabled in LOCK\_BYPASS register. The write lock prevents all other masters from writing to all registers except the status registers: ISR, IMR, IEN, and IDS.

Note: All ZUP\_XMPU\_PL registers are readable by secure or non-secure bus masters.

**Note:** Regardless of the LOCK [RegWrDis] setting, the status registers are always writable by secure and non-secure bus masters.

Table 13: LOCK\_BYPASS (XMPU\_PL) Register Bit-Field Summary

| Field Name       | Bits | Туре | Reset<br>Value | Description                            |

|------------------|------|------|----------------|----------------------------------------|

| Reserved         | 31   | ro   | 0x0            | Reserved                               |

| MID_FPD_DMA[6:7] | 30   | rw   | 0x0            | Enable FPD DMA [ch 6:7]                |

| MID_FPD_DMA[4:5] | 29   | rw   | 0x0            | Enable FPD DMA [ch 4:5]                |

| MID_FPD_DMA[2:3] | 28   | rw   | 0x0            | Enable FPD DMA [ch 2:3]                |

| MID_FPD_DMA[0:1] | 27   | rw   | 0x0            | Enable FPD DMA [ch 0:1]                |

| MID_DP_DMA[4:5]  | 26   | rw   | 0x0            | Enable DisplayPort DMA [ch 4:5]        |

| MID_DP_DMA[2:3]  | 25   | rw   | 0x0            | Enable DisplayPort DMA [ch 2:3]        |

| MID_DP_DMA[0:1]  | 24   | rw   | 0x0            | Enable DisplayPort DMA [ch 0:1]        |

| MID_PCIE         | 23   | rw   | 0x0            | Enable PCIe                            |

| MID_DAP_AX1      | 22   | rw   | 0x0            | Enable Debug Access Port AXI           |

| MID_GPU          | 21   | rw   | 0x0            | Enable GPU                             |

| MID_SATA1        | 20   | rw   | 0x0            | Enable SATA1                           |

| MID_SATA0        | 19   | rw   | 0x0            | Enable SATA0                           |

| MID_APU          | 18   | rw   | 0x0            | Enable APU.                            |

|                  |      |      |                | <b>Note:</b> Requires that AxProt[1]=0 |

| MID_GEM3         | 17   | rw   | 0x0            | Enable GEM3                            |

| MID_GEM2         | 16   | rw   | 0x0            | Enable GEM2                            |

| MID_GEM1         | 15   | rw   | 0x0            | Enable GE1                             |

Table 13: LOCK\_BYPASS (XMPU\_PL) Register Bit-Field Summary (cont'd)

| Field Name       | Bits | Туре | Reset<br>Value | Description                  |

|------------------|------|------|----------------|------------------------------|

| MID_GEM0         | 14   | rw   | 0x0            | Enable GEM0                  |

| MID_QSPI         | 13   | rw   | 0x0            | Enable QSPI                  |

| MID_NAND         | 12   | rw   | 0x0            | Enable NAND                  |

| MID_SD1          | 11   | rw   | 0x0            | Enable SD1                   |

| MID_SD0          | 10   | rw   | 0x0            | Enable SD0                   |

| MID_LPD_DMA[6:7] | 9    | rw   | 0x0            | Enable LPD DMA [ch 6:7]      |

| MID_LPD_DMA[4:5] | 8    | rw   | 0x0            | Enable LPD DMA [ch 4:5]      |

| MID_LPD_DMA[2:3] | 7    | rw   | 0x0            | Enable LPD DMA [ch 2:3]      |

| MID_LPD_DMA[0:1] | 6    | rw   | 0x0            | Enable LPD DMA [ch 0:1]      |

| MID_DAP_APB      | 5    | rw   | 0x0            | Enable Debug Access Port APB |

| MID_USB1         | 4    | rw   | 0x0            | Enable USB1                  |

| MID_USB0         | 3    | rw   | 0x0            | Enable USB0                  |

| MID_PMU          | 2    | rw   | 0x1            | Enable PMU                   |

| MID_RPU1         | 1    | rw   | 0x0            | Enable RPU1                  |

| MID_RPU0         | 0    | rw   | 0x0            | Enable RPU0                  |

## **Regions Register**

The regions register is shown in the following table. The table displays the number of secure regions enabled. It is a *read only* register.

Table 14: Regions (XMPU\_PL) Register Bit-Field Summary

| Field Name | Bits | Туре | Reset<br>Value | Description                                                                                                                      |

|------------|------|------|----------------|----------------------------------------------------------------------------------------------------------------------------------|

| Reserved   | 31:5 | ro   | 0x0            | Reserved                                                                                                                         |

| ENABLED    | 4:0  | ro   | 0x0            | Number of active regions  Note: There are 16 available regions that are independently enabled in the R[region]_CONFIG registers. |

## Rxx\_START Region Starting Address Register

The R[n]\_START register is shown in the following table. Each region is defined by a start and end address base addresses mapped to the PL.

Note: Address Offset: 0x00000[n]00

Table 15: R[n]\_START (XMPU\_PL) Register Bit Field Summary

| Field Name | Bits | Туре | Reset<br>Value | Description                                          |

|------------|------|------|----------------|------------------------------------------------------|

| ADDR       | 31:0 | rw   | 0x0            | AXI address within the PL.                           |

|            |      |      |                | Note: Bits [31:0] correspond to address bits [39:8]. |

## Rxx\_END Region Ending Address Register

The R[n]\_END register is shown in the following table. Each region is defined by a start and end address base addresses mapped to the PL.

Note: Address Offset: 0x00000[n]04

Table 16: R[n]\_END (XMPU\_PL) Register Bit Field Summary

| Field name | Bits | Туре | Reset<br>Value | Description                                          |

|------------|------|------|----------------|------------------------------------------------------|

| ADDR       | 31:0 | rw   | 0x0            | AXI address within the PL.                           |

|            |      |      |                | Note: Bits [31:0] correspond to address bits [39:8]. |

## Rxx\_MASTERS Region Masters Register

The AXI\_MasterID from the requester is compared with all authorized secure MasterIDs for the region addressed. If the originating master is authorized: *False*, transaction is poisoned; if it is *True*, transaction is forwarded downstream.

Note: Address Offset: 0x00000[n]08

Note: PMU is always authorized by default.

The R[n]\_MASTERS register is shown in the following table.

Table 17: R[n]\_MASTERS (XMPU\_PL) Register Bit Field Summary

| Field Name       | Bits | Туре | Reset<br>Value | Description                     |

|------------------|------|------|----------------|---------------------------------|

| Reserved         | 31   | ro   | 0x0            | Reserved                        |

| MID_FPD_DMA[6:7] | 30   | rw   | 0x0            | Enable FPD DMA [ch 6:7]         |

| MID_FPD_DMA[4:5] | 29   | rw   | 0x0            | Enable FPD DMA [ch 4:5]         |

| MID_FPD_DMA[2:3] | 28   | rw   | 0x0            | Enable FPD DMA [ch 2:3]         |

| MID_FPD_DMA[0:1] | 27   | rw   | 0x0            | Enable FPD DMA [ch 0:1]         |

| MID_DP_DMA[4:5]  | 26   | rw   | 0x0            | Enable DisplayPort DMA [ch 4:5] |

| MID_DP_DMA[2:3]  | 25   | rw   | 0x0            | Enable DisplayPort DMA [ch 2:3] |

| MID_DP_DMA[0:1]  | 24   | rw   | 0x0            | Enable DisplayPort DMA [ch 0:1] |

Table 17: R[n]\_MASTERS (XMPU\_PL) Register Bit Field Summary (cont'd)

| Field Name       | Bits | Туре | Reset<br>Value | Description                             |

|------------------|------|------|----------------|-----------------------------------------|

| MID_PCIE         | 23   | rw   | 0x0            | Enable PCIe                             |

| MID_DAP_AXI      | 22   | rw   | 0x0            | Enable Debug Access Port AXI            |

| MID_GPU          | 21   | rw   | 0x0            | Enable GPU                              |

| MID_SATA1        | 20   | rw   | 0x0            | Enable SATA1                            |

| MID_SATA0        | 19   | rw   | 0x0            | Enable SATA0                            |

| MID_APU          | 18   | rw   | 0x0            | Enable APU.                             |

|                  |      |      |                | <b>Note:</b> Requires that AxProt[1]=0. |

| MID_GEM3         | 17   | rw   | 0x0            | Enable GEM3                             |

| MID_GEM2         | 16   | rw   | 0x0            | Enable GEM2                             |

| MID_GEM1         | 15   | rw   | 0x0            | Enable GEM1                             |

| MID_GEM0         | 14   | rw   | 0x0            | Enable GEM0                             |

| MID_QSPI         | 13   | rw   | 0x0            | Enable QSPI                             |

| MID_NAND         | 12   | rw   | 0x0            | Enable NAND                             |

| MID_SD1          | 11   | rw   | 0x0            | Enable SD1                              |

| MID_SD0          | 10   | rw   | 0x0            | Enable SD0                              |

| MID_LPD_DMA[6:7] | 9    | rw   | 0x0            | Enable LPD DMA [ch 6:7]                 |

| MID_LPD_DMA[4:5] | 8    | rw   | 0x0            | Enable LPD DMA [ch4:5]                  |

| MID_LPD_DMA[2:3] | 7    | rw   | 0x0            | Enable LPD DMA [ch 2:3]                 |

| MID_LPD_DMA[0:1] | 6    | rw   | 0x0            | Enable LPD DMA [ch 0:1]                 |

| MID_DAP_APB      | 5    | rw   | 0x0            | Enable Debug Access Port APB            |

| MID_USB1         | 4    | rw   | 0x0            | Enable USB1                             |

| MID_USB0         | 3    | rw   | 0x0            | Enable USB0                             |

| MID_PMU          | 2    | rw   | 0x1            | Enable PMU                              |

| MID_RPU1         | 1    | rw   | 0x0            | Enable RPU1                             |

| MID_RPU0         | 0    | rw   | 0x0            | Enable RPU0                             |

## Rxx\_CONFIG Region Configuration Register

The R[n]\_CONFIG register is shown in the following table. If a transaction address is within an enabled region's start and end addresses, then the [WrAllowed]/[RdAllowed] condition is checked. If the transaction R/W type is allowed, then the security Master ID check is performed. When more than one address region includes the transaction address (regions overlap) or if any region poisons the transaction, then it takes precedence.

Note: Address Offset: 0x00000[n]0C

Table 18: R[n]\_CONFIG (XMPU\_PL) Register Bit Field Summary

| Field Name | Bits | Туре | Reset<br>Value | Description |

|------------|------|------|----------------|-------------|

| Reserved   | 31:6 | ro   | 0x0            | Reserved    |

Table 18: R[n]\_CONFIG (XMPU\_PL) Register Bit Field Summary (cont'd)

| Field Name      | Bits | Туре | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|------|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MidCheckDisable | 5    | rw   | 0x0            | <ul> <li>0: [default] Master ID is checked. Transactions are only considered secure when MasterID aligns with R00_MASTERS[] Register.</li> <li>1: Disables Master ID check during security check. Any transaction with AxProt[1] = 0 will be considered Secure.</li> <li>Note: PL_Masters such as MicroBlaze™ do not propagate a MasterID. Setting MidCheckDisable = 1 allows WrAllow and RdAllow to define the permissions for the region.</li> </ul> |

| NSCheckType     | 4    | rw   | 0x0            | Non-secure Region Check Type. Secure masters may or may not be allowed to access Non-Secure (NS) memory regions.  0: relaxed checking; secure requests may access a non-secure (NS) region.  1: strict checking; secure requests may only access a secure region.  A non-secure access request can only access non-secure regions regardless of bit setting.                                                                                           |

| RegionNS        | 3    | rw   | 0x0            | Select security level of region: 0: secure. 1: non-secure (NS).                                                                                                                                                                                                                                                                                                                                                                                        |

| WrAllowed       | 2    | rw   | 0x1            | Allow writers to region: 0: not allowed; write transaction poisoned. 1: allowed.                                                                                                                                                                                                                                                                                                                                                                       |

| RdAllowed       | 1    | rw   | 0x1            | Allow writers to region: 0: not allowed; read transaction poisoned. 1: allowed.                                                                                                                                                                                                                                                                                                                                                                        |

| Enable          | 0    | rw   | 0x0            | Enable region: 0:disabled. 1: enabled.                                                                                                                                                                                                                                                                                                                                                                                                                 |

# XMPU\_PL Usage Examples

The Programmable Logic (PL) of the Zynq UltraScale+ devices allows the designer to create a fully custom system. This section provides some guidance on various design scenarios.

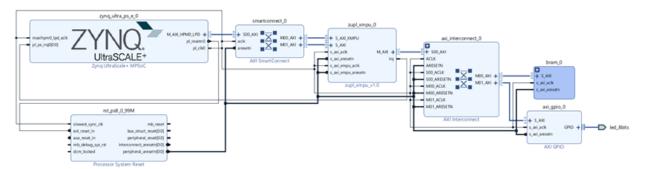

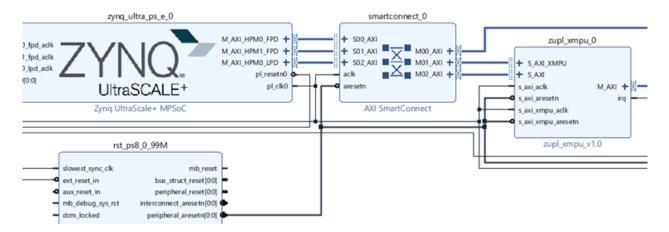

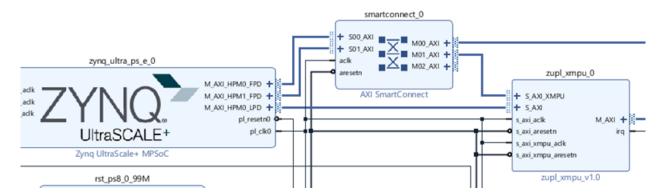

#### **AXI SmartConnect**

The XMPU\_PL functionality relies on access to the AXI MasterID contained in transactions from PS masters. The S\_AXI and S\_AXI\_XMPU have been implemented as AXI4 full interfaces to maintain the AxUser port connections which carries the MasterID values. If an inter-connect block is needed between the PS and the XMPU\_PL, use the AXI SmartConnect, as shown in the following figure, instead of AXI Interconnect. AXI Interconnect blocks to do not pass the AxUser bus and block the transmission of the MasterIDs. However, AXI Interconnect blocks may be used to connect to PL Masters or multiple end-point slaves, as MasterIDs are not utilized in those connections.

Figure 5: Using AXI SmartConnect

## Connecting to Multiple PS Master I/Fs

The SmartConnect combines multiple PS Master I/Fs into a single or multiple XMPU\_PLs, as evidenced from the following figure. Use SmartConnect instead of AXI-Interconnect to maintain access to PS MasterIDs.

Figure 6: Connecting Multiple PS Masters I/Fs

**Note:** The XMPU\_PL will not provide any AXI data width conversion. Use SmartConnect upstream, and/or AXI-Interconnect downstream, to provide any needed data or clock conversions between the PS Master and end-point PL-Slaves.

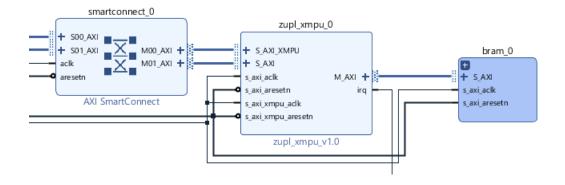

## Connecting Directly to PS Master I/Fs

The following figure shows the S\_AXI port of the XMPU\_PL may be directly connected to a PS master I/F. The data widths of both interfaces are selectable in their respective IP customization settings in the IP integrator. It is the responsibility of the user to ascertain that both are set to the same value.

Figure 7: PS Master I/F Direct Connection

**Note:** The XMPU\_PL will not provide any AXI data width conversion. Use SmartConnect upstream, and/or AXI-Interconnect downstream, to provide any needed data or clock conversions between the PS Master and end-point PL-Slaves.

## Connecting Directly to PL Slave I/Fs

An XMPU\_PL can be dedicated to a specific PL Slave and directly connected to the slave I/F without an interconnect stage. The XMPU\_PL AXI Data Width must be set in accordance with the slave's data width (typically, 32-bits).

Figure 8: Slave I/F Direct Connection

### Isolating the XMPU\_PL Configuration

As described in Configuration Lock, from the Overview section, the XMPU\_PL configuration registers can be write protected from unauthorized masters, but are still readable. The following figure demonstrates one way to completely isolate the configuration I/F.

Figure 9: Configuration I/F Isolation

Map the S\_AXI\_XMPU configuration slave port to the M\_AXI of the  $zupl_xmpu$  instead of using the Configuration Lock. Either the static or run-time configuration can define a region to protect the XMPU\_PL configuration from both read and write accesses.

**TIP:** If using a run-time application to define the XMPU\_PL configuration protection region, ensure that the DefRdAllowed and DefWrAllowed settings in the CTRL register are set. Otherwise, the run-time application may not have access to load the region parameters. DefRdAllowed and DefWrAllowed are set by default.

#### **Isolating Secure Slaves**

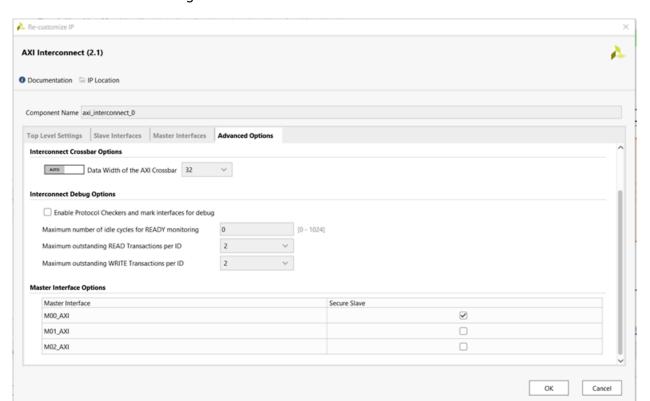

Enabling the Advanced Configuration Options in the AXI-Interconnect IPI customization window reveals Master Interface Options to select AXI Master output ports as being connected to Secure Slaves. The AXI-Interconnect customization window is shown in the following figure.

Figure 10: AXI-Interconnect Secure Slaves

Applying this setting causes the AXI-Interconnect to poison any transaction targeting a secure slave with an unsecure protection level (AxProt[1]=1).

This feature can be used in conjunction with the XMPU\_PL Poison-by-Attribute setting. By disabling Poison-by-Address setting in the XMPU\_PL, a poisoned transaction gets forwarded with non-secure protection level (AxProt[1]=1) causing the AXI-Interconnect to block the transaction.

Note: The SmartConnect does not have this feature.

**TIP:** The AXI-Interconnect Secure Slave feature may also be used to isolate secure slaves from Non-secure PL masters without the use of an XMPU\_PL.

### **Isolating PL Masters**

PL masters, such as MicroBlaze or AXI DMA, do not output a MasterID, nor do they utilize the AxUser side-channel. Therefore, such masters cannot be differentiated from each other on that basis. The following figure shows MicroBlaze processors that supports a Non\_Secure operating mode.

microblaze\_0 smartconnect\_0 + INTERRUPT M\_AXI\_DP + + DEBUG + 500 AXI zupl\_xmpu\_0 + 501\_AXI M\_AXI\_IP + M\_AXI\_P + ...

MB\_Halted

Sleep

Hibernate

Suspend

Dbg\_Wakeup

Dbg\_Continue

Pause\_Ack + S\_AXI\_XMPU Reset

Ext\_BRK + 503\_AXI M01\_AXI + + S.AXI Ext\_NM\_BRK MicroBlaze. adk s\_axi\_adk - Dbg\_Stop Wakeup[0:1] s\_axi\_xmpu\_adk AXI SmartConnect Reset\_Mode [0:1] s\_axi\_xmpu\_aresetn zupl\_xmpu\_v1.0 microblaze 1 + INTERRUPT + DEBUG M AXI DP 4 M AXL P + Clk MB\_Halted Ext\_BRK Sleep Ext\_NM\_BRK MicroBlaze: Dbg\_Stop Wakeup[0:1] Dbg\_Wakeup xlconstant\_1 Reset\_Mode (0:1) Dbg\_Continue Pause Ack Non\_Secure[0:3]

Figure 11: Secure and Non\_Secure MicroBlazes

The Non\_Secure[0:3] inputs may be asserted by a constant in the IPI block design. Each of the four bits control the Security level (AxProt[1]) for each of the AXI master ports  $(M\_AXI\_DP, M\_AXI\_IP, M\_AXI\_DC, M\_AXI\_IC)$ .

For the configuration above, it is recommended to disable the MasterID checks in the region configuration, Rxx\_CONFIG[MidCheckDisable], and rely on the security level to differentiate between the processors.

**TIP:** Using security level controls on the PL master enables the capability of using NonSecure with Strict Check Type regions.

microblaze\_0 + INTERRUPT + DEBUG + 500\_AXI + S01\_AXI ACLK Clk M\_AXI\_IP + Ext\_BRK Ext\_NM\_BRK ARESETN Sleep MicroBlaze: S00 ACLK = Ext\_NM\_BRK Dbg\_Stop Wakeup[0:1] Reset\_Mode[0:1] S00\_ARESETN M00\_ACLK M01 AXI + M00\_ARESE Dbg\_Continue M01\_ACLK M01\_ARESETN Non\_Secure[0:3] S01 ACLK microblaze 1 axi interconnect 2 + INTERRUPT + DEBUG M AXI DP + 501\_AXI + 502\_AXI Clk M\_AXI\_IP + Reset Ext\_BRK Ext\_NM\_BRK ACLK zupl\_xmpu\_0 ARESETN + S,AXI,XMPU MicroBlaze: S00 ACLK Dbg\_Stop Wakeup[0:1] SOO\_ARESE M00\_ACLK Dbg\_Wakeup s axi ack Reset\_Mode(0:1) M00\_ARESE **o** s\_axi\_areset Dbg Continue S01\_ACLK Pause Ark s axi xmpu adk = S01\_ARESETN \_axi\_xmpu\_arese Non\_Secu S02\_ACLK S02\_ARESETN

Figure 12: S AXI XMPU Isolated to Secure MicroBlaze

The previous figure shows an example of isolating the S\_AXI\_XMPU configuration port to the secure MicroBlaze. Additional protections are not required as only the secure MicroBlaze has a physical connection. Similarly, the designer can establish a path to any secure processor, in the PL or PS, of their choosing to configure and manage any XMPU\_PL in the system.

Figure 13: MicroBlaze with Dedicated XMPU

The previous example exhibits that each and every MicroBlaze processor has a dedicated XMPU\_PL. There is no need to differentiate between masters in this configuration.

**TIP:** If the run-time configuration access is not needed for system operation, the example in the previous figure could have alternatively been implemented with the AXI MMU IP which also provides address decoding, read and write access control, and is only statically configured.

## **Isolation Example Design**

## **System Isolation**

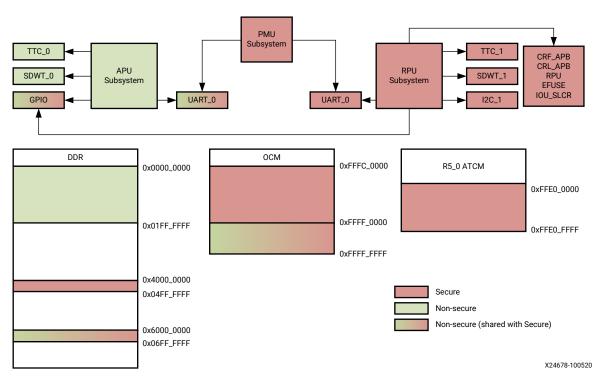

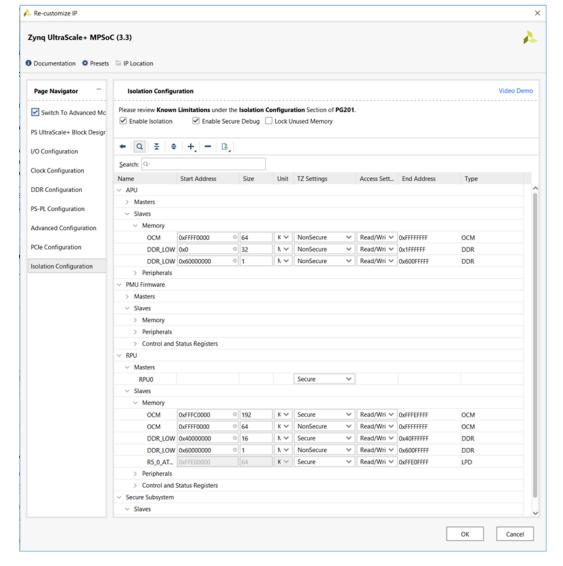

The isolation reference design created in *Isolation Methods in Zynq UltraScale+ MPSoCs* (XAPP1320) is the starting point for building the PL isolation example design. The TrustZone (TZ) settings for the Processing System (PS) are shown in the following figure.

Figure 14: Isolation Reference Design TrustZone Settings

The system contains three active PS masters. The PMU and RPU (r5\_0) are designated Secure, and the APU is designated Non-Secure. All three masters execute as bare metal standalone OS.

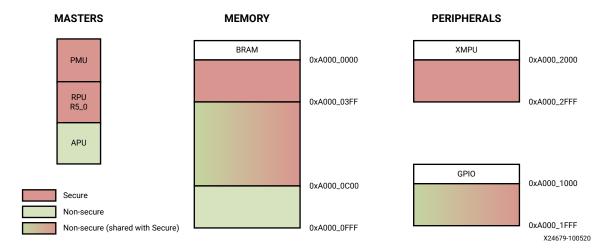

The PL isolation example design adds the PL memory and peripheral elements shown in the following figure.

Figure 15: PL Isolation Security Settings

## **Secure PL Memory**

The first KB of the PL BRAM will be designated as secure, which means that it must only be accessible by the secure masters, PMU and RPU ( $R5_0$ ).

## **Secure PL Peripherals**

The S\_AXI\_XMPU configuration port of the XMPU\_PL will be designated as secure, which means that it will only be accessible by the Secure masters, PMU and RPU ( $R5_0$ ). If you use the LOCK registers in the XMPU, the configuration port becomes writable to only the designated masters, but still is readable by other masters.

## Non Secure PL Memory

PL BRAM's last KB is designated as non-secure and is accessible only by the APU. Configure the associated XMPU region as non-secure with Strict Check Type. The APU has to set the AXI protection security level to non-secure (AxProt[1]=1) to access the region. Since bare metal standalone applications are being run in this example, all transactions originating from the APU enters the PL as secure (AxProt[1]=0). Therefore, to isolate the region to the APU, the region is configured as secure, but only the APU is authorized to access it.

## **Non-Secure Shared Memory & Peripherals**

The middle two KBs of the PL BRAM and the AXI GPIO are designated as non-secure shared. They must be accessible by both secure and non-secure masters. One way to accomplish this is to designate regions to cover their respective address ranges and list all the masters as authorized. Alternatively, omit defining a region and instead utilize the default CTRL register settings to allow read and write access to undefined ranges.

The following table shows the XMPU\_PL configuration for the example design. The MACRO definitions can be found in the zupl\_xmpu BSP SW driver ( $zupl_xmpu_hw.h$ ).

**Table 19: XMPU PL Region Definitions**

| CONTROL     | MACROS                    | Description              |

|-------------|---------------------------|--------------------------|

| CTRL        | XMPU_PL_CTRL_DEFRD +      | Default Read             |

|             | XMPU_PL_CTRL_DEFWR +      | Default Write            |

|             | XMPU_PL_CTRL_PSNATTREN +  | Poison by Attribute      |

|             | XMPU_PL_CTRL_PSNADDREN +  | Poison by Address        |

|             | XMPU_PL_CTRL_ARSP_DEC     | Poison Response DECERR   |

| LOCK        | 1                         | enable                   |

| LOCK_BYPASS | XMPU_PL_MID_RPU0 +        | RPU0                     |

|             | XMPU_PL_MID_PMU           | PMU                      |

|             | REGION 0                  |                          |

| R00_START   | BRAM BASEADDR             | BRAM Base Address        |

| R00_END     | BRAM BASEADDR + 0x03FF    | Size 1KB                 |

| R00_MASTERS | XMPU_PL_MID_RPU0 +        | RPU0                     |

|             | XMPU_PL_MID_PMU           | PMU                      |

| R00_CONFIG  | XMPU_PL_REGION_WR_ALLOW + | Region Write Allow       |

|             | XMPU_PL_REGION_RD_ALLOW + | Region Read Allow        |

|             | XMPU_PL_REGION_ENABLE     | Region Enable            |

|             | REGION 1                  |                          |

| R01_START   | BRAM BASEADDR + 0x0C00    | BRAM Base Address + 3 KB |

| R01_END     | BRAM BASEADDR + 0x0FFF    | Size 1 KB                |

| R01_MASTERS | XMPU_PL_MID_APU0          | APU                      |

| R01_CONFIG  | XMPU_PL_REGION_WR_ALLOW + | Region Write Allow       |

|             | XMPU_PL_REGION_RD_ALLOW + | Region Read Allow        |

|             | XMPU_PL_REGION_ENABLE     | Region Enable            |

## **Reference Design**

Download the reference design files for this application note from the Xilinx website.

#### **Reference Design Matrix**

The following checklist indicates the procedures used for the provided reference design.

*Table 20:* **Reference Design Matrix**

| Parameter                                                                                                            | Description                                             |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|

| General                                                                                                              |                                                         |  |  |  |

| Developer name                                                                                                       | Carl Carmichael                                         |  |  |  |

| Target devices                                                                                                       | Zynq UltraScale+ Devices                                |  |  |  |

| Source code provided?                                                                                                | Yes                                                     |  |  |  |

| Source code format (if provided)                                                                                     | C, VHDL                                                 |  |  |  |

| Design uses code or IP from existing reference design, application note, 3rd party or Vivado software? If yes, list. | Isolation Methods in Zynq UltraScale+ MPSoCs (XAPP1320) |  |  |  |

| Simulation                                                                                                           |                                                         |  |  |  |

| Functional simulation performed                                                                                      | Yes                                                     |  |  |  |

| Timing simulation performed?                                                                                         | No                                                      |  |  |  |

Table 20: Reference Design Matrix (cont'd)

| Parameter                                                 | Description             |  |  |  |

|-----------------------------------------------------------|-------------------------|--|--|--|

| Test bench provided for functional and timing simulation? | No                      |  |  |  |

| Test bench format                                         | No                      |  |  |  |

| Simulator software and version                            | Yes                     |  |  |  |

| SPICE/IBIS simulations                                    | N/A                     |  |  |  |

| Implementation                                            |                         |  |  |  |

| Synthesis software tools/versions used                    | N/A                     |  |  |  |

| Implementation software tool(s) and version               | N/A                     |  |  |  |

| Static timing analysis performed?                         | Yes                     |  |  |  |

| Hardware Verification                                     |                         |  |  |  |

| Hardware verified?                                        | Yes                     |  |  |  |

| Platform used for verification                            | ZCU102 Evaluation Board |  |  |  |

## **Reference Design Zip File**

The xapp1353-pl-isolation.zip file (download from Xilinx website) contains a Vivado packaged IP with example design support files. A description of the zip archive is provided in the following table.

**Table 21:** Contents of Reference Design Archive

| Directory/File Name                                                                                                       | Description                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ./XmpuPL_ZUplus_v1.0a/zupl_xmpu_v1_0                                                                                      | IP Repository Package                                                                                                                                                                                                                                                                                                           |

| ./XmpuPL_ZUplus_v1.0a/zupl_xmpu_v1_0/ component.xml                                                                       | This IP-XACT file defines the contents of the IP to Vivado.                                                                                                                                                                                                                                                                     |

| ./XmpuPL_ZUplus_v1.0a/zupl_xmpu_v1_0/bd/bd.tcl                                                                            | The Tcl script used by Vivado IP Integrator supports integration of the IP in the Block Design.                                                                                                                                                                                                                                 |

| ./XmpuPL_ZUplus_v1.0a/zupl_xmpu_v1_0/drivers/ zupl_xmpu_v1_0                                                              | This is the directory of the low-level software drivers for the zupl_xmpu PL peripheral. When the Vivado project's hardware is exported to SDK/Vitis, these drivers are included in the export, and will be included in any board support package (BSP) created within the SDK/Vitis workspace that uses the exported hardware. |

| ./XmpuPL_ZUplus_v1.0a/zupl_xmpu_v1_0/<br>example_designs/xapp1320_isolation                                               | This directory contains files to build the isolation example reference design from <i>Isolation Methods in Zynq UltraScale+MPSoCs</i> (XAPP1320).                                                                                                                                                                               |

| ./XmpuPL_ZUplus_v1.0a/zupl_xmpu_v1_0/<br>example_designs/xcu102_example                                                   | This directory contains files to build the PL isolation example reference design.                                                                                                                                                                                                                                               |

| ./XmpuPL_ZUplus_v1.0a/zupl_xmpu_v1_0/gui/ zupl_xmpu_v1_0.gtc./XmpuPL_ZUplus_v1.0a/ zupl_xmpu_v1_0/xgui/zupl_xmpu_v1_0.tcl | The Tcl script used by Vivado IP Integrator creates the configuration GUI for the PL instance IP.                                                                                                                                                                                                                               |

| ./XmpuPL_ZUplus_v1.0a/zupl_xmpu_v1_0/hdl                                                                                  | Reference core (vhdl) source files                                                                                                                                                                                                                                                                                              |

## **Build HW Design in Vivado**

Once you have obtained and extracted the design files for this tutorial, you have the option to either manually add the  $\mathtt{zupl\_xmpu}$  reference core to the isolation reference design, or use an automated script to build the completed HW platform.

If you wish to make the modifications manually, proceed to Start with the XAPP1320 Isolation Reference Design . If you wish to build the HW platform with an automated script, proceed to Build with the Automated Design Script section.

### Start with the XAPP1320 Isolation Reference Design

#### **Isolation Reference Design**

The next section provides a step-by-step instruction to manually add the <code>zupl\_xmpu</code> reference core to isolation reference design. Reconstruct the reference design from *Isolation Methods in Zyng UltraScale+ MPSoCs* (XAPP1320).

An automated script is provided to build the design. If you wish to review the procedures for creating an isolated design, refer to *Isolation Methods in Zynq UltraScale+ MPSoCs* (XAPP1320).

Following are the steps to build the isolation reference design:

- 1. Unzip the zupl\_xmpu archive: zupl\_xmpu\_v1\_0[revision].zip.

- 2. a. If running on Linux: Browse to the ./zupl\_xmpu\_v1\_0/example\_designs/xapp1320\_isolation directory and run Vivado.

- b. If running Vivado on Windows, use the Tcl Console to navigate to the zupl\_xmpu\_v1\_0/example\_designs/xapp1320\_isolation directory:

```

cd{<your_path>/XmpuPL_ZUplus_v1.0[revision]/zupl_xmpu_v1_0/

example_designs/xapp1320_isolation}

```

3. Run the example\_design.tcl script:

```

source ./example_design.tcl

```

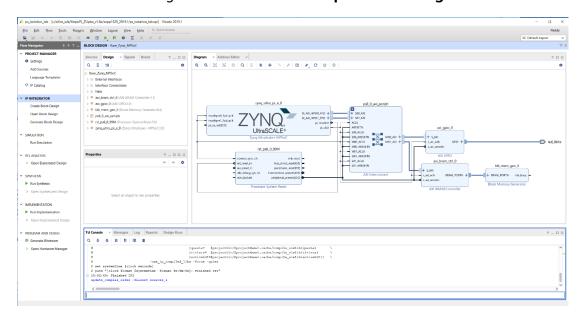

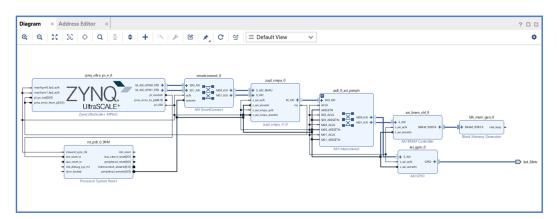

When the IP Integrator Block Design is complete, it looks like the following figure.

Figure 16: Isolation Example Block Design

4. Right-click zynq\_ultra\_ps\_e\_0 and select Customize Block....

| Application | District | Distri

Figure 17: Customize Zynq\_Ultra\_PS

5. Click **Switch to Advanced Mode**, then click **Isolation Configuration**, and you can see that the isolation parameters as described in *Isolation Methods in Zynq UltraScale+ MPSoCs* (XAPP1320) have been implemented. The following figure shows a sample of the settings.

Figure 18: Isolation Configuration Parameters

- a. Click Cancel to close the customization window.

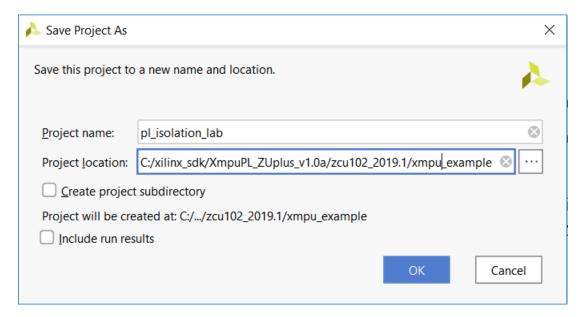

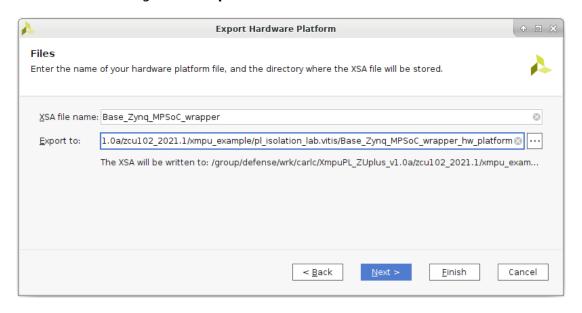

- 6. Save the project to a new name before making modifications.

- a. File-> Project->Save As

- b. Fill in the required information as shown in the following figure:

- i. Project name: pl\_isolation\_lab

- ii. Project Location: <your\_path>/XmpuPL\_ZUplus\_v1.0a/zcu102\_<version>/

xmpu\_example

Figure 19: Save Project As

iii. Do not create project sub directory. Do not include run results. Click **OK**.

## Manual Insertion of the XMPU\_PL in the IP Integrator

#### Manual Insertion in the IP Integrator

Isolation reference design gets created in the previous section, Start with the XAPP1320 Isolation Reference Design, and is saved to the following location:

```

/XmpuPL_ZUplus_v1.0a/xcu102_<version>/xmpu_example/pl_isolation_lab.xpr

```

Open the project in Vivado, and click Open Block Design if you have it closed.

You will go through the following steps to add a XMPU\_PL module to the block design.

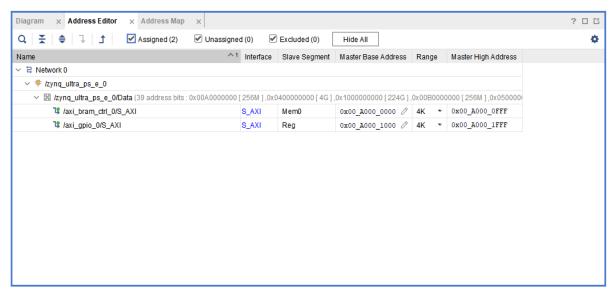

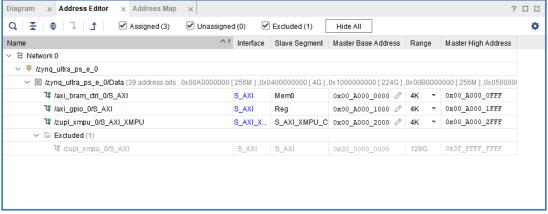

- 1. Click the **Address Editor** and note the current mappings in the following pane.

- a. axi\_bram\_ctrl\_0 is mapped to 0x00\_A000\_0000 (4K) and axi\_gpio\_0 is mapped to 0x00\_A000\_1000 (4K) in the Address Editor window. Return to the diagram.

#### Figure 20: Address Editor

X26559-041822

- 2. Add the zupl\_xmpu\_vl\_0 core to your repository.

- a. Click Settings beneath Project Manager. This is located in the Flow Manager.

- b. Under Project Settings, expand > IP, and click **Repository**.

- c. Click the + symbol in the IP Repositories.

- d. Browse to the zup1\_xmpu\_v1\_0 directory and click Select.

- e. One (1) repositiory must be added to the project. Click **OK** to clear the **Add Repository** window.

- f. Click **OK** to clear the **Settings** window.

- 3. Add the <code>zupl\_xmpu\_vl\_0</code> core to the block design.

- a. Click the + symbol in the Block Diagram window.

- b. Type <code>zupl</code> in the Search field type and double-click <code>zupl\_xmpu\_vl\_0</code> or press enter.

- 4. Add a SmartConnect IP core.

- a. Click the + symbol in the Block Diagram window.

- b. Type smart in the search field type.

- c. Double-click **AXI SmartConnect** or just press **enter**.

- d. Right-click the smartconnect\_0 instance and select **Customize Block**.

- e. Change the Number of Master Interfaces to 2 and click OK.

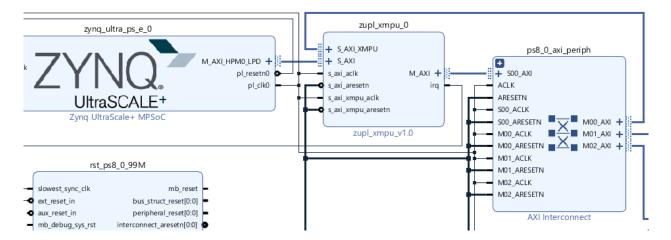

- 5. **Disconnect** the AXI Interconnect block from the Zyngzyng PS block.

- a. Select and delete the bus signals between zynq\_ultra\_ps\_e\_0 and ps8\_0\_axi\_periph.

- b. Right-click ps8\_0\_axi\_periph and Customize Block.

- c. Reduce the Number of Slave Interfaces to 1. Click OK.

- 6. Connect the Zyng PS M\_AXI\_ ports.

- a. Connect zynq\_ultra\_ps\_e\_0/M\_AXI\_HPM0\_FPD to smartconnect\_0/S00\_AXI.

- b. Connect zynq\_ultra\_ps\_e\_0/M\_AXI\_HPM1\_FPD to smartconnect\_0/S01\_AXI.

- 7. Connect the XMPU AXI ports.

- a. Connect zupl\_xmpu\_0/S\_AXI\_XMPU to smartconnect\_0/M00\_AXI.

- b. Connect zupl\_xmpu\_0/S\_AXI to smartconnect\_0/M01\_AXI.

- c. Connect zupl\_xmpu\_0/M\_AXI to ps8\_0\_axi\_periph/S00\_AXI.

- d. Regenerate Layout. Click OK.

- 8. Connect the AXI clock and reset ports.

- a. Click Run Connection Automation.

- b. Select All Automation. Click the Regenerate button.

- C

- c. Manually connect any unconnected aclk or aresetn ports.

- 9. Connect the IRQ signal.

- a. This example design demonstrates the usage of PMU and RPU to receive interrupts from the XMPU so the <code>pmu\_error\_from\_pl</code> port needs to be enabled. Right-click <code>zynq\_ultra\_ps\_e\_0</code> and select **Customize Block**.

- b. Click PS-PL Configuration. Expand > General. Expand > Others.

- c. Select the check box for Errors to and from PMU. Click OK.

- d. Connect zupl\_xmpu\_0/irq port to both pl\_ps\_irq0[0:0] and pmu\_error\_from\_pl[3:0] ports on zynq\_ultra\_ps\_e\_0.

- e. Regenerate Layout. The diagram resembles the following.

Figure 21: xmpu pl Example Block Diagram

- 10. Map the Address segments.

- a. Click Address Editor.

- b. Assign addresses:

- Expand > Network 0 > zynq\_ultra\_ps\_e\_0 > Data > Unassigned (4).

- ii. Right-click zupl\_xmpu\_0: S\_AXI\_XMPU (S\_AXI\_XMPU\_Config) and select

Assign.

Note: If two entries are shown, select either one.

- iii. Change the range of S\_AXI\_XMPU to 4K.

- iv. Change the Master Base Address of S\_AXI\_XMPU to 0x00\_A000\_2000.

- v. Select File > Save Block Design.

- vi. Select Tools > Validate Design.

Note: If asked to assign unmapped slaves, select No.

- vii. Ignore warnings about unmapped slaves. Click **OK**.

- viii. Right-click **Uassigned Slaves/zupl\_xmpu\_0**: **S\_AXI** (**S\_AXI**) and select **Exclude**.

- ix. The final configuration is shown in the following diagram.

Figure 22: xmpu\_pl Example Address Map

X26560-041822

x. Select File > Save Block Design.

**Note:** The  $\mathtt{zupl\_xmpu\_0/S\_AXI}$  is excluded due to the AXI Bridge in the core. Downstream slaves are mapped directly to upstream masters.

- 11. Customize the zupl\_xmpu\_0 block.

- a. Return to the block diagram and right-click <code>zupl\_xmpu\_0</code> and select Customize Block.

- b. Select **AXI Settings**.

- c. The C\_S\_AXI\_ DATA\_WIDTH is set to the default value of 32. Leave it at default setting. The AXI infrastructure blocks adjusts for the PS M\_AXI\_ bus widths.

- d. The M\_AXI\_BASEADDR and M\_AXI\_HIGHADDR will not have any functional effect. However they are provided as a means to communicate to the SW Driver the address range that the XMPU monitors. These values will be exported to the xparameters.h file and be included in the peripheral's instance configuration data.

- e. (Optional) Set these values to correspond with the address ranges shown in the previous figure.

- i. HIGHADDR:0xA0001FFFii. BASEADDR:0xA000000

- **(**

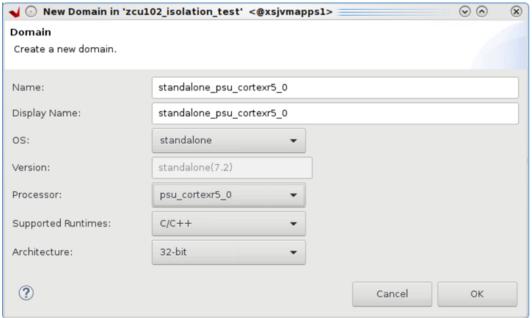

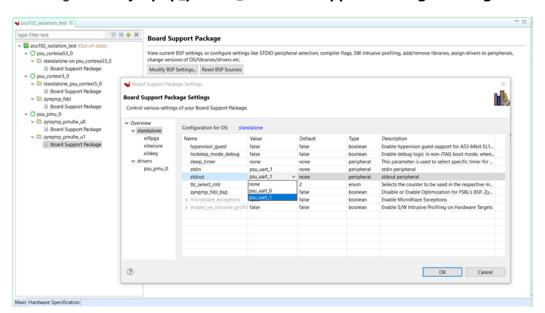

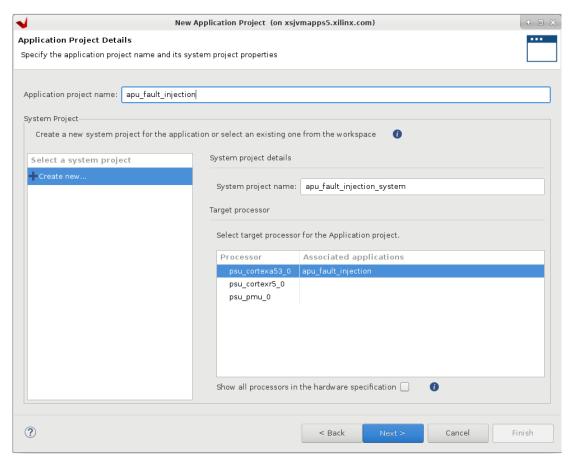

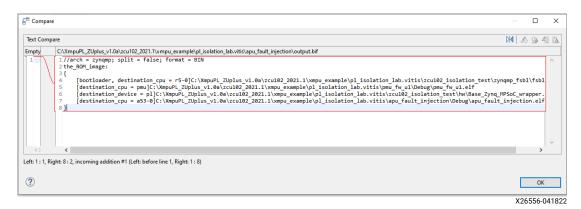

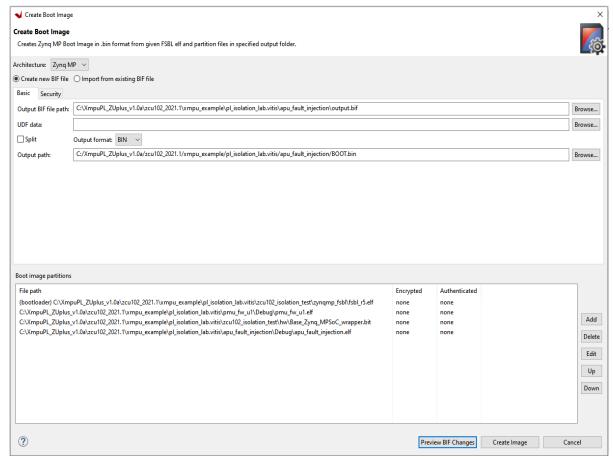

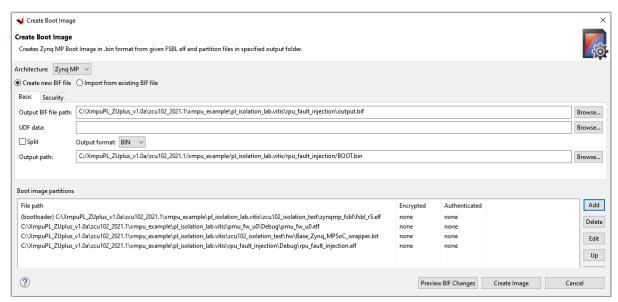

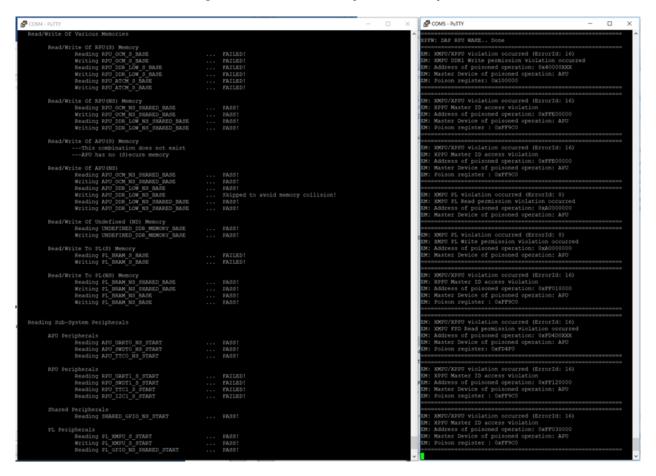

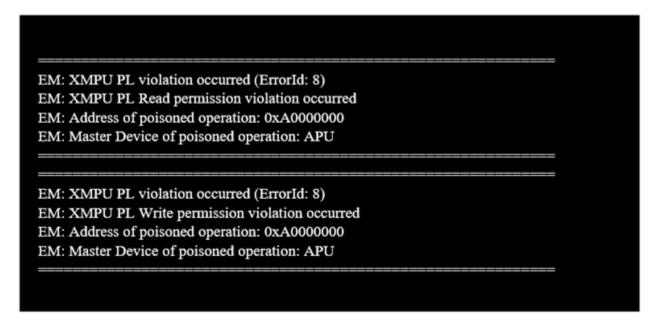

**TIP:** Use the upper 32 bits to specify a 40 bit address..