# 7 Series Isolation Design Flow Lab Using ISE Design Suite 14.4

XAPP1085 (v1.0.2) July 31, 2013

#### Notice of Disclaimer

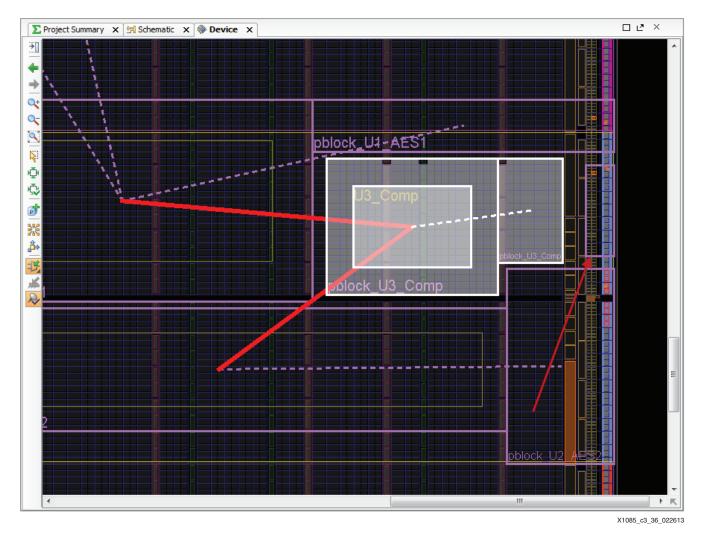

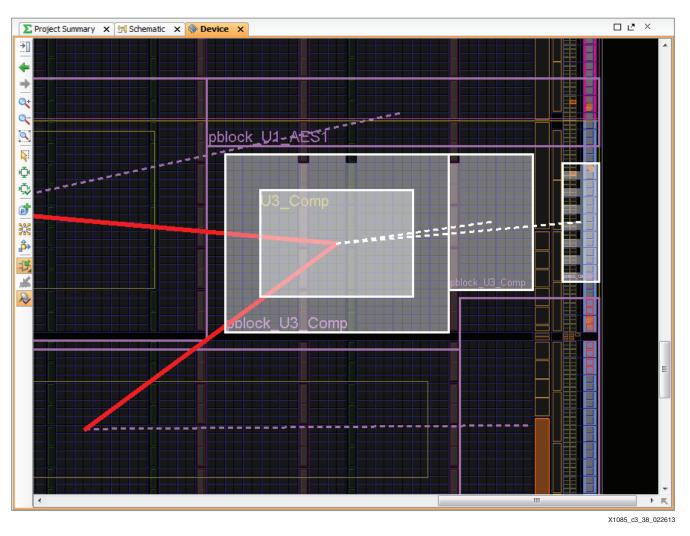

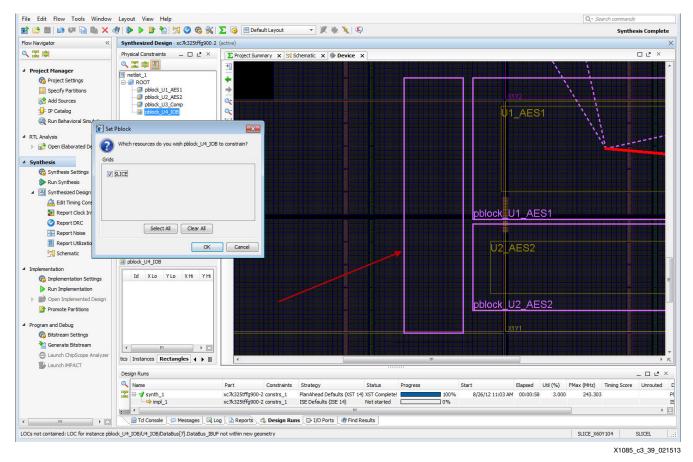

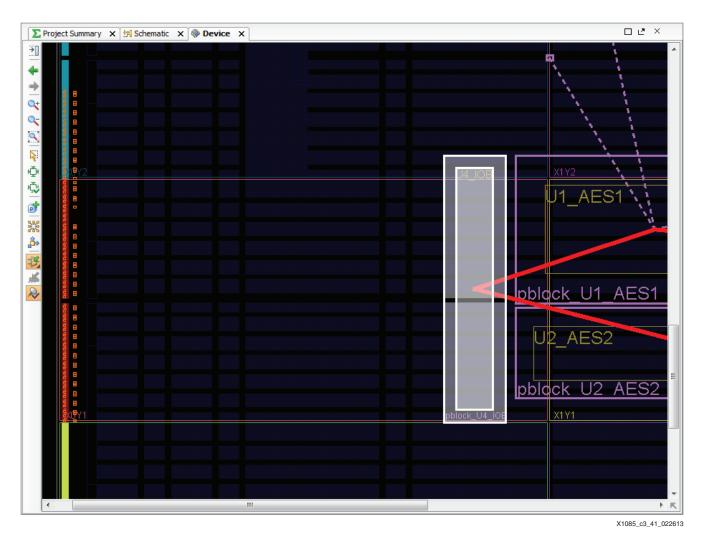

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: <a href="http://www.xilinx.com/warranty.htm#critapps">http://www.xilinx.com/warranty.htm#critapps</a>.

© Copyright 2013 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

## **Revision History**

| Date       | Version | Revision                                                                                                                                       |

|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 02/27/2013 | 1.0     | Initial Xilinx release.                                                                                                                        |

| 06/20/2013 | 1.0.1   | Replaced SCC lounge with IDF page throughout. Added URL to download reference design in Reference Design Files.                                |

| 07/31/2013 | 1.0.2   | Replaced SCC lounge with IDF page in Lab Design Overview and Further Resources.<br>Replaced Secure Solutions site with IDF page in References. |

The following table shows the revision history for this document.

# Table of Contents

| <b>Revision History</b>                                      |

|--------------------------------------------------------------|

| Chapter 1: Isolated Design Flow Overview                     |

| Isolation Design Flow Overview                               |

| Single Chip Crypto                                           |

| Lab Design Overview                                          |

| Reference Design Files                                       |

| Installing Reference Design Files into Target Directories    |

| Chapter 2: Synthesizing Design with PlanAhead Tool           |

| Lab Design Source VHDL Files                                 |

| Entering Project in PlanAhead Tool                           |

| Defining ISO Partitions                                      |

| Synthesizing the Design 21                                   |

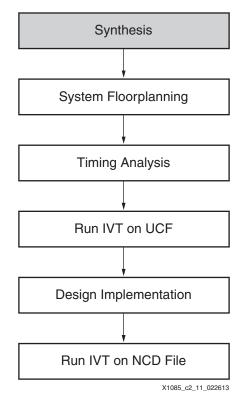

| Isolation Design Flow Progress – Synthesis Block             |

| Chapter 3: Floorplanning the System                          |

| Placing I/Os and Clocking Resources 27                       |

| Defining Attributes for ISO Partition 34                     |

| Setting Up Timing Constraints 39                             |

| Setting Up Area Groups for ISO Regions 42                    |

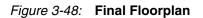

| Isolation Design Flow Progress – System Floorplanning Block  |

| Running Report Timing 78                                     |

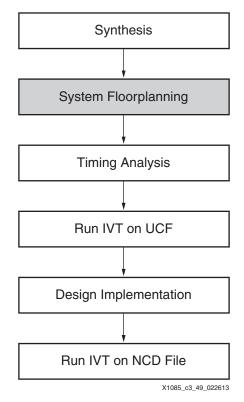

| Isolation Design Flow Progress 79                            |

| Exporting the Design                                         |

| Chapter 4: Running Isolation Verification Tool Against UCF   |

| Creating the Pin Isolation Group File 81                     |

| Creating the File Used to Run the IVT UCF Test               |

| Running the IVT UCF Test 83                                  |

| Examining the Output from the IVT UCF Test                   |

| Isolation Design Flow Progress – Run IVT on UCF Block        |

| Chapter 5: Implementing Design with PlanAhead Tool           |

| Generating and Running an Implementation87                   |

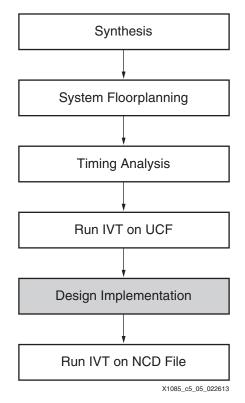

| Isolation Design Flow Progress – Design Implementation Block |

|                                                              |

|                                                              |

|                                                              |

| Chapter 6: | Verifying Design with NCD Isolation Verification Tool |   |

|------------|-------------------------------------------------------|---|

| Creating   | g File to Run IVT NCD Test                            | 3 |

| Running    | g IVT NCD Test                                        | 1 |

| Examini    | ng Output from IVT NCD Test                           | 4 |

## Appendix A: Additional Resources

| Xilinx Resources 1     | 01  |

|------------------------|-----|

| Solution Centers 1     | 01  |

| References 1           | .01 |

| Further Resources    1 | .01 |

## Chapter 1

## Isolated Design Flow Overview

## **Isolation Design Flow Overview**

The Isolation Design Flow (IDF) is the software methodology that allows Single Chip Crypto (SCC) implementations, or any other application requiring module isolation. This methodology is backed by significant schematic analysis and software verification (Isolation Verification Tool) to ensure elimination of single points of failure. SCC is an application allowing the implementation of a multi-chip crypto system in a single FPGA.

## Single Chip Crypto

This chapter describes how an SCC system is created using a Kintex<sup>TM</sup>-7 FPGA, ISE® Design Suite 14.4, and PlanAhead<sup>TM</sup> 14.4 development tools.

SCC systems are implemented using the isolation design flow (IDF). The IDF permits SCC applications that include redundant type 1 encryptors, resident red and black data, and functions that operate on multiple levels of security within the same Xilinx FPGA.

At the core of the IDF is physical and electrical isolation of chosen logic from other areas of the design. This is accomplished using:

- Conventional, best practices, modular Xilinx design entry where each function isolated by the designer must be at its own level of hierarchy

- Modular synthesis of each isolated region of the design

- (Mandatory) manual floorplanning to isolate the desired regions of the design on the FPGA while providing user-specified intra-region communication through the use of trusted routing

- Automated verification of isolation using the Xilinx Isolation Verification Tool (IVT) software

### Lab Design Overview

The Kintex-7 FPGA IDF rules are outlined in the *Developing Secure and Reliable Single FPGA Designs with Xilinx 7 Series FPGAs Using the Isolation Design Flow* (XAPP1086). This companion application note describes how functions are isolated; specific differences between a normal partition flow and an IDF partition flow; IDF-specific HDL code mnemonics; and trusted routing rules. This application note is accessible from the Isolation Design Flow page on Xilinx.com [Ref 1].

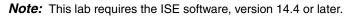

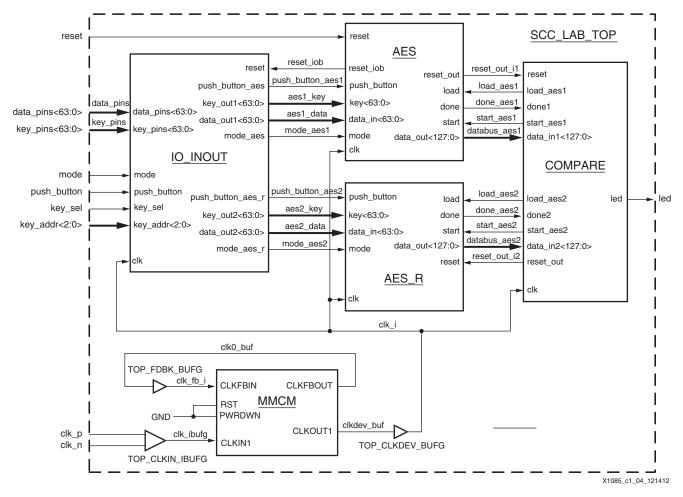

To illustrate the IDF and its capabilities, this design implements isolated, redundant advanced encryption standard (AES) modules in a single 7 series FPGA, targeting a Kintex-7 device. Figure 1-1 is a hierarchical diagram of the various VHDL sub-blocks used in the implementation of the design. Type 1 crypto applications using 7 series FPGAs require defense-grade (XQ) devices for mask control. The design example used in this application note was created using a non-defense grade Kintex-7 XC7K325T-2FFG900 device.

Figure 1-1: VHDL Design Hierarchical Block Diagram

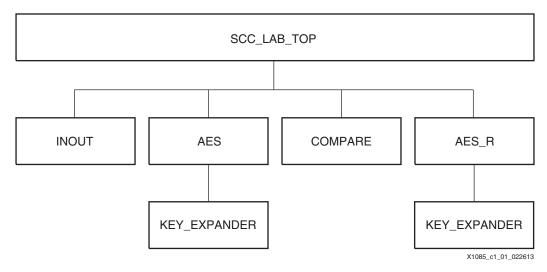

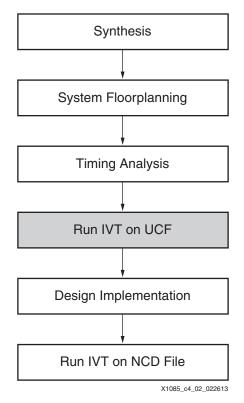

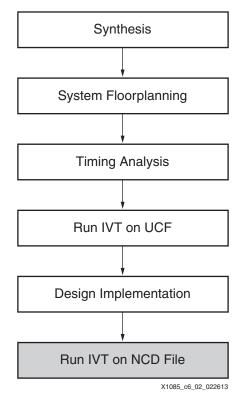

Figure 1-2 shows the IDF that is used for the single-chip crypto lab.

Figure 1-2: IDF System Design Flow

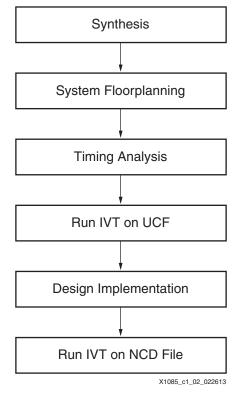

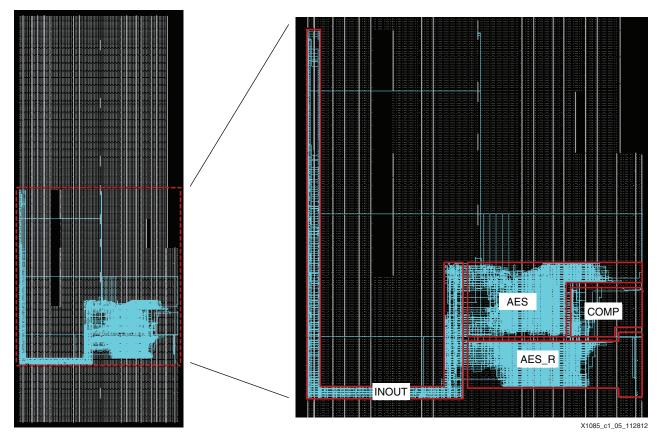

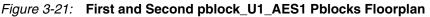

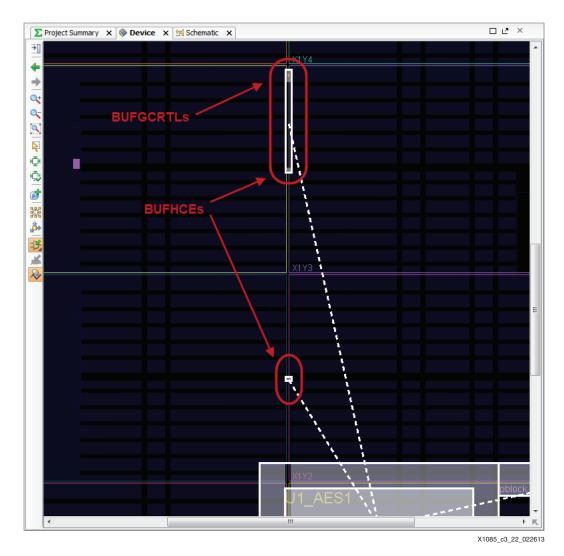

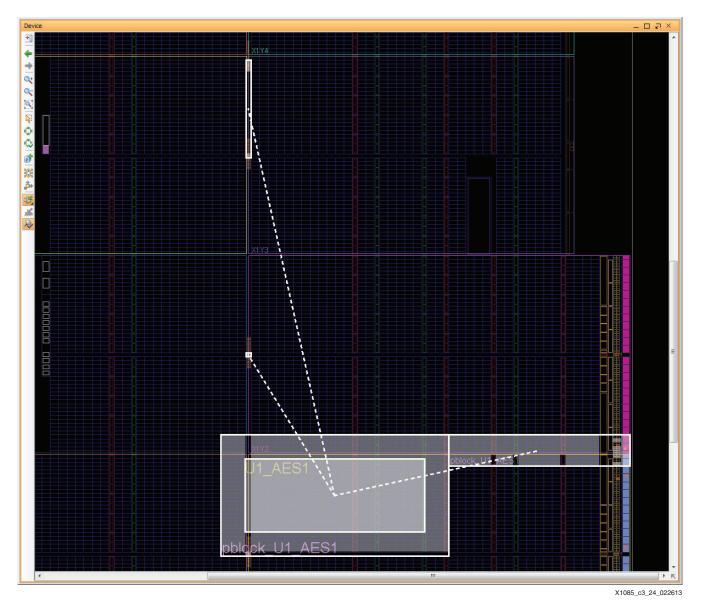

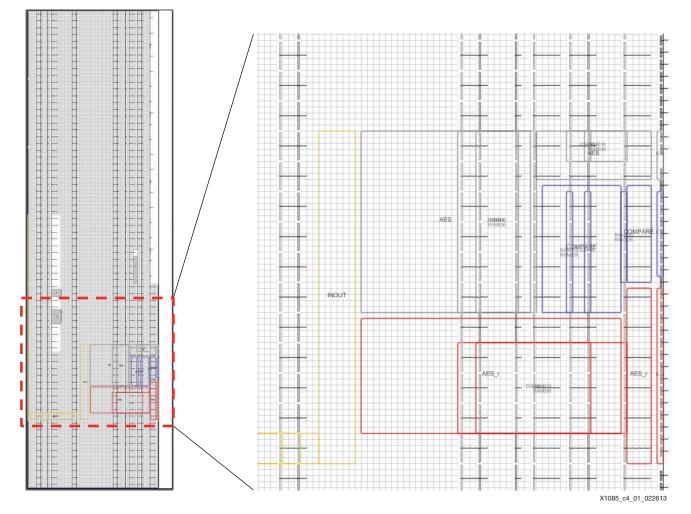

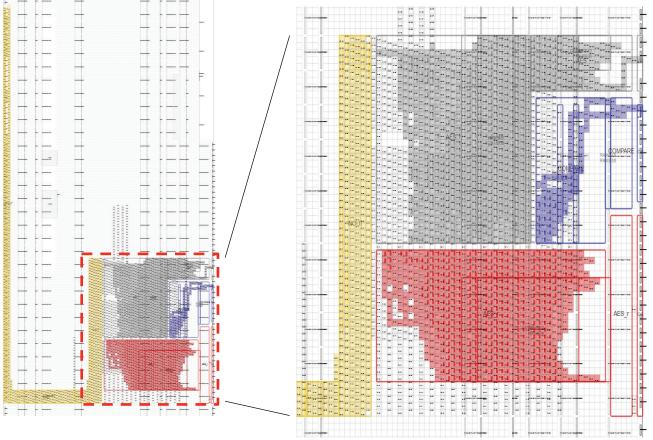

Figure 1-3 shows the partitioning and I/O mapping for the SCC lab design as implemented in an XC7K325T-2FFG900 device. The relative placement of the I/O pins is shown along the left and right sides of the device. All of the global clocking resources must physically reside in one of the isolated regions for them to be routed (as a condition of the isolated rules). The BUFGs and BUFHCEs are shown in the diagram as part of the AES partition.

Kintex-7 SCC Lab Floorplan

X1085\_c1\_03\_021213

*Figure 1-3:* Die View: Partitions and I/O Map in XC7K325T-2FFG900 Device

www.xilinx.com

Figure 1-4 is a detailed block diagram of the SCC lab design showing all of the isolated functions (modules), the I/O pins, and the internal signals connecting the isolated functions.

Figure 1-4: Detailed Block Diagram of SCC Lab Modules

The design incorporates two AES algorithm blocks: AES and AES\_R. Both of the AES blocks are driven by the same input data and key. The AES blocks are tied to the COMPARE block, which compares the outputs of the AES blocks. If the outputs of the AES blocks do not match, the COMPARE block sends an alert to the user indicated by an LED. Both AES blocks have an input that allows the user to inject an error. However, only the AES block has the error injection input tied to an external pushbutton. The fourth block shown is an I/O distribution module. It contains I/O and LUT buffers used for splitting the pin data to the redundant AES modules. A 64-bit data input bus and a 64-bit key input bus drive the AES blocks. The push\_button pin, and the data and key input buses can be driven externally or left open because they have internal pull-downs in the INOUT HDL code. The mode pin has an internal pull-up. The key input to the encryption blocks can be selected from the key input external pins or from an internal ROM with eight sample 64-bit keys. This lab design gives an example of how a key might be stored internal to the FPGA in a ROM, potentially making a more secure design.

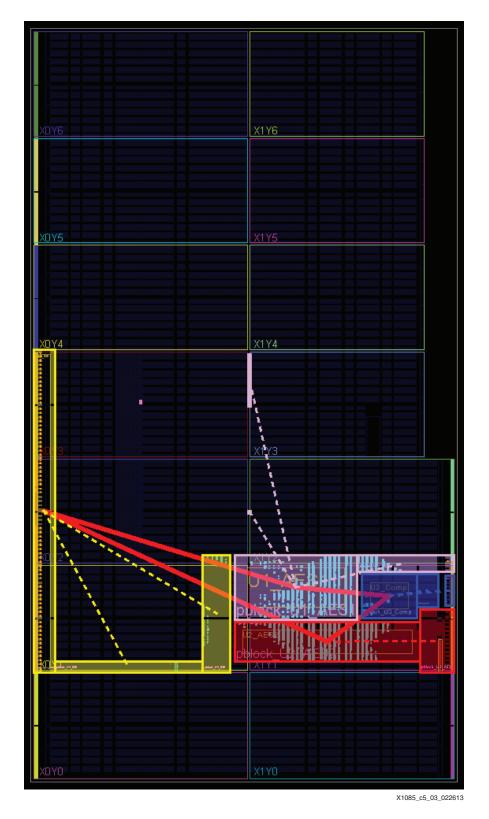

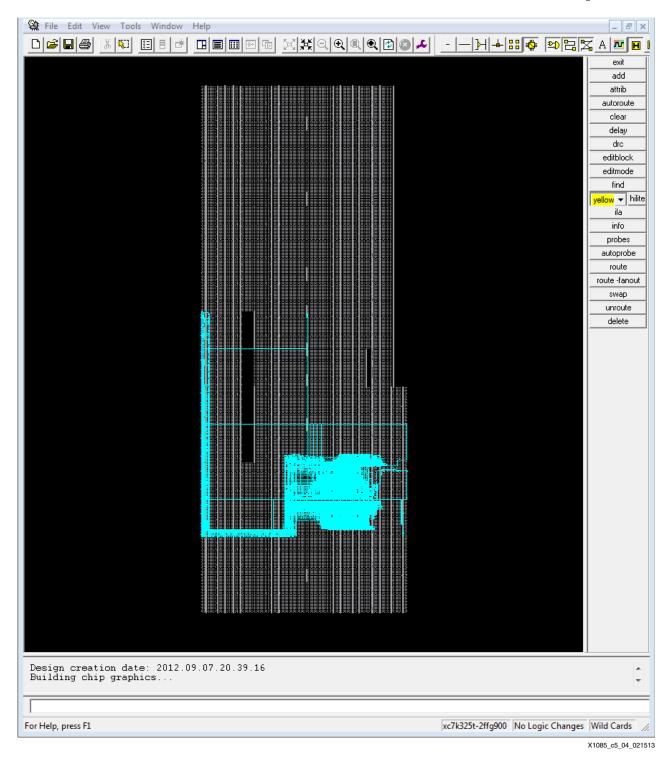

*Figure 1-5:* **FPGA Editor View: Implementation of Single-Chip Crypto Lab Design**

## **Reference Design Files**

## **Reference Design Checklist**

The design files for this application note can be downloaded from:

https://secure.xilinx.com/webreg/clickthrough.do?cid=343444

The design checklist in Table 1-1 lists simulation, implementation, and hardware details for the reference design.

| Parameter            | Description            |

|----------------------|------------------------|

| General              |                        |

| Developer Name       | Xilinx                 |

| Target devices       | Kintex-7 XC7K325T FPGA |

| Source code provided | Υ                      |

| Parameter                                                                                                                                 | Description           |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Source code format                                                                                                                        | VHDL                  |

| Design uses code/IP from existing Xilinx application note/<br>reference designs, CORE Generator <sup>TM</sup> software, or third<br>party | N                     |

| Simulation                                                                                                                                |                       |

| Functional simulation performed                                                                                                           | Υ                     |

| Timing simulation performed                                                                                                               | Y                     |

| Testbench used for functional and timing simulations                                                                                      | Y                     |

| Testbench format                                                                                                                          | VHDL                  |

| Simulator software/version used                                                                                                           | ISE Design Suite 14.4 |

| SPICE/IBIS simulations                                                                                                                    | N                     |

| Implementation                                                                                                                            |                       |

| Synthesis software tools/version used                                                                                                     | XST                   |

| Implementation software tools/versions used                                                                                               | ISE Design Suite 14.4 |

| Static timing analysis performed                                                                                                          | Y                     |

| Hardware Verification                                                                                                                     |                       |

| Hardware verified                                                                                                                         | N                     |

| Hardware platform used for verification                                                                                                   | N/A                   |

| Table 1-1: | Reference Design Ch | necklist (Cont'd) |

|------------|---------------------|-------------------|

|------------|---------------------|-------------------|

Table 1-2 shows the reference design utilization information for the targeted device.

#### Table 1-2: Device Utilization Table

| Device   | Speed<br>Grade | Package | Pre-Map    | Post-Route | Slices    |

|----------|----------------|---------|------------|------------|-----------|

| XC7K325T | -2             | FFG900  | 243.30 MHz | 78.46 MHz  | 5861 (2%) |

## Installing Reference Design Files into Target Directories

These steps describe the process for installing the reference design files:

*Note:* It is best if the design files are unzipped into a directory without any spaces in the path.

- 1. Copy xapp1085.zip to the Windows desktop.

- 2. Double-click **xapp1085.zip** and unzip the contents to the selected location.

- 3. The project files are placed in these directories:

\Xilinx\_Design\buildscripts

```

\Xilinx_Design\ivt

```

```

\Xilinx_Design\results\

```

```

\Xilinx_Design\source\

```

**Note:** When the zip file is extracted, the Xilinx\_Design directory is created, which contains the SCC lab project design files. The directory structure shown applies to this project.

www.xilinx.com

## Chapter 2

## Synthesizing Design with PlanAhead Tool

This chapter describes the steps in a bottom-up synthesis flow using the PlanAhead™ tool. The bottom-up synthesis flow is used for IDF designs to maintain isolation. The PlanAhead tool v14.4 allows the user to import RTL source code directly.

### Lab Design Source VHDL Files

The VHDL source files for the top-level and the individual isolated functions or modules are:

```

scc_lab_top.vhd

top_package.vhd

aes.vhd

aes_package.vhd

key_expander.vhd

aes_r.vhd

aes_package.vhd

key_expander.vhd

compare.vhd

io inout.vhd

```

In the flow in previous SCC/IDF application notes, each of the isolated functions are synthesized independently (out of context). The I/O buffers are inferred by default for each of the I/O pins in a module unless specifically inhibited via the buffer\_type is none attribute.

The PlanAhead tool, version 14.4 provides the option to use a hierarchical or in-context RTL source import flow. This flow is used in this application note so the I/O buffers are specifically instantiated as needed in each isolated function at the HDL level. The global clock input buffers are instantiated in the top-level block (scc\_lab\_top.vhdl).

The Add I/O Buffers (-iobuf) synthesis option enables or disables I/O buffer insertion. The option is left at the default (which is *Yes*), so that I/O buffers are automatically inserted during synthesis, provided they are not already instantiated in the isolated function. XST does not place two I/O buffers on an I/O pin.

This is an example snippet of the I/O block (IOB) instantiation VHDL code for an input and an output buffer:

```

-- Instantiate Input Buffer for PUSH_BUTTON

PushButton_IBUF : IBUF

port map(

0 => push_button_inbuf,

I => push_button

);

-- Instantiate Output Buffer for LED

Led_OBUF : OBUF

port map(

0 => led,

I => led_outbuf

);

```

For this design, all of the inputs are registered and are packed into the IOBs to improve input/output path timing. The Map option for packing I/O registers must be set as:

#### Set Pack internal flops/latches into IOBs (-pr) to Both (b).

The Pack I/O Registers Into IOBs (-iob) synthesis option is left at the default (which is *Auto*). The input and output registers are automatically packed in the IOBs during synthesis, depending on the optimization setting.

This is an example snippet of VHDL code for the input register instantiation in the INOUT isolated module:

```

-- Input Register Instantiations

process (clk)

begin

if rising_edge(clk)then

if reset = '1' then

data_inreg <= (others => '0');

key_inreg <= (others => '0');

mode_inreg <= '0';</pre>

push_button_inreg <= '0';</pre>

key_sel_inreg

<= '0';

key_addr_inreg

<= (others => '0');

else

data_inreg <= data_inbuf;

key_inreg <= key_inbuf;

mode_inreg <= mode_inbuf;</pre>

push_button_inreg <= push_button_inbuf;</pre>

key_sel_inreg <= key_sel_inbuf;

key_addr_inreg <= key_addr_inbuf;</pre>

end if;

end if;

end process;

```

## **Entering Project in PlanAhead Tool**

### Launching PlanAhead Tool

To launch the PlanAhead tool v14.4, select **Start > All Programs > Xilinx Design Tools > ISE Design Suite 14.4 > PlanAhead > PlanAhead**.

## **Creating Project**

The PlanAhead tool works with any standard RTL source file. The standard guidelines are followed to generate a new project and import the RTL source files into the PlanAhead tool to create a floorplan for the design.

1. Set up a new PlanAhead project. From the Getting Started menu, select **Create New Project** and click **Next** (Figure 2-1).

| 💽 New Project               |                                                                                        | 23       |

|-----------------------------|----------------------------------------------------------------------------------------|----------|

| Project Name<br>Enter a nam | e for your project and specify a directory where the project data files will be stored | <b>S</b> |

| Project name:               | FloorPlan_SCC                                                                          | 0        |

| Project location:           | C:/Xilinx_Design/planahead                                                             | 0        |

| 🔽 Create Proje              | ct Subdirectory                                                                        |          |

| Project will be cre         | eated at: C:/Xilinx_Design/planahead/FloorPlan_SCC                                     |          |

|                             |                                                                                        |          |

|                             |                                                                                        |          |

|                             |                                                                                        |          |

|                             |                                                                                        |          |

|                             |                                                                                        |          |

|                             |                                                                                        |          |

|                             |                                                                                        |          |

|                             |                                                                                        |          |

|                             |                                                                                        |          |

|                             | <back next=""> Finish</back>                                                           | Cancel   |

|                             |                                                                                        |          |

X1085\_c2\_01\_112812

Figure 2-1: New Project

- 2. Enter:

- Project name: FloorPlan\_SCC

- Project location: ../Xilinx\_Design/planahead

- Create Project Subdirectory: checked

- 3. Click Next.

- 4. Select **RTL Project** (Figure 2-2) to specify and add the RTL source files.

- 5. Click Next.

|   | ject Type<br>Specify the type of project to create.                                                                                     | a c    |

|---|-----------------------------------------------------------------------------------------------------------------------------------------|--------|

|   |                                                                                                                                         |        |

|   | RTL Project<br>You will be able to add sources, generate IP, run RTL analysis, synthesis, implementation, design planning and analysis. |        |

|   | Do not specify sources at this time                                                                                                     |        |

| D | Post-synthesis Project<br>You will be able to add sources, view device resources, run design analysis, planning and implementation.     |        |

|   | Do not specify sources at this time                                                                                                     |        |

|   | Enable Partial Reconfiguration                                                                                                          |        |

| 2 | I/O Planning Project                                                                                                                    |        |

|   | Do not specify design sources. You will be able to view part/package resources.                                                         |        |

| 5 | Import ISE Place & Route results                                                                                                        |        |

|   | You will be able to do post-implementation analysis of your design.                                                                     |        |

|   | Imported Project                                                                                                                        |        |

|   | Create a PlanAhead project from a Synplify, XST or ISE Project File.                                                                    |        |

|   |                                                                                                                                         |        |

|   |                                                                                                                                         |        |

|   |                                                                                                                                         |        |

|   |                                                                                                                                         |        |

|   |                                                                                                                                         |        |

|   |                                                                                                                                         |        |

|   | < Back Next > Finish                                                                                                                    | Cancel |

Figure 2-2: New Project (Project Type - RTL)

6. Import the RTL source files, directories, or both. In this case, all of the design HDL files are located in the directory ... \Xilinx\_Design\source\design. Click Add Directories, browse to the directory shown, and click Select as shown in Figure 2-3. The HDL source file directory is shown in the Name field.

| × |

|---|

|   |

| 5 |

|   |

| 4 |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

X1085\_c2\_03\_112812

Figure 2-3: New Project (Add Directories– Add Sources)

- 7. Do not copy sources into the project for this lab. Uncheck **Copy Sources into Project**. Check **Add Sources from Subdirectories**. For Target Language, select **VHDL**.

- 8. Click Next.

- 9. This lab does not add existing IP, so click Next again.

- 10. This lab creates the final UCF from the beginning. Because no UCF files need to be imported, click **Next** again.

- 11. Select the product, family, and sub-family for the default part (see Figure 2-4). For this lab, make these selections:

- Product: General Purpose

- Family: Kintex-7

- Sub-Family: Kintex-7

- Package: FFG900

- Speed Grade: -2

- Temperature Grade: **C**

| pecify     | Filter            |                   |                   |           |                  |        |                    |             |

|------------|-------------------|-------------------|-------------------|-----------|------------------|--------|--------------------|-------------|

|            |                   | y General Purpose | General Purpose 👻 |           |                  | FFG900 |                    |             |

| Boards     |                   | y Kintex-7        | Kintex-7 👻        |           |                  | -2     |                    |             |

|            | Sub-Famil         | y Kintex-7        |                   | -         |                  | C      |                    | -           |

|            |                   |                   |                   | Reset All | Filters          |        |                    |             |

|            |                   |                   |                   |           |                  |        |                    |             |

| arch: Q-   |                   |                   |                   |           |                  |        |                    |             |

| vice       | I/O Pir<br>Count  | Available<br>IOBs | LUT<br>Elements   | FlipFlop  | os Block<br>RAMs | DSPs   | Gb<br>Transceivers | PCI<br>Buse |

| xc7k325tff |                   | 500               | 203800            | 407600    |                  | 840    | 16                 | 1           |

| xc7k410tH  | <u> 900-2 900</u> | 500               | 254200            | 508400    | 795              | 1540   | 16                 | 1           |

|            |                   | à                 |                   |           |                  |        |                    | ,           |

Figure 2-4: New Project (Default Part)

- 12. Choose the **xc7k325tffg900-2** device.

- 13. Click **Next** and then click **Finish**.

www.xilinx.com

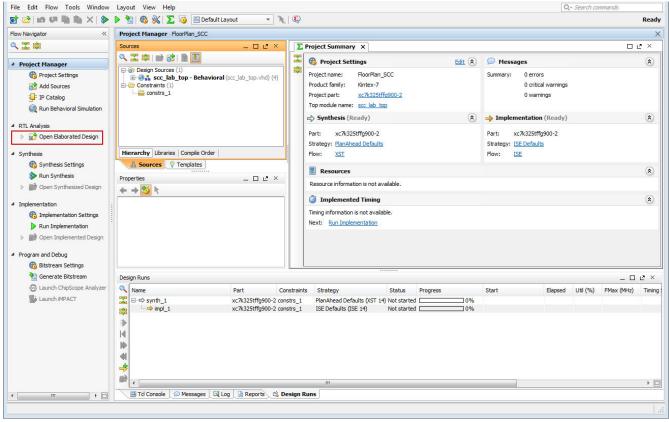

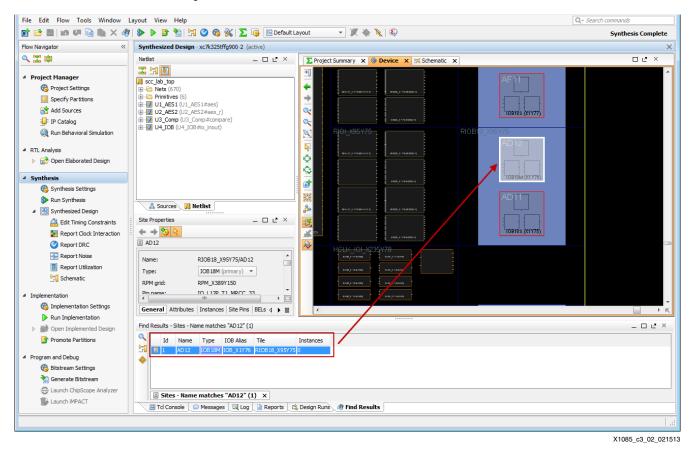

14. The PlanAhead tool project is created. Figure 2-5 shows the PlanAhead tool Project Manager window for the FloorPlan\_SCC project.

X1085\_c2\_05\_021513

Figure 2-5: PlanAhead Tool Project Manager (Open Elaborated Design)

### Building Netlists (Elaborated Design)

The next step is to generate the RTL netlist (compiled netlist of the design). From the RTL netlist, the partitions can be specified. Setting partitions in the PlanAhead tools builds the xpartition.pxml file that is used by the implementation tools to specify the partitions and the partition attributes. The partitions define the isolated regions and the isolated functions in the PlanAhead tool.

15. To open the elaborated design in the PlanAhead tool, under the Project Manager view on the left, select **RTL Analysis > Open Elaborated Design**. See Figure 2-5.

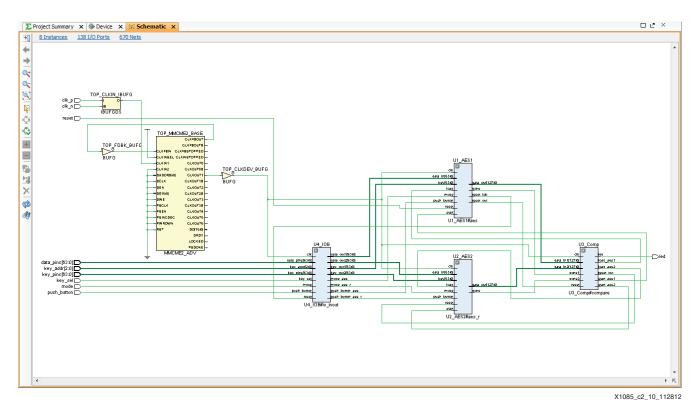

The RTL Netlist tab is displayed in the PlanAhead tool along with the RTL schematic.

*Note:* If at some time during the process of creating it, the lab must be saved and continued at a later time, the project must either be re-elaborated or the synthesized design must be re-opened.

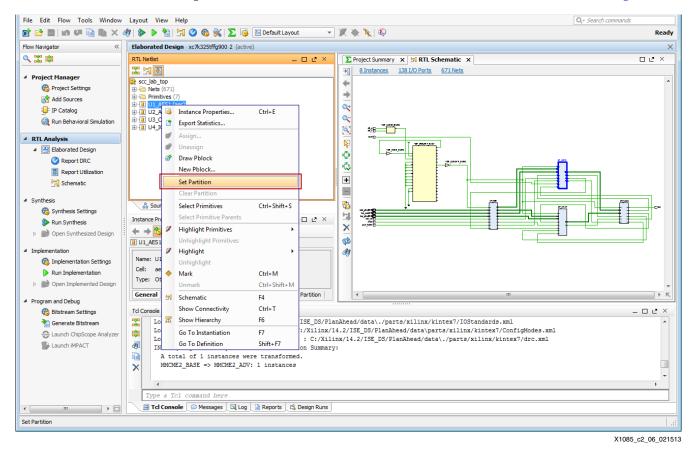

Each partition (isolated function) must be converted to an isolated partition (ISO). The square to the left of the instance name, in the RTL Netlist tab, turns solid yellow after the partition is set. This operation sets the is\_partition property to true for each partition.

🐮 XILINX.

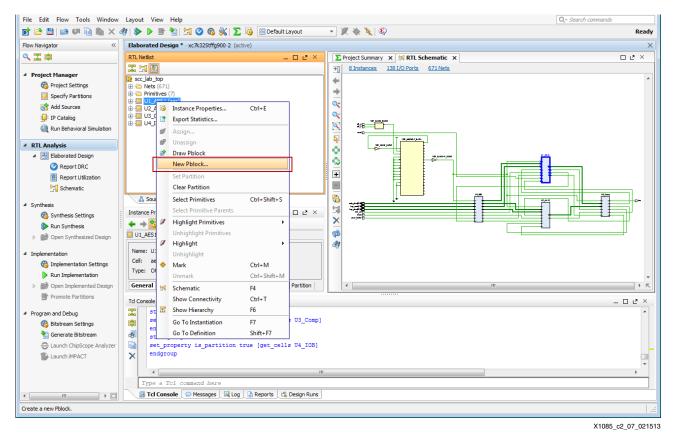

1. Right-click U1\_AES (AES) in the Netlist tab and select Set Partition (see Figure 2-6).

#### Figure 2-6: Set Partition

- 2. Repeat step 1 for the U2\_AES2 (AES\_R) partition.

- 3. Repeat step 1 for the U3\_Comp (COMPARE) partition.

- 4. Repeat step 1 for the U4\_IOB (IO\_INOUT) partition.

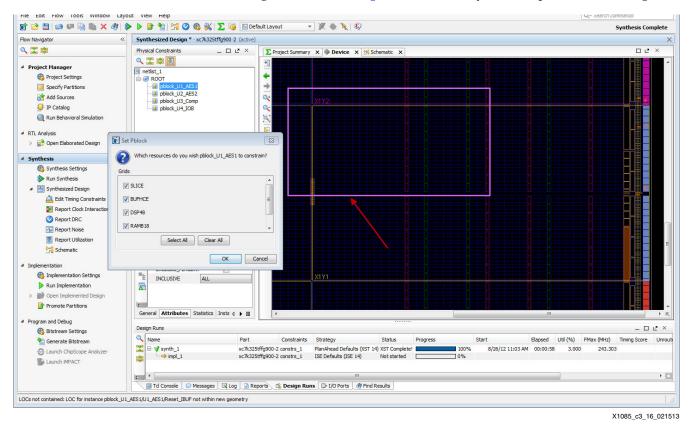

The PlanAhead tool uses pblocks to define the area group definition for an isolated region. Area group constraints specify the components that are reserved for implementation of a partition or isolated function. The Physical Constraints tab defines the partitions by identifying pblocks.

A new pblock must be created for each partition. The solid yellow square to the left of the instance name in the RTL Netlist tab has a blue check mark after New Pblock is selected. Later in the process, the pblock sizes are actually set for each partition.

www.xilinx.com

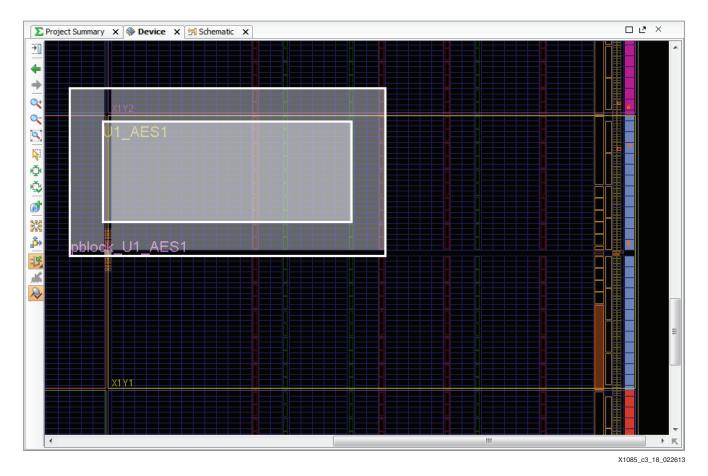

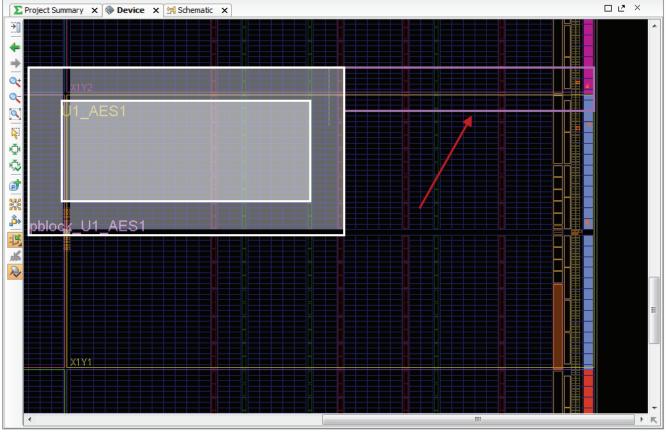

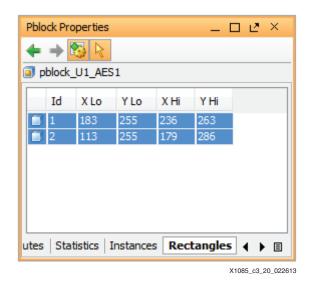

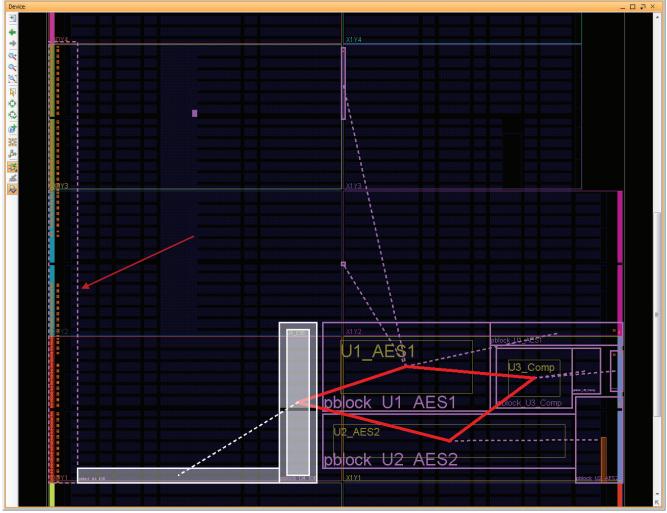

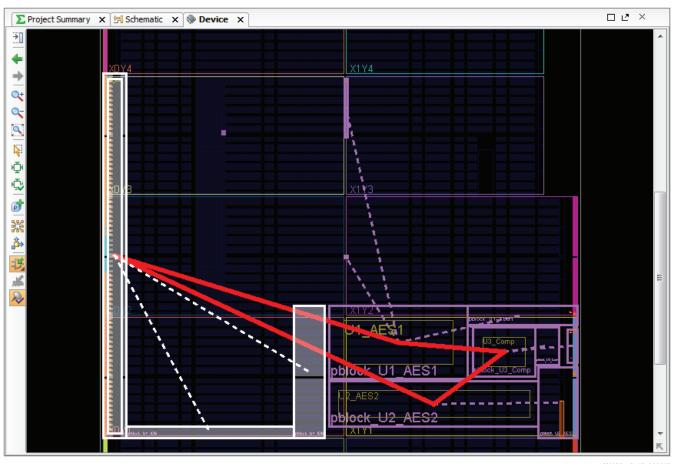

In the RTL\_Netlist tab, right-click the U1\_AES1 (AES) partition and select New Pblock (see Figure 2-7). Keep the default name, pblock\_U1\_AES1. Make sure that Assign selected instance is checked to map the pblock to the isolated function and click OK.

Figure 2-7: New Pblock

- 6. Repeat step 5 for the U2\_AES2 (AES\_R) partition while keeping the default name, pblock\_U2\_AES2.

- 7. Repeat step 5 for the U3\_Comp (COMPARE) partition while keeping the default name, pblock\_U3\_Comp.

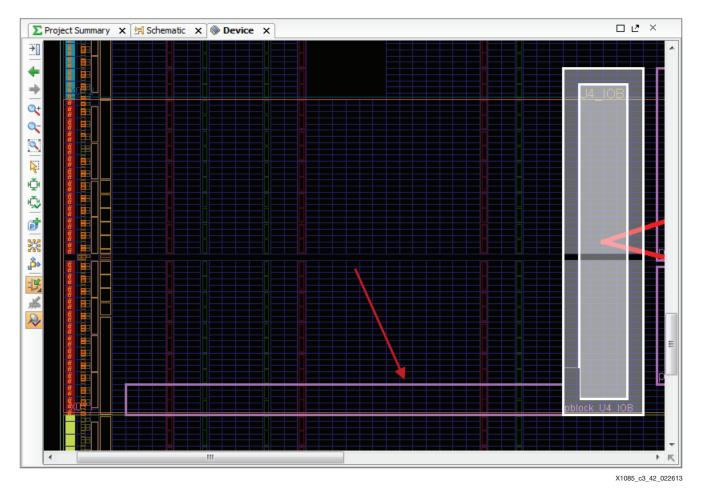

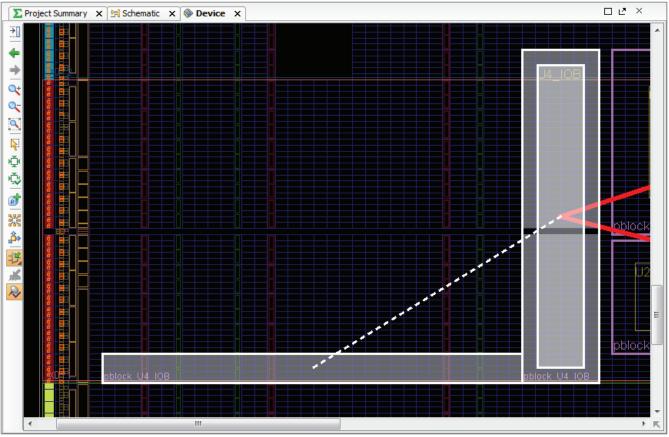

- 8. Repeat step 5 for the U4\_IOB (IO\_INOUT) partition while keeping the default name, pblock\_U4\_IOB.

## Synthesizing the Design

### Setting Synthesis Options and Synthesizing the Design

The PlanAhead tool now has enough information to automatically execute a bottom-up synthesis of the design.

Before running the synthesis, the synthesis options need to be specified. These steps describe how to synthesize the design:

1. Set the synthesis options by bringing up the XST Synthesis Options window. Click **Synthesis > Synthesis Settings** in the Flow Navigator window. Set Optimization

Goal (-opt\_mode) to **Area**, set Optimization Effort Level (-opt\_level) to **2**. Refer to the Synthesis window in the Project Settings dialog shown in Figure 2-8. The remaining synthesis settings can use the default setting. Click **OK**.

| Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

| Defection and the last the last the second s |                          |

| Default constraint set: 🔚 constrs_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (active)                 |

| Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

| Strategy: <u>Representations</u> Strategy:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (ST 14) 👻 🚹              |

| Description: PlanAhead Defaults (XST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | defaults with hierarchy) |

| □ Synthesis (xst)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| -opt_mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | area                     |

| -opt_level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2                        |

| -register_balancing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | no                       |

| -register_duplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | yes                      |

| -fsm_encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | auto                     |

| -lc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | off                      |

| -auto_bram_packing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | no                       |

| -use_dsp48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | auto                     |

| -resource_sharing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | yes                      |

| -shreg_extract<br>-iob                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | yes                      |

| -netlist_hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | rebuilt                  |

| -power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | no                       |

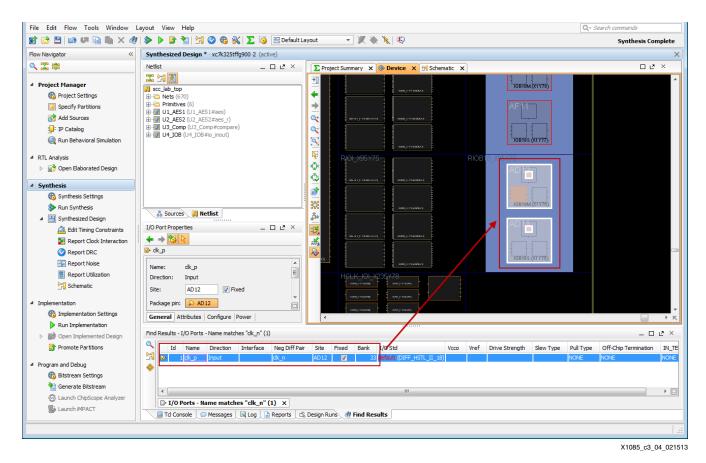

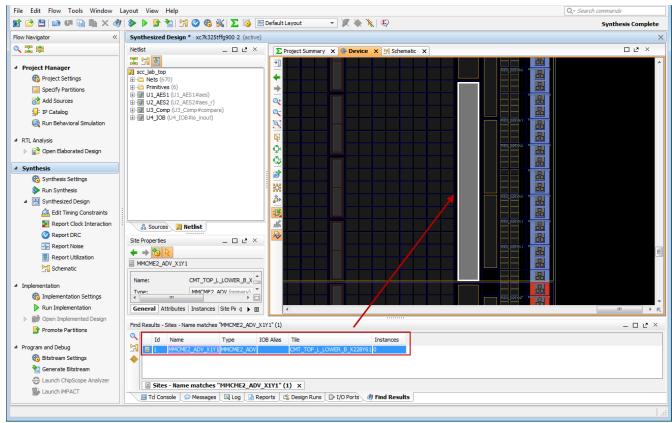

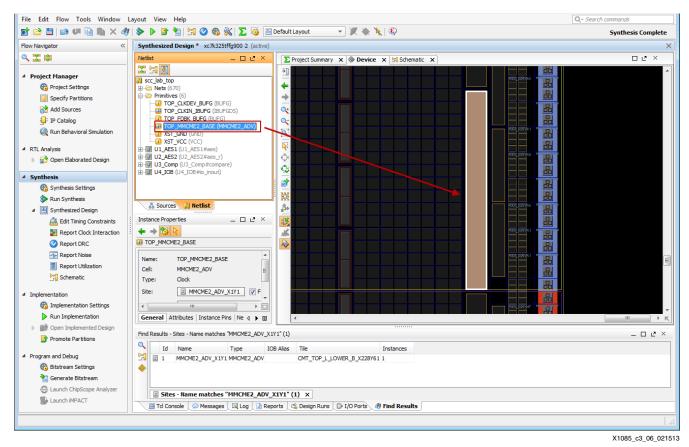

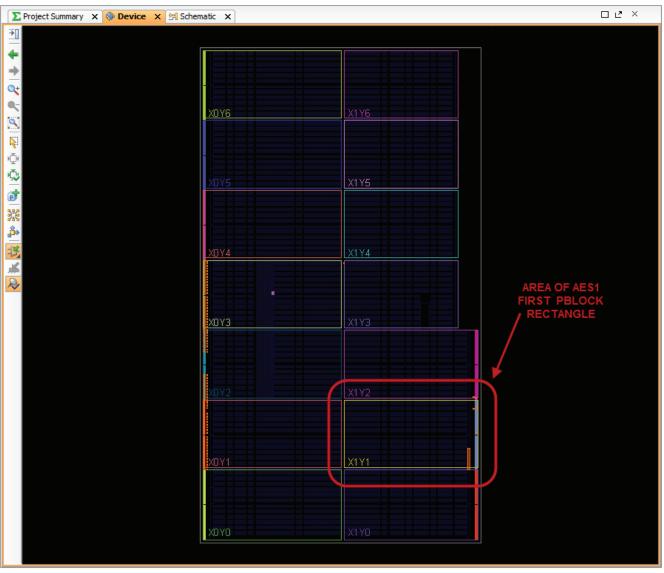

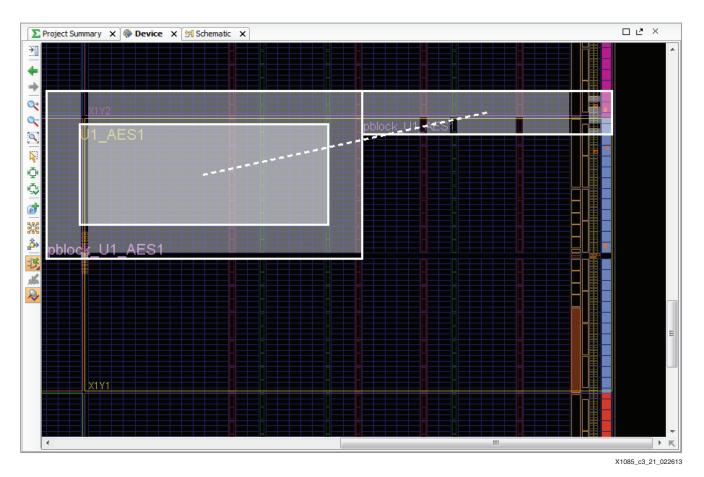

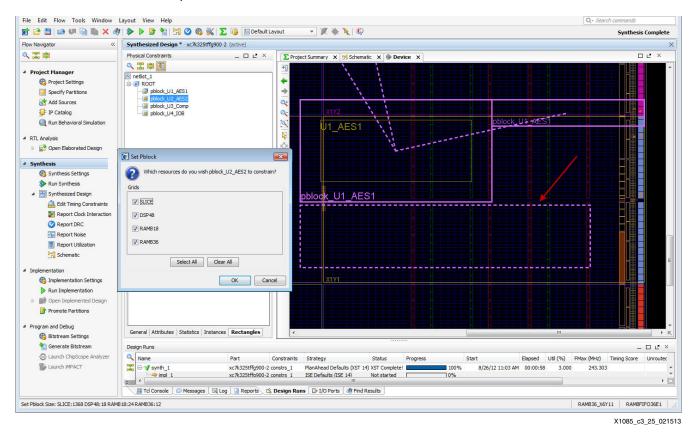

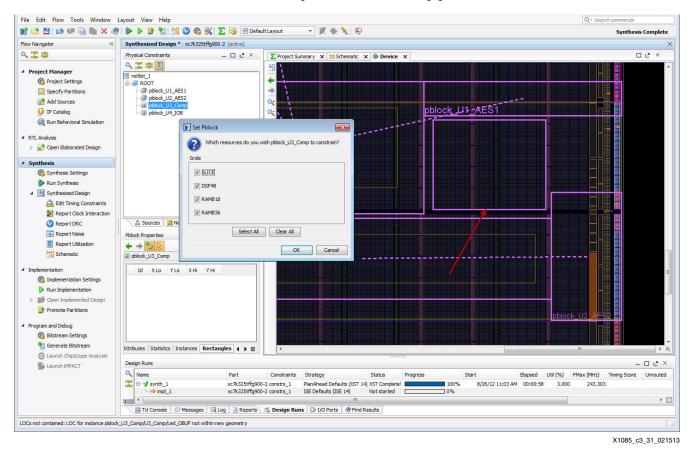

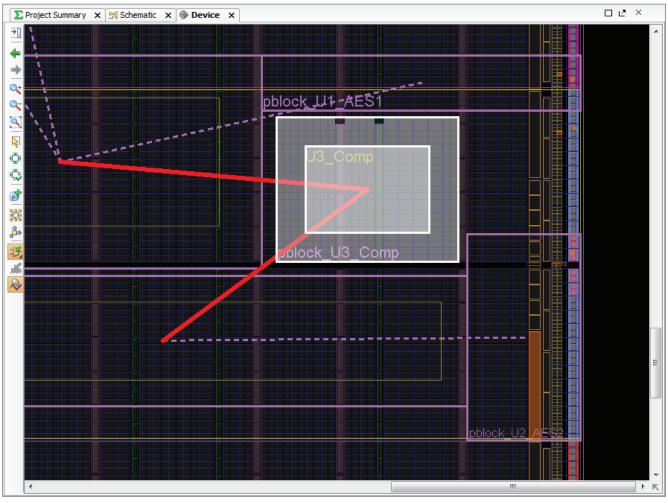

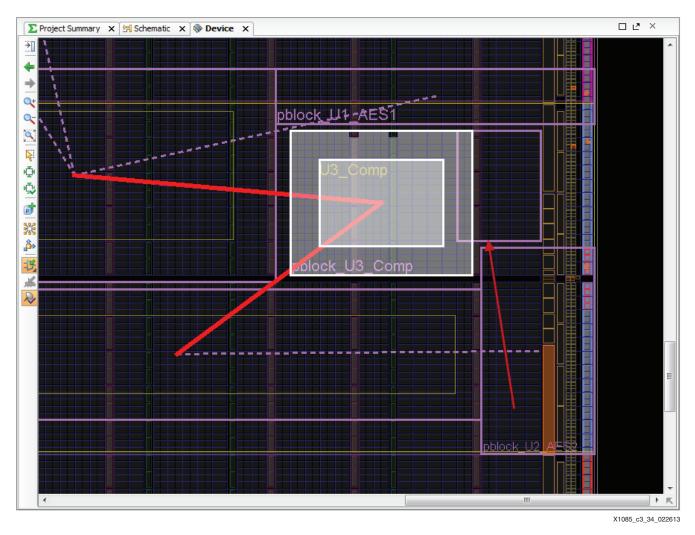

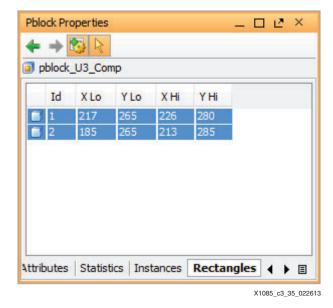

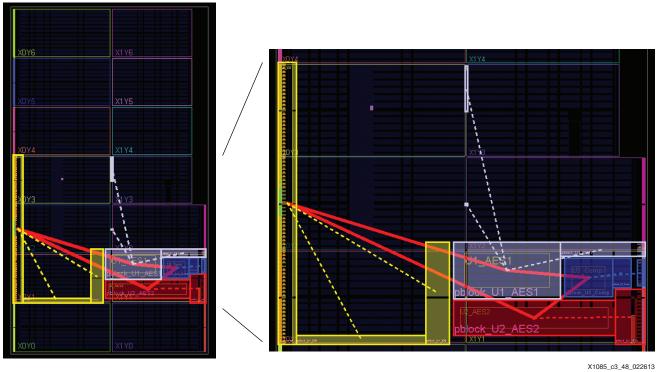

| ram_style                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | auto                     |