# Zebra<sup>™</sup> by Mipsology: Accelerating Neural Network Inference

# INTRODUCTION

#### FPGAs Ideally suited for Inference Acceleration

FPGAs are full of basic computing elements and filled with memories, ideally suitable for high performance and low latency CNN inference computing. They are reprogrammable at the hardware level allowing for continual adaptation. But FPGA programming can be challenging.

## SOLUTION OVERVIEW

#### Zebra Software Accelerates Inference

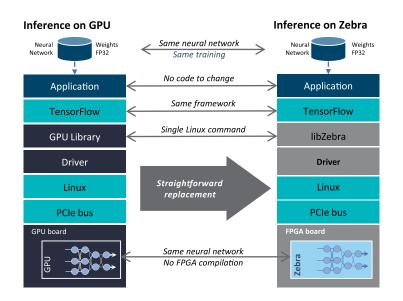

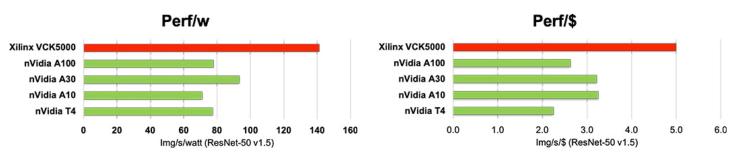

Zebra is the ideal compute engine to accelerate CNN inference. Zebra seamlessly replaces CPUs/GPUs to compute any neural network on an FPGA faster, with lower power consumption, and at lower cost.

Simply type a single Linux command. No knowledge of FPGA technology, compilation, or any changes to the environment or the application are required.

Zebra lets AI engineers focus on application development, while enjoying unmatched performance.

# AMD - XILINX ADVANTAGE

- > Delivers high performance from edge to cloud

- Supports most popular deep learning frameworks and broad range of CNN inference

- Easy to use a single Linux command replaces costly CPU or GPU inference nodes

- > Zero Neural Networks Change

- > Zero New Training

- > Zero Line of Code to Add

- > Zero FPGA Knowledge

- > Zero FPGA Compilation

- > Zero Transition Effort

- ... In Short, ZERO Effort

# AMDA XILINX

## **KEY BENEFITS**

#### **The Fastest Inference**

> Computes neural networks highest speed with lowest latency

#### Supports All Neural Networks

> Accelerates any CNN, including user defined neural networks

#### **Extremely Simple to Use**

> Deploying Zebra is a "Plug & Play" process

## **SOLUTION DETAILS**

#### **Neural Networks**

- > Supports CNN without modification

- Delivered with tested networks: GoogLeNet V1, Inception V3, Inception V4, VGG16, VGG19, ResNet50, ResNet152, YoloV1, YoloV2, YoloV3, Tiny YoloV2, Tiny YoloV3, VDSR, SSD, MobileNet

- > Accelerated layers: convolution, fully connected, max/average pooling, concat, batch norm, scale, add eltwise, reorg, up sampling, depth to space, reduce mean, dilated convolution, squeeze, separable depth wise, clip to value, relu, leaky relu, relu6

- > Automatic split of graph

- > Up to 3.2 billion weights

- > Up to 1 million layers

- > Unbounded number of convolutions

- > Single or multiple outputs

- > Up to 1360x1360x3 input images

- > Up to 24 simultaneous independent users

## No Changes to the Software Environment

> Not a single line of code must be changed in the application

## Scalable, Flexible and Adaptable

> Easy replacement of GPUs or complement CPUs

## **Supported Frameworks**

- > TensorFlow, PyTorch , ONNX, and many more

- > No change to source code required

#### Precision

- > 8 bit

- > Automatic proprietary quantization

#### Migration from GPU or CPU

- > Trained parameters from GPU/CPU training without changes

- No proprietary training or re training needed, and no pruning required

- > Usable immediately

- > Similar accuracy as FP32

#### **Power & Cooling**

> From few watts in the field to 140W in data centers

#### RESULTS

Zebra's quantization ensures results stay accurate and does not require retraining the NN.

# TAKE THE NEXT STEP

Learn more about Xilinx VCK5000 Development Card xilinx.com/products/boards-and-kits/vck5000

Japan

Corporate Headquarters Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124 USA Tel: 408-559-7778 www.xilinx.com

Xilinx Europe Bianconi Avenue Citywest Business Campus Saggart, County Dublin Ireland Tel: +353-1-464-0311 www.xilinx.com

Xilinx Europe

Xilinx K.K. Art Village Osaki Central Tower 4F 1-2-2 Osaki, Shinagawa-ku Tokyo 141-0032 Japan Tel: +81-3-6744-7777 japan.xilinx.com Asia Pacific Pte. Ltd. Xilinx, Asia Pacific 5 Changi Business Park Singapore 486040 Tel: +65-6407-3000 www.xilinx.com

Xilinx India Technology Services Pvt. Ltd. Block A, B, C, 8th & 13th floors, Meenakshi Tech Park, Survey No. 39 Gachibowli(V), Seri Lingampally (M), Hyderabad -500 084 Tel: +91-40-6721-4747 www.xilinx.com

India

© Copyright 2022 Advanced Micro Devices, Inc. All rights reserved. Xilinx, the Xilinx logo, AMD, the AMD Arrow logo, Alveo, Artix, Kintex, Kria, Spartan, Versal, Vitis, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight, Cortex, and PrimeCell are trademarks of ARM in the EU and other countries. PCIe, and PCI Express are trademarks of PCI-SIG and used under license. Printed in the U.S.A. SF03-4-22