# **Network Accelerator with Versal Premium Series**

- > Hardened infrastructure for greater power efficiency than competing FPGAs

- > Dynamically adapts for diverse workloads with custom datapaths

- > Complete network acceleration platform programmed in HLS or RTL

## **CHALLENGE**

The growth of data and compute complexity in data centers and cloud service providers has made it critically important to develop and integrate hardware accelerators to offload a broad range of applications from host CPUs. As network port speed and packet processing rates are overwhelming servers, additional packet processing and computational resources are required to have server CPU resources for other tasks. A new class of hardware accelerators has emerged to help offload CPU-intensive application processing to build a more scalable, low-latency processing pipeline.

# SOLUTION: VERSAL PREMIUM ACAP FOR NETWORK ACCELERATION

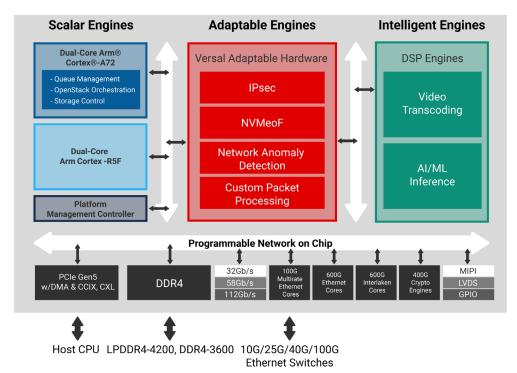

Xilinx network accelerators revolutionize the effective use of the CPU by providing composable and extensible dataplane programmability while offloading compute-extensive network processes such as IPsec and NVMeoF. Versal® Premium adaptive compute acceleration platforms (ACAPs) provide fundamental NIC functions as hard IP and deliver exceptional compute density to offload a wide range of workloads from network to compute to storage at low power to meet the PCIe® form factor requirements in many data centers and cloud environments.

#### Hardened Infrastructure for Superior Performance/Watt

Versal Premium devices feature networked, power-optimized cores including Ethernet cores, High-Speed Crypto Engines, integrated PCIe Gen5 with hardened DMA, a programmable network on chip (NoC), and DDR memory controllers. These key hard IP deliver power-efficient NIC functionality and have more device resources for hardware differentiation, such as inline machine learning and custom packet processing functions.

#### Dynamically Adapts for Diverse Workloads with Custom Datapaths

Equipped with a rich set of multicore, heterogeneous compute engines, Versal Premium devices offer unmatched composability to support new protocols, custom offloads, and application-specific datapaths. Software programmable hardware architecture with dynamic function exchange (DFx) allows users to swap compute kernels in milliseconds to provision network accelerators with streamlined orchestration for the most efficient use of cloud infrastructure.

#### **Complete Network Acceleration Platform Programmed in HLS or RTL**

Co-optimized for Vivado® Design Suite and Vitis<sup>™</sup> unified software platform, Versal Premium ACAP-based network accelerators provide a comprehensive suite of acceleration solutions to enable full custom RTL design, program abstractions such as HLS, and compute acceleration frameworks to enable both Xilinx and 3rd party applications.

1: Versal Premium VP1202 ACAP vs. Intel Agilex AGF027 FPGA for 2x100G Network Accelerator

**XILINX**

Less Power<sup>1</sup>

Versal Premium ACAP for 2x100G Network Accelerator (HHHL)

# VERSAL ACAP IMPLEMENTATION

#### 2X100G Network Accelerator in a 75W PCIe Form Factor

A Versal Premium ACAP implementation provides heterogeneous engines for optimal acceleration, a hardened shell for power-optimized fundamental infrastructure for network processing, hardware adaptability for composable dataplane programmability, and a form factor ideal for data center deployment.

#### VERSAL PREMIUM ACAP

| PLATFORM HIGHLIGHTS                        |                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Adaptable Engines                          | <ul> <li>Adaptable to offload regularly changing workloads across a broad set of applications including inline machine learning, video transcoding, hashing for blockchains, custom packet processing, and more</li> <li>Enable network traffic filtering, overlay network processing, and custom datapath features with low latency</li> </ul> |

| Intelligent (DSP)<br>Engines               | <ul> <li>Variable fixed- and floating-point DSP compute with up to 1GHz performance</li> <li>Ideal for video transcoding and AI / ML inference workloads</li> </ul>                                                                                                                                                                             |

| Scalar Engines                             | <ul> <li>Arm processing subsystem for queue management, OpenStack orchestration, and storage controller</li> <li>Platform management controller for security, power management, and bitstream management</li> </ul>                                                                                                                             |

| Programmable<br>Network on Chip            | <ul> <li>Seamless on-chip data movement for all engines and key interfaces</li> <li>Simplifies kernel and IP placement, reducing soft logic needed for connectivity</li> <li>Streamlines programming experience for software and hardware developers</li> </ul>                                                                                 |

| Integrated Shell                           | <ul> <li>Hardened host interface (PCIe Gen5 w/DMA, DDR4 controllers), interconnected by programmable NoC</li> <li>Ensures streamlined device bring-up and connectivity to off-chip interfaces-making the platform available at boot</li> <li>Delivers pre-engineered timing closure and logic resource savings</li> </ul>                       |

| Multirate Ethernet<br>MAC and Transceivers | <ul> <li>Supports the latest optical and electrical communication standards while preserving existing infrastructure</li> <li>Scalable and robust serial bandwidth for high-speed networking connectivity</li> </ul>                                                                                                                            |

### **BENCHMARK**

#### 75W Form Factor Network Accelerator

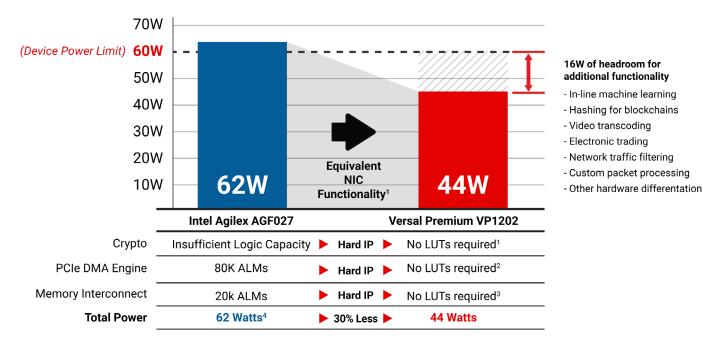

Shown below is a comparison of estimated power consumption of a Versal Premium device vs. a competing 10nm Agilex FPGA for a network accelerator application in an HHHL PCIe form factor and 75W power envelope. The Versal architecture's hardened infrastructure enables a power-optimized implementation with 16W power headroom for additional hardware differentiation. In contrast, the competing Intel Agilex FPGA exceeds the device power delivery limit. Hardened IP leveraged by the Versal ACAP include the integrated shell—comprising the programmable NoC, integrated PCIe Gen5 with integrated DMA, and DDR4 controllers–delivering programmable logic savings of 200K LUTs, as well as High-Speed Crypto Engines for security functions.

#### **DEVICE POWER CONSUMPTION**

1: Versal ACAPs feature hardened full-duplex 400G High-Speed Crypto Engines

2: Versal Premium ACAPs provide fully hardened PCIe Gen4/5 and DMA IP; Intel Agilex FPGAs provide PCIe Gen4 with soft DMA implementation only

3: The Versal ACAP's NoC provides hardened connectivity for memory subsystem

4: Quartus Power & Thermal Calculator 21.2 for Intel Agilex FPGA power calculation, includes SmartVID claimed static power savings

## TAKE THE NEXT STEP

- > To learn more about the breakthrough integration of Versal Premium series, watch the video

- > To try the above benchmark yourself, visit www.xilinx.com/versal-performance-elevated

- > For more information on the Versal Premium series, visit www.xilinx.com/versal-premium

- > To apply to the Versal Premium Evaluation Kit Early Access Program, visit Contact Sales

Versal Premium Evaluation Kit Contact Sales for Early Access

India

Corporate Headquarters

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124 USA Tel: 408-559-7778 www.xilinx.com

AMDA XILINX Xilinx Europe Bianconi Avenue Citywest Business Campus Saggart, County Dublin Ireland Tel: +353-1-464-0311 www.xilinx.com

Xilinx Europe

#### Japan

Xilinx K.K. Art Village Osaki Central Tower 4F 1-2-2 Osaki, Shinagawa-ku Tokyo 141-0032 Japan Tel: +81-3-6744-7777 japan.xilinx.com Asia Pacific Pte. Ltd.

Xilinx, Asia Pacific 5 Changi Business Park Singapore 486040 Tel: +65-6407-3000 www.xilinx.com Xilinx India Technology Services Pvt. Ltd. Block A, B, C, 8th & 13th floors, Meenakshi Tech Park, Survey No. 39 Gachibowli(V), Seri Lingampally (M), Hyderabad -500 084 Tel: +91-40-6721-4747 www.xilinx.com

© Copyright 2021 Advanced Micro Devices, Inc. All rights reserved. Xilinx, the Xilinx logo, AMD, the AMD Arrow logo, Alveo, Artix, Kintex, Kria, Spartan, Versal, Vitis, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight, Cortex, and PrimeCell are trademarks of ARM in the EU and other countries. PCIe, and PCI Express are trademarks of PCI-SIG and used under license. Printed in the U.S.A. AC11-2-21